基于FPGA芯片的最小系统设计

- 格式:docx

- 大小:3.86 MB

- 文档页数:53

《电子设计自动化(EDA)技术》课程实训报告题目: 基于EPF10K10LC84-3的FPGA最小系统姓名:院系:专业:学号:指导教师:完成时间: 年月日目录1 课程设计题目、内容与要求……………………………………4页1.1 设计内容…………………………………………………4页1.2 具体要求…………………………………………………4页2 系统设计…………………………………………………………5页2.1系统原理…………………………………………………5页2.2 设计思路…………………………………………………6页3 系统实现……………………………………………………… 6页3.1电源电路和复位电路模块………………………………6页3.2 外部时钟模块……………………………………………6页3.3 下载电路模块……………………………………………7页4 硬件验证操作说明………………………………………………7页4.1 PCB工程项目的环境创建…………………………………7页4.2原理图的编写和ERC检查…………………………………8页4.3元件的封装检查……………………………………………9页4.4 PCB图中元件的布局和布线………………………………9页5总结………………………………………………………………12页6 参考书目…………………………………………………………12页基于EPF10K10LC84-3的FPGA最小系统摘要:提出一种新的FPGA最小系统开发板的设计思想,开发板以ALTERA公司的的ACEX1K 系列的EPF10K10LC84-3为主芯片,整体采用模块的设计,文章对最小系统的原理框图、信号的运行流程进行了详细地阐述,并给出了实际的制作过程图例。

此FPGA实用价值不错,并且FPGA与以微处理器为核心的数字系统相比,具有可靠性高,可实时升级、体积小巧、结构简单、运行速度快的优点。

关键词:FPGA 设计最小系统1 课程设计题目、内容与要求1.1 设计题目基于EPF10K10LC84-3的FPGA最小系统1.2 设计内容芯片电源和复位电路时钟脉冲电路接口电路1.3 具体要求1.电源电路将产生一个3.3V和1.5V的输出电路,复位电路利用高低电平的原理设计;2.显示电路由7段数码管进行显示;3.下载电路连接芯片与电脑之间的数据传输;4.外部时钟电路将产生标准1Hz的秒脉冲信号2 系统设计2.1 设计原理基于EPF10K10LC84-3的FPGA最小系统2.2设计思路1.电源电路将产生一个3.3V和1.5V的输出电路,复位电路利用高低电平的原理设计;2.显示电路由7段数码管进行显示;3.下载电路连接芯片与电脑之间的数据传输;4.外部时钟电路将产生标准1Hz的秒脉冲信号3 系统实现3.1电源电路和复位电路模块电源电路VREF一般是3.3V,假定VCC出入为5V,则此电路可输出一个3.3V和1.5V 的电压。

计算机工程与设计COMPUTER ENGINEERING AND DESIGNApr.2021Vol.42 No.42021年4月第42卷第4期基于RISC-V 的计算机系统综合实验设计孙卫真1!刘雪松朱威浦2 !向 勇3 +(1首都师范大学 信息工程学院,北京100048; 2.中国科学院计算技术研究所,北京101407;3.清华大学 计算机科学与技术系,北京100084)摘要:针对目前高校计算机系统各课程实验衔接不紧密、实验成本较高的问题!提出设计基于小型FPGA 开发板、以 RISC-V CPU 和Rut 操作系统内核为核心的计算机系统综合实验平台。

硬件实验以在低成本FPGA 芯片上搭建picorv32 RISC-V CPU 为核心!软件实验以在硬件实验基础上移植Rut 编写的rCore 教学操作系统为核心。

以较低成本在同一平台 完成计算机组成原理与操作系统实验设计!使其形成一个有机的整体,在资源与成本有限的情况下构建一个较为完整的实验体系。

实例结果表明!实验平台以软硬件协作的方式,适应技术的发展!及时更新实验内容!可满足高校计算机系统教学综合实验的基本要求。

关键词:RISC-V &系统编程语言;组成原理实验&操作系统实验&软硬件协作中图法分类号:TP301 文献标识号:A 文章编号:1000-7024 (2021 041159-07doi : 10. 16208/j. issnl 000-7024. 2021. 04. 037De?ign for comprehen?ive laboratory of computer?y?tem ba?ed onRISC-VSUN Wei-zhen 1, LIU Xue-song 1, ZHU Wei-pu 2, XIANG Yong 3+(1. I n f o r m a t i o n E n g i n e r i n g C o l e g e , C a p i t a l N o r m a l U n i v e r s i t y # B e i j n g 10048, C h i n a ;2. I n s t i u t e o f C o m p u t i n g T e c h n o l o g y , C h i n e s e A c a d e m y o f S c i e n c e s , B e i j n g 101407 , C h i n a ;3. Department of Computer Science and Technology , Tsinghua University , Beijing 100084 , China)Abstract: A i m i n g a t r y i n g t o i m p r o v e t h e e x p e r i m e n t a l c o n e c t i o n a m o n g t h e c o m p u t e r s y s t e m c o u r s e s i n t h e u n i v e r s i t e s a n d r e - d u c e t h e x p e r i m e n t c o s t #a c o m p r e h e n s i v e c o m p u t e r s y s t e m e x p e r i m e n t a l p l a t f o r m b a s e d o n a s m a lF PG Ab o a r d a n d a t e a c h i n g o p e r a t i o n s y s t e m w a s p r o p o s e d . T h e h a r d w a r e e x p e r i m e n t w a s b u i l d i n g a s y s t e m o n c h i p (S o C ) w i t h p i c o r v 32 R I S C -V C P U o n a l o w -c o s t F P G A c h i p . T h e s o f t w a r e e x p e r i m e n t w a s t r a n s p l a n t i n g t h e r C o r e t e a c h i n g o p e r a t i o n s y s t e m w r i t e n b y R u s t o n t h e i r o w n S o C . T h e c o m p u t e r c o m p o s i t o n p r i n c i p l e a n d o p e r a t i o n s y s t e m e x p e r i m e n t a l d e s i g n o n t h e s a m e p l a t f o r m a t a l o w e r c o s t wa s F o m p l e t e d #a n d a n o r g a n i F w h o l e w a s f o r m e d . T h e e x p e r i m e n t a l s y s t e m w a s a r e l a t i v e F o m p l e t e p l a t f o r m w i t h l i m i t e d F o s t s . E x a m p l e s h o w t h a t #t h e x p e r i m e n t a l F o n t e n t s a r e t i m e l y u p d a t e d f o r t r a F i n g F o m p u t e r t e F h n o l o g y t r e n d s i n a s o f t w a r e -h a r d - w a r e c o p e r a t i v e m a n e r t o m e t h e b a s i c r e q u i r e m e n t s o f c o m p u t e r s y s t e m t e a c h i n g e x p e r i m e n t s i n u n i v e r s i t e s .Keywords :RI S C -V ; s y s t e m p r o g r a m mi n g l a n g u a g e ; c o m p o s i t o n p r i n c i p l e e x p e r i m e n t ; o p e r a t i n g s y s t e m e x p e r i m e n t ; s o f t w a r e h a r d w a r e c o p e r a t i v e4引言目前,高校进行计算机系统教学实验主要有以下几种教学方式:其一是使用纯硬件搭建实验平台,虽该方式可深入接触计算机硬件模块,但实验操作机械死板、硬件平台开发成本较高;其二是采用软件系统仿真的方式,该方法成本较低、易于上手,但受教育者不能在实验过程中较好体会到计算机与硬件的紧密结合!为了优化上述问题,实现设计目标,本文从硬件支持、 处理器构建、系统编程语言选择三方面考虑,构建计算机 系统实验平台。

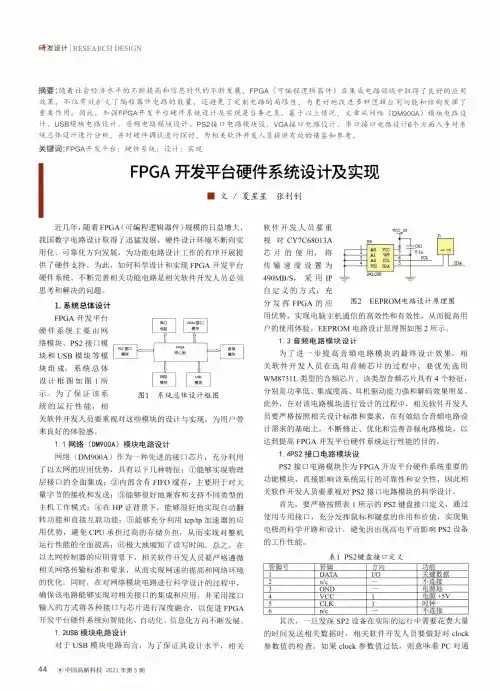

研发设计 I RESEARCH DESIGN樓块图1系统总体设计框图近几年,随着FPGA (可编程逻辑器件)规模的日益增大, 我国数字电路设计取得了迅猛发展,硬件设计环境不断向实 用化、可靠化方向发展,为功能电路设计工作的有序开展提 供了硬件支持。

为此,如何科学设计和实现FPGA 开发平台 硬件系统、不断完善相关功能电路是相关软件开发人员必须思考和解决的问题。

1.系统总体设计FPGA 开发平台硬件系统主要由网 络模块、PS 2接口模 块和U S B 模块等模 块组成,系统总体 设计框图如图1所 示。

为了保证该系 统的运行性能,相关软件开发人员要重视对这些模块的设计与实现,为用户带 来良好的体验感。

1.1网络(D M 900A )模块电路设计网络(DM 900A )作为一种先进的接口芯片,充分利用 了以太网的应用优势,具有以下几种特征:①能够实现物理 层接口的全面集成;②内部含有FIFO 缓存,主要用于对大 量字节的接收和发送:③能够很好地兼容和支持不同类型的 主机工作模式;④在HP 证背景下,能够很好地实现自动翻 转功能和直接互联功能;⑤能够充分利用tcp /tp 加速器的应 用优势,避免CPU 承担过高的存储负担,从而实现对整机 运行性能的全面提高:⑥极大地缩短了读写时间。

总之,在 以太网控制器的应用背景下,相关软件开发人员要严格遵循 相关网络传输标准和要求,从而实现网速的提高和网络环境 的优化。

同时,在对网络模块电路进行科学设计的过程中, 确保该电路能够实现对相关接口的集成和应用,并采用接口 输入的方式将各种接口与芯片进行深度融合,以促进FPGA 开发平台硬件系统向智能化、自动化、信息化方向不断发展。

1.2USB 模块电路设计对于U S B 模块电路而言,为了保证其设计水平,相关软件开发人员要重 视对 CY 7C 68013A 芯片的使用,将 传输速度设置为摘要:随着社会经济水平的不断提高和信息时代的不断发展,FPGA (可编程逻辑器件)在集成电路领域中取得了良好的应用 效果,不仅有效扩大了编程器件电路的数量,还避免了定制电路的局限性,为更好地改进多种逻辑应用功能和结构发挥了 重要作用。

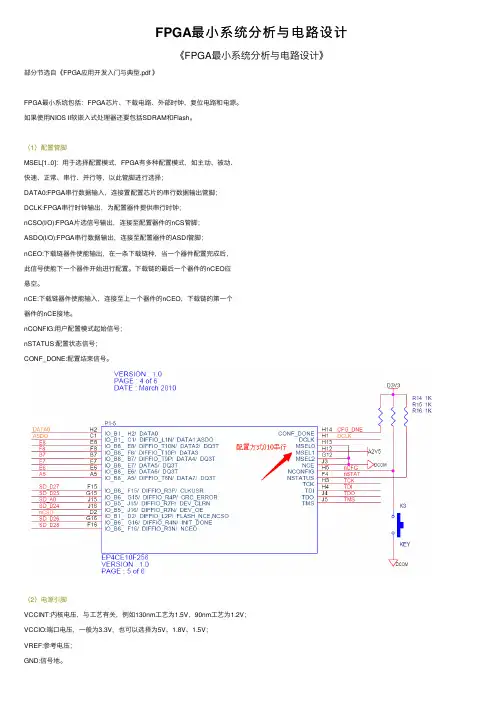

FPGA最⼩系统分析与电路设计《FPGA最⼩系统分析与电路设计》部分节选⾃《FPGA应⽤开发⼊门与典型.pdf 》FPGA最⼩系统包括:FPGA芯⽚、下载电路、外部时钟、复位电路和电源。

如果使⽤NIOS II软嵌⼊式处理器还要包括SDRAM和Flash。

(1)配置管脚MSEL[1..0]:⽤于选择配置模式,FPGA有多种配置模式,如主动、被动、快速、正常、串⾏、并⾏等,以此管脚进⾏选择;DATA0:FPGA串⾏数据输⼊,连接置配置芯⽚的串⾏数据输出管脚;DCLK:FPGA串⾏时钟输出,为配置器件提供串⾏时钟;nCSO(I/O):FPGA⽚选信号输出,连接⾄配置器件的nCS管脚;ASDO(I/O):FPGA串⾏数据输出,连接⾄配置器件的ASDI管脚;nCEO:下载链器件使能输出,在⼀条下载链种,当⼀个器件配置完成后,此信号使能下⼀个器件开始进⾏配置。

下载链的最后⼀个器件的nCEO应悬空。

nCE:下载链器件使能输⼊,连接⾄上⼀个器件的nCEO,下载链的第⼀个器件的nCE接地。

nCONFIG:⽤户配置模式起始信号;nSTATUS:配置状态信号;CONF_DONE:配置结束信号。

(2)电源引脚VCCINT:内核电压,与⼯艺有关,例如130nm⼯艺为1.5V,90nm⼯艺为1.2V;VCCIO:端⼝电压,⼀般为3.3V,也可以选择为5V、1.8V、1.5V;VREF:参考电压;GND:信号地。

(4)时钟管脚VCC_PLL:锁相环管脚电压,直接连VCCIO。

VCCA_PLL:锁相环模拟电压,⼀般通过滤波器连到VCCINT上。

GNDA_PLL:锁相环模拟地。

GNDD_PLL:锁相环数字地。

CLKnum(LVDSCLKnump):锁相环时钟输⼊,⽀持LVDS时钟输⼊,p接正端,num表⽰PLL序号。

CLKnum(LVDSCLKnumn):锁相环时钟输⼊,⽀持LVDS时钟输⼊,n接负端,num表⽰PLL序号。

PLLnum_OUTp(I/O):锁相环时钟输出,⽀持LVDS时钟输⼊,p接正端,num表⽰PLL序号。

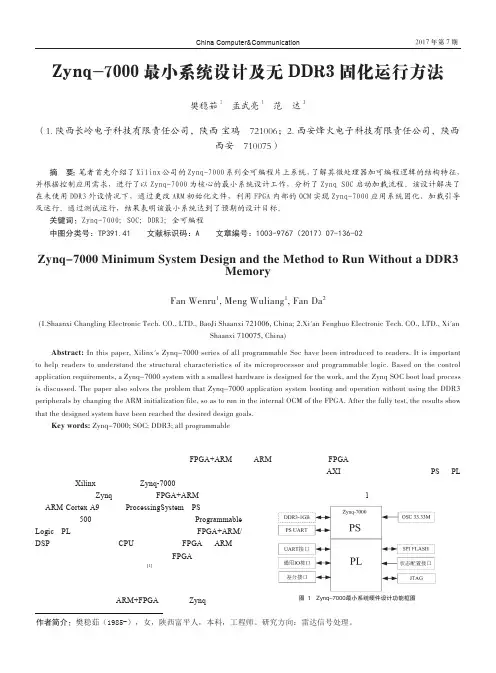

图1 Zynq-7000最小系统硬件设计功能框图樊稳茹(1985-),女,陕西富平人,本科,工程师。

研究方向:雷达信号处理。

2017年第7期信息与电脑China Computer&Communication软件开发与应用该最小系统PS部分结合用户应用程序用于实现控制功能,PL部分包括UART接口、时序产生、地址译码、片上存储和外设控制等逻辑功能模块。

主要的功能芯片为X7Z045、MT41K256M16HA、MAX3160E、MAX3096、MAX3045、W25Q128、ADG3308等,为了降低硬件成本,在满足使用需求的条件下,该最小系统设计时取消了图1中虚线框中的DDR3存储器。

2 基本启动配置流程分析Zynq是一个可扩展处理平台,简单地说就是有个FPGA 做外设的A9双核处理器,所以它的启动流程与FPGA完全不同,而与ARM处理器类似。

Zynq支持JTAG、NAND、Parallel NOR、QSPI以及SD卡等启动方式。

Zynq有效利用了片上的CPU来帮助配置,在没有外部JTAG的情况下,处理器系统(PS)与可编程逻辑(PL)都必须依靠PS来完成芯片的初始化配置,内部的启动存储区(BootROM)和芯片配置单元可实现Zynq从BootROM主动启动或者从JTAG被动启动[2]。

与其他XILINX 7系列的器件不同的是,Zynq并不支持从PL端直接进行启动配置,Zynq的启动配置是分多级进行的,配置过程最少需要两步,但通常是按如下三个阶段进行。

阶段0(Stage0):简称BootROM,控制着整个芯片的初始化过程。

该部分代码是不可修改的,处理器核在上电或者热启动时自动执行这部分代码,并对外部的NAND、NOR、SD等外设控制器进行初始化,同时还负责将阶段1的启动镜像(FSBL镜像)加载到OCM(Zynq片上一个256K的RAM,但在FSBL运行前只能使用其中的192K,所以FSBL要小于192K),然后运行FSBL,FSBL镜像来源由板上MIO[5:3]引脚选择的启动方式决定。

引言随着经济和科学技术的发展,电梯在高层建筑物的作用越来越凸出。

目前电梯主要分为机械系统与控制系统两大部份,而电梯的控制系统主要有三种控制方式分别是:继电路控制系统(“早期安装的电梯多位继电器控制系统)、基于FPGA控制系统、微机控制系统。

实现继电路控制系统方法很多,可以用标准逻辑器件、可编程序控制器PLC、单片机等方案来实现。

但是这些方法的功能修改及调试都需要硬件电路的支持,在一定程度上增加了功能修改及系统调试的困难,且该系统由于故障率高、可靠性差、控制方式不灵活以及消耗功率大等缺点,已渐渐被人民淘汰。

微机控制系统虽在智能控制方面有较强的功能,但也存在抗扰性差,系统设计复杂,一般维修人员难以掌握其维修技术等缺陷,没能广泛应用电梯中。

而基于FPGA的电梯控制系统由于可靠性高,使用维修方便,抗干扰性强,设计和调试周期较短等优点,在电梯控制中得到广泛应用,从而使电梯由传统的继电器控制方式发展为计算机控制的一个重要方向,成为当前电梯控制和技术改造的热点之一。

本文给出一个基于FPGA的6层自动升降电梯控制系统的设计方案。

它的设计是采用通俗易懂的Verilog HDL硬件描述语言使用EDA技术在Quartus II软件平台上设计完成,程序设计、编译以及时序仿真通过后再下载到开发板配合外围电路(模拟电梯的电路)来验证该系统的可行性。

这个系统分主要有6个模块,分别是键盘响应寄存处理模块、上升/下降请求寄存处理模块、电梯运行和停止处理模块、开门/关门与延时处理模块、电梯运行方向判断模块和电梯运行状态显示模块。

通过模块化设计不仅提高了程序编程错误的排查能力还提高了系统的可靠性。

1 概论1.1 电梯国内外现状1.1.1国内现状电梯作为中国对外最早的行业经过多年的发展,电梯产品无论在数量和质量都有了显著的提高,和国外产品差距越来越小。

考虑到经济性,现有国内的电梯控制系统,通常采用微机或可编程逻辑控制器对变频器进行多段速控制。

《电路设计与PCB制板》设计报告题目:STM32F103最小系统学院:专业:班级:姓名:学号:引言:Altium Designer基于一个软件集成平台,把为电子产品开发提供完整环境所需工具全部整合在一个应用软件中。

Altium Designer 包含所有设计任务所需工具:原理图和PCB设计、基于FPGA的嵌入式系统设计和开发。

目前我们使用到的功能特点主要有以下几点:1、提供了丰富的原理图组件和PCB封装库并且为设计新的器件提供了封装,简化了封装设计过程。

2、提供了层次原理图设计方法,支持“自上向下”的设计思想,使大型电路设计的工作组开发方式称为可能。

3、提供了强大的查错功能,原理图中的ERC(电气规则检查)工具和PCB的DRC(设计规则检查)工具能帮助设计者更快的查出和改正错误。

4、全面兼容Protel系列以前的版本,并提供orcad格式文件的转换。

一、课程设计目的1、培养学生掌握、使用实用电子线路、计算机系统设计、制板的能力;2.提高学生读图、分析线路和正确绘制设计线路、系统的能力;3.了解原理图设计基础、了解设计环境设置、学习Altium Designer 软件的功能及使用方法;4。

掌握绘制原理图的各种工具、利用软件绘制原理图;5。

掌握编辑元器件的方法构造原理图元件库;6。

熟练掌握手工绘制电路版的方法,并掌握绘制编辑元件封装图的方法,自己构造印制板元件库;7.了解电路板设计的一般规则、利用软件绘制原理图并自动生成印制板图。

二、设计过程规划1、根据实物板设计方案;2、制作原理图组件;3、绘制原理图;4、选择或绘制元器件的封装;5、导入PCB图进行绘制及布线;6、进入DRC检查;三、原理图绘制✧新建工程:1。

在菜单栏选择File →New →Project →PCB Project2.Projects面板出现。

3。

重新命名项目文件。

✧新建原理图纸1。

单击File →New→Schematic,或者在Files面板的New单元选择:Schematic Sheet.2.通过选择File →Save As来将新原理图文件重命名(扩展名为STM32最小系统。

FPGA的最小硬件系统设计FPGA(现场可编程门阵列)是一种可编程的集成电路,其具有实现数字电路功能的能力。

然而,要实现一个完整的硬件系统,需要考虑到诸多因素,包括FPGA的资源利用、时序设计、通信接口、外设接口、时钟管理等等。

下面是一个关于FPGA最小硬件系统设计的详细说明。

一、FPGA的资源利用1.时钟资源:FPGA系统通常需要一个时钟源。

最小硬件系统设计中,可以采用一个外部时钟来驱动FPGA系统,这可以通过将时钟信号连接到FPGA的时钟引脚上来实现。

2.逻辑资源:FPGA包含大量的逻辑门用于实现所需的数字逻辑电路功能。

这些逻辑门可以通过在FPGA开发环境中进行引脚映射和逻辑编程来实现。

二、时序设计1.时钟分频:要实现复杂的数字逻辑电路,通常需要使用其他频率的时钟信号。

在FPGA中,可以使用时钟分频电路来生成所需的时钟频率。

2.时序限制:FPGA的时序限制是为了确保逻辑电路能在正确的时间窗口内运行。

时序限制可以通过指定逻辑电路路径上的延迟时间来实现。

三、通信接口1.串口:串口是一种常用的通信接口,适用于与其他设备进行数据交换。

在FPGA系统中,可以通过配置FPGA的引脚和使用适当的通信协议来实现串口通信。

2.并行接口:并行接口主要用于高速数据传输,相对于串口更适合传输大量数据。

在FPGA系统中,可以通过配置引脚和使用适当的并行接口协议来实现并行接口。

四、外设接口1.存储器接口:存储器接口用于与外部存储器进行数据交换。

在FPGA系统中,可以使用存储器控制器和适当的存储器接口协议来实现存储器接口。

2.传感器接口:传感器接口用于与外部传感器进行数据交换。

在FPGA系统中,可以使用模数转换器(ADC)和数字模数转换器(DAC)来实现传感器接口。

五、时钟管理1.时钟分配:在FPGA系统中,需要使用时钟信号来驱动各个模块。

通过时钟分配,可以将时钟信号传输到不同的模块中,这可以通过时钟分配网络来实现。

2.时钟域划分:在FPGA系统中,通常存在多个时钟域。

武汉工业学院毕业设计(论文)设计(论文)题目:基于FPGA的信号发生器设计姓名学号院系电气与电子工程学院专业电子信息科学与技术指导教师目录摘要 ...................................................................................................................................... i ii Abstract (iv)前言 (1)1绪论 (3)1.1 FPGA简介 (3)1.2 modelsim简介 (5)1.3 DDS基本原理介绍 (6)2设计方案 (8)2.1 总体设计方案 (8)2.2方案论证 (8)2.2.1方案一 (8)2.2.2方案二 (9)2.2.3方案三 (9)2.3方案确定 (9)3 硬件电路设计 (11)3.1硬件设计注意事项 (11)3.2 DA电路 (11)3.3滤波电路 (12)3.4硬件电路实现 (13)4软件设计 (14)4.1波形产生模块 (14)4.1.1正弦波 (14)4.1.2方波 (15)4.1.3 三角波 (15)4.2频率控制模块 (16)4.3相位累加模块 (17)4.4选择波形模块 (17)4.5幅度控制模块 (18)4.6软件设计总成 (19)5 调试 (20)5.1设计及仿真调试使用设备 (20)5.2 调试方法 (20)5.2.1 硬件调试 (20)5.2.2 软件调试 (20)5.2.3 综合调试 (20)5.3 调试结果 (21)5.3.1 软件仿真结果及分析 (21)5.3.2 综合调试结果 (24)总结 (25)致谢辞 (26)参考文献 (27)附件1 ROM生成源程序 (28)附件2 40位流水线加法器程序 (30)摘要信号发生器是数字设备运行工作中必不可少的一部分,没有良好的信号源,最终就会导致系统不能够正常工作,更不必谈什么实现其它功能了。

Cyclone III FPGA最小系统设计李柱炎2011.12.10目录1.前言 (1)2.CycloneⅢ系列FPGA的管脚 (1)3.CycloneⅢ系列FPGA的配置模式与配置过程 (3)4.FPGA的最小系统 (6)1.前言当今,FPGA的生产商主要有四大家:Altera、Xilinx、Actel、Lattice。

主流的FPGA的实现工艺有三种:SRAM结构、Flash结构、反融丝结构。

采用SRAM 结构的厂商有Altera,Xilinx,Lattice,采用Flash结构的厂商有Actel,Lattice,采用反融丝结构的厂商有Actel。

SRAM结构的FPGA优点是:灵活,速度快;缺点是:易受干扰。

FALSH 结构的FPGA优点是:灵活,稳定可靠;缺点是:速度一般,编译工具差。

反融丝结构的FPGA优点是:稳定,可靠性非常高;缺点是:灵活性差,价格昂贵。

国内应用最多的FPGA品牌是Altera和Xilinx,其中Altera品牌在国内应用得最多,这是因为Altera进入中国市场较多,与中国的许多大学合作建立了实验室推广Altera的FPGA技术,培养了大量了Altera的FPGA技术人才。

2.CycloneⅢ系列FPGA的管脚CycloneⅢ系列FPGA的管脚主要包括:用户I/O、电源管脚、时钟管脚、配置管脚等,其中有些管脚可有多种用途。

(1)IO:用户IO管脚,可用作输入口,或输出口,或双向口,可以根据应用需要,用户自定义管脚功能。

部分IO管脚支持LVDS差分电平标准,DIFFIO_B num p和DIFFIO_B numn分别接LVDS差分对的正端和负端,num表示LVDS差分对的序号。

(2)电源管脚。

VCCINT:内核工作电源管脚。

CycloneⅢ系列FPGA的工作电压为1.2V,低内核工作电压可以降低芯片的功率。

VCCIO num:IO端口电源管脚。

CycloneⅢ系列FPGA支持3.3V、3.0V、2.5V,1.8V,1.5V、1.2V IO端口电压,以适应各种各样IO电平标准。

FPGA最小系统的数字电源设计FPGA(Field Programmable Gate Array)是一种灵活可编程的集成电路,可以通过编程实现数字逻辑功能。

在FPGA的设计中,数字电源是非常重要的一部分,它为FPGA芯片提供稳定且干净的电源供应,对FPGA的性能和可靠性起着至关重要的作用。

本文将介绍FPGA最小系统的数字电源设计。

数字电源主要包括三个部分:电源管理模块、电源滤波模块和电源输出模块。

电源管理模块负责从外部电源或电池中获取稳定电压,电源滤波模块负责消除电源中的噪声和杂散,电源输出模块则将经过处理的电源提供给FPGA芯片使用。

在FPGA最小系统的数字电源设计中,首先需要确定FPGA芯片的电源需求。

通常情况下,FPGA芯片的电源需求包括核心电压、I/O电压以及其他辅助电压。

核心电压是FPGA芯片内部逻辑电路所需要的电压,I/O电压是FPGA芯片与外部设备进行通信所需要的电压,而其他辅助电压则是为了支持FPGA芯片的特定功能而提供的电压。

在确定了电源需求之后,就可以开始设计数字电源了。

首先是电源管理模块的设计。

电源管理模块通常由稳压器、开关电源和保护电路组成。

稳压器可以将输入的电压稳定在一个特定的数值,通常采用线性稳压器或者开关稳压器。

线性稳压器简单易用,但效率较低,而开关稳压器效率高但设计复杂。

开关电源则可以从外部电源或电池中获取电能,并将其转换为所需的核心电压、I/O电压和辅助电压。

保护电路则可以确保FPGA芯片在电源异常情况下不会受到损坏,通常包括过压保护、欠压保护和过流保护等功能。

其次是电源滤波模块的设计。

电源滤波模块主要包括滤波器和去耦电容。

滤波器可以消除电源中的高频噪声和杂散,确保电源的稳定性和干净度。

去耦电容则可以提供额外的电源储备,在FPGA芯片运行过程中吸收电源的瞬态波动。

最后是电源输出模块的设计。

电源输出模块通常包括电源连接器和电源指示灯。

电源连接器是FPGA芯片与电源管理模块之间的接口,通常采用插头或排针的形式。

基于FPGA的抢答器设计和实现抢答器在各类竞赛中的必备设备,有单路输入的,也有组输入方式,本设计以FPGA 为基础设计了有三组输入(每组三人),具有抢答计时控制,能够对各抢答小组成绩进行相应加减操作的通用型抢答器;现行的抢答器中主要有两种:小规模数字逻辑芯片译码器和触发器来做,另外一种用单片机来做;小规模数字逻辑电路比较复杂,用单片机来做随着抢答组数的增加有时候存在I/O 口不足的情况;本设计采用FPGA 来做增强了时序控制的灵活性,同时由于FPGA 的I/O 端口资源丰富,可以在本设计基础上稍加修改可以设计具有多组输入的抢答器。

功能描述本文设计了一个通用型电子抢答器:三个参赛队,每个队有三个成员,各自可手动按按钮申请抢答权;回到正确加1 分,回答错误减1 分,违规抢答减1分,不抢答不加分不扣分;用4 位LED 的左边2 位显示抢答组号及抢答计时时间,右边2 位显示相应组的成绩。

抢答器具体功能如下:1、可同时进行三组每个小组三人的抢答,用9 个按钮Group1_1,Group1_2,Group1_3,Group2_1,Group2_2,Group2_3,Group3_1,Group3_2,Group3_3 表示;2、设置一个抢答控制开关Start,该开关由主持人控制;只有当主持人按下开始键才能抢答;在按开始按钮前抢答属于违规;3、抢答器具有定时抢答功能,且一次抢答的时间设定为30 秒。

当主持人启动“开始”键后,用4 位LED 数码管左边两位显示30s 的倒计时;同时红色LED灯亮,表明可以抢答。

4、抢答器具有锁存和显示功能。

即选手按动按钮,锁存相应的组号,并在4 位LED 数码管的左边两位显示,同时用一个绿色LED 指示是否有选手抢答,如果是违规抢答还能用选手蜂鸣器报警提示。

抢答实行优先锁存,优先抢答选手的相应组号和成绩一直保持到下一轮抢答开始。

5、参赛选手在设定的时间内进行抢答,抢答有效,数码管左边两位显示”FX”,如果抢答违规则显示”XF”(其中X 表示组号1~3),并保持到下一轮抢答。

摘要随着半导体工艺技术的迅猛发展,可编程逻辑器件的集成度越来越高,FPGA中的逻辑资源也日益丰富,已达到百万门量级,这使得使用FPGA实现片上系统成为可能。

基于FPGA的片上系统设计方案具有开发周期短、设计成本低、软硬件在系统可编程、系统设计灵活、可裁减、可扩充、可升级等优点,正在成为电子系统设计的研究热点。

随着设计与制造技术的发展,集成电路设计从晶体管的集成发展到逻辑门的集成,现在又发展到IP的集成,即SOC设计技术。

SOC可以有效地降低电子信息系统产品的开发成本,缩短开发周期,提高产品的竞争力,是未来工业界将采用的最主要的产品开发方式。

FPGA将现代的VLSI逻辑集成的优点和可编程器件设计灵活,制作及上市快速的长处相结合,使设计者在FPGA开发系统软件的支持下,现场直接根据系统要求定义和修改其逻辑功能。

使一个包含数千个逻辑门的数字系统设计实现,采用FPGA技术,即可几天内完成。

本设计实现一种基于FPGA的SOPC解决方案,实现了系统的灵活性架构,以及参数化配置,便于系统的集成与设计修改,具有良好的可继承性与可移植性。

关键词:系统级芯片(片上系统);现场可编程门阵列;NiosⅡAbstractWith the rapid development of semiconductor technology,logic resources in FPGA have reached millions orders of magnitude,which make system-on-chip (SOC) based on FPGA has become possible. The design of SOC based on FPGA has many advantages,such as a short development cycle,low-cost,software and hardware in-system programmable,system design flexibility and can be trimmed,sealable,upgradeable,etc,Because of these,it has became a hot spot of research of electrical system design.With the design and manufacturing technology, integrated circuit design from transistors to integrated development of integrated logic gates, and now developed to the IP integration, that SOC design technology. SOC can effectively reduce the electronic information system product development costs, shorten development cycles, improve product's competitiveness, is the next most important industry will use methods of product development. FPAG the modern logic of integration of the advantages of VLSI and programmable device design flexibility, faster production and market strengths combined to enable FPGA designers to develop system software support, on-site directly from system requirements definition and change its logic function. Make a logic gate that contains thousands of digital system design and implementation, using FPGA technology can be completed within a few days.The Design and Implementation of FPGA-based SOPC solutions to achieve the flexibility of the system structure and parameters of configuration, ease of system integration and design changes, has a good inheritable and portability.Key words:SOC;FPGA;Nios Ⅱ目录摘要 (I)Abstract (II)1 绪论 (1)1.1 课题背景 (1)1.2目的及意义 (1)1.3国内外研究现状 (1)1.4论文章节安排 (2)2基于FPGA的SOC技术 (3)2.1 FPGA简介 (3)2.2 SOC概述 (7)2.3 SOPC概述 (8)2.4软核与硬核 (11)3 系统硬件设计 (14)3.1 QuartusⅡ简介 (14)3.2 SOPC Builder工具简介 (14)3.3嵌入式软核Nios II处理器 (15)3.4 Nios II CPU的搭建 (16)4 Nios ⅡIDE的软件设计 (22)4.1 新建软件工程 (22)4.2主程序设计 (23)4.3 UART串口 (24)4.4 LED控制 (26)结论 (29)致谢 (30)参考文献 (31)附录1:英文文献 (32)附录2:中文文献 (38)附录3:程序代码 (43)1 绪论1.1 课题背景EDA(Electronic Design Automation)技术是近几年迅速发展起来的计算机软件,硬件和微电子交叉的现代电子学科,涉及计算机操作系统、计算数学、电路理论和微电子学等领域,其内容广泛,综合性强。