quartus分享--SignalTap的使用方法

- 格式:docx

- 大小:613.30 KB

- 文档页数:6

Quartus II: SignalTap II Logic Analyzer的使用教程(基于quartus II 13.0)

1.点击Tools | SignalTap II Logic Analyzer

2.按照下图所设置的步骤进行设置:

添加实例名称,添加结点,设置采样时钟,设置采样深度,设置被测信号触发以及触发器模式,设置

3.新建实例并进行重命名如图:(该实例名称可以和工程中实例的名字相同)

4.为仿真实例添加结点,按软件提示新建结点

4.1打开结点查找器,将新建的实例的与工程中的信号结点绑定起来。

如图:点击1处设置过滤类型为前综合类型,点击2处的List,选择相应的结点。

4.2点击下图1导入结点,设置完成后,点击2处确定。

5.信号配置:

a)设置采样时钟:

点击1处,打开结点查找器,点击2搜索相应结点,并导入工程系统时钟,设置完

成后点击OK

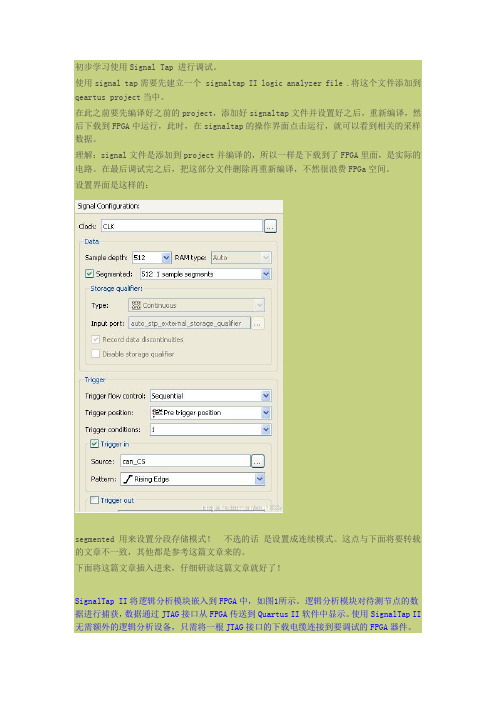

b)设置采样深度,以及信号触发模式以及触发器模式按照下图进行设置即可

6.所有设置完成后点击保存,

7.按照如图下步骤进行硬件配置以及下载,然后进行JTAG调试

点击2处设置JTAG连接器硬件,

点击3处进行FPGA芯片扫描

点击4处进行下载

点击1处进行调试,观察仿真结果

8.运行结果如图所示:

9.注意:断电之后拔掉JTAG。

静电可以击穿芯片。

初步学习使用Signal Tap 进行调试。

使用signal tap需要先建立一个 signaltap II logic analyzer file .将这个文件添加到qeartus project当中。

在此之前要先编译好之前的project,添加好signaltap文件并设置好之后,重新编译,然后下载到FPGA中运行,此时,在signaltap的操作界面点击运行,就可以看到相关的采样数据。

理解:signal文件是添加到project并编译的,所以一样是下载到了FPGA里面,是实际的电路。

在最后调试完之后,把这部分文件删除再重新编译,不然很浪费FPGa空间。

设置界面是这样的:segmented 用来设置分段存储模式!不选的话是设置成连续模式。

这点与下面将要转载的文章不一致,其他都是参考这篇文章来的。

下面将这篇文章插入进来,仔细研读这篇文章就好了!SignalTap II将逻辑分析模块嵌入到FPGA中,如图1所示。

逻辑分析模块对待测节点的数据进行捕获,数据通过JTAG接口从FPGA传送到Quartus II软件中显示。

使用SignalTap II 无需额外的逻辑分析设备,只需将一根JTAG接口的下载电缆连接到要调试的FPGA器件。

SignalTap II对FPGA的引脚和内部的连线信号进行捕获后,将数据存储在一定的RAM块中。

因此,需要用于捕获的采样时钟信号和保存被测信号的一定点数的RAM块。

使用SignalTap II的一般流程是:设计人员在完成设计并编译工程后,建立SignalTap II (.stp)文件并加入工程、配置STP文件、编译并下载设计到FPGA、在Quartus II软件中显示被测信号的波形、在测试完毕后将该逻辑分析仪从项目中删除。

以下描述设置SignalTap II 文件的基本流程:1.设置采样时钟。

采样时钟决定了显示信号波形的分辨率,它的频率要大于被测信号的最高频率,否则无法正确反映被测信号波形的变化。

SignalTapII 及SignalProbe 使用指南1.SignalTapII 支持器件及下载电缆SignalTapII 内嵌式规律需要占用ALMs/LEs 布线资源和RAM 采样存储资源,支持下面的器件系列:StratxiII、Stratix、StratixIIGX、StratixGX、CycloneII、Cyclone、APEXII、APEX20K/E/C、Excalibur 和Mercury。

SignalII 规律支持目前Altera 全部下载电缆,包括USB Blaster、ByteBlasterII、ByteBlasterMV 和MasterBlaster。

2.SignalTapII 工作流程及资源消耗○1配置ELA〔Embedded Logic Analyzer〕。

○2通过QuartusII软件完成布局布线,ELA下载至FPGA中。

○3ELA采样到内部触发信号。

○4ELA通过JTAG电路与QuartusII软件发生通信,以图形化的界面显示出来。

ELA 占用片内LE 资源由信号通道数及触发级数打算,占用片内RAM 资源由信号通道数及采样深度来打算。

Altera 建议选择选择通道数量和采样深度时要考虑二者之间的平衡,以免占用太多RAM 资源,影响原本的规律设计。

比方不推举同时使用1024 个最大通道数和128K 最大采样深度〔相当于消耗了32,768 个M4K 的资源〕。

下表给出了在Statix/Cyclone 器件中使用ELA 的资源占用状况。

8316 371 42632 566 773 981256 2900 4528 61568< 1 1416 6432 2416 64 256256 16 32 128 5123.SignalTapII 设计流程在设计中嵌入SignalTapII有两种方法:一是创立一个SignalTapII文件〔.stp〕,然后定义STP 文件的具体内容;二是用MegaWizard Plug-In Manager 建立并配置STP 文件,然后用MegaWizard 实例化一个HDL 输出模块。

SignalTapII简单使用小记Signal Tap II有助于观察逻辑内部信号行为,可使不借助外部设备进行设计调试。

(当然使用的前提条件是有硬件平台)Signal Tap II ELA 组成框图采样获得的数据会存储在器件的存储器块中,通过JTAG下载线可以把数据传回Quartus 中进行波形显示。

可以设置数据采集缓冲器(Buffers)的大小、数据采集方式和存储方式、以及此Buffer的存储器类型。

可以在一片FPGA上生成多个ELA,这一功能非常适合在设计中为每个时钟域配备一个分析仪。

ELA可以计算每个实例用到的逻辑资源和存储器资源,并显示在实例管理器中。

要使用Signal Tap II ELA,必须对其进行配置:1 设置采样时钟。

ELA只能在采样时钟的上升沿采样数据,可以使用设计中的任何信号作为采样时钟(推荐使用全局的与被测信号同步的非门控信号)。

采样时钟决定了信号波形的分辨率,它的频率要大于被测信号的最高频率。

2 设置被测信号。

可以分配两种信号(通过Node List信号设置触发条件):Pre-Synthesis:设计拟定之后,综合优化之前的信号,反映RTL 级信号。

(RTL Viewer)Post-fitting :物理综合优化和布局布线后的信号(Technical Map Viewer)为了可以使用增量编译,建议不要混合使用两种信号;若使用了预综合信号则要采取信号保留(Signal Preservation)措施。

不可测试引脚:Post-fit输出引脚、进位链信号、JTAG控制信号、ALTGXB宏功能信号、LVDS信号(串行/解串器块的数据输出)、DQ/DQS信号。

3 设置采样深度。

代表每个信号的采样数量,即采样Buffer大小。

还可以选择采样Buffer的RAM类型,如M4K、M512、M_RAM等。

被测信号波形的时间长度为t,则t = N × T. N为Buffer存储的采样点数(采样深度),T为采样时钟周期。

第10章SignalTapⅡ嵌入式逻辑分析仪的使用10.1 在设计中嵌入SignalTapⅡ逻辑分析仪10.2 在SOPC Builder中使用SignalTapⅡ逻辑分析仪10.3 在DSP Builder中使用SignalTapⅡ逻辑分析仪思考题10.1 在设计中嵌入SignalTapⅡ逻辑分析仪在设计中嵌入SignalTapⅡ逻辑分析仪有两种方法:第一种方法是建立一个SignalTapⅡ文件(.stp),然后定义STP文件的详细内容;第二种方法是用MegaWizard Plug-In Manager建立并配置STP文件,然后用MegaWizard实例化一个HDL输出模块。

图10.1给出用这两种方法建立和使用SignalTapⅡ逻辑分析仪的过程。

SignalTapMegaWizardQuartusSTPQuartus,/ 图10.1 SignalTapⅡ操作流程10.1.1 使用STP文件建立嵌入式逻辑分析仪1.创建STP文件STP文件包括SignalTapⅡ逻辑分析仪设置部分和捕获数据的查看、分析部分。

创建一个STP文件的步骤如下:(1) 在QuartusⅡ软件中,选择File→New命令。

(2) 在弹出的New对话框中,选择Other Files标签页,从中选择SignalTapⅡ File,如图10.2所示。

图10.2 新建一个STP文件(3) 点击OK按钮确定,一个新的SignalTapⅡ窗口如图10.3所示。

DataS etup图10.3 SignalTapⅡ窗口上面的操作也可以通过Tools→SignalTapⅡLogic Analyzer命令完成,这种方法也可以用来打开一个已经存在的STP文件。

2.设置采集时钟在使用SignalTapⅡ逻辑分析仪进行数据采集之前,首先应该设置采集时钟。

采集时钟在上升沿处采集数据。

设计者可以使用设计中的任意信号作为采集时钟,但Altera建议最好使用全局时钟,而不要使用门控时钟。

altera signaltap核例化与使用SignalTap是Altera公司提供的一个强大的逻辑分析工具。

它可以用于调试和分析FPGA设计中的信号。

SignalTap提供了FPGA内部信号的实时观察和记录功能,可以用于查看特定信号的波形和统计信息,从而有效地进行调试和分析。

为了方便使用SignalTap,首先需要对其进行核例化。

核例化是在设计中插入一个SignalTap模块,以便于对指定信号进行分析。

下面将详细介绍SignalTap的核例化和使用。

1.核例化SignalTap:a.打开Quartus Prime软件,在项目导航器中选择要核例化SignalTap的设计文件。

b.右键点击设计文件,选择“Start Analysis & Synthesis",进入设计的综合和分析设置。

c.在综合设置对话框中,选择“Add/Remove Assignments",在控制面板中选择“SignalTap II Logic Analyzer",点击“OK"。

d.在SignalTap Logic Analyzer对话框中,选择“Create a new SignalTap II instance"。

e.在SignalTap II Analyzer Instance对话框中,选择要观察的信号和模块,并设置时钟和采样点等参数。

点击“OK"保存设置。

f.回到设计窗口,编译设计文件,核例化SignalTap。

2. SignalTap使用:a.完成核例化后,可以打开SignalTap II Logic Analyzer的视图。

点击菜单栏上的“Tools"并选择“S ignalTap II Logic Analyzer",或者使用快捷键Ctrl+Alt+L。

b.在SignalTap II Logic Analyzer的视图中,可以选择要观察的信号,并设置触发条件和触发位置等参数。

Altera(现在由英特尔公司拥有)的SignalTap是一种用于逻辑分析和调试的IP核,用于FPGA设计。

它允许你在FPGA中捕获和分析信号以进行调试。

下面是关于如何实例化和使用Altera SignalTap IP核的一般步骤:1. **打开Quartus Prime**:首先,打开Altera的Quartus Prime集成开发环境(IDE)。

2. **创建一个工程**:创建一个新的FPGA工程或打开现有的工程。

3. **添加SignalTap IP核**:在Quartus Prime中,你可以通过以下步骤添加SignalTap IP 核:- 在"Project"菜单下,选择"Add/Remove MegaWizard Plug-In Manager"。

- 在"MegaWizard Plug-In Manager"对话框中,选择"SignalTap II"。

- 配置SignalTap II,选择你要捕获和分析的信号。

你可以选择要监视的信号,设置触发条件,以及其他配置选项。

4. **生成和编译设计**:确保你的设计和SignalTap IP核都已经添加到工程中,并生成和编译你的FPGA设计。

5. **配置SignalTap II**:在Quartus Prime中,选择"Tools" > "SignalTap II Logic Analyzer"以打开SignalTap II配置界面。

在此界面中,你可以完成以下操作:- 添加捕获点:选择要捕获的信号,并将它们添加到捕获点列表中。

- 配置触发条件:设置触发条件,以确定何时开始捕获信号。

- 配置存储深度:设置存储深度,以确定SignalTap II可以捕获多少时钟周期的数据。

- 配置触发操作:设置触发后要执行的操作,如停止或暂停捕获。

SignalTap的使用方法SignalTap是由Altera公司开发的一个在线、片内信号分析的工具,为设计开发者验证所用。

我们什么时候会用到signalTap呢?当代码经过仿真没有问题,但加载到FPGA电路板后,发现功能不正确时,我们就可以用signalTap工具进行分析,它的作用就类似于一个数字逻辑分析仪。

利用signaltap基本上可以代替数字逻辑分析仪了,它是quartus里最常用的工具,同学们必须熟练使用这个工具。

1.SignalTapII原理在使用signalTap前,我们先理解一下SignalTap的原理,这样就助于理解每个参数。

如下图所示,我们想观察一组信号,我们称之为“被测信号”(可以是多个),同时我们指定一个采样时钟。

现在我们想看这个被测信号,在其下降沿前后几个时钟内,被测信号的值是多少。

那么“下降沿”就是触发条件。

当满足触发条件时,signaltap会将触发条件前后,时钟上升沿时的所有信号值保存到一个RAM当中。

我们可以指定触发条件前后采多少个样点。

如果RAM比较大,那么可以保存的数据就比较多。

如果RAM比较小,那么保存的数据自然少。

(因此RAM大小决定了观察数据的多少)。

SignalTap将数据保存到RAM后,将读出RAM中的数据,然后逐个在显示器中显示出来(因此SignalTap看到的都是理想的,没有毛刺的信号)。

2.打开SignalTapII打开Quartus后,在菜单栏中,选择“Tools”->”SignalTal II Logic Analyzer”,就可以打开SignalTap工具。

如下图:3.界面介绍上面是SignalTap的界面,我们按照使用顺序简述地介绍每个部分功能。

红色标号1:下载线选择,点击setup选择硬件的USB接口红色标号2:硬件检测,扫描有没有FPGA硬件。

红色标号3:选择工程配置文件。

可以将综合后的sof文件加载进来红色标号4:正式加载sof工程文件红色标号5:设置采样时钟红色标号6:设置RAM的大小红色标号7:选择要观察的信号,并且设置触发条件红色标号8:开始运行,等待触发条件满足后显示波形红色标号9:这里可以观察FPGA资源使用情况。

Quartus Ⅱ应用深入(SignalTap Ⅱ的使用方法) 一、新建项目:二、新建Verilog文件:三、输入代码:module CNT2LED(CLK,RST,EN,LOAD,DATA,COUT,LED,DOUT,SCL); input CLK,RST,EN,LOAD;input[3:0] DATA;output COUT,SCL;output[3:0] DOUT;output[6:0] LED;wire[6:0] led;CNT10 inst(.CLK(CLK),.RST(RST),.EN(EN),.LOAD(LOAD),.DATA(DATA),.COUT(COUT),.DOUT(DOUT));DECL7S inst1(.A(DOUT),.LED7S(led));assign LED=~led;assign SCL=0;endmodule保存CNT2LEDmodule CNT10 (CLK,RST,EN,LOAD,COUT,DOUT,DATA);input CLK;input EN;input RST ;input LOAD;input [3:0] DATA;output [3:0] DOUT;output COUT ;reg [3:0] Q1;reg COUT;assign DOUT = Q1;always @(posedge CLK or negedge RST)beginif(!RST) Q1<= 4'b0000;else if(!EN)beginif(!LOAD) Q1<= DATA;else if(Q1<9) Q1<= Q1+1;else Q1<= 4'b0000;endendalways @(Q1)if (Q1==4'h9) COUT = 1'b1;else COUT = 1'b0;endmodulemodule DECL7S(A,LED7S);input[3:0] A;output[6:0] LED7S;reg [6:0] LED7S;always@(A)case(A)4'b0000: LED7S<=7'b0111111;4'b0001: LED7S<=7'b0000110;4'b0010: LED7S<=7'b1011011;4'b0011: LED7S<=7'b1001111;4'b0100: LED7S<=7'b1100110;4'b0101: LED7S<=7'b1101101;4'b0110: LED7S<=7'b1111101;4'b0111: LED7S<=7'b0000111;4'b1000: LED7S<=7'b1111111;4'b1001: LED7S<=7'b1101111;4'b1010: LED7S<=7'b1110111;4'b1011: LED7S<=7'b1111100;4'b1100: LED7S<=7'b0111001;4'b1101: LED7S<=7'b1011110;4'b1110: LED7S<=7'b1111001;4'b1111: LED7S<=7'b1110001;default: LED7S<=7'b0111111;endcaseendmodule四、输完代码后编译:查错改错,通过后可进行一次全编译,之后进行管脚分配五、管脚分配:查电路原理图分配脚:放大全编译,出现错误Error: Can't place multiple pins assigned to pin location Pin_101(IOPAD_X34_Y18_N21)Info: Pin LED[5] is assigned to pin location Pin_101(IOPAD_X34_Y18_N21)Info: Pin ~ALTERA_nCEO~ is assigned to pin location Pin_101(IOPAD_X34_Y18_N21)原因:101引脚是一个多功能管脚(multiple pin),可以当普通IO连LED[5]来用也可以做nCEO,nCEO是默认功能,这里要用它做普通IO连LED[5],需要设置一下。

【主题】Altera SignalTap核例化与使用【内容】一、Altera SignalTap核例化简介Altera SignalTap是一种用于时序分析和信号调试的FPGA核例化工具。

它可以帮助工程师在FPGA设计中实时监测内部信号的变化,并且能够捕获和显示信号波形,方便分析与调试。

Altera SignalTap核例化提供了丰富的功能和灵活的设置,是FPGA设计调试的重要利器。

二、Altera SignalTap核例化使用步骤1. 设置SignalTap核例化在Quartus Prime软件中打开你的FPGA工程。

在项目导航器中右键点击你的设计文件,选择"Add/Remove Megawizard Plug-In Manager",然后在窗口中选择"SignalTap II Logic Analyzer"插件。

在Quartus Prime的菜单栏中选择"Tools" -> "SignalTap II Logic Analyzer",打开SignalTap II的设置界面。

在这里可以添加需要监测的信号、设置触发条件等。

2. 编译工程完成SignalTap核例化的设置后,需要重新编译你的FPGA工程,以便将SignalTap插入到FPGA中。

在Quartus Prime软件中选择"Processing" -> "Start Compilation",等待编译完成。

3. 下载到FPGA编译完成后,需要将设计下载到FPGA中。

在Quartus Prime软件中选择"Tools" -> "Programmer",选择你的FPGA芯片类型和连接方式,然后点击"Start"按钮下载到FPGA。

4. 运行SignalTap核例化下载完成后,在Quartus Prime软件中选择"Tools" -> "SignalTap II Logic Analyzer",打开SignalTap II的运行界面。

SignalTap的使用方法

SignalTap是由Altera公司开发的一个在线、片内信号分析的工具,为设计开发者验证所用。

我们什么时候会用到signalTap呢?当代码经过仿真没有问题,但加载到FPGA电路板后,发现功能不正确时,我们就可以用signalTap工具进行分析,它的作用就类似于一个数字逻辑分析仪。

利用signaltap基本上可以代替数字逻辑分析仪了,它是quartus里最常用的工具,同学们必须熟练使用这个工具。

1.SignalTapII原理

在使用signalTap前,我们先理解一下SignalTap的原理,这样就助于理解每个参数。

如下图所示,我们想观察一组信号,我们称之为“被测信号”(可以是多个),同时我们指定一个采样时钟。

现在我们想看这个被测信号,在其下降沿前后几个时钟内,被测信号的值是多少。

那么“下降沿”就是触发条件。

当满足触发条件时,signaltap会将触发条件前后,时钟上升沿时的所有信号值保存到一个RAM当中。

我们可以指定触发条件前后采多少个样点。

如果RAM比较大,那么可以保存的数据就比较多。

如果RAM比较小,那么保存的数据自然少。

(因此RAM大小决定了观察数据的多少)。

SignalTap将数据保存到RAM后,将读出RAM中的数据,然后逐个在显示器中显示出来(因此SignalTap看到的都是理想的,没有毛刺的信号)。

2.打开SignalTapII

打开Quartus后,在菜单栏中,选择“Tools”->”SignalTal II Logic Analyzer”,就可以打开

SignalTap工具。

如下图:

3.界面介绍

上面是SignalTap的界面,我们按照使用顺序简述地介绍每个部分功能。

红色标号1:下载线选择,点击setup选择硬件的USB接口

红色标号2:硬件检测,扫描有没有FPGA硬件。

红色标号3:选择工程配置文件。

可以将综合后的sof文件加载进来

红色标号4:正式加载sof工程文件

红色标号5:设置采样时钟

红色标号6:设置RAM的大小

红色标号7:选择要观察的信号,并且设置触发条件

红色标号8:开始运行,等待触发条件满足后显示波形

红色标号9:这里可以观察FPGA资源使用情况。

如果资源多于FPGA本身的资源,综合时会报错。

4.SignalTapII使用步骤

a选择下载线、fpga芯片型号、工程配置文件

b设置采样时钟、采样深度

这里我们选择内部pll的输出信号c1作为采样时钟,注意采样时钟不一定是工程里的时钟,内部任何信号都可以是采样时钟。

这里我们将采样深度设置为128个。

也就是我们总共能看到128采样点的数据。

c选择采样信号

在setup窗口中,双击空白地方,弹出如下界面

红色框是选择哪个阶段的信号,例如是综合前、综合后等,因为综合时会优化,有些信号可能就找不到了。

我们一般选择pre-synthesis或Design Entry(all name)。

在Nodes Found选择我们要观察的信号,添加到右边框即可。

我们这里选择key_col和rst_n信号来观察。

d设置触发条件

选择好信号后,设置触发条件。

同学们可以观察到trigger Conditions一列,key_col的值为xh,rst_n的值为don’t care。

这意味着只要一观察,立刻捕获信号。

在trigger Conditions一列中,右击rst_n那个位置,将有6个选择。

don’t care:表示不关心,也就是说这个信号的值不影响触发条件。

Low :表示为0时触发,也就是说触发条件包括该信号的值为0.

Falling Edge:下降沿触发。

即该信号的下降沿是触发条件

Rising Edge:上升沿触发。

High:给为1时触发

Either Edge:双沿触发,即有变化时触发。

以上是对一个信号的触发。

如果触发条件包含多个信号,如下图所示:

此时的触发条件是:当rst_n为上升沿并且key_col为F。

注意,这里是“与”的关系,很多同学会误认为是“或”的关系。

e点击“Run Analysis”按钮,开始抓波形

f观看结果

如果触发条件成立,则可在Data窗口观察到采样波形,此处是某一工程的采样结果,可以看到,其与modelsim波形是很相似的。

点击波形,则可以放大波形观看;右击波形,则是缩小波形。

SignalTap工具的使用方法就介绍到这里,接下来明德扬的点拨FPGA课程提供了几个SignalTap的练习,同学们通过练习熟悉掌握SignalTap。