第10章_数字系统设计(1)

- 格式:ppt

- 大小:525.00 KB

- 文档页数:49

verilog数字系统设计教程习题答案第二章1.Verilog HDL 既是一种行为描述语言,也是一种结构描述语言。

如果按照一定的规则和风格编写代码,就可以将功能行为模块通过工具自动转化为门级互联的结构模块。

这意味着利用Verilog语言所提供的功能,就可以构造一个模块间的清晰结构来描述复杂的大型设计,并对所需的逻辑电路进行严格的设计。

2.模块的基本结构由关键词module和endmodule构成。

3.一个复杂电路系统的完整Verilog HDL模型是由若干个Verilog HDL模块构成的,每一个模块又可以由若干个子模块构成。

其中有些模块需要综合成具体电路,而有些模块只是与用户所设计的模块交互的现存电路或激励信号源。

利用Verilog HDL语言结构所提供的这种功能就可以构造一个模块间的清晰层次结构来描述极其复杂的大型设计,并对所作设计的逻辑电路进行严格的验证。

4.Verilog HDL和VHDL作为描述硬件电路设计的语言,其共同的特点在于:能形式化地抽象表示电路的结构和行为、支持逻辑设计中层次与领域的描述、可借用高级语言的精巧结构来简化电路的描述、具有电路仿真与验证机制以保证设计的正确性、支持电路描述由高层到低层的综合转换、硬件描述与实现工艺无关(有关工艺参数可通过语言提供的属性包括进去)、便于文档管理、易于理解和设计重用。

5.不是6.将用行为和功能层次表达的电子系统转换为低层次的便于具体实现的模块组合装配的过程。

7.综合工具可以把HDL变成门级网表。

这方面Synopsys工具占有较大的优势,它的Design Compile是作为一个综合的工业标准,它还有另外一个产品叫Behavior Compiler,可以提供更高级的综合。

另外最近美国又出了一个软件叫Ambit,据说比Synopsys的软件更有效,可以综合50万门的电路,速度更快。

今年初Ambit被Cadence公司收购,为此Cadence 放弃了它原来的综合软件Synergy。

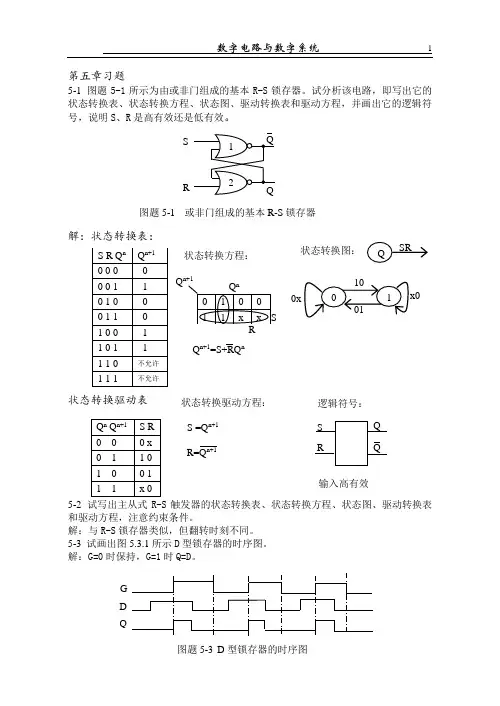

王毓银数字电路逻辑设计

《数字电路逻辑设计》是王毓银编著的普通高等教育“十一五”国家级规划教材,全书共分为 10 章,主要内容包括数字逻辑基础、逻辑门电路、组合逻辑电路、时序逻辑电路、半导体存储器和可编程逻辑器件、硬件描述语言、脉冲波形的产生与变换、数模和模数转换器、数字系统设计等。

本书以数字逻辑电路的设计为主线,突出了中大规模集成电路在数字系统设计中的重要地位,在内容取舍和编排上进行了新的尝试,将数字逻辑基础知识、中大规模集成电路的原理及应用与数字系统设计有机地结合在一起,使读者能够建立系统的概念。

本书可作为高等院校电气信息类、仪器仪表类、电子信息科学类等专业“数字电路”课程的教材,也可供相关工程技术人员参考。

数字系统设计hdl课后答案【篇一:数字系统设计与verilog hdl】ss=txt>(复习)eda(electronic design automation)就是以计算机为工作平台,以eda软件工具为开发环境,以pld器件或者asic专用集成电路为目标器件设计实现电路系统的一种技术。

1.电子cad(computer aided design)2.电子cae(computer aided engineering)3.eda(electronic design automation)eda技术及其发展p2eda技术的应用范畴1.3 数字系统设计的流程基于fpga/cpld的数字系统设计流程1. 原理图输入(schematic diagrams )2、硬件描述语言 (hdl文本输入)设计输入硬件描述语言与软件编程语言有本质的区别综合(synthesis)将较高层次的设计描述自动转化为较低层次描述的过程◆行为综合:从算法表示、行为描述转换到寄存器传输级(rtl)◆逻辑综合:rtl级描述转换到逻辑门级(包括触发器)◆版图综合或结构综合:从逻辑门表示转换到版图表示,或转换到pld器件的配置网表表示综合器是能自动实现上述转换的软件工具,是能将原理图或hdl语言描述的电路功能转化为具体电路网表的工具适配适配器也称为结构综合器,它的功能是将由综合器产生的网表文件配置于指定的目标器件中,并产生最终的可下载文件对cpld器件而言,产生熔丝图文件,即jedec文件;对fpga器件则产生bitstream位流数据文件p8仿真(simulation)功能仿真(function simulation)时序仿真(timing simulation)仿真是对所设计电路的功能的验证p9编程(program)把适配后生成的编程文件装入到pld器件中的过程,或称为下载。

通常将对基于eeprom工艺的非易失结构pld器件的下载称为编程(program),将基于sram工艺结构的pld器件的下载称为配置(configure)。

第七章 可编程数字系统设计基础在前面的章节里,我们所有的实验都是基于这样一个观点,即将一个数字系统划分成合适利用已有的中小规模数字集成电路的功能的模块,然后将这些集成电路通过外部引线连接起来。

从本章开始我们将研究用可编程逻辑器件(PLD/FPGA)来进行数字系统设计。

可编程逻辑器件是一种大规模的集成电路,其内部预置了大量易于实现各种逻辑函数的结构,同时还有一些用来保持信息或控制连接的特殊结构,这些保持的信息或连接确定了器件实现的实际逻辑功能,当改变这些信息或连接时器件的功能也将随之改变。

可编程逻辑器件的设计过程和传统的中小规模数字电路设计也不一样,可编程数字系统,无论是CPLD还是FPGA器件都需要利用软件工具来进行设计。

可编程数字系统设计总体上一般可以分为设计输入、项目处理、设计校验和器件编程这四个主要过程如图7.1.1所示。

在本章中我们将一个简单的模60BCD计数器为例,说明可编程数字系统设计的基本流程、概念和方法,掌握Quartus II软件的基本功能和操作,了解原理图输入方式的设计全过程。

7.1 设计项目输入7.1.1 概述设计输入是设计者对系统要实现的逻辑功能进行描述的过程。

设计输入有多种表达方式,常用的有原理图输入、硬件描述语言输入、网表输入以及混合输入这四种。

1、原理图输入:原理图设计输入方式是利用软件提供的各种原理图库,采用画图的方式进行设计输入。

这是一种最为简单和直观的输入方式。

原理图输入方式的效率比较低,一般只用于小规模系统设计,或用于在顶层拼接各个已设计完成的电路子模块。

2、硬件描述语言:这种设计输入方式是通过文本编辑器,用VHDL、Verilog或AHDL等硬件描述语言进行设计输入。

采用语言描述的优点是效率较高,结果容易仿真,信号观察方便,在不同的设计输入库之间转换方便,适用于大规模数字系统的设计。

但语言输入必须依赖综合器,只有好的综合器才能把语言综合成优化的电路。

3、网表输入现代可编程数字系统设计工具都提供了和其它第三方EDA工具相连接的接口。