第7章 组合逻辑电路的设计

- 格式:ppt

- 大小:971.50 KB

- 文档页数:58

实验三组合逻辑电路的设计组合逻辑电路是由与门、或门、非门等基本逻辑门组成的电路,其输出取决于输入信号的组合方式。

本实验旨在通过设计一个具体的组合逻辑电路,来强化学生对组合逻辑电路的理解和应用能力。

一、实验目的1.掌握组合逻辑电路的基本原理和设计方法;3.进一步理解与门、或门、非门等基本逻辑门的逻辑运算。

二、实验器材1.教学实验箱;2.相关实验电路元器件。

三、实验内容1.根据给定的逻辑功能要求,设计一个组合逻辑电路;2.使用门电路组合搭建所设计的组合逻辑电路;3.利用数字电路实验箱进行电路的搭建和测试;4.验证电路的功能是否符合设计要求。

四、实验步骤1.确定逻辑功能要求。

在本实验中,我们以设计一个4位二进制加法器为例。

4位二进制加法器是由4个全加器和一个或门组成的。

全加器的功能是将三位输入(被加数、加数和进位)相加得到两位输出(和和进位)。

2.进行真值表的列写和逻辑方程的列写。

为了完成4位二进制加法器的设计,我们首先需要根据功能要求列写真值表,包括所有的输入和输出组合。

然后,我们可以通过观察真值表,得出逻辑方程,并将其转化为门电路的连接方式。

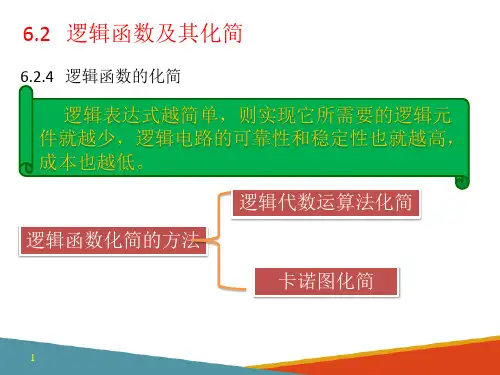

3.根据真值表和逻辑方程进行卡诺图化简。

卡诺图是一种用于化简逻辑方程的方法。

通过将逻辑方程的输入和输出用二进制表示,在卡诺图上标记出函数值为1的格子,然后将格子组合成最简化的表达式。

在本实验中,通过化简后的逻辑方程,我们可以确定需要使用的与门、或门、非门的数量和连接方式。

根据实验器材的要求,选择相应的门电路元器件进行电路的搭建。

5.利用数字电路实验箱进行电路的搭建和测试。

根据门电路的设计,使用数字电路实验箱中的元器件进行电路的搭建。

搭建完成后,仔细检查电路连接是否正确,确保没有接错导线或插错元器件。

6.验证电路的功能是否符合设计要求。

根据真值表的结果,对经过测试的电路进行验证。

观察输出是否符合预期,如果输出结果与设计要求一致,则说明电路的功能实现正确。

五、实验注意事项1.在进行实验之前,应仔细阅读实验内容和操作步骤,理解实验的目的和要求;2.在进行电路连接时,应注意电路元器件的极性和连接方式,确保电路连接正确;3.在进行电路测试时,应注意接线的稳固性和安全性,避免触电事故的发生;4.实验结束后,应及时关闭电源,避免给他人和设备带来危险。

《组合逻辑电路》公开课教案第一章:组合逻辑电路概述1.1 教学目标让学生了解组合逻辑电路的定义和特点使学生掌握组合逻辑电路的基本构成要素培养学生理解组合逻辑电路在数字电路中的应用1.2 教学内容组合逻辑电路的概念组合逻辑电路的特点组合逻辑电路的基本构成要素组合逻辑电路的应用1.3 教学方法采用讲授法,讲解组合逻辑电路的基本概念和特点采用案例分析法,分析组合逻辑电路的应用实例采用互动讨论法,引导学生探讨组合逻辑电路的构成要素1.4 教学准备教案、PPT、教学设备组合逻辑电路的相关案例资料1.5 教学过程1.5.1 导入利用生活中的实例引入组合逻辑电路的概念1.5.2 讲解讲解组合逻辑电路的定义和特点讲解组合逻辑电路的基本构成要素1.5.3 案例分析分析组合逻辑电路的应用实例1.5.4 互动讨论引导学生探讨组合逻辑电路的构成要素第二章:组合逻辑电路的设计方法2.1 教学目标让学生掌握组合逻辑电路的设计方法培养学生运用设计方法解决实际问题的能力2.2 教学内容组合逻辑电路的设计方法组合逻辑电路设计实例2.3 教学方法采用讲授法,讲解组合逻辑电路的设计方法采用案例分析法,分析组合逻辑电路设计实例采用互动讨论法,引导学生探讨设计方法的应用2.4 教学准备教案、PPT、教学设备组合逻辑电路设计的相关案例资料2.5 教学过程2.5.1 导入复习组合逻辑电路的概念,引出设计方法的话题2.5.2 讲解讲解组合逻辑电路的设计方法2.5.3 案例分析分析组合逻辑电路设计实例2.5.4 互动讨论引导学生探讨设计方法的应用第三章:组合逻辑电路的仿真与测试3.1 教学目标让学生掌握组合逻辑电路的仿真与测试方法培养学生运用仿真与测试方法诊断和优化电路的能力3.2 教学内容组合逻辑电路的仿真方法组合逻辑电路的测试方法组合逻辑电路仿真与测试实例3.3 教学方法采用讲授法,讲解组合逻辑电路的仿真与测试方法采用案例分析法,分析组合逻辑电路仿真与测试实例采用互动讨论法,引导学生探讨仿真与测试方法的应用3.4 教学准备教案、PPT、教学设备组合逻辑电路仿真与测试的相关案例资料3.5 教学过程3.5.1 导入复习组合逻辑电路的设计方法,引出仿真与测试的话题3.5.2 讲解讲解组合逻辑电路的仿真方法讲解组合逻辑电路的测试方法3.5.3 案例分析分析组合逻辑电路仿真与测试实例3.5.4 互动讨论引导学生探讨仿真与测试方法的应用第四章:组合逻辑电路的应用实例4.1 教学目标让学生了解组合逻辑电路在实际应用中的典型实例培养学生运用组合逻辑电路解决实际问题的能力4.2 教学内容组合逻辑电路的应用实例4.3 教学方法采用讲授法,讲解组合逻辑电路的应用实例采用案例分析法,分析组合逻辑电路应用实例采用互动讨论法,引导学生探讨应用实例的设计与实现4.4 教学准备教案、PPT、教学设备组合逻辑电路应用实例的相关资料4.5 教学过程4.5.1 导入复习组合逻辑电路的仿真与测试,引出应用实例的话题4.5.2 讲解讲解组合逻辑电路的应用实例4.5第五章:组合逻辑电路的综合设计实例5.1 教学目标让学生掌握组合逻辑电路的综合设计方法培养学生运用综合设计方法解决实际问题的能力5.2 教学内容组合逻辑电路的综合设计方法组合逻辑电路综合设计实例5.3 教学方法采用讲授法,讲解组合逻辑电路的综合设计方法采用案例分析法,分析组合逻辑电路综合设计实例采用互动讨论法,引导学生探讨综合设计方法的应用5.4 教学准备教案、PPT、教学设备组合逻辑电路综合设计的相关案例资料5.5 教学过程5.5.1 导入复习组合逻辑电路的应用实例,引出综合设计的话题5.5.2 讲解讲解组合逻辑电路的综合设计方法5.5.3 案例分析分析组合逻辑电路综合设计实例5.5.4 互动讨论引导学生探讨综合设计方法的应用第六章:组合逻辑电路的优化6.1 教学目标让学生了解组合逻辑电路的优化方法培养学生运用优化方法提高电路性能的能力6.2 教学内容组合逻辑电路的优化方法组合逻辑电路优化实例6.3 教学方法采用讲授法,讲解组合逻辑电路的优化方法采用案例分析法,分析组合逻辑电路优化实例采用互动讨论法,引导学生探讨优化方法的应用6.4 教学准备教案、PPT、教学设备组合逻辑电路优化的相关案例资料6.5 教学过程6.5.1 导入复习组合逻辑电路的综合设计,引出优化的话题6.5.2 讲解讲解组合逻辑电路的优化方法6.5.3 案例分析分析组合逻辑电路优化实例6.5.4 互动讨论引导学生探讨优化方法的应用第七章:组合逻辑电路的troubleshooting 与维护7.1 教学目标让学生掌握组合逻辑电路的troubleshooting 与维护方法培养学生运用troubleshooting 与维护方法解决实际问题的能力7.2 教学内容组合逻辑电路的troubleshooting 方法组合逻辑电路的维护方法组合逻辑电路troubleshooting 与维护实例7.3 教学方法采用讲授法,讲解组合逻辑电路的troubleshooting 与维护方法采用案例分析法,分析组合逻辑电路troubleshooting 与维护实例采用互动讨论法,引导学生探讨troubleshooting 与维护方法的应用7.4 教学准备教案、PPT、教学设备组合逻辑电路troubleshooting 与维护的相关案例资料7.5 教学过程7.5.1 导入复习组合逻辑电路的优化,引出troubleshooting 与维护的话题7.5.2 讲解讲解组合逻辑电路的troubleshooting 方法讲解组合逻辑电路的维护方法7.5.3 案例分析分析组合逻辑电路troubleshooting 与维护实例7.5.4 互动讨论引导学生探讨troubleshooting 与维护方法的应用第八章:组合逻辑电路在现代电路中的应用8.1 教学目标让学生了解组合逻辑电路在现代电路中的应用领域培养学生运用组合逻辑电路解决现代电路问题的能力8.2 教学内容组合逻辑电路在现代电路中的应用领域组合逻辑电路在现代电路中的应用实例8.3 教学方法采用讲授法,讲解组合逻辑电路在现代电路中的应用领域采用案例分析法,分析组合逻辑电路在现代电路中的应用实例采用互动讨论法,引导学生探讨组合逻辑电路在现代电路中的应用8.4 教学准备教案、PPT、教学设备组合逻辑电路在现代电路中的应用领域的相关资料8.5 教学过程8.5.1 导入复习组合逻辑电路的troubleshooting 与维护,引出现代电路应用重点和难点解析1. 教学内容的选取与编排:确保教学内容既能够覆盖组合逻辑电路的基础知识,又能够结合实例深入讲解,使学生能够理解并应用所学知识。

组合逻辑电路设计实验报告实验名称: 组合逻辑电路设计实验报告摘要:本实验旨在通过设计和实现不同的组合逻辑电路,加深对数字电路和逻辑门的理解,并通过实际操作提升实验者的动手能力和解决问题的能力。

实验中,我们掌握了组合逻辑电路的基本原理,并成功设计了多个功能不同的组合逻辑电路。

引言:组合逻辑电路是由多个逻辑门组成的电路,其输出只取决于当前的输入。

在数字电路中,组合逻辑电路是最基本的构建模块,常用于实现各种逻辑功能,如加法器、减法器、多路选择器等。

因此,掌握组合逻辑电路的设计和实现技巧对于数字电路的学习至关重要。

实验过程:1. 实验准备:在开始实验前,我们先了解了基本的逻辑门,如与门、或门、非门等,并根据实验要求准备所需的元件和工具。

2. 设计逻辑电路:根据实验要求,我们开始设计所需的组合逻辑电路。

首先,我们根据真值表确定逻辑功能,并使用布尔代数化简或卡诺图法简化逻辑表达式。

然后,我们根据简化后的逻辑表达式,逐步设计逻辑电路的电路图。

3. 仿真验证:在进行实际的电路搭建之前,我们使用仿真软件对所设计的电路进行验证。

通过输入各种组合的逻辑输入,观察输出是否符合预期的逻辑功能。

4. 实际搭建:在通过仿真验证后,我们开始使用实际的电子元件搭建电路。

根据电路图,按照正确的连接方式依次连接各个元件,并进行适当的调试和检查,确保电路的正常工作。

5. 测试与分析:完成电路搭建后,我们对电路进行了进一步的测试。

通过输入各种组合的逻辑输入,观察输出是否符合预期的逻辑功能。

同时,我们还对电路的响应时间、功耗等性能进行了测试和分析。

6. 总结与改进:根据实验得到的结果,我们对实验进行了总结和改进。

总结了实验中遇到的问题和解决方法,并提出了对电路性能和设计方法的改进建议。

结论:通过本次实验,我们深入了解了组合逻辑电路的设计和实现过程。

通过实际搭建和测试,我们成功实现了多个功能不同的组合逻辑电路,并对电路的性能进行了评估。

实验过程中,我们不仅提升了动手能力和解决问题的能力,也加深了对数字电路和逻辑门的理解。

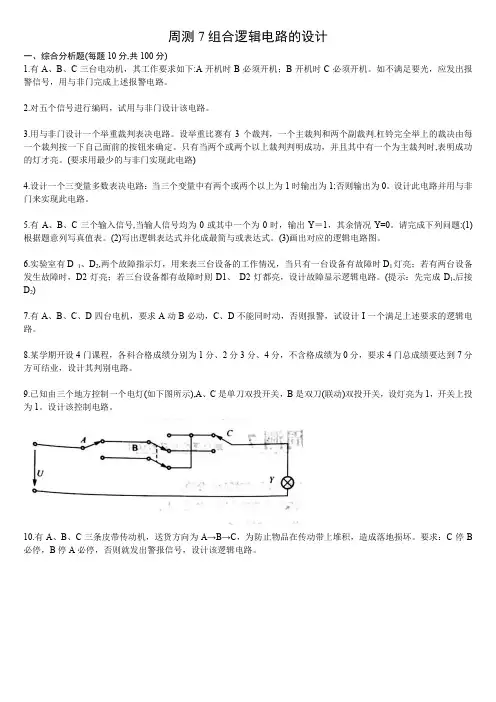

周测7组合逻辑电路的设计一、综合分析题(每题10分,共100分)1.有A、B、C三台电动机,其工作要求如下:A开机时B必须开机;B开机时C必须开机。

如不满足要光,应发出报警信号,用与非门完成上述报警电路。

2.对五个信号进行编码,试用与非门设计该电路。

3.用与非门设计一个举重裁判表决电路。

设举重比赛有3个裁判,一个主裁判和两个副裁判.杠铃完全举上的裁决由每一个裁判按一下自己面前的按钮来确定。

只有当两个或两个以上裁判判明成功,并且其中有一个为主裁判时,表明成功的灯才亮。

(要求用最少的与非门实现此电路)4.设计一个三变量多数表决电路:当三个变量中有两个或两个以上为1时输出为1;否则输出为0。

设计此电路并用与非门来实现此电路。

5.有A、B、C三个输入信号,当输人信号均为0或其中一个为0时,输出Y=1,其余情况Y=0。

请完成下列问题:(1)根据题意列写真值表。

(2)写出逻辑表达式并化成最简与或表达式。

(3)画出对应的逻辑电路图。

6.实验室有D 1、D2,两个故障指示灯,用来表三台设备的工作情况,当只有一台设备有故障时D1灯亮;若有两台设备发生故障时,D2灯亮;若三台设备都有故障时则D1、D2灯都亮,设计故障显示逻辑电路。

(提示:先完成D1,后接D2)7.有A、B、C、D四台电机,要求A动B必动,C、D不能同时动,否则报警,试设计I一个满足上述要求的逻辑电路。

8.某学期开设4门课程,各科合格成绩分别为1分、2分3分、4分,不含格成绩为0分,要求4门总成绩要达到7分方可结业,设计其判别电路。

9.已知由三个地方控制一个电灯(如下图所示),A、C是单刀双投开关,B是双刀(联动)双投开关,设灯亮为1,开关上投为1。

设计该控制电路。

10.有A、B、C三条皮带传动机,送货方向为A→B→C,为防止物品在传动带上堆积,造成落地损坏。

要求:C停B 必停,B停A必停,否则就发出警报信号,设计该逻辑电路。

实验一组合逻辑电路的设计班级:11电信1班姓名:张斌学号:3111003113一、实验目的:1.熟悉QuartusⅡ的VHDL文本设计流程全过程,学习简单组合电路的设计、多层次电路设计、仿真和硬件测试。

2.加深FPGA\CPLD设计的过程,并比较原理图输入和文本输入的优劣。

二、实验的硬件要求:1.GW48EDA/SOPC+PK2实验系统。

三、实验内容及预习要求:1.首先利用QuartusⅡ完成2选1多路选择器(如图S1-1)的文本编辑输入(mux21a.vhd)和仿真测试等步骤。

最后在实验系统上进行硬件测试,验证本项设计的功能。

图S1-12.将此多路选择器看成是一个元件mux21a,利用原理图输出法完成图s1-2,并将此文件放在同一目录中。

图s1-2编译、综合、仿真本例程,并对其仿真波形作出分析说明。

最后在实验系统上进行硬件测试,验证本项设计的功能。

3.以1位二进制全加器为基本元件,用例化语句写出8位并行二进制全加器的顶层文件,编译、综合、仿真本例程,并对其仿真波形作出分析说明。

最后在实验系统上进行硬件测试,验证本项设计的功能。

4.七段数码管译码器(Decoder)七段数码管译码器(Decoder)的输入为4位二进制代码,输出为7个表征七段数码管代码的状态信号。

下面为一个七段数码管译码器的VHDL源代码模型:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY display ISPORT(A:IN STD_LOGIC_VECTOR(3 DOWNTO 0);LED7S:OUT STD_LOGIC_VECTOR(6 DOWNTO 0));END;ARCHITECTURE ONE OF display ISBEGINPROCESS(A)BEGINCASE A ISWHEN "0000"=>LED7S<="0111111";--X"3F"->0WHEN "0001"=>LED7S<="0000110";--X"06"->1WHEN "0010"=>LED7S<="1011011";--X"5B"->2WHEN "0011"=>LED7S<="1001111";--X"4F"->3WHEN "0100"=>LED7S<="1100110";--X"66"->4WHEN "0101"=>LED7S<="1101101";--X"6D"->5WHEN "0110"=>LED7S<="1111101";--X"7D"->6WHEN "0111"=>LED7S<="0000111";--X"07"->7WHEN "1000"=>LED7S<="1111111";--X"7F"->8WHEN "1001"=>LED7S<="1101111";--X"6F"->9WHEN "1010"=>LED7S<="1110111";--X"77"->10WHEN "1011"=>LED7S<="1111100";--X"7C"->11WHEN "1100"=>LED7S<="0111001";--X"39"->12WHEN "1101"=>LED7S<="1011110";--X"5E"->13WHEN "1110"=>LED7S<="1111001";--X"79"->14WHEN "1111"=>LED7S<="1110001";--X"71"->15WHEN OTHERS=>NULL;END CASE;END PROCESS;END;编译、综合、仿真本例程,并对其仿真波形作出分析说明。

实验一 组合逻辑电路的设计一、实验目的:1、 掌握组合逻辑电路的设计方法。

2、 掌握组合逻辑电路的静态测试方法。

3、 加深FPGA 设计的过程,并比较原理图输入和文本输入的优劣。

4、 理解“毛刺”产生的原因及如何消除其影响。

5、 理解组合逻辑电路的特点。

二、实验的硬件要求:1、 EDA/SOPC 实验箱。

2、 计算机。

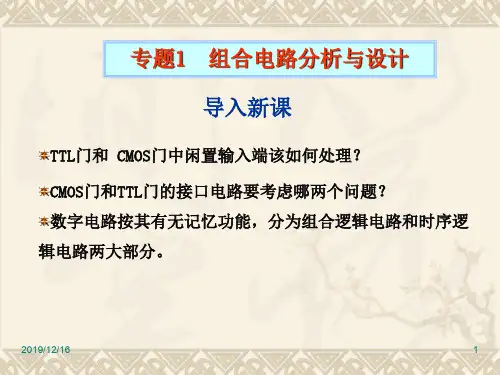

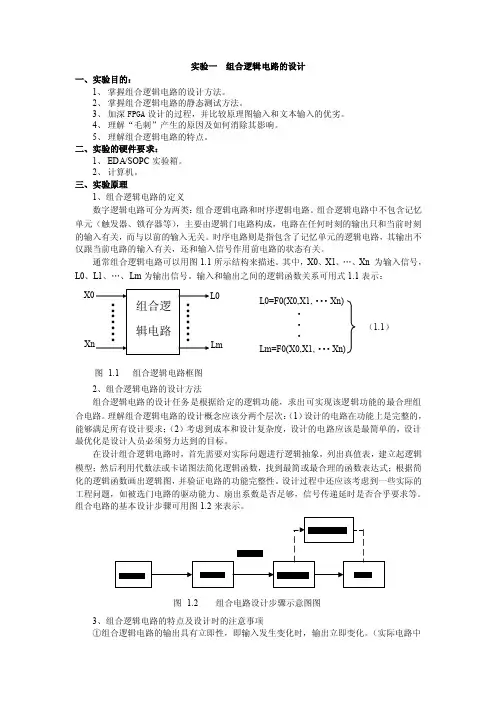

三、实验原理1、组合逻辑电路的定义数字逻辑电路可分为两类:组合逻辑电路和时序逻辑电路。

组合逻辑电路中不包含记忆单元(触发器、锁存器等),主要由逻辑门电路构成,电路在任何时刻的输出只和当前时刻的输入有关,而与以前的输入无关。

时序电路则是指包含了记忆单元的逻辑电路,其输出不仅跟当前电路的输入有关,还和输入信号作用前电路的状态有关。

通常组合逻辑电路可以用图1.1所示结构来描述。

其中,X0、X1、…、Xn 为输入信号, L0、L1、…、Lm 为输出信号。

输入和输出之间的逻辑函数关系可用式1.1表示: 2、组合逻辑电路的设计方法组合逻辑电路的设计任务是根据给定的逻辑功能,求出可实现该逻辑功能的最合理组 合电路。

理解组合逻辑电路的设计概念应该分两个层次:(1)设计的电路在功能上是完整的,能够满足所有设计要求;(2)考虑到成本和设计复杂度,设计的电路应该是最简单的,设计最优化是设计人员必须努力达到的目标。

在设计组合逻辑电路时,首先需要对实际问题进行逻辑抽象,列出真值表,建立起逻辑模型;然后利用代数法或卡诺图法简化逻辑函数,找到最简或最合理的函数表达式;根据简化的逻辑函数画出逻辑图,并验证电路的功能完整性。

设计过程中还应该考虑到一些实际的工程问题,如被选门电路的驱动能力、扇出系数是否足够,信号传递延时是否合乎要求等。

组合电路的基本设计步骤可用图1.2来表示。

3、组合逻辑电路的特点及设计时的注意事项①组合逻辑电路的输出具有立即性,即输入发生变化时,输出立即变化。

(实际电路中图 1.1 组合逻辑电路框图L0=F0(X0,X1,²²²Xn)² ² ²Lm=F0(X0,X1,²²²Xn)(1.1)图 1.2 组合电路设计步骤示意图图还要考虑器件和导线产生的延时)。

组合逻辑电路设计

组合逻辑电路是一种结构较简单的逻辑电路设计,其组成主要包括逻辑门、寄存器、

比较器、计数器和定时器等功能单元,其基本原理主要是将控制信号和数据信号通过特定

的逻辑关系进行组合,使这两类信号既配合现实应用运算结果正确也可输出想要的结果。

一般来说,组合逻辑电路的设计包括六个基本步骤:要求分析、功能拆解、设计模块、时序分析、组合实现及电路优化。

首先,根据用户的要求或系统的特性分析出电路需求,

以便根据功能分析出系统所要实现的具体功能;其次,划分电路功能模块,然后使用触发器、逻辑门、网络等实现每个功能模块的组合;再次,进行时序分析,以便确定出触发器

的进化规律;再次,将上述步骤中的结果组合起来,使用合适的触发器、逻辑门等将系统

的所有功能实现、组合起来;最后,进行电路优化,以便确定电路的表达能力,减少电路

复杂度,提高组合系统效能。

这样,最终设计出的组合逻辑电路就可以满足用户要求,满足较严格的要求则可以避

免运行失效问题,大大提高电路的可靠性。

此外,组合逻辑还可以按电路特性把功能模块

实现简单化,使系统运行速度更快,也可以更小的电路节省空间达到节能的要求,可谓组

合逻辑电路的优点之一。

组合逻辑电路的设计一.实验目的1、加深理解组合逻辑电路的工作原理。

2、掌握组合逻辑电路的设计方法。

3、掌握组合逻辑电路的功能测试方法。

二.实验器材实验室提供的芯片:74LS00与非门、74LS86异或门,74LS54与或非门,实验室提供的实验箱。

三.实验任务及要求1、设计要求(1)用与非门和与或非门或者异或门设计一个半加器。

(2)用与非门和与或非门或者异或门设计一个四位奇偶位判断电路。

2、实验内容(1)测试所用芯片的逻辑功能。

(2)组装所设计的组合逻辑电路,并验证其功能是否正确。

三.实验原理及说明1、简述组合逻辑电路的设计方法。

(1)分析实际情况是否能用逻辑变量来表示。

(2)确定输入、输出逻辑变量并用逻辑变量字母表示,作出逻辑规定。

(3)根据实际情况列出逻辑真值表。

(4)根据逻辑真值表写出逻辑表达式并化简。

(5)画出逻辑电路图,并标明使用的集成电路和相应的引脚。

(6)根据逻辑电路图焊接电路,调试并进一步验证逻辑关系是否与实际情况相符。

2、写出实验电路的设计过程,并画出设计电路图。

(1)半加器的设计如果不考虑有来自低位的进位将两个1位二进制数相加。

A、B是两个加数,S是相加的和,CO是向高位的进位。

逻辑表达式S=A’B+A’B=A⊕BCO=AB(2) 设计一个四位奇偶位判断电路。

当四位数中有奇数个1时输出结果为1;否则为0。

A,B,C,D分别为校验器的四个输入端,Y时校验器的输出端逻辑表达式Y=AB’C’D’+A’BC’D’+A’B’CD’+A’B’C’D+A’BCD+AB’CD+ABC’D+ABCD’=(A⊕B)⊕(C⊕D)四.实验结果1、列出所设计电路的MULTISM仿真分析结果。

(1)半加器的设计,1-A被加数,2-B加数,XMMI(和数S)XMM2(进位数CO)(2) 设计一个四位奇偶位判断电路。

2、写出检查芯片好坏的办法。

试连芯片,检测芯片的输入和输出是否符合芯片的逻辑功能3、记录所设计电路的测试结果。