数字电子技术组合逻辑电路

- 格式:ppt

- 大小:2.51 MB

- 文档页数:48

数字电子技术实验报告学院班级:软件学院131213班学生学号:13121228学生姓名:黄雯同作者: 吴青霞实验日期:2014年4月27日实验题目:组合逻辑电路的研究一.实验目的:1.了解三变量表决器的真值表、卡诺图,用数字电路板实现电路2.掌握一位全加器的真值表、卡诺图,用数字电路板实现电路3.掌握用MSI器件实现四位全加器的方法,并掌握全加器的应用。

二、实验环境:数字电路实验板三、实验内容及实验原理、(一)基本命题1. 用四2输入与非门74LS00和三输入与非门74HC11组成电路。

输入加逻辑开关,实现三变量多数表决器的功能,记录真值表,画出卡诺图和逻辑电路图2.用四2输入异或门74LS86和四2输入与非门74LS00组成一位全加器电路,输入加逻辑开关,测试其功能,并记录真值表,画出卡诺图和逻辑电路图。

3.用74LS283实现四位全加器电路,用数码管显示其全加和,并将结果填入表1中。

(二)实验原理与实验步骤a.三变量表决器1.实验原理:三变量表决器真值表如表1所示真值表(表1)根据三变量表决器真值表,画出三变量逻辑卡诺图。

如图1所示三变量表决器参考电路如图2所示图2用门电路实现的多数表决电路由真值表和卡诺图得出三变量表决器的逻辑表达式为:F= ACBC⋅⋅AB2.实验步骤:用逻辑开关当做A B C三个变量,将A接到1A,B接到1B, 将A接到2A,将C接到2B, 将B接到3A,C接到3B, 将1Y接到74HC10的1A,2Y接到1B, 将3Y接到1C,将1Y与与led灯相连,将开关打到“1”,观察led灯是否闪亮,以此检验电路图的正确性。

74SL00ABCF74HC10b.设计一位全加器1.实验原理:一位全加器真值表如表2所示:真值表A iB iC i S i C i+10 0 0 0 00 0 1 1 00 1 0 1 00 1 1 0 11 0 0 1 01 0 1 0 11 1 0 0 11 1 1 1 1(表2)根据一位全加器的真值表,画出三变量卡诺图,如图3所示:S i 的卡诺图 C i+1的卡诺图(图3)一位全加器的参考如图4所示:图 4一位全加器电路图4所示电路是由四2输入与非门74LS00和四2输入异或门74LS86组成的 一位全加器电路。

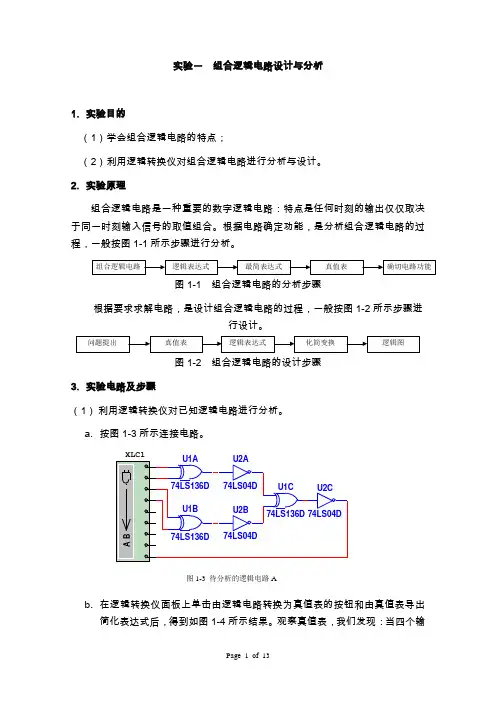

实验一组合逻辑电路设计与分析1.实验目的(1)学会组合逻辑电路的特点;(2)利用逻辑转换仪对组合逻辑电路进行分析与设计。

2.实验原理组合逻辑电路是一种重要的数字逻辑电路:特点是任何时刻的输出仅仅取决于同一时刻输入信号的取值组合。

根据电路确定功能,是分析组合逻辑电路的过程,一般按图1-1所示步骤进行分析。

图1-1 组合逻辑电路的分析步骤根据要求求解电路,是设计组合逻辑电路的过程,一般按图1-2所示步骤进行设计。

图1-2 组合逻辑电路的设计步骤3.实验电路及步骤(1)利用逻辑转换仪对已知逻辑电路进行分析。

a.按图1-3所示连接电路。

b.在逻辑转换仪面板上单击由逻辑电路转换为真值表的按钮和由真值表导出简化表达式后,得到如图1-4所示结果。

观察真值表,我们发现:当四个输入变量A,B,C,D中1的个数为奇数时,输出为0,而当四个输入变量A,B,C,D 中1的个数为偶数时,输出为1。

因此这是一个四位输入信号的奇偶校验电路。

图1-4 经分析得到的真值表和表达式(2)根据要求利用逻辑转换仪进行逻辑电路的设计。

a.问题提出:有一火灾报警系统,设有烟感、温感和紫外线三种类型不同的火灾探测器。

为了防止误报警,只有当其中有两种或两种以上的探测器发出火灾探测信号时,报警系统才产生报警控制信号,试设计报警控制信号的电路。

b.在逻辑转换仪面板上根据下列分析出真值表如图1-5所示:由于探测器发出的火灾探测信号也只有两种可能,一种是高电平(1),表示有火灾报警;一种是低电平(0),表示正常无火灾报警。

因此,令A、B、C分别表示烟感、温感、紫外线三种探测器的探测输出信号,为报警控制电路的输入、令F 为报警控制电路的输出。

图1-5 经分析得到的真值表(3)在逻辑转换仪面板上单击由真值表到处简化表达式的按钮后得到最简化表达式AC+AB+BC。

4.实验心得通过本次实验的学习,我们复习了数电课本关于组合逻辑电路分析与设计的相关知识,掌握了逻辑转换仪的功能及其使用方法。

竭诚为您提供优质文档/双击可除组合逻辑电路的设计实验报告篇一:数电实验报告实验二组合逻辑电路的设计实验二组合逻辑电路的设计一、实验目的1.掌握组合逻辑电路的设计方法及功能测试方法。

2.熟悉组合电路的特点。

二、实验仪器及材料a)TDs-4数电实验箱、双踪示波器、数字万用表。

b)参考元件:74Ls86、74Ls00。

三、预习要求及思考题1.预习要求:1)所用中规模集成组件的功能、外部引线排列及使用方法。

2)组合逻辑电路的功能特点和结构特点.3)中规模集成组件一般分析及设计方法.4)用multisim软件对实验进行仿真并分析实验是否成功。

2.思考题在进行组合逻辑电路设计时,什么是最佳设计方案?四、实验原理1.本实验所用到的集成电路的引脚功能图见附录2.用集成电路进行组合逻辑电路设计的一般步骤是:1)根据设计要求,定义输入逻辑变量和输出逻辑变量,然后列出真值表;2)利用卡络图或公式法得出最简逻辑表达式,并根据设计要求所指定的门电路或选定的门电路,将最简逻辑表达式变换为与所指定门电路相应的形式;3)画出逻辑图;4)用逻辑门或组件构成实际电路,最后测试验证其逻辑功能。

五、实验内容1.用四2输入异或门(74Ls86)和四2输入与非门(74Ls00)设计一个一位全加器。

1)列出真值表,如下表2-1。

其中Ai、bi、ci分别为一个加数、另一个加数、低位向本位的进位;si、ci+1分别为本位和、本位向高位的进位。

2)由表2-1全加器真值表写出函数表达式。

3)将上面两逻辑表达式转换为能用四2输入异或门(74Ls86)和四2输入与非门(74Ls00)实现的表达式。

4)画出逻辑电路图如图2-1,并在图中标明芯片引脚号。

按图选择需要的集成块及门电路连线,将Ai、bi、ci接逻辑开关,输出si、ci+1接发光二极管。

改变输入信号的状态验证真值表。

2.在一个射击游戏中,每人可打三枪,一枪打鸟(A),一枪打鸡(b),一枪打兔子(c)。

实验报告实验课程名称数字电子技术实验实验项目名称组合逻辑电路设计专业、班级电子信息类四班实验日期2020-05-25 姓名、学号同组人教师签名成绩实验报告包含以下7项内容:一、实验目的二、实验基本原理三、主要仪器及设备四、操作方法和实验步骤五、实验原始数据记录六、数据处理过程及结果、结论七、问题和讨论一、实验目的掌握组合逻辑电路的设计方法、设计步骤。

二、实验基本原理门电路的逻辑功能三、实验设备及器件1、直流稳压电源、信号源、示波器、万用表、面包板2、器件:74LS00 四2输入与非门,74LS86 四2输入异或门74LS10 3输入与非门,74LS153 双4选1数据选择器图4-1 74LS10内部结构及引脚排列四、操作方法和实验步骤组合逻辑电路设计的步骤大致如下:(1)根据已知条件要求列出逻辑状态表(2)写出逻辑表达式(3)运用逻辑代数化简或变换(4)画出逻辑电路图1、用74LS00(2输入与非门)、74LS10(3输入与非门)设计并实现三人表决电路。

功能:多数人(2人及以上)同意就通过(输出Y=1),少数人同意就不通过。

(1)列出逻辑状态表。

表3-1 三人表决器逻辑状态表输入输出A B C Y0 0 0 00 0 1 00 1 0 00 1 1 11 0 0 01 0 1 11 1 0 11 1 1 1(2Y=A’BC+AB’C+ABC’+ABC =AC+AB+BC(3)将逻辑表达式转换为需要的形式。

转化为与非表达式:取两次反。

即Y=AB+AC+BC=((AB)’(AC)’(BC)’)’(4)画出电路图。

(5)按电路图接线,验证状态表思考题1:如果只使用74LS00(2输入与非门)如何实现三人表决电路?给出电路接线图并验证。

2、使用74LS86异或门、74LS00与非门,设计一个四位奇偶校验器。

功能:当A、B、C、D四位数中有奇数个1时输出Y1为1,否则Y1输出为0(奇校验);如果四位输入有偶数个1时,Y2输出为1(偶校验)。

第四章组合逻辑电路1. 解: (a)(b)是相同的电路,均为同或电路。

2. 解:分析结果表明图(a)、(b)是相同的电路,均为同或电路。

同或电路的功能:输入相同输出为“1”;输入相异输出为“0”。

因此,输出为“0”(低电平)时,输入状态为AB=01或103. 由真值表可看出,该电路是一位二进制数的全加电路,A为被加数,B为加数,C为低位向本位的进位,F1为本位向高位的进位,F2为本位的和位。

4. 解:函数关系如下:ABSF+⊕=++ABSSSABB将具体的S值代入,求得F 312值,填入表中。

A A FB A B A B A A F B A B A A F A A F AB AB F B B A AB F AB B A B A B A AB F B A A AB F B A B A B A F B A AB AB B A B A F B B A B A B A B A B A B A F AB BA A A B A A B A F F B A B A F B A B A F A A F S S S S =⊕==+==+⊕===+⊕===⊕===⊕===+⊕===+=+⊕===⊕==+==⊕==Θ=+=+⊕===+++=+⊕===+=⊕===⊕==+=+⊕==+=+⊕===⊕==01111111011010110001011101010011000001110110)(01010100101001110010100011000001235. (1)用异或门实现,电路图如图(a)所示。

(2) 用与或门实现,电路图如图(b)所示。

6. 解因为一天24小时,所以需要5个变量。

P变量表示上午或下午,P=0为上午,P=1为下午;ABCD表示时间数值。

真值表如表所示。

利用卡诺图化简如图(a)所示。

化简后的函数表达式为D C A P D B A P C B A P A P DC A PD B A P C B A P A P F =+++=用与非门实现的逻辑图如图(b)所示。

《数字电子技术B》实验报告班级:姓名学号:实验二组合逻辑电路(半加器、全加器)一、实验目的1.掌握组合逻辑电路的功能测试。

2.验证半加器和全加器的逻辑功能。

3.学会二进制数的运算规律。

二、实验仪器及材料74LS00 二输入端四与非门 3片74LS86 二输入端四异或门 1 片74LS54 四组输入与或非门 1片三、实验内容(如果有可能,附上仿真图)1.组合逻辑电路功能测试。

(1).用2片74LS00组成图2.1所示逻辑电路。

为便于接线和检查,在图中要注明芯片编号及各引脚对应的编号。

(2).图中A、B、C接电平开关,Y1,Y2接发光管电平显示。

(3).接表2.1要求,改变A、B、C的状态填表并写出Y1,Y2逻辑表达式。

(4).将运算结果与实验比较。

表2.1Y1=A+B Y2=(A’*B)+(B’*C)2.测试用异或门(74LS86)和与非门组成的半加器的逻辑功能。

根据半加器的逻辑表达式可知,半加器Y是A、B的异或,而进位Z是A、B相与,故半加器可有一个集成异或门和二个与非门组成如图2.2。

图2.2(1).在实验仪上用异或门和与门接成以上电路。

A、B接电平开关K,Y,Z接电平显示。

(2).按表2.2要求改变A、B状态,填表。

表2.23.(1).写出图2.3电路的逻辑表达式。

(2).根据逻辑表达式列真值表。

表2.3(5)按原理图选择与非门并接线进行测试,将测试结果记入表2.4,并与上表进行比较看逻辑功能是否一致。

4. 测试用异或、与或和非门组成的全加器的逻辑功能。

全加器可以用两个半加器和两个与门一个或门组成,在实验中,常用一块双异或门、一个与或非门和一个与非门实现。

(1).画出用异或门、与或非门和非门实现全加器的逻辑电路图,写出逻辑表达式。

(2).找出异或门、与或非门和与门器件按自己画出的图接线。

接线时注意与或非门中不用的与门输入端接地。

(3).当输入端A i、B i及C i-1为下列情况时,用万用表测量S i和C i的电位并将其转为逻辑状态填入下表。