状态检测机verilog

- 格式:docx

- 大小:112.34 KB

- 文档页数:12

状态机verilog实际工程应用

Verilog状态机在实际工程中有着广泛的应用。

状态机是一种能够根据输入信号和当前状态自动转移的逻辑电路,它可以用来描述系统的行为和控制逻辑。

在Verilog中,状态机通常使用有限状态机(FSM)来描述,可以分为Moore状态机和Mealy状态机两种类型。

在实际工程中,Verilog状态机可以应用于各种数字系统的设计,包括但不限于通信系统、控制系统、图形处理器、计算机处理器等。

下面我将从不同的角度来介绍Verilog状态机在实际工程中的应用。

1. 控制逻辑,Verilog状态机可以用于实现控制逻辑,例如在数字系统中根据特定的输入信号来控制输出信号的状态转移,比如在通信系统中根据接收到的数据来执行特定的操作。

2. 时序逻辑,状态机可以用于描述时序逻辑,例如在时序电路中根据时钟信号来执行特定的操作,比如在处理器中根据时钟信号来执行指令的译码和执行。

3. 状态转移,Verilog状态机可以描述系统中不同状态之间的

转移关系,比如在控制系统中描述不同的控制状态和状态之间的转

移条件,从而实现系统的自动控制。

4. 状态检测,状态机可以用于检测系统的状态,例如在通信系

统中可以用状态机来检测数据的传输状态,从而实现数据的接收和

发送控制。

总的来说,Verilog状态机在实际工程中有着广泛的应用,可

以用于描述系统的控制逻辑、时序逻辑、状态转移和状态检测等方面,是数字系统设计中非常重要的一部分。

通过合理的设计和实现,Verilog状态机可以帮助工程师们实现复杂的数字系统功能,提高

系统的可靠性和性能。

systemverilog断言例子(一)SystemVerilog断言什么是SystemVerilog断言SystemVerilog断言是一种在硬件设计中使用的验证技术,用于检查设计行为和性质的正确性。

断言可以描述设计中的时序序列、性质规则或者约束条件,并在设计运行时进行验证。

SystemVerilog断言的语法SystemVerilog断言采用assert关键字来定义。

断言语句由一个条件表达式和一个可选的信息字符串组成,语法如下:assert condition;assert condition else failure_message;断言实例例子1:检查FIFO写入操作的空闲状态assert (wr_en == 0) |-> (is_empty == 1);上述例子中,断言检查了当写使能信号wr_en为0时,FIFO的空状态is_empty应为1。

如果断言条件不满足,则产生错误。

例子2:验证FIFO读取操作的一致性assert (rd_en == 0) |-> (rd_data === rd_data[$rose (wr_en)]);这个例子中,断言检查了当读使能信号rd_en为0时,已读取的数据rd_data应与最近的写入数据wr_data相等。

使用$rose函数来检测写入使能信号的上升沿。

例子3:检查FIFO写入和读取的顺序assert (wr_en & rd_en) |-> (wr_index <= rd_index);此例中,断言验证了在写入使能信号和读取使能信号同时为1时,写入的索引地址wr_index应小于等于读取的索引地址rd_index。

例子4:检查FIFO的深度不超过上限int depth = 16;assert (wr_en & !rd_en) |-> (wr_index - rd_index < dept h);这个例子中,断言验证了在写使能信号为1且读使能信号为0时,写入的索引地址与读取的索引地址之差应小于FIFO的深度上限。

实验报告用状态机实现序列检测器实验一、实验目的1.用Verilog HDL描述有限状态机电路。

2.IPCORE的概念与设计。

二、实验内容1.应用有限状态机的设计思路,检测从FPGA片上ROM读出的串行数据是否是特定的数据。

2.每个人需要检测的数据是所用的电脑编号+200后转换的8位二进制数。

三、实验要求1.拟用按键、拨动开关实现系统的时钟,复位信号的输入。

2.一个7段数码显示译码器作为检测结果的输出显示,如果串行序列为”100101”,显示A,否则显示b(系统需要设计一个7段数码显示译码器模块)仍使用消抖模块,对由按键输入的时钟进行消抖处理。

3.读取的串行数据为rom中固化的一个宽度为1bit,深度为16bits的数据。

四、设计思路软件的设计框图如下,该实验可以分为几个模块,rom数据读出模块,串行检测模块,数码管显示模块,顶层模块。

输入的clk为按键消抖后输出的数据,按下一次检测一次,在时钟的上升沿读出数据,时钟的下降沿检测数据,串行模块输出的4bits的数据,直接送给数码管译码模块,译码输出。

五、设计原理1.ROM IP核的生成首先在ISE自己的工程中新建一个块内存,Block Memory Generator,配置深度为16,宽度为1bit,选择生成的类型为单端ROM,然后选择一个已经编写好的memory初始化文件。

Memory初始化文件,编写coe文件:这里我要写入的是226,所以二进制是11100010,写入的内容如下,:memory_initialization_radix=10;memory_initialization_vector=1 1 1 0 0 0 1 1 1 0 1 0 1 0 1 0;保存并选择载入。

2.读取rom中的数据根据时钟上升沿读取数据,所以可以写出rom读的代码,代码如下:module read_rom(clk,da,rst);input clk;input rst;output da;reg[3:0] counter;always@(posedge clk or posedge rst) beginif(rst)counter<=1'b0;else counter<=counter+1'b1;enddata_rom u1(.clka(clk), // input clka.addra(counter), // input [3 : 0] addra.douta(da) // output [0 : 0] douta);编写仿真激励文件,得到如下波形,分析可以知道,时钟上升沿数据被读取,读取的数据与我们在配置文件中写入的相同。

《FPGA》课程报告设计题目:状态机实现序列检测器设计学生班级:学生学号:学生姓名:指导教师:时间:成绩:一、实验目的:1.理解有限状态机的概念;2. 掌握有限状态机的状态图的画法及其含义二、实验原理:本次实验的内容是:应用有限状态机设计思路,检测输入的串行数据是否是”11100101”,本次实验由顶层文件、串行检测、并行数据转串行、数码管显示四个模块组成。

1.并行数据转串行数据模块功能是:可以异步复位,可以在时钟控制下,将并行输入数据din[7:0],按照din[7],din[6],din[5],din[4],din[3],din[2],din[1],din[0]的顺序输出至串行检测模块的输入端口din。

2.串行检测模块:输入信号:DIN-----1bit的串行输入数据CLK-----同步输入时钟CLR ------异步清零信号,当CLR=1,系统输出置0,否则,系统正常工作输出信号:AB--------4bits数据,如果系统检测到“11100101”这8bit 的输入,AB=4’b1010,否则,AB=4’b1011.三、实验过程:1.首先建立一个新的工程,添加一个新的Verilog Module文件,然后写入并行数据转串行数据模块的代码,代码如下:进行仿真,仿真图如下:2.再新建一个Verilog Module文件,在其中写入串行检测模块的代码,代码如下:进行仿真,仿真图如下:3. 再新建一个Verilog Module文件,数码管显示模块的代码,代码如下:然后执行综合,确认无误后,新建一个Test Bench WaveForm文件,进行仿真,仿真图如下:4.编写顶层文件,将上面三个模块例化在一起,代码如下:然后将新的顶层文件经行综合,确认无误后,新建一个Test Bench WaveForm文件,进行仿真,仿真图如下:5.添加消抖模块,然后编写新的顶层文件,将消抖模块与上面的模块例化在一起,代码如下:保存后生成新的顶层文件:6.完成以上操作后,执行综合确认无误,经行锁引脚操作:锁引脚完成后,编辑、修改约束文件:7. 生成下载配置文件,下载到开发板进行经行验证。

systemverilog posedge条件用法SystemVerilog中的posedge条件用法是一种在硬件描述语言中使用的条件语句,用于检测时钟信号的上升沿。

本篇文章将详细介绍posedge 条件用法,并提供一步一步的解释和举例。

I. posedge条件用法简介SystemVerilog中的posedge条件用法是一种特殊的条件用法,它用于检测时钟信号的上升沿。

当时钟信号的电压从低电平跳变到高电平时,posedge条件将为真。

这种条件用法可以用于设计中的许多方面,如时序逻辑、状态机和触发器等。

II. 语法和用法在SystemVerilog中,使用posedge关键字来定义posedge条件。

它的语法如下:`posedge <时钟信号>`其中,时钟信号是一个逻辑信号,它通常是一个(或多个)时钟引脚,或者是一个位或者信号。

当等号左边的电平变为高电平时,该条件将为真。

III. 示例为了更好地理解posedge条件的用法,我们将通过几个实例来说明。

1. 使用posedge条件进行时序逻辑假设我们有一个简单的计数器,它在时钟的上升沿增加一个值,并在达到最大计数时(例如8位计数器的最大值为255)重置为零。

下面是一个使用posedge条件的例子:reg [7:0] count;always @(posedge clk) beginif (count == 255)count <= 0;elsecount <= count + 1;end在上述代码中,posedge条件`(posedge clk)`表示每当时钟信号`clk`的上升沿发生时,将执行该代码块中的内容。

这样,当计数器的值达到最大值时,使用posedge条件进行检测并将其重置为0。

2. 使用posedge条件进行状态机转换假设我们有一个简单的状态机,它具有三个状态:A、B和C。

状态之间的转换基于时钟信号的上升沿。

下面是一个使用posedge条件的例子:parameter A = 2'b00;parameter B = 2'b01;parameter C = 2'b10;reg [1:0] state;always @(posedge clk) begincase (state)A: state <= B;B: state <= C;C: state <= A;endcaseend在上述代码中,posedge条件`(posedge clk)`用于检测时钟信号的上升沿。

verilog判断上升沿的方法在 Verilog 中判断上升沿的方法有多种。

以下是其中两种常用方法的介绍:方法一:使用边沿检测器要判断信号的上升沿,可以使用边沿检测器模块。

边沿检测器将输入信号与其之前的状态进行比较,当输入信号从低电平变为高电平时,输出产生一个上升沿脉冲。

以下是一个示例代码片段:```module EdgeDetector (input wire clk,input wire sig,output wire posedge);reg sig_prev = 0;always @(posedge clk) beginsig_prev <= sig;posedge <= (sig && !sig_prev);endendmodule```在上述示例中,输入信号 `sig` 和时钟信号 `clk` 都采用 `wire` 类型声明。

`sig_prev` 为上一个时刻的信号值,使用 `reg` 类型存储,并在时钟上升沿触发时进行更新。

`posedge` 为输出信号,当边沿检测到输入信号 `sig` 由低电平变为高电平时,输出一个脉冲。

方法二:使用组合逻辑Verilog 中也可以使用组合逻辑来判断上升沿。

以下是一个使用组合逻辑实现的示例代码片段:```module RisingEdgeDetector (input wire clk,input wire sig,output wire posedge);wire sig_prev = ~sig;assign posedge = (sig && sig_prev);endmodule```在上述示例中,`sig_prev` 通过对输入信号 `sig` 取反得到,用于表示上一个时刻的信号状态。

`posedge` 是一个输出信号,使用 `assign` 语句通过逻辑运算判断输入信号 `sig` 是否为高电平,并且上一个时刻的信号 `sig_prev` 为低电平。

verilog dma原理-概述说明以及解释1.引言1.1 概述概述部分的内容可以简要介绍DMA的基本概念和作用,以及本文将要讨论的内容和结构。

概述部分内容示例:概述DMA(Direct Memory Access,直接内存访问)是一种计算机技术,用于实现数据在外设和内存之间的直接传输,不需要CPU的介入。

通过使用DMA,可以提高数据传输的速度和效率,减少CPU的负载,提升系统的整体性能。

本文将介绍DMA的原理及其在Verilog中的实现。

首先,我们将简要介绍DMA的基本概念和作用,以及Verilog语言的基础知识。

然后,我们将详细探讨DMA在Verilog中的实现原理,并分析其在实际应用中的优势和不足之处。

最后,我们将对DMA的应用前景进行展望,并对本文进行总结。

通过阅读本文,读者将深入了解DMA技术的原理和Verilog语言的应用。

同时,读者也将了解DMA在各种应用场景中的潜力和限制,有助于更好地应用它来提升系统性能。

让我们开始探索DMA的奥秘吧!1.2 文章结构文章结构部分的内容:本文将按照以下结构组织和呈现关于Verilog DMA原理的详细资料。

引言部分将首先对Verilog DMA原理进行概述。

我们将简要介绍DMA的基本概念,解释Verilog语言的重要性,并说明本文的目的。

正文部分将进一步深入探讨Verilog DMA在硬件设计中的实现原理。

我们将讨论DMA在Verilog中的具体应用,介绍Verilog语言的特点和用法,以及具体实现DMA的方法和技巧。

结论部分将对Verilog DMA的应用前景进行展望。

我们将评估DMA 在硬件设计中的优势和不足,并总结文章中的观点和结论。

通过以上结构的安排,本文将对读者提供一个全面而深入的Verilog DMA原理的学习资料。

读者将了解到DMA的基本概念和Verilog语言的关键知识,以及如何在Verilog中实现DMA的方法。

同时,我们还会探讨DMA在硬件设计中的前景,并评估其在实际应用中的优势与不足。

verilog状态跳变检测方法在Verilog中,你可以使用时钟边缘检测的方法来检测状态跳变。

一种常见的方法是使用触发器(Flip-Flop)或寄存器(Register)来实现。

下面是一个简单的例子,展示如何使用触发器来检测状态跳变:```verilogmodule state_detector (input wire clk, // 输入时钟信号input wire reset, // 输入复位信号input wire current_state, // 输入当前状态output reg next_state // 输出下一个状态);reg previous_state; // 寄存器,用于存储上一个状态always (posedge clk or posedge reset) beginif (reset) beginnext_state <= 0; // 复位时,将下一个状态设置为0previous_state <= 0; // 同时将上一个状态也设置为0end else begin// 检测状态跳变if (current_state != previous_state) beginnext_state <= ~previous_state; // 状态跳变时,取反上一个状态作为下一个状态end else beginnext_state <= previous_state; // 状态未跳变时,保持上一个状态作为下一个状态endprevious_state <= current_state; // 更新上一个状态为当前状态 endendendmodule```在上面的代码中,我们使用了一个触发器(`previous_state`)来存储上一个状态。

在时钟上升沿时,我们比较当前状态和上一个状态,如果它们不相等,则表示发生了状态跳变。

根据需要,你可以根据状态跳变的规则来设置下一个状态的值。

![[数字芯片]SystemVerilog与Modelsim自动化仿真](https://img.taocdn.com/s1/m/c9c0eec97e192279168884868762caaedd33babd.png)

[数字芯⽚]SystemVerilog与Modelsim⾃动化仿真简单Verilog编写数字电路的各个模块,必须伴随着⼀testbench⽂件⽤作仿真验证。

简单的module当然可以使⽤简单的Verilog编写⼀个testbench进⾏简单的仿真,但⼀旦遇到功能较为复杂时,Verilog语⾔的灵活性不⾜C/C++这类语⾔。

SystemVerilog作为⼀门针对验证的⾯向对象的编程语⾔,能够更好的描述时序,同时具有⾯向对象语⾔的灵活性以及重复使⽤性,能够为⼯程仿真带来许多便利。

接下来,简单使⽤SystemVerilog对序列检测的module进⾏仿真验证。

⼀、⼯程框架本⼯程测试⼀个使⽤状态机检测“1110010”序列的module,包含五个⽂件,具体描述如下:├── top.sv:顶层模块,⽤以连接下列各个模块││├── module_bfm.sv: 模块的bus functional model,描述⽤以连接的interface││├── tester.sv: 产⽣仿真的时序信号││├── coverage.sv: 对模块覆盖率的检测││├── module.v: 待仿真验证的模块由于module是使⽤Verilog编写的,不能直接使⽤Interface, ⽽需要按照Verilog的规范进⾏连接,⽽其余SV的module直接使⽤BFM连接。

module top();seq_fsm_bfm bfm();coverage converage_i(bfm);tester tester_i(bfm);seq_fsm seq_fsm_i(.in(bfm.in),.out(bfm.out),.state(bfm.state),.clk(bfm.clk),.reset(bfm.rst_n));endmodule⼆、SystemVerilog的interface使⽤使⽤Verilog是对于module端⼝的连接,不管使⽤顺序还是使⽤名称连接都容易出错以及极为繁琐。

Verilog--序列检测器(采⽤移位寄存器实现)Verilog --序列检测器(采⽤移位寄存器实现)序列检测器就是将⼀个指定序列从数字码流中识别出来。

本例中将设计⼀个“10010”序列的检测器。

设X为数字码流的输⼊,Z为检测出标记输出,⾼电平表⽰发现指定的序列10010.考虑码流为110010010000100101这篇博客,才发现原来使⽤移位寄存器可以如此简单,原理图如下:基本思路就是利⽤移位寄存器作为检测窗⼝,每进来⼀个数就跟⽬标序列进⾏⽐较,简单粗暴。

下⾯贴⼀下原帖的代码:module seqdet(input wire x,input wire clk,input wire rst,output wire z,output reg [4:0] q);//reg [4:0] q;assign z = (q == 5'b10010) ? 1'b1:1'b0;always @ (posedge clk,negedge rst)if(!rst)q <= 5'd0;elseq <= {q[3:0],x};endmoduletestbench:`timescale 1ns/1nsmodule seqdet_tb;localparam T =20;reg clk,rst;reg [23:0] data;wire z,x;wire [4:0] q;assign x = data[23];initialbeginclk =0;rst =1;#2 rst =0;#30 rst =1;data =20'b1100_1001_0000_1001_0100;#(T*1000) $stop;endalways #T clk = ~clk;always @ (posedge clk)#2 data = {data[22:0],data[23]};seqdet U1(.x(x),.z(z),.clk(clk),.q(q),.rst(rst));endmodule由于移位寄存器的赋值是在always块中,故⽽相对实际延迟了⼀个clk.由上⾯的⽅针结果可知,输出z相对x晚了⼀个时钟周期,因为由于移位寄存器的赋值是在always块中,故⽽相对实际延迟了⼀个clk.Note:跟⽤状态机实现的区别在于,使⽤移位寄存器需要存储所有的码字,因此如果序列长度为N,则该⽅法需要消耗的寄存器就是N个。

一、什么是sv assertion在系统Verilog中,sv(SystemVerilog)assertion是一种用于验证设计行为和性能的一种方法。

它可以用于检测设计中的错误和异常条件,以确保设计的正确性和稳定性。

sv assertion可以帮助设计工程师发现潜在的问题,并提前进行修复,从而提高设计的可靠性和稳定性。

二、sv assertion的基本语法和结构sv assertion通常由两部分组成:属性和触发器。

属性描述了设计中的某种行为或性质,而触发器指定了何时或在何种条件下进行属性检查。

sv assertion的基本语法结构如下:```property property_name;// property body// 属性描述endpropertyassert property_name;// 触发器// 触发条件```其中,property定义了属性的内容,而assert则表示了对该属性进行检查的触发器。

在property中可以使用逻辑运算、比较运算等方式描述设计的行为,而在assert中可以指定触发属性检查的条件和触发时机。

三、sv assertion的常见应用场景1. 时序验证sv assertion可以用于时序验证,例如检查时序约束是否满足、时钟颗粒度是否合理等。

通过定义属性和触发器,可以对设计中的时序关系进行检查和验证,从而确保设计的正确性和稳定性。

2. 数据一致性检查在设计中经常需要对不同数据信号之间的一致性进行检查,以避免数据错误引发的问题。

sv assertion可以帮助设计工程师定义数据一致性的属性,并在特定的条件下进行检查,以保证数据的正确性和一致性。

3. 状态机验证状态机在数字设计中经常被使用,而sv assertion可以用于验证状态机的正确性和稳定性。

通过定义状态机的属性和触发器,可以对状态转移、状态转移条件等进行检查,以确保状态机的正确行为。

4. 功能验证sv assertion也可以用于对设计的功能进行验证。

Moore型verilog源代码:FSM实现10010串的检测Moore状态转移图module moorefsm(clk,rst,a,z);input clk,rst;input a;output z;reg z;reg [3:0] currentstate,nextstate;parameter S0 = 4'b0000;parameter S1 = 4'b0001;parameter S2 = 4'b0010;parameter S3 = 4'b0011;parameter S4 = 4'b0100;parameter S5 = 4'b0101; always@(posedge clk or negedge rst) beginif(!rst)currentstate <= S0;elsecurrentstate <= nextstate;endalways@(currentstate or a or rst)beginif(!rst)nextstate = S0;elsecase(currentstate)S0: nextstate = (a==1)?S1:S0;S1: nextstate = (a==0)?S2:S1;S2: nextstate = (a==0)?S3:S1;S3: nextstate = (a==1)?S4:S0;S4: nextstate = (a==0)?S5:S1;S5: nextstate = (a==0)?S3:S1;default: nextstate = S0;endcaseendalways@(rst or currentstate)beginif(!rst)z = 0;elsecase(currentstate)S0: z = 0;S1: z = 0;S2: z = 0;S3: z = 0;S4: z = 0;S5: z = 1;default: z = 0;endcaseend endmodulemoorefsm测试模块testbenchmodule tb_fsm;reg clk,rst;reg a;wire z;moorefsmfsm(.clk(clk),.rst(rst),.a(a),.z(z)); initialbeginclk = 0;rst = 1;#5 rst = 0;#3 rst = 1;#20 a = 1;#100 a = 1;#100 a = 0;#100 a = 0;#100 a = 1;#100 a = 0;#100 a = 0;#100 a = 1;#100 a = 0;#100 a = 0;#100 a = 0;#100 a = 0;#100 a = 1;#100 a = 0;#100 a = 0;#100 a = 1;#100 a = 0;#100 a = 1;#100 a = 0;endalways #50 elk = ~clk; endmoduleMealy型verilog源代码:FSM实现10010串的检测module mealyfsm(clk,rst,a,z);Mealy状态转移图input clk;input rst;input a;output z;reg z;reg [3:0] temp_z;reg [3:0] currentstate,nextstate;parameter S0 = 4'b0000;parameter S1 = 4'b0001;parameter S2 = 4'b0010;parameter S3 = 4'b0011;parameter S4 = 4'b0100;always@(posedge clk or negedge rst) if(!rst) currentstate <= S0;elsecurrentstate <= nextstate;always@(currentstate or a or rst) if(!rst)nextstate = S0;elsecase(currentstate)S0: nextstate = (a == 1)? S1 : S0;S1: nextstate = (a == 0)? S2 : S1;S2: nextstate = (a == 0)? S3 : S1;S3: nextstate = (a == 1)? S4 : S0;S4: nextstate = (a == 0)? S2 : S0;default:nextstate = S0;endcasealways@(rst or currentstate or a) if(!rst)temp_z = 0;elsecase(currentstate)S0: temp_z = 0;S1: temp_z = 0;S2: temp_z = 0;S3: temp_z = 0;S4: temp_z = (a == 0)? 1 : 0;default:temp_z = 0;endcasealways@(posedge clk or negedge rst)if(!rst)z <= 0;elsebeginif((temp_z == 1)&&(nextstate == S2))z <= 1;elsez <= 0;endendmodulemealyfsm 测试模块testbenchmodule tb_fsm;reg clk,rst;reg a;wire z; mealyfsmfsm(.clk(clk),.rst(rst),.a(a),.z(z));initialbeginclk = 0;rst = 1;#5 rst = 0;#3 rst = 1;#20 a = 1;#100 a = 1;#100 a = 0;#100 a = 0;#100 a = 1;#100 a = 0;#100 a = 0;#100 a = 1;#100 a = 0;#100 a = 0;#100 a = 0;#100 a = 0;#100 a = 1;#100 a = 0;#100 a = 0;#100 a = 1;#100 a = 0;#100 a = 1;#100 a = 0;endalways #50 clk = ~clk; endmodule。

Verilog语言可以用于数字逻辑设计和硬件描述语言(HDL)的编写,因此可以用来实现自动波特率检测的功能。

自动波特率检测是指在串行通信中自动识别输入数据的波特率(即数据传输速率)的过程。

以下是一个基本的Verilog代码框架,用于实现自动波特率检测的原理:```verilogmodule baudrate_detector (input wire clk, // 输入时钟信号input wire data_in, // 串行输入数据信号output reg baudrate_detected // 输出波特率检测结果);reg [15:0] count; // 计数器,用于计算每个数据位之间的时间间隔reg [3:0] state; // 状态机的状态寄存器parameter BIT_PERIOD = 16'd62500; // 假设波特率为9600bps,计算得到每位数据的时间间隔always @(posedge clk) begin// 状态机case (state)4'b0000: begin // 初始状态count <= 0;state <= 4'b0001;end4'b0001: begin // 检测起始位if (data_in == 0) beginstate <= 4'b0010;endend4'b0010: begin // 检测数据位if (count < BIT_PERIOD) begincount <= count + 1;end else beginstate <= 4'b0011;endend4'b0011: begin // 检测停止位if (data_in == 1) beginbaudrate_detected <= 1; // 波特率检测成功endstate <= 4'b0000; // 返回初始状态enddefault: state <= 4'b0000;endcaseendendmodule```这段Verilog代码实现了一个简单的波特率检测模块。

基于Verilog应用2007-09-18 16:25:19 来源:电子技术应用关键字:可编程逻辑器件Verilog HDL FIFO FSM随着数字时代的到来,数字技术的应用已经渗透到了人类生活的各个方面。

数字系统的发展在很大程度上得益于器件和集成技术的发展,著名的摩尔定律(Moore's Law)的预言也在集成电路的发展过程中被印证了,数字系统的设计理念和设计方法在这过程中发生了深刻的变化。

从电子CAD、电子CAE到电子设计自动化(EDA),随着设计复杂程度的不断增加,设计的自动化程度越来越高。

目前,EDA技术作为电子设计的通用平台,逐渐向支持系统级的设计发展;数字系统的设计也从图形设计方案向硬件描述语言设计方案发展。

可编程器件在数字系统设计领域得到广泛应用,不仅缩短了系统开发周期,而且利用器件的现场可编程特性,可根据应用的要求对器件进行动态配置或编程,简单易行地完成功能的添加和修改。

在现代工业的发展中,实时测控系统得到广泛应用,这就对高速数字信号处理系统提出了更高的要求。

因为要涉及大量的设计,为了提高运算速度,应用了大量DSP器件。

数字采集系统是整个系统的核心部分之一,传统方法是应用MCU或DSP通过软件控制数据采集的模/数转换,这样必将频繁中断系统的运行从而减弱系统的数据运算,数据采集的速度也将受到限制。

因此,DSP+CPLD的方案被认为是数字信号处理系统的最优方案之一,由硬件控制模/数转换和数据存储,从而最大限度地提高系统的信号采集和处理能力。

1 系统总体方案数据采集系统是基于DSP的信号处理系统中的一部分。

框图如图1所示。

该数字信号处理系统用于随机共振理论在弱信号检测中的应用研究中。

整个系统由信号放大、信号滤波、信号采样、高速数字信号处理、与主计算机的高速数据传输接口等部分组成。

其中,信号放大是对输入信号进行调理以满足采样的要求;信号滤波是防止信号产生“混叠现象”;信号采样是完成模拟信号的数字化;高速数字信号处理是在建立随机共振模型的基础上完成各种算法;与主计算机的高速数据传输接口是满足信号检测的实时性,将DSP处理的数据传给计算机以进行进一步的处理。

《数字逻辑电路》课程思政优秀案例一、课程简介“数字逻辑电路”课程是电子信息与电气工程类专业的工程基础课,提供数字技术和数字系统的基本概念、基本原理和基本技能,学习数字电路的分析与设计方法,培养工程实践能力、创新精神,以及工程师的使命与责任,同时为后续专业课程的学习以及适应现代信息社会的快速变化奠定坚实的基础。

案例一:时序逻辑电路的设计思政育人目标1. 培养高阶思维和计算思维;2. 培养学无止境、追求真理的精神。

思政育人案例设计教学内容:1. 米里(Mealy)型与摩尔(Moore)型有限状态机的建立;2. 时序逻辑电路的设计方法。

思政融入点:1.“111”序列检测器的传统设计方法首先根据同步时序电路的设计步骤讲授基于Mealy型状态机的“111”序列检测器的设计过程,然后设定时钟和输入,让学生画出上述设计的“111”序列检测器的状态和输出波形,会发现输出波形与预期的不一致。

通过这个活动,引发学生认知冲突,激发学生思维碰撞,引导学生批判性地思考问题,找到解决问题的答案。

接着研讨:(1)如何用Moore型状态机设计“111”序列检测器?(2)Mealy型状态机和Moore型状态机的区别。

2.“111”序列检测器的Verilog HDL设计方法通过讨论,让学生明白可以用两种结构化的方法和一种直接描述状态机的方法设计“111”序列检测器,使学生理解用HDL描述状态机的方法设计数字逻辑电路的优点,培养学生的计算思维。

总结时序逻辑电路设计方法,让学生领会数字电路设计会存在多种方案,要学会对不同方案进行评价,发展学生的高阶思维。

在此基础上,讲述钱学森“Nothing is final !”的故事,通过这个故事培养学生学无止境、追求真理的科学精神。

案例二:可编程逻辑器件的发展与应用思政育人目标1. 培养创新意识;2. 培养科技报国的使命担当。

思政育人案例设计教学内容:1. PLD器件的发展历程;2. CPLD与FPGA的特点;3. FPGA的开发与应用。

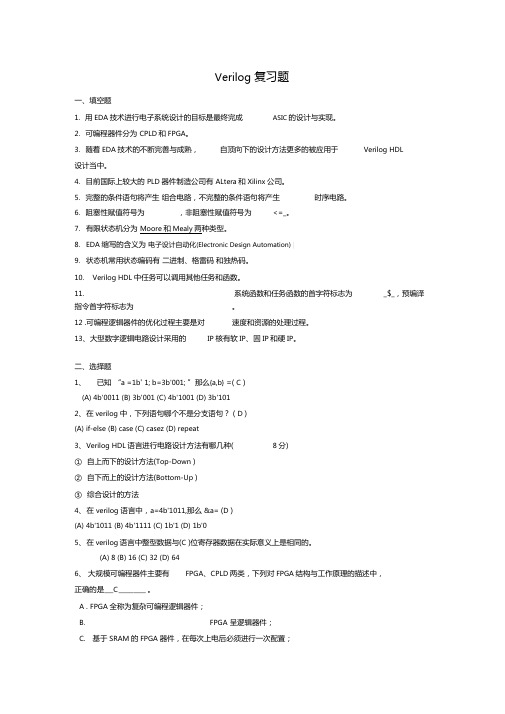

Verilog 复习题一、填空题1.用EDA技术进行电子系统设计的目标是最终完成ASIC的设计与实现。

2.可编程器件分为CPLD和FPGA。

3.随着EDA技术的不断完善与成熟,自顶向下的设计方法更多的被应用于Verilog HDL设计当中。

4.目前国际上较大的PLD器件制造公司有ALtera和Xilinx公司。

5.完整的条件语句将产生组合电路,不完整的条件语句将产生时序电路。

6.阻塞性赋值符号为,非阻塞性赋值符号为<=_。

7.有限状态机分为Moore和Mealy两种类型。

8.EDA缩写的含义为电子设计自动化(Electronic Design Automation) |9.状态机常用状态编码有二进制、格雷码和独热码。

10.Verilog HDL中任务可以调用其他任务和函数。

11.系统函数和任务函数的首字符标志为_$_,预编译指令首字符标志为。

12 .可编程逻辑器件的优化过程主要是对速度和资源的处理过程。

13、大型数字逻辑电路设计采用的IP核有软IP、固IP和硬IP。

二、选择题1、已知“a =1b' 1; b=3b'001; ”那么{a,b} =( C )(A) 4b'0011 (B) 3b'001 (C) 4b'1001 (D) 3b'1012、在verilog中,下列语句哪个不是分支语句? ( D )(A) if-else (B) case (C) casez (D) repeat3、V erilog HDL语言进行电路设计方法有哪几种( 8分)①自上而下的设计方法(Top-Down )②自下而上的设计方法(Bottom-Up )③综合设计的方法4、在verilog 语言中,a=4b'1011,那么&a= (D )(A) 4b'1011 (B) 4b'1111 (C) 1b'1 (D) 1b'05、在verilog语言中整型数据与(C )位寄存器数据在实际意义上是相同的。

哈尔滨工业大学电气工程及其自动化Harbin Institute of Technology数字电子技术基础课程名称:数字电子技术课程大作业设计题目:基于Verilog HDL语言的状态检测机设计院系:电气工程及其自动化班级:设计者:学号:指导教师:设计时间:2011.12.06哈尔滨工业大学数字电子技术基础状态检测机设计目录第一章引言 (3)1.1 状态机简介 (3)1.2 状态检测 (3)1.3V erilog HDL硬件描述语言简介 (4)1.4V erilog HDL硬件描述语言主要功能简介 (4)第二章状态检测机设计 (6)2.1 状态检测机设计要求 (6)2.2 状态检测机设计思路 (6)2.3 利用Quartus II软件仿真实现 (6)2.3.1 电路变量分析 (6)2.3.2 新建工程moore (7)2.3.3 设计输入 (7)2.3.4 Verilog语言描述 (7)2.3.5 仿真电路图 (8)2.3.6 状态装换图 (9)2.3.7创建波形文件 (9)2.3.8Quartus II仿真设置 (10)2.3.9仿真结果 (10)第三章总结 (11)参考文献 (12)第一章引言1.1状态机简介有限状态机是绝大部分控制电路的核心结构。

有限状态机是一种概念性机器,它能采取某种操作来响应一个外部事件。

具体采取的操作不仅能取决于接收到的事件,还能取决于各个事件的相对发生顺序。

之所以能做到这一点,是因为机器能跟踪一个内部状态,它会在收到事件后进行更新。

为一个事件而响应的行动不仅取决于事件本身,还取决于机器的内部状态。

另外,采取的行动还会决定并更新机器的状态。

这样一来,任何逻辑都可建模成一系列事件/状态组合。

状态机可归纳为4个要素,即现态、条件、动作、次态。

这样的归纳,主要是出于对状态机的内在因果关系的考虑。

“现态”和“条件”是因,“动作”和“次态”是果。

详解如下:①现态:是指当前所处的状态。

②条件:又称为“事件”,当一个条件被满足,将会触发一个动作,或者执行一次状态的迁移。

③动作:条件满足后执行的动作。

动作执行完毕后,可以迁移到新的状态,也可以仍旧保持原状态。

动作不是必需的,当条件满足后,也可以不执行任何动作,直接迁移到新状态。

④次态:条件满足后要迁往的新状态。

“次态”是相对于“现态”而言的,“次态”一旦被激活,就转变成新的“现态”了。

状态机可以分为以下两种类型:Moore型:输出是当前状态的函数。

Mealy型:输出是当前状态和输入的函数。

Mealy型状态机输出的变化先于Moore型状态机。

具体来说,Mealy型状态机的输出在输入变化的时候立刻发生变化;而Moore型状态机在输入变化后,还必须等到时钟的到来,时钟使状态发生变化时才导致输出的变化,所以比Mealy型状态机要多等待一个时钟周期。

1.2状态检测所谓状态检测,就是直接对分组的数据进行处理,并且结合前后分组的数据进行综合判断,然后决定是否允许该数据包通过。

状态检测技术的发展由来已久,早期的电报即可看作是基于状态检测的通讯手段。

近年来,随着计算机技术与互联网的不断发展,数据传送量已经变得越来越大,如何保证接收到的数据准确无误,已经受到人们越来越多的关注。

为了解决这一问题,科学家和工程师们已经研发出了很多种检错与纠错码,而这些技术的实现又肯定离不开状态检测技术的应用,因此状态检测技术在数据传送中起着十分重要的作用。

当然状态检测技术不仅应用于数据传送领域,还广泛应用于其他领域,这里不作赘述。

1.3V erilog HDL硬件描述语言简介Verilog HDL是一种硬件描述语言,用于从算法级、门级到开关级的多种抽象设计层次的数字系统建模。

被建模的数字系统对象的复杂性可以介于简单的门和完整的电子数字系统之间。

数字系统能够按层次描述,并可在相同描述中显式地进行时序建模。

Verilog HDL描述逻辑电路时常用3种描述方式,分别为:行为型描述、数据流型描述和结构型描述。

行为型描述指对行为与功能进行描述,它只描述行为特征,而没有涉及用什么样的逻辑电路来实现,因此是一种高级语言描述方式,具有很强的通用性与有效性;数据流型描述指通过assign连续赋值实现组合逻辑功能的描述方式;结构型描述指描述实体连接的结构方式,这里的实体一般指Verilog语言已定义的基元,也就是说结构型描述指利用Verilog语言已定义的基元描述逻辑电路的描述方式。

Verilog HDL的3种描述方式中,行为型描述方式注重整体与功能,语句可能更简略,但写出来的语句可能不能被硬件所实现,即不能被综合;结构型语句通常更容易被综合,但可能语句显得更复杂。

在实际开发中往往结合使用多种描述方法。

Verilog HDL语言不仅定义了语法,而且对每个语法结构都定义了清晰的模拟、仿真语义。

因此,用这种语言编写的模型能够使用Verilog仿真器进行验证。

语言从C编程语言中继承了多种操作符和结构。

Verilog HDL提供了扩展的建模能力,其中许多扩展最初很难理解。

但是,Verilog HDL语言的核心子集非常易于学习和使用,这对大多数建模应用来说已经足够。

当然,完整的硬件描述语言足以对从最复杂的芯片到完整的电子系统进行描述。

1.4V erilog HDL硬件描述语言主要功能简介*基本逻辑门,例如and、or和nand等都内置在语言中。

*用户定义原语(UDP)创建的灵活性。

用户定义的原语既可以是组合逻辑原语,也可以是时序逻辑原语。

* 开关级基本结构模型,例如pmos 和nmos等也被内置在语言中。

* 提供显式语言结构指定设计中的端口到端口的时延及路径时延和设计的时序检查。

* 可采用三种不同方式或混合方式对设计建模。

这些方式包括:行为描述方式—使用过程化结构建模;数据流方式—使用连续赋值语句方式建模;结构化方式—使用门和模块实例语句描述建模。

* Verilog HDL中有两类数据类型:线网数据类型和寄存器数据类型。

线网类型表示构件间的物理连线,而寄存器类型表示抽象的数据存储元件。

* 能够描述层次设计,可使用模块实例结构描述任何层次。

* 设计的规模可以是任意的;语言不对设计的规模(大小)施加任何限制。

* Verilog HDL不再是某些公司的专有语言而是IEEE标准。

* 人和机器都可阅读Verilog 语言,因此它可作为EDA的工具和设计者之间的交互语言。

* Verilog HDL语言的描述能力能够通过使用编程语言接口(PLI)机制进一步扩展。

PLI是允许外部函数访问Verilog 模块内信息、允许设计者与模拟器交互的例程集合。

* 设计能够在多个层次上加以描述,从开关级、门级、寄存器传送级(RTL)到算法级,包括进程和队列级。

* 能够使用内置开关级原语在开关级对设计完整建模。

* 同一语言可用于生成模拟激励和指定测试的验证约束条件,例如输入值的指定。

* Verilog HDL 能够监控模拟验证的执行,即模拟验证执行过程中设计的值能够被监控和显示。

这些值也能够用于与期望值比较,在不匹配的情况下,打印报告消息。

* 在行为级描述中,Verilog HDL不仅能够在RTL级上进行设计描述,而且能够在体系结构级描述及其算法级行为上进行设计描述。

* 能够使用门和模块实例化语句在结构级进行结构描述。

* Verilog HDL 的混合方式建模能力,即在一个设计中每个模块均可以在不同设计层次上建模。

* Verilog HDL 还具有内置逻辑函数,例如&(按位与)和|(按位或)。

* 对高级编程语言结构,例如条件语句、情况语句和循环语句,语言中都可以使用。

* 可以显式地对并发和定时进行建模。

* 提供强有力的文件读写能力。

* 语言在特定情况下是非确定性的,即在不同的模拟器上模型可以产生不同的结果;例如,事件队列上的事件顺序在标准中没有定义。

第二章状态检测机设计2.1 状态检测机设计要求设计一个基于Verilog HDL语言的状态检测机,其可以对输入的一串二进制数进行检测,用于检测序列中连续3个或3个以上的1。

当检测到3个或3个以上的1时机器输出1,否则输出0。

其状态转换图和状态转化表如下:图1状态检测机状态转换图表格1状态检测机状态转换表要求编写设计源程序,并生成仿真电路图和状态转换表,最后通过仿真实验验证设计的可靠性并给出仿真波形图。

2.2 状态检测机设计思路根据状态检测机的状态转换图,可以确定本系统应选用moore型状态机,即状态机的输出仅受当前状态的控制,而与输入无关。

2.3 利用Quartus II软件仿真实现2.3.1电路变量分析clk:时钟输入;din:检测输入;op:检测输出;state:状态输出。

2.3.2新建工程moore选择File>New Project Wizard,新建工程文件,输入工程名为moore(注意此处工程名与工程的顶层实体名必须一致)。

在Available devices列表中选择FPGA 型号EP2C70F896C6(本实验为仿真实验,此处不作硬性要求)。

2.3.3设计输入在当前工程下,选择File>New菜单,接着选择Verilog HDL File,单击OK,打开Text Editor。

选择File>Save as菜单,将文件保存到工程下,文件名为moore,保存类型为Verilog HDL File,则生成moore.v文件。

2.3.4 Verilog语言描述利用Verilog HDL语言编写的源程序如下:modulemoore(clk,din,op,state);inputclk,din;output op;output[1:0] state;reg op;reg[1:0] current_state,next_state;parameter S0=2'b00,S1=2'b01,S2=2'b10,S3=2'b11;assign state=current_state;always@(posedgeclk)begincurrent_state<=next_state;endalways@(current_state or din)begincase(current_state)S0:beginop=0;if(!din) next_state=S0;elsenext_state=S1;endS1:beginop=0;if(!din) next_state=S0;elsenext_state=S2;endS2:beginop=0;if(!din) next_state=S0;elsenext_state=S3;endS3:beginop=1;if(!din) next_state=S0;elsenext_state=S3;enddefault:beginop=0;next_state=S0;endendcaseendendmodule2.3.5仿真电路图保存上述源程序,进行综合编译。