- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

3.2.1 汇编语言:传送数据

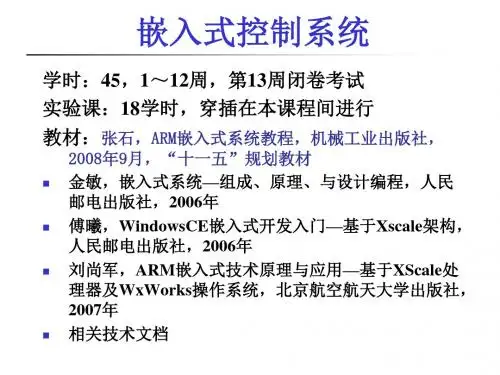

嵌入式控制系统原理及设计

• 多个加载和存储操作可以合并为一个指令,也就是多加载(LDM)和多存储(STM)。

实例

描述

LDMIA Rd!, <reg list> 从Rd指定的存储器位置读取多个字,每次传输后地址增加

STMIA Rd!, <reg list> 从Rd指定的存储器位置存储多个字,每次传输后地址增加

;存储后R8变为0x810(增加四个字节)

STMIA.W R8, {R0 – R3}

;存储后R8不变

• ARM微处理器也可以按照前序或后序的方式访问存储器,对于前序,寄存器中 为要调整的存储器地址,从存储器传输使用更新后的地址,例如:

LDR.W R0,[R1, #offset]!

;读取存储器[R1+offset],R1更新为R1+offset

SBC.W Rd, Rn, Rm

; Rd= Rn-Rm-borrow

RSB.W Rd, Rn, #immed ; Rd=#immed-Rn

RSB.W Rd, Rn, Rm

; Rd= Rm-Rn

MUL Rd, Rm

; Rd=Rd*Rm

MUL.W Rd, Rn, Rm

; Rd=Rn*Rm

UDIV Rd, Rn, Rm

3.2.1 汇编语言:传送数据

嵌入式控制系统原理及设计

表3.10 常用的存储器访问指令

实例 LDRB Rd, [Rn, #offset] LDRH Rd, [Rn, #offset] LDR Rd, [Rn, #offset] LDR Rd1, Rd2, [Rn, #offset] STRB Rd, [Rn, #offset] STRH Rd, [Rn, #offset] STR Rd, [Rn, #offset] STR Rd1, Rd2, [Rn, #offset]

; 当立即数是32位时,需要用两个指令来设置高半部分

和第半部分

MOVS.W R0, #0x789A ; 将R0的低半字设置为0x789A

MOVT.W R0, #0x2345 ; 将R0的高半字设置为0x2345

嵌入式控制系统原理及设计

3.2.2 LDR和ADR伪指令

• 伪指令LDR和ADR都可将寄存器设置为程序地址值,他们的语法和行为不同,对于 LDR,如果地址为程序地址值,汇编器会自动将LSB置1,例如:

描述

多种数据大小的前序加载指令(字、字节、半 字和双字)

带符号展开、多种数据大小的前序加载指令 (字节、半字)

多种数据大小的前序存储指令(字、字节、半 字和双字)

嵌入式控制系统原理及设计

3.2.1 汇编语言:传送数据

• 后序存储器访问指令则使用寄存器指定的基地址进行存储器传输,完成后才会将 地址更新,例如

指令

操作

SMULL RdLo, RdHi, Rn, Rm ; {RdHi, RdLo}=Rn*Rm SMLAL RdLo, RdHi, Rn, Rm ; {RdHi, RdLo}+=Rn*Rm

有符号数值的32位乘法 指令

UMULL RdLo, RdHi, Rn, Rm ; {RdHi, RdLo}=Rn*Rm UMLAL RdLo, RdHi, Rn, Rm ; {RdHi,RdLo}+=Rn*Rm

嵌入式控制系统原理及设计

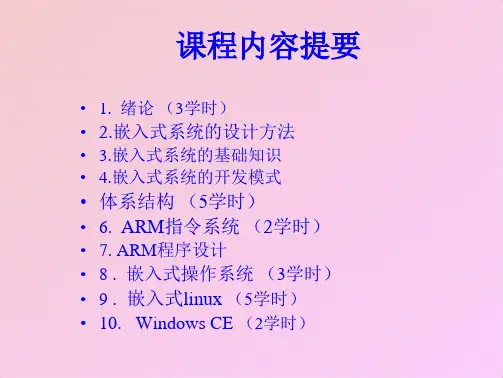

第3章 编程基础

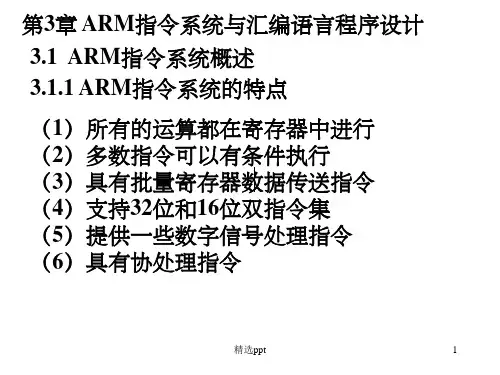

3.2 指令描述

3.2.1 汇编语言:传送数据

嵌入式控制系统原理及设计

处理器的一个最基本的功能为数据传送,对于ARM Cortex-M3,数据传送支 持如下方式: (1)寄存器间传送数据; (2)存储器和寄存器间传送数据; (3)寄存器和特殊寄存器间传送数据; (4)将立即数送至寄存器。

LDR R0, =address1

; 将R0设置为0x4001

…

address1

; 这里的地址是0x4000

MOV R0, R1

; address1包含程序代码

• 执行的结果是LDR指令将0x4001放入R1,并且其最低位置1表示Thumb代码。

嵌入式控制系统原理及设计

3.2.2 LDR和ADR伪指令

描述 从存储器位置Rn + offset处读取字节 从存储器位置Rn + offset处读取半字 从存储器位置Rn + offset处读取字 从存储器位置Rn + offset处读取双字 往存储器位置Rn + offset处存储字节 往存储器位置Rn + offset处存储半字 往存储器位置Rn + offset处存储字 往存储器位置Rn + offset处存储双字

; Rd=Rn&#immed

AMD.W Rd, Rn, Rm

• 除了ARSR寄存器外,其他的特殊寄存器在特权模式下都不能访问。

嵌入式控制系统原理及设计

3.2.1 汇编语言:传送数据

• 将立即数送入寄存器应使用MOVS指令,例如:

MOVS R0, #0x12

; 将R0设置为0x12(适用于8位或以下的立即数)

MOVS.W R0, #0x789A ; 将R0设置为0x789A(适用于超过8位但小于32位的立即数)

无符号数值的32位乘法 指令

3.2.3 汇编语言:处理数据

嵌入式控制系统原理及设计

ARM Cortex-M3支持逻辑运算,这些指令包括AND(与)、ORR(或)以

及移位和循环移位等,表3.16给出了常见的逻辑算算指令。

指令

AND Rd, Rn

; Rd=Rd&Rn

AND.W Rd, Rn, #immed

SUB Rd, Rn, Rm

; Rd=Rn-Rm

SUB Rd, #immed

; Rd=Rd-#immed

SUB Rd, Rn, #immed

; Rd=Rn-#immed

SBC Rd, Rm

; Rd=ቤተ መጻሕፍቲ ባይዱd-Rm-borrow

SBC.W Rd, Rm, #immed ; Rd=Rn-#immed-borrow

list>

表明为32位Thumb-2指令)

STMDB.W Rd(!), <reg 从Rd指定的存储器位置存储多个字,每次传输后地址减小(.W

3.2.1 汇编语言:传送数据

嵌入式控制系统原理及设计

• 指令中的(!)指定寄存器Rd是否在指令完成后更新。例如:若R8等于0x8000,则

STMIA.W R8!, {R0 – R3}

实例

描述

LDR.W Rd, [Rn], #offset LDRB.W Rd, [Rn], #offset LDRH.W Rd, [Rn], #offset

多种数据大小的前序加载指令(字、字节、半字 和双字)

LDRD.W Rd1, Rd2, [Rn], #offset LDRSB.W Rd, [Rn], #offset LDRSH.W Rd, [Rn], #offset

嵌入式控制系统原理及设计

3.2.1 汇编语言:传送数据

• PUSH和POP是栈的存储器操作,例如

PUSH {R0, R4-R7, R9} ;将R0,R4-R7,R9压栈

POP {R2,R3}

;将R2和R3出栈

• 通常PUSH指令要用一个对应的POP指令,并且寄存器列表相同。但在异常处理 中使用POP时需要注意,例如

ADD.W R0, R1, R2 ; R0=R1+R2

嵌入式控制系统原理及设计

3.2.3 汇编语言:处理数据

• 传统的Thumb指令语法下,当使用16位Thumb代码时,ADD指令可以修 改PSR中的标志。

• 但32位Thumb-2代码则可以修改一个标志或者保持不变。如果下面的操 作以来标志的话,要区分这两种不同的操作,就需使用s后缀了:

LDR.W R0, [R1], #offset

;读取存储器[R1],R更新为R1+offset

• 在使用后序指令时,无须使用“!”符号,因为所有的后序指令都会更新基地址 寄存器,而前序访问则可以选择是否更新基地址寄存器。

嵌入式控制系统原理及设计

3.2.1 汇编语言:传送数据

• 后序存储器访问指令实例如表3.13所示,也可用于多种大小。

嵌入式控制系统原理及设计

3.2.3 汇编语言:处理数据

• ARM Cortex-M3提供了许多不同的指令用于数据处理,这些数据操作指 令可以有多种指令格式。

• 例如,ADD指令可以在寄存器间或者寄存器和立即数间执行:

ADD R0, R0, R1

; R0=R0+R1

ADD R0, R0, #0x12 ; R0=R0+0x12

• “!”的使用表明基地址寄存器R1会更新,“!”是可选的,若没有使用,指令 会被当作从基地址寄存器偏移地址处开始的普通存储器传输。 。

嵌入式控制系统原理及设计

3.2.1 汇编语言:传送数据

• 前序存储器访问指令包括各种大小的加载和存储指令,如表3.12所示。

实例 LDR.W Rd, [Rn, #offset] LDRB.W Rd, [Rn, #offset] LDRH.W Rd, [Rn, #offset] LDRD.W Rd1, Rd2, [Rn, #offset] LDRSB.W Rd, [Rn, #offset] LDRSH.W Rd, [Rn, #offset] STR.W Rd, [Rn, #offset] STRB.W Rd, [Rn, #offset] STRH.W Rd, [Rn, #offset]

3.2.1 汇编语言:传送数据

嵌入式控制系统原理及设计

• 寄存器间传送数据的命令为MOV,例如:将数据从寄存器R3送入寄存器 R8的指令可以写为: