cadence16.6差分约束规则

- 格式:docx

- 大小:1.94 MB

- 文档页数:27

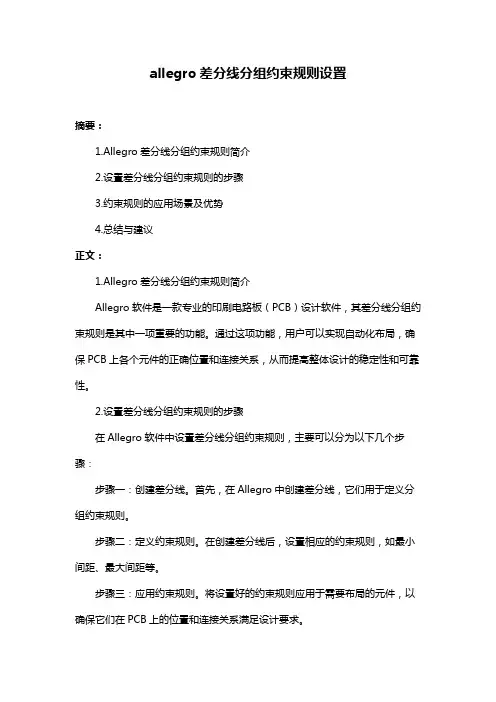

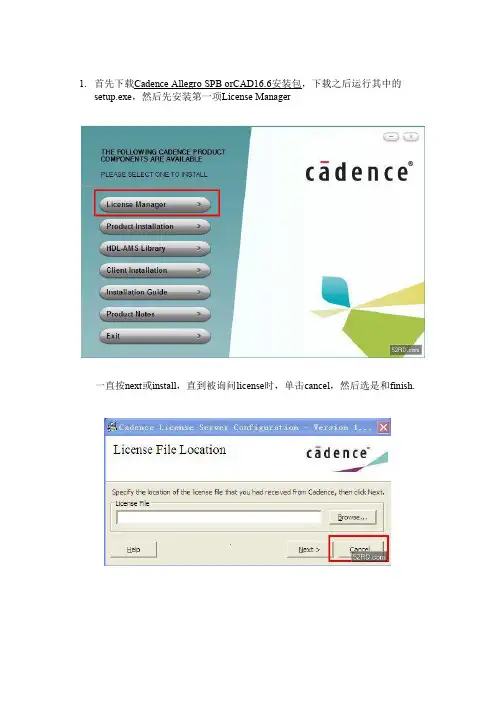

Cadence_SPB16.5、16.6的安装、破解、打补丁图⽂教程SPB16.5/6基于pubkey1.30的安装及破解注意:我的电脑是win7旗舰版,破解成功,请关闭防⽕墙和杀毒软件,16.5和16.6均破解成功了⾸先,安装license manager,步骤如下:点击LicenseManager。

选择接受许可,点击Next选择LicenseManager安装⽬录,根据个⼈习惯修改吧。

选择要安装的模块,点击Next。

到这⾥要刹车,直接Cancel。

最后完成安装,点击Finish接下来,要安装Cadence的主要⼯具:Product Installation。

安装Product Installation,⼀路Next到下图。

注:选择customs和anyone who……选择安装⽬录,路径如上图所⽰,点击Next。

预览安装信息,不满意的点击Back修改,感觉ok的点击Next。

点击Install开始安装。

耐⼼等待。

⼀般安装到最后,出现要寻找firewall的允许项添加什么的,需要等很长⼀会,⼀开始以为软件装的不动了,不想⼀会⼜开始装了。

这⾥不⽤管,直接Next。

要查看产品信息了就在选中该项,不需要了直接点击Finsh,就完成了安装⼯作。

⼀、破解步骤。

1、在任务管理器中确认⼀下是否有这两个进程,有就结束掉,即cdsNameServer.exe和cdsMsgServer.exe,没有就算了。

说明:看来没有。

2、把安装⽬录下的SPB_16.5/tools/pspice⽬录下的orSimSetup.dll剪切出来找个地⽅先放着不理(待完成破解后再拷回原来的地⽅,如果不⽤仿真部分删掉也⽆所谓)。

按照这个说的做吧。

3、解压本⽂档第⼀页中的pubkey.rar⽂件,把pubkey、pubkey1.3.exe和lLicenseManagerPubkey.bat放到Cadence\LicenseManager⽬录下并运⾏LicenseManagerPubkey.bat。

一、背景介绍CADENCE16.6是一款专业的电子设计自动化软件,广泛应用于集成电路设计和电子系统设计领域。

本文将总结我在自学CADENCE16.6过程中的体会和心得。

二、学习经历1. 学习动机在电子设计领域,CADENCE16.6是一个非常重要的工具,具备强大的功能和广泛的应用范围。

我希望通过自学掌握这一工具,提升自己在电子设计领域的技能和竞争力。

2. 学习方法我通过阅读冠方文档、观看视瓶教程、参加上线培训等方式进行学习。

在学习过程中,我注重理论与实践相结合,不断尝试实际项目并总结经验。

三、学习收获1. 理论知识通过学习,我掌握了CADENCE16.6的基本概念、原理和操作方法,包括电路仿真、布局与布线、模拟与数字信号处理等方面的知识。

2. 实际应用我在实际项目中应用CADENCE16.6进行电路设计与仿真,包括模拟电路和数字电路方面的设计。

通过实践,我深化了对软件的理解,并且提升了自己的实际操作能力。

3. 问题与解决在学习过程中,我遇到了一些难题和技术挑战,如仿真结果不符合预期、布局与布线不理想等。

通过查阅资料、询问专业人士等方式,我逐一解决了这些问题,并积累了丰富的经验。

四、自学心得1. 坚持不懈学习CADENCE16.6需要付出大量的时间和精力,需要耐心和恒心。

我坚持每天花一定的时间进行学习和实践,不断积累经验和提升能力。

2. 多角度学习CADENCE16.6涉及的知识面广泛,需要从不同的角度进行学习和理解。

我通过阅读冠方文档、参加培训、观看案例分析等方式进行多角度学习,从而加深对软件的理解。

3. 实践为主在学习过程中,理论与实践相辅相成。

我注重将所学知识应用于实际项目中,通过实践来加深理解、巩固知识和提升技能。

4. 不断总结在实践中,我不断总结经验和教训,形成自己的经验积累和技术规范。

这些总结能够帮助我更好地应对各种问题和挑战。

五、展望CADENCE16.6作为一个复杂而强大的电子设计工具,我深知自己的掌握还只是皮毛。

cadence布线规则和技巧Cadence布线规则和技巧在电子设计领域,Cadence是一种常用的EDA工具,被广泛用于电路设计和布线。

布线是电路设计的重要环节,它决定了电路的性能和稳定性。

本文将介绍一些Cadence布线规则和技巧,帮助工程师更好地进行电路布线。

1. 保持信号完整性:在布线过程中,保持信号完整性是至关重要的。

信号完整性可以通过遵循一些规则来实现。

首先,尽量减少信号线的长度,以减少信号传输的延迟和损耗。

其次,要避免信号线之间的串扰,可以采用合适的间距和屏蔽措施。

最后,要确保信号线的阻抗匹配,以避免反射和干扰。

2. 地线布线规则:地线是电路中至关重要的信号回路。

在进行地线布线时,需要注意以下几点。

首先,地线应尽可能宽,以降低电阻和电流密度。

其次,地线应尽量与信号线平行,以减少干扰。

最后,地线应尽量靠近信号线,以减少回环面积和电感。

3. 电源线布线规则:电源线是供电的关键部分,其布线也需要一些规则。

首先,电源线应尽量短,以减少电源噪声和电压降。

其次,电源线应尽量宽,以降低电阻和电流密度。

最后,电源线应尽量避免与信号线和地线交叉,以减少干扰。

4. 时钟线布线规则:时钟线在数字电路中起着关键作用,其布线需要一些特殊规则。

首先,时钟线应尽量短,以降低时钟偏移和延迟。

其次,时钟线应尽量避免与其他信号线交叉,以减少串扰。

最后,时钟线应尽量靠近其相关的信号线,以减少时钟抖动和功耗。

5. 差分信号布线规则:差分信号是一种常用的抗干扰技术,在布线时也需要一些特殊规则。

首先,差分信号的两条线应尽量相等,以保持差分模式的平衡。

其次,差分信号的两条线应尽量靠近,以减少共模噪声。

最后,差分信号的两条线应尽量避免与其他信号线交叉,以减少串扰。

6. 规避布线冲突:在布线过程中,可能会出现一些冲突,如信号线之间的交叉、信号线与电源线的交叉等。

为了规避这些冲突,可以使用一些技巧。

例如,可以通过增加层次来避免交叉,将信号线和电源线分布在不同的层次上。

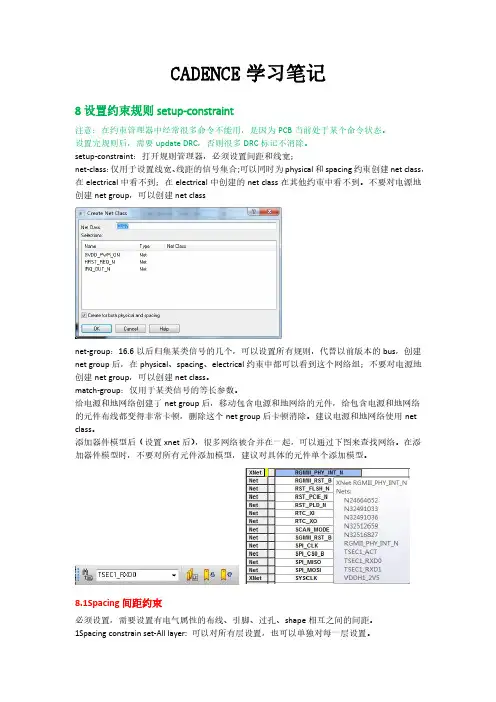

CADENCE学习笔记8设置约束规则setup-constraint注意:在约束管理器中经常很多命令不能用,是因为PCB当前处于某个命令状态。

设置完规则后,需要update DRC,否则很多DRC标记不消除。

setup-constraint:打开规则管理器,必须设置间距和线宽;net-class:仅用于设置线宽、线距的信号集合;可以同时为physical和spacing约束创建net class,在electrical中看不到;在electrical中创建的net class在其他约束中看不到。

不要对电源地创建net group,可以创建net classnet-group:16.6以后归集某类信号的几个,可以设置所有规则,代替以前版本的bus,创建net group后,在physical、spacing、electrical约束中都可以看到这个网络组;不要对电源地创建net group,可以创建net class。

match-group:仅用于某类信号的等长参数。

给电源和地网络创建了net group后,移动包含电源和地网络的元件,给包含电源和地网络的元件布线都变得非常卡顿,删除这个net group后卡顿消除。

建议电源和地网络使用net class。

添加器件模型后(设置xnet后),很多网络被合并在一起,可以通过下图来查找网络。

在添加器件模型时,不要对所有元件添加模型,建议对具体的元件单个添加模型。

8.1Spacing间距约束必须设置,需要设置有电气属性的布线、引脚、过孔、shape相互之间的间距。

1Spacing constrain set-All layer:可以对所有层设置,也可以单独对每一层设置。

在右侧表格内,default行连续选择多个表格,输入数值,然后按enter键可以实现多个表格统一赋值。

一般间距不要小于6mil,一般板厂都能加工。

注意此间距是走线边沿间的安全间距,不是走线中心间距。

allegro差分线分组约束规则设置【最新版】目录1.Allegro 软件概述2.差分线分组约束规则的概念3.差分线分组约束规则的设置方法4.差分线分组约束规则的应用实例5.总结正文一、Allegro 软件概述Allegro 是一款专业的 EDA(电子设计自动化)软件,广泛应用于 PCB (印刷电路板)设计领域。

通过 Allegro 软件,设计人员可以轻松实现电路原理图的绘制、PCB 布局布线以及各种设计规则的检查等功能。

在PCB 设计过程中,设计规则的合理设置是保证电路板性能和可靠性的关键。

二、差分线分组约束规则的概念差分线分组约束规则是 Allegro 软件中一种用于控制差分线(Differential Pair)布局布线的设计规则。

差分线是指在高速信号传输过程中,通过两条走线进行数据传输,以降低外部干扰和信号衰减的影响。

在实际应用中,为了保证差分线的传输性能,需要对差分线的布局布线进行分组约束。

三、差分线分组约束规则的设置方法在 Allegro 软件中,设置差分线分组约束规则的方法如下:1.打开 Allegro 软件,载入需要设置差分线分组约束规则的 PCB 设计文件。

2.在顶部菜单栏中,依次点击“规则”(Rules)→“约束规则”(Constraints)→“新建”(New),打开“新建约束规则”对话框。

3.在“新建约束规则”对话框中,设置差分线分组约束规则的名称、描述等信息,然后点击“添加”(Add)按钮。

4.在弹出的“添加约束规则”对话框中,设置差分线分组约束规则的具体参数,包括差分线分组名称、走线宽度、间距等,点击“确定”(OK)按钮。

5.在“新建约束规则”对话框中,点击“确定”(OK)按钮,完成差分线分组约束规则的设置。

四、差分线分组约束规则的应用实例在实际的 PCB 设计过程中,我们可以通过以下实例应用差分线分组约束规则:假设某高速信号传输系统,需要设计两条差分线,分别为 A 和 B。

allegro差分线分组约束规则设置摘要:1.Allegro差分线分组约束规则简介2.设置差分线分组约束规则的步骤3.约束规则的应用场景及优势4.总结与建议正文:1.Allegro差分线分组约束规则简介Allegro软件是一款专业的印刷电路板(PCB)设计软件,其差分线分组约束规则是其中一项重要的功能。

通过这项功能,用户可以实现自动化布局,确保PCB上各个元件的正确位置和连接关系,从而提高整体设计的稳定性和可靠性。

2.设置差分线分组约束规则的步骤在Allegro软件中设置差分线分组约束规则,主要可以分为以下几个步骤:步骤一:创建差分线。

首先,在Allegro中创建差分线,它们用于定义分组约束规则。

步骤二:定义约束规则。

在创建差分线后,设置相应的约束规则,如最小间距、最大间距等。

步骤三:应用约束规则。

将设置好的约束规则应用于需要布局的元件,以确保它们在PCB上的位置和连接关系满足设计要求。

步骤四:检查与修复。

在布局过程中,不断检查PCB设计是否符合约束规则,如有问题,及时进行修复。

3.约束规则的应用场景及优势差分线分组约束规则在以下场景中具有显著优势:- 提高设计效率:通过自动化布局,设计者可以更快地完成PCB设计,减少重复性工作。

- 保证连接可靠性:约束规则确保了元件之间的正确连接,降低了故障风险。

- 优化电路性能:合理的布局可以降低信号干扰,提高电路性能。

- 易于维护:约束规则使得设计更加规范,便于后期维护和升级。

4.总结与建议差分线分组约束规则在Allegro软件中发挥着重要作用,能够帮助设计者实现自动化布局,提高PCB设计的质量。

在使用过程中,建议设计者熟练掌握约束规则的设置方法,并根据实际需求进行调整。

1.首先下载Cadence Allegro SPB orCAD16.6安装包,下载之后运行其中的setup.exe,然后先安装第一项License Manager一直按next或install,直到被询问license时,单击cancel,然后选是和finish.2.接下来安装Product,直到安装结束(这个时间有点长)装完成后,点Exit退出3.按ctrl+alt+delete打开任务管理器,查看进程里是否有cdsNameServer.exe或cdsMsgServer.exe,一般都没有,如果有将其结束掉4.把安装路径下的cadence\SPB_16.6\tools\pspice目录下的orsimsetup.dll剪切到别的地方(千万不要删除该文件,否则不能破解(破解结束后,步骤11用))6、把crack文件夹中的pubkey、pubkey1.3.exe和lLicenseManagerPubkey.bat放到Cadence\LicenseManager目录下并运行LicenseManagerPubkey.bat;7、把crack文件夹中的pubkey、pubkey1.3.exe和ToolsPubkey.bat放到Cadence\SPB_16.5\tools目录下并运行ToolsPubkey.bat,如果ToolsPubkey.bat运行的时候提示pubkey命令窗口出现任何can not open ……或者是diff pubkey等字样(出线的话,相应的工具就不能破解),请留意一下,把pubkey、pubkey1.3.exe和ToolsPubkey.bat,放置相应tool的目录下并运行ToolsPubkey.bat,8. 把license_gen文件夹里面的src.lic所有的cdslmd 16.5改成16.6(对应版本号,已经改好了),双击licgen.bat生成新的license.lic,LIC位置随便放,使用License Server Configuration Utility指定新生成的license.lic并启动服务(留意hostname必须要为计算机名)在弹出的对话框中点browse...指向license_gen文件夹里面的license.lic,点next在接下来弹出的窗口中,把host name改为你计算机的完整计算机名称(在我的电脑上点右键,然后点属性——计算机名就看到了),之后点next9. 在电脑开始菜单中的程序里找到Licenseclient configuration Unility,点击运行后,不用填什么直接点next,最后点finish10. 在电脑开始菜单中的程序里找到LmTools,点击运行在弹出的窗口里找到Config Services项,在Path to the license file项的那一行里,点Browes指向刚才新生成的license.lic,之后再点Save Service。

差分约束算法差分约束算法(Difference Constraint Algorithm)是一种用于求解差分约束系统的方法,差分约束系统是一种特殊的线性约束系统,其中约束关系为“某个变量的值与另一个变量的差的绝对值不超过某个常数”。

差分约束算法的基本思想是通过对约束条件进行适当的转换,构造一个有向图,并利用拓扑排序的方法求解变量的取值范围。

具体步骤如下:1. 将差分约束系统中的每个差分约束关系转化为两个线性约束关系。

例如,对于约束 a - b ≤ c,可以将其转化为a ≤ b + c 和b ≤ a - c;对于约束 a - b ≥ c,可以转化为a ≥ b +c 和b ≥ a - c。

2. 根据转化后的约束关系构造一个有向图,图中的每个变量表示一个节点,约束关系表示节点间的有向边。

对于每个约束关系a ≤ b + c,构造一条从节点 a 到节点 b 的有向边,边的权重为 c;对于每个约束关系a ≥ b + c,构造一条从节点 b 到节点a 的有向边,边的权重为 c。

3. 对构造的有向图进行拓扑排序,得到拓扑排序的顺序。

4. 根据拓扑排序的顺序,依次计算每个节点的取值范围。

对于每个节点 a,初始化其取值范围为负无穷大到正无穷大。

对于节点 a 的每个后继节点 b,更新节点 b 的取值范围为节点 a 的取值范围加上边的权重。

重复此步骤,直到没有节点的取值范围发生变化,即达到稳定状态。

5. 根据计算得到的每个节点的取值范围,判断差分约束系统是否可解。

如果存在某个节点的取值范围为负无穷大到正无穷大,则差分约束系统无解;否则,取值范围即为差分约束系统的解。

差分约束算法的时间复杂度为 O(nm),其中 n 是变量的个数,m 是约束关系的个数。

这种算法通常用于求解动态最短路径等问题,具有较高的效率。

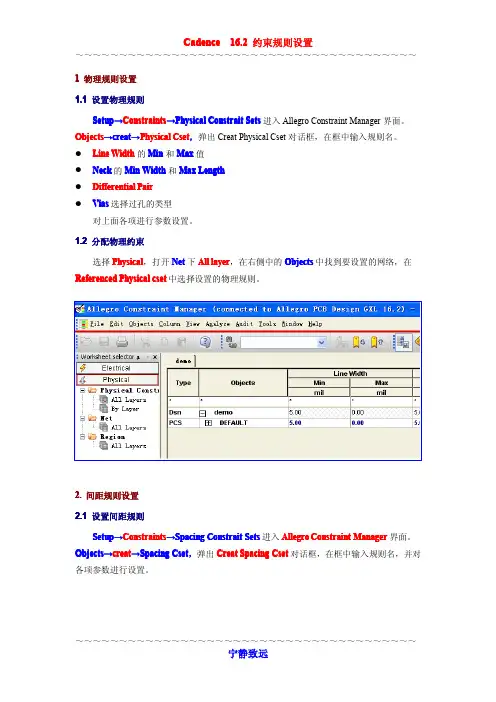

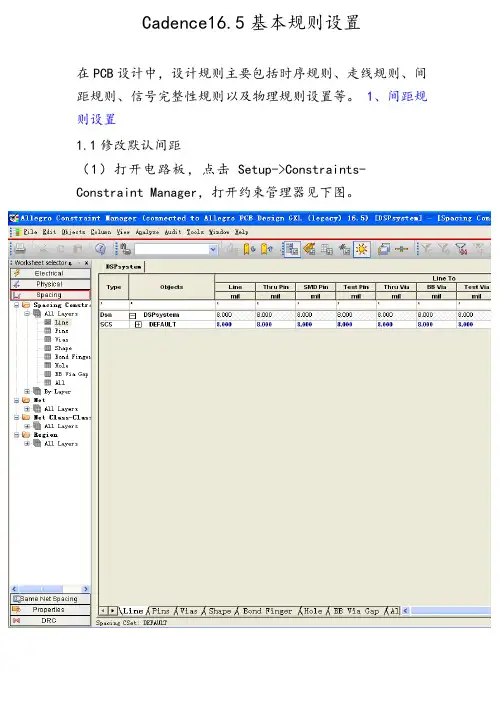

Cadence16.5 基本规则设置在PCB 设计中,设计规则主要包括时序规则、走线规则、间距规则、信号完整性规则以及物理规则设置等。

1、间距规则设置1.1 修改默认间距(1)打开电路板,点击 Setup->Constraints-Constraint Manager,打开约束管理器见下图。

左侧为Worksheet selector 栏,可以选择要设置约束类型Electrical 设置电气约束,Physical 设置物理约束,Spacing 设置间距约束,Same Net Spacing 设置Net to Net Spacing 之间的约束规则,Properties 设置元件或网络属性,DRC 显示DRC 错误信息。

(2)、选择Spacing Constraint Set 前加号-打开All layer,选择Line,右侧表格的数据表示Line 到Line,Thru Pin 等的距离,默认距离为5mil,我们这里设成6mil,双击即可直接输入数值,见下图在管理器下方有很多种类型,刚才我们只设置了线到其他的距离,还可以设置管脚、过孔等到其他的距离,见下图(3)、在左侧Worksheet selector 栏选择All 将所有默认间距值改为6,见下图1.2 设定间距规则假定网络 VCC1V2 和VCC3V3需要比前面设置的间距更大。

(1)、选择Objects-Create-Spacing Cset,见下图在弹出的Create Spacing Cset 对话框中输入10mil_space 如右图所示(2)、单击OK,在Objects 栏出现新的规则吗10mil_space,改变表格区域的值全为10,见下图1.3 分配约束(1)、选择Spacing-打开Net 前加号,打开All layer,选择Line,如下图所示(2)、在右侧工作窗口Objects 栏下找到网络VCC1V2,单击Referenced Spacing Cset 属性,出现一个下拉框,在下拉框中选择我们刚才设置的约束10mil_space,同样VCC3V3 同样设置,见下图。

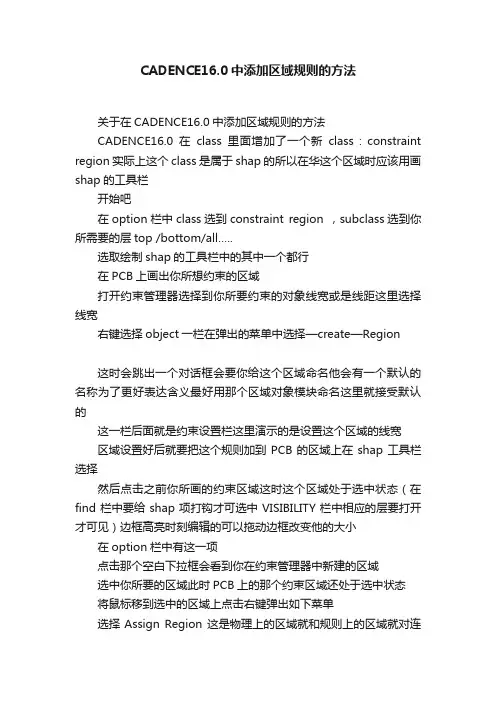

CADENCE16.0中添加区域规则的方法关于在CADENCE16.0中添加区域规则的方法CADENCE16.0在class里面增加了一个新class : constraint region 实际上这个class是属于shap的所以在华这个区域时应该用画shap的工具栏开始吧在option栏中class选到constraint region ,subclass选到你所需要的层top /bottom/all…..选取绘制shap的工具栏中的其中一个都行在PCB上画出你所想约束的区域打开约束管理器选择到你所要约束的对象线宽或是线距这里选择线宽右键选择object一栏在弹出的菜单中选择—create—Region这时会跳出一个对话框会要你给这个区域命名他会有一个默认的名称为了更好表达含义最好用那个区域对象模块命名这里就接受默认的这一栏后面就是约束设置栏这里演示的是设置这个区域的线宽区域设置好后就要把这个规则加到PCB的区域上在shap工具栏选择然后点击之前你所画的约束区域这时这个区域处于选中状态(在find栏中要给shap项打钩才可选中VISIBILITY栏中相应的层要打开才可见)边框高亮时刻编辑的可以拖动边框改变他的大小在option栏中有这一项点击那个空白下拉框会看到你在约束管理器中新建的区域选中你所要的区域此时PCB上的那个约束区域还处于选中状态将鼠标移到选中的区域上点击右键弹出如下菜单选择Assign Region 这是物理上的区域就和规则上的区域就对连接了此时再用information按钮查看物理区域属性会有一条是区域组名再画线你将会看到区域内外有不同的线宽End这种是先画物理约束区域-- 再定区域规则—再连接也可以先定规则---在物理区域的同时指明约束规则16.0对约束规则定义更加细功能也更强设置过程也更加简单我先以为16.0把这个功能给丢弃了按道理也不会cadence这么大的工具不会这样做。

Cadence SPB15.7 快速入门视频教程目录第1讲课程介绍,学习方法,了解CADENCE软件第2讲创建工程,创建元件库第3讲分裂元件的制作方法区别(Ctrl+B、Ctrl+N切换Part)点击View,点击Package可以显示所有的元件Part1、homogeneous 和heterogeneous2、创建homogeneous类型元件3、创建heterogeneous类型元件第4讲正确使用heterogeneous类型的元件增加packeg属性。

点击Option,选择Part Properties,选择new,增加属性。

用于在原理图中确定同一块的元件。

1、可能出现的错误2、出现错误的原因3、正确的处理方法第5讲加入元件库,放置元件1、如何在原理图中加入元件库2、如何删除元件库3、如何在元件库中搜索元件4、放置元件5、放置电源和地第6讲同一个页面内建立电气互连(设置索引编号,Tools里面,Annotate来设置)1、放置wire,90度转角,任意转角(画线时按住Shift)2、wire的连接方式3、十字交叉wire加入连接点方法,删除连接点方法(快捷键J)4、放置net alias方法(快捷键n)5、没有任何电气连接管脚处理方法(工具栏Place no Conection)6、建立电气连接的注意事项第7讲总线的使用方法1、放置总线(快捷键B)2、放置任意转角的总线(按住Shift键)3、总线命名规则(LED[0:31],不能数字结尾)4、把信号连接到总线(工具栏Place Bus entry 或者E)5、重复放置与总线连接的信号线(按住Ctrl向下拖)6、总线使用中的注意事项7、在不同页面之间建立电气连接(工具栏Place off-page connector)第8讲browse命令的使用技巧(选中dsn文件,选择Edit中的browse)1、浏览所有parts,使用技巧(浏览元件<编号,值,库中的名字,库的来源>,双击元件可在原理图上找到元件)2、浏览所有nets,使用技巧(浏览网络)3、浏览所有offpage connector,使用技巧(页面间的连接网络,一般一个网络至少会在两个页面中出现)4、浏览所有DRC makers,使用技巧(DRC检测)第9讲搜索操作使用技巧(右上脚的望远镜那,按下下拉三角可以设置搜索的范围)1、搜索特定part(查找元件)2、搜索特定net(查找网络)3、搜索特定power(查找电源)4、搜索特定flat nets(将搜索的网络在一个原理图中都高亮显示)第10讲元件的替换与更新(打开Designer Cache,选中元件,右键打击,选择Replace Cache或者Update Cache)1、replace cache用法(New Part Name 选择替换元件,Part Library 库的位置,Action 1、保存原理图属性(比如编号),2、去除所有属性)2、update cache用法(同replace Cache,如果更改了元件,可以用updata把最新的元件模型更新进来)3、replace cache与pdate cache区别(replace可以更改元件与元件库的连接关系,封装属性只能用replace的不保存属性来更新封装信息)第11讲对原理图中对象的基本操作1、对象的选择2、对象的移动(默认是保持现有连接的移动,可以按住Alt可以断开连接),(断开后如不能移动连接:打开菜单栏Options,打开prefrence,选择Miscellaneous,勾选右下角wire Drag)3、对象的旋转(选中元件,然后按住R键)4、对象的镜像翻转(选中元件,选择菜单栏edit中的mirror(文本和位图不能镜像))5、对象的拷贝、粘贴、删除(按住Ctrl,然后选中元件并拖动)第12讲1、修改元件的V ALUE及索引编号方法(双击V ALUE或者索引编号就可以直接改了)2、属性值位置调整(选中并拖动)3、放置文本(菜单栏place,text(换行按住Ctrl和Enter)。

cadence中差分线的标注-回复什么是CADENCE中差分线的标注?在电路设计和集成电路产业中,CADENCE是非常著名且广泛使用的EDA 软件之一。

而在CADENCE中,差分线的标注是非常重要的一步,它能够帮助设计师更好地理解和分析电路中信号的运行方式和特性。

差分线是指在电路设计中将信号线分为两条平行走向的线路,其中一条为正向信号线路,另一条为反向信号线路。

这种设计方式常用于高速差分信号的传输,例如USB、SATA、PCIe等。

差分线设计能够减轻电磁干扰,提高信号的可靠性和抗干扰能力。

为了更好地理解和分析差分线的特性,CADENCE中提供了一系列标注功能,帮助设计师更好地了解差分信号的驱动方式、阻抗匹配、延迟等参数。

下面将一步一步回答关于CADENCE中差分线标注的问题。

第一步:电路设计与搭建要使用CADENCE中的差分线标注功能,首先需要进行电路设计与搭建。

这涉及到使用CADENCE提供的电路元件库,选择合适的元件进行组合,建立电路原理图。

在电路搭建过程中,需要选择合适的元件进行差分线设计,通常有差分对、电压比较器、差分放大器等。

第二步:差分线的布局与绘制在电路原理图中,需要对差分线进行布局与绘制。

差分线通常是平行的两条线路,它们之间的距离取决于设计要求和电路的特性参数。

在CADENCE 中,可以使用标准的线段绘制工具来绘制差分线,并保持它们的平行性。

第三步:添加差分线的标注一旦差分线的布局和绘制完成,接下来需要添加差分线的标注。

标注可以帮助设计师更好地理解差分线的特性和参数。

在CADENCE中,可以通过选择差分线并使用标注工具来添加标注。

标注可以包括线宽、长度、电阻、电容等参数。

第四步:差分线的参数分析与优化一旦差分线的标注添加完成,设计师可以根据标注信息进行参数分析和优化。

通过测量差分线的长度、电阻、电容等参数,可以评估差分线的传输特性和信号完整性。

如果需要改进差分线的性能,设计师可以通过调整线宽、改变线路布局、添加终端电阻等方法来进行优化。

差分线布线规则设置1.差分线对称性:差分线两侧的引脚和电路元件布局应保持对称。

这可以减少差分线之间的不对称模式耦合和电磁辐射。

2.差分线长度匹配:差分线的长度应保持匹配,以确保同时到达终端。

如果差分线长度不匹配,会产生时间延迟不一致,降低信号完整性。

3.差分线宽度和间距:差分线的宽度和间距应根据设计要求和信号速度来选择。

宽度和间距的选择会影响差分线的阻抗匹配和互联层与控制层之间的电场耦合。

4.反噪声短接:差分线的末端应通过反噪声短接到地,以减少终端反射和信号回波。

这可以通过添加电容、电阻和电感等元件来实现。

5.差分阻抗控制:差分线的阻抗应根据设计要求来控制。

为了保持阻抗匹配,可以通过调整差分线的宽度、间距和布线层的厚度来实现。

6.弯曲和过渡:差分线在转弯和过渡区域需要遵循一定的规则。

弯曲半径应足够大,以减少信号的损失和失真。

过渡区域应尽可能短,并使用过渡导线来平滑过渡。

7.差分线与其他线的保持距离:差分线与其他线(如功率线和时钟线)之间应保持一定的距离,以减少互相之间的电磁干扰。

8.差分线与地线的布局:差分线和地线之间应尽可能保持平行,并且在布局上应注意避免高频回路的闭合路径,以减少环路电流。

9.差分线层选择:在多层电路板设计中,差分线的布局有多种选择。

差分线应尽量选用内层布线,以减少对外界的电磁辐射和抗干扰能力的提高。

10.差分线屏蔽:在一些特殊的应用中,如高速信号传输,可以考虑在差分线上添加屏蔽层或屏蔽罩,以进一步减少电磁干扰和提高信号完整性。

在进行差分线布线时,可以借助专业的电路板设计软件,如Altium Designer、Cadence Allegro等,来自动生成差分线布线规则。

这些软件通常提供了丰富的设置选项和规则检查功能,可以帮助设计工程师进行布线规则设置和布线优化。

Cadenc e原理图约束管理器的基本使用1.1 约束管理器简介约束管理器是一个交叉的平台,以工作薄(workbo ok)和工作表(worksheet)的形式通过用户定义约束管理来管理设计中的各个网络和管脚对。

例如控制某条网络的阻抗值和布线长度等等。

约束管理器具有以下功能:1)它以数据表格的形式与用户接口,使用户能够快速的获取,修改和删除用户定义的约束值。

2)它能够所有的定义的约束进行语法检查。

3)它提供约束的继承,在高等级对象中定义的约束能够被低等级对象所集成。

而且低等级对象可以重新定义约束覆盖从高等级对象继承下来的所有约束。

能够产生原理图和pcb板关于约束捕捉的报告。

2.1 原理图和pcb板间约束捕捉的同步原理图和pcb的约束同步是指在原理图或pcb中定义或修改的约束在原理图和p cb之间可以相互传递的(原理图到pc b或pcb到原理图)。

如下图1所示:图1 原理图与pc b板约束的同步3.1 带约束管理的设计流程带约束管理的设计流程与传统的设计流程相比,其主要包含了约束文件,该约束文件以设计板的名字命名,文件扩展名为.dcf,该文件放在设计板目录下的cons train ts目录下。

例如在E:\KS8695P_DEM O_V100.1目录下创建了KS8695P_D EMO_V100.1工程,设计板的名称为NETCAMERA,那么在E:\KS8695P_DEM O_V100.1\WORKLIB\NETCAMERA\CONSTR AINTS目下会产生n etcamera.dcf约束文件。

带约束管理的设计流程如下图2所示:图2 约束使能的设计流程3.1.1 从原理图导出约束管理到pcb在使能约束管理器的设计流程中,canden ce会产生5个必须发送pcb板上的文件:p stchi p.dat,pstrxp rt.datt,pstxne t.dat,pstcmd b.dat,pstcmb c.dat,其中前3个在传统的设计中也会产生,后2个是在使能约束管理器后产生的文件。

差分对的约束设置第一步,差分对的设置差分对的设置有很多方法,下面介绍两种最常用的方法。

1.点击菜单Logic→Assign Differential Pair... 弹出以下对话框。

点击你想要创建差分对的Net1和Net2,填入差分的名字,点击Add后就成功创建了差分对。

点击Auto Generate按钮后,弹出以下对话框:在第一个输入框填入Net的主要名字后,在下面的框中填入差分线的标志如N,P。

点击Generate即可自动产生差分对。

2.在约束管理器中设置差分对。

在DSN上点击右键,在菜单中选择Create→Differential Pair。

即可弹出下面的对话框。

和上一种方法的设置差不多,这里就不再叙述了。

第二步差分对约束规则的设置差分对各项约束可以在约束管理器中的Electric→Net→routing→Differential Pair中直接在各差分对上填入各项约束数值就可生效,但更好的方法是创建约束规则后赋给各个差分对。

在DSN上点击右键,在菜单中选择Create→Electrical CSet后,弹出下面的对话框;输入规则名后点Ok,在Electric→constraimt set→outing→Differential Pair中可以看到新规则。

在表格中输入各项数值即可完成新规则的设置。

如图所示差分对约束参数主要有以下几个:1coupling paramaters 主要包括了Primary Gap 差分对最优先线间距(边到边间距)。

Primary Width 差分对最优先线宽。

Neck Gap 差分对Neck模式下的线间距(边到边间距),用于差分对走线在布线密集区域时切换到Neck值。

Neck Width差分对Neck模式下的线宽,用于差分对走线在布线密集区域时切换到Neck值。

如图所示设置数值时在表格中右键菜单中选择change,会出现以下各层数值表格,可以在每一层上设置不同的数值。

需要注意的是在物理(physical)约束中同样可以设置差分规则,但是电气规则约束在布线时更优先,同时电气规则可以设置更多的约束,推荐在电气规则中设置差分走线的约束。

2 Min Line Specing 差分对最小间距,一定要小于或等于"Primary gap"与(-)tolerance的数值,并且也要小于或等于"Neck gap"与(-)tolerance的数值。

对于不符合约束的差分对,会显示“DS”的DRC错误提示。

3 Dynamic Phase:动态相位检查,在16.3版本新加入的功能。

对差分对路径中每个转角之间造成的路径差异进行检查。

如在整个差分对网络中,正向与反向之间的走线差距不能超过“x mils”。

如果整个路径中的某一个位置,发生了两个信号之间相位偏移超过了规定的“x mils”,这个误差必须在“y mils”范围内补偿回来。

如下图x=20,y=600.设定约束时tolerance填入x值,max length 填入y值。

对于不符合约束的走线的路径会以高亮显现,并且显示DY错误。

4 Static Phase Tolerance 这个约束设置了两根差分线之间的差值,单位是mil或ns。

设置了此项后,在走线时会实时的显示走线差,在绿灯时符合约束。

如图在Net→routing→Differential Pair中也可以看到实际的值。

需要注意的是布线时“SPhase”显示的是裕量值(Margin),而并非实际值(Actual)。

裕量值的范围如图所示在-∞到+-公差区间内,实际线长比目标线长要短,裕量值为实际值—目标值+公差。

绿灯0意为实际值比目标值少公差值长,+裕量值越大意为实际线长越接近目标线长。

在+∞到+-公差区间内,实际线长比目标线长要长,裕量值为实际值—目标值—公差。

—裕量值越大意为实际线长越接近目标线长。

对于不符合约束的差分对会显示”DP”的DRC错误提示。

5 Uncoupled length:该约束限制了差分对的一对网络之间的不匹配长度。

差分对刚刚从芯片出来的走线通常是不耦合的,“gather contrlo”可以设置为“ignore(忽略)”和“include(包括)”,意思为在计算不匹配长度时是否包含差分对刚从芯片出来的这段不耦合的线长。

在在Net→routing→Differential Pair可以查看具体的数值。

对于不符合约束的差分对,会显示“DU”的DRC错误提示。

间距约束规则设置间距约束设置有两种方法;1,直接在spacing→net→all layer中填入各项数值。

2,创建约束规则,赋给各net。

这种方法管理方便,在 Physical 和 Spacing 设置中用后者比较好。

1,创建规则如图,点击右键后选择Create→Spacing Cset。

输入名字后点OK。

2.设计规则图示中的为all layer-line中的内容,可以设置连线到各个要素的约束,在all layer中还有其他的内容的约束,和图示内容基本一样,可以分别设置。

设置好后可以在all layer-all中查看一下,这里包括了所有约束的内容。

3.赋予规则在net-all layer中,设置Referenced Spacing Cset栏即可选择不同的约束规则,如图所示。

Net class-class的间距设置NCIs(NET CLASS)由众多nets或者buses、differential pairs、Xnet所组成的类,可对其赋予相似的约束。

NCC(Net Class-Class)也就是设置不同class组相遇后的间距设置。

首先建立class组。

首先在net-all layer中复选多个对象,右键后选择Create-Class。

输入Class名后即可建立class。

设置class-class规则如图,在Net Class-Class –all layer中点击右键选择Creat- Class-Class,即可弹出以下对话框。

分别选择不同的class组后即可建立class-class对。

如图,CCls LED设置的是class组LED内部的间距规则。

CCls 48设置的是class组LED对class组48的间距规则。

same net spacing工作表在Spacing工作表下还有same net spacing工作表,用于对同一网络上的不同元素进行间距约束。

在16.2以前的版本中只能选择是否开启same net DRC检查,16.2后专门独立出一个工作表,可以设置详细的数值。

规则设置和Spacing规则设置没有多少差异,可以和Spacing规则设置的一样。

需要在Analysis – Analysis Modes -- same net spacing Modes中开启分析选项,如图。

并在same net spacing – Options中开启相应层的DRC选项,如图。

为了避免和Spacing DRC混淆,Same Net Spacing DRC显示为小写,如图。

区域约束规则设置region约束就是15.X 的 Area 约束。

在pcb布线时有些区域比如bga封装区因为过孔密集需要特殊的线宽线距约束,此时设置region就可以满足要求首先,创建region区域。

在physical或者 spacing工作表下新建一个区域(Region)约束。

输入名字。

建立完成后,在pcb板上画出一个区域。

选择 shape-regtanglar,注意在右边的options 窗口中,active class subclass 选择 constrait region,选定你需要约束的那一层,在 assign to region 里选择刚刚建好的好个区域规则(RGN2)将这个规则指定到这个区域中。

建好了region就可以赋予相应的规则了。

建立区域物理规则如图,在菜单中选择Create – region-class,弹出的对话框中选择需要约束的class组,就可以建立在该区域下class组的走线物理约束规则。

设定好约束后,在region区域就会按照特定的规则走,出了region后就按照一般的规则走。

建立区域间距约束规则创建region-class规则如图,在菜单中选择Create – region-class,弹出的对话框中选择需要约束的class组,就可以建立在该区域下class组的走线间距约束规则。

创建region-class-class规则、如图,在菜单中选择Create – region-class-class,弹出的对话框中选择需要约束的两组class组,就可以建立在该区域下两组class组相遇时的走线间距约束规则。

如图所示,在区域内设置两线最小间距1mil,布线时间距不少于1mil就不会有DRC错误。

等长约束设置首先设置管脚对(pin pair).在Electrical-net-Relative Propagation Daley工作表中,选中要建立的网络名,右键选择Create-Pin Pair。

在弹出的对话框中选择管脚。

创建match group将所有设置等长的网络创建好的管脚对后,选中管脚对,右键选择create-match group。

输入名字后即可创建match group。

等长设置设置好match group后就可设置等长了。

主要设置参数如下图所示Scope:可以选择Local和global。

Local意为仅比较同一Net或XNet内的管脚对,Global意为比较同一Match Group内的所有管脚对。

一般选择Global即可。

Pin delay:大多是在pin之间的延时不一致时,需要做一个补偿,那就需要设置pin delay,指的是IC包装内部的长度。

需要在菜单Analyze -> Analysis Modes 填入->Options.勾Analyze选PinDelay开启此功能。

打开后,在计算线长时就会包括这段线长。

另外pin delay下的Z Axis Delay指的是计算线长时是否考虑Via的长度,设置好了叠层参数后就会加上via的长度。

delta:tolerance:这项控制了match group内的线长差。

单位有三种:ns,mil,%;单位%指以目标线的N%为公差。

对已经走好的线,以最长值为目标线。

Delta指的是基准线比目标线长还是短,长则写入+delta值,短则写入-delta 值,和目标线一样长则写入0,计算公差时的基准线便是目标线长加上delta值的结果。

如上图,target线长2120.08mil,delta值为20mil,计算差值时就是(2120.08+20)-1680.28=459.80mil。