差分约束

- 格式:ppt

- 大小:856.00 KB

- 文档页数:30

综合是指在集成电路设计中,将高级描述语言(如Verilog或VHDL)的代码转化为逻辑门级电路网络的过程。

在综合过程中,设计会受到多种约束的限制,其中包括时钟约束和差分时钟约束。

时钟约束:时钟约束是指在综合过程中,对时钟信号的频率、时序和相位等方面进行限制。

时钟约束的目的是确保设计在工作时能够满足时序要求,防止时序故障的发生。

时钟约束包括时钟频率、时钟上升和下降时间、时钟延迟等方面的限制。

差分时钟约束:差分时钟约束是一种特殊的时钟约束,用于差分信号(例如差分信号对、差分时钟对等)。

差分信号是由两个相位相反的信号组成的,它们在高速电路中常用于减小干扰和提高抗噪性能。

差分时钟约束需要确保差分信号在不同部分的电路中保持同步,并且满足规定的时序要求。

综合工具在进行综合时,会根据设计描述和约束生成电路的逻辑门级表示,并进行优化以满足时序要求。

如果设计中包含时钟约束和差分时钟约束,综合工具会考虑这些约束,以确保生成的电路能够在工作时满足时序和时钟同步的要求。

综合过程中的约束,尤其是时钟约束和差分时钟约束,对于确保设计的正确性、稳定性和性能都具有重要作用,能够在集成电路设计中发挥关键的作用。

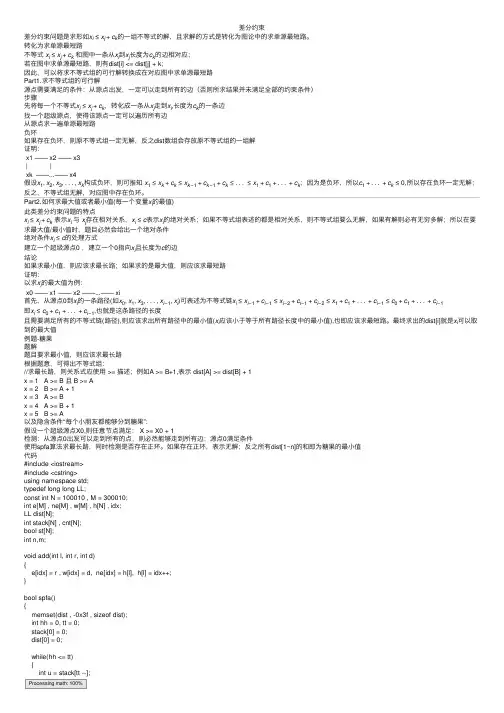

(本文假设读者已经有以下知识:最短路径的基本性质、Bellman-Ford算法。

)比如有这样一组不等式:X1 - X2 <= 0X1 - X5 <= -1X2 - X5 <= 1X3 - X1 <= 5X4 - X1 <= 4X4 - X3 <= -1X5 - X3 <= -3X5 - X4 <= -3不等式组(1)全都是两个未知数的差小于等于某个常数(大于等于也可以,因为左右乘以-1就可以化成小于等于)。

这样的不等式组就称作差分约束系统。

这个不等式组要么无解,要么就有无数组解。

因为如果有一组解{X1, X2, ..., Xn}的话,那么对于任何一个常数k,{X1 + k, X2 + k, ..., Xn + k}肯定也是一组解,因为任何两个数同时加一个数之后,它们的差是不变的,那么这个差分约束系统中的所有不等式都不会被破坏。

差分约束系统的解法利用到了单源最短路径问题中的三角形不等式。

即对于任何一条边u -> v,都有:d(v) <= d(u) + w(u, v)其中d(u)和d(v)是从源点分别到点u和点v的最短路径的权值,w(u, v)是边u -> v的权值。

显然以上不等式就是d(v) - d(u) <= w(u, v)。

这个形式正好和差分约束系统中的不等式形式相同。

于是我们就可以把一个差分约束系统转化成一张图,每个未知数Xi对应图中的一个顶点Vi,把所有不等式都化成图中的一条边。

对于不等式Xi - Xj <= c,把它化成三角形不等式:Xi <= Xj + c,就可以化成边Vj -> Vi,权值为c。

最后,我们在这张图上求一次单源最短路径,这些三角形不等式就会全部都满足了,因为它是最短路径问题的基本性质嘛。

话说回来,所谓单源最短路径,当然要有一个源点,然后再求这个源点到其他所有点的最短路径。

那么源点在哪呢?我们不妨自已造一个。

vivado差分时钟管脚约束【原创版】目录1.差分时钟管脚约束的概念2.差分时钟管脚约束的作用3.差分时钟管脚约束的实现方法4.差分时钟管脚约束的注意事项正文差分时钟管脚约束是指在 FPGA 设计中,对于差分对(differential pair)中的两个管脚,进行特定的连接和约束,以保证差分信号的正确传输和处理。

差分对是高速信号传输中常用的方式,其特点是抗干扰能力强,传输速度快。

差分时钟管脚约束的作用主要体现在以下几点:1.保证差分信号的完整性:通过管脚约束,可以确保差分对中的两个信号在传输过程中保持同步,避免因信号传输误差导致的数据丢失或错误。

2.减少电磁干扰:合理的管脚约束能够降低差分信号对外部的电磁干扰,提高系统的稳定性和可靠性。

3.提高传输速率:通过差分时钟管脚约束,可以实现高速信号的快速传输,满足高速数据通信的需求。

实现差分时钟管脚约束的方法主要有以下几种:1.物理连接:通过物理层上的连接,将差分对中的两个管脚直接连接在一起,实现信号的同步传输。

2.电路设计:通过差分放大器、电阻、电容等元器件的设计,实现差分信号的放大、滤波等功能,从而保证信号的同步传输。

3.软件控制:通过编写程序,控制 FPGA 内部的逻辑电路,实现差分信号的同步传输。

在实施差分时钟管脚约束时,需要注意以下几点:1.合理选择管脚:应选择相邻且布局合理的管脚作为差分对,以减小信号传输的延迟和电磁干扰。

2.避免跨区域连接:差分对中的两个管脚应尽量避免跨区域连接,以减小信号传输的延迟和损耗。

3.考虑电源完整性:在设计差分时钟管脚约束时,需要充分考虑电源完整性,保证电源电压的稳定和噪声抑制。

总之,差分时钟管脚约束在 FPGA 设计中起着关键作用,能够有效保证差分信号的正确传输和处理,提高系统的稳定性和可靠性。

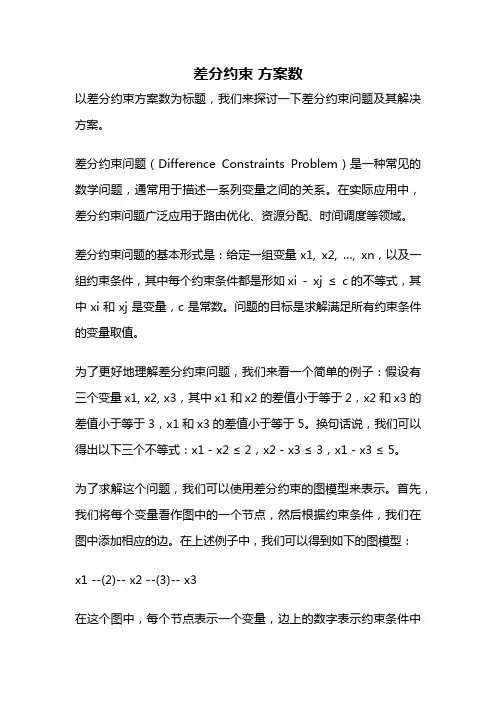

差分约束方案数以差分约束方案数为标题,我们来探讨一下差分约束问题及其解决方案。

差分约束问题(Difference Constraints Problem)是一种常见的数学问题,通常用于描述一系列变量之间的关系。

在实际应用中,差分约束问题广泛应用于路由优化、资源分配、时间调度等领域。

差分约束问题的基本形式是:给定一组变量x1, x2, …, xn,以及一组约束条件,其中每个约束条件都是形如xi - xj ≤ c的不等式,其中xi和xj是变量,c是常数。

问题的目标是求解满足所有约束条件的变量取值。

为了更好地理解差分约束问题,我们来看一个简单的例子:假设有三个变量x1, x2, x3,其中x1和x2的差值小于等于2,x2和x3的差值小于等于3,x1和x3的差值小于等于5。

换句话说,我们可以得出以下三个不等式:x1 - x2 ≤ 2,x2 - x3 ≤ 3,x1 - x3 ≤ 5。

为了求解这个问题,我们可以使用差分约束的图模型来表示。

首先,我们将每个变量看作图中的一个节点,然后根据约束条件,我们在图中添加相应的边。

在上述例子中,我们可以得到如下的图模型:x1 --(2)-- x2 --(3)-- x3在这个图中,每个节点表示一个变量,边上的数字表示约束条件中的常数。

接下来,我们可以使用拓扑排序的算法来解决差分约束问题。

拓扑排序算法的基本思想是通过计算每个节点的入度,然后按照入度的顺序依次将节点加入拓扑序列中。

在差分约束问题中,我们可以使用拓扑排序来确定变量的取值范围。

具体来说,首先我们将所有节点的入度初始化为0,并将所有节点加入一个队列中。

然后,从队列中依次取出节点,更新其相邻节点的入度,并将入度为0的节点加入队列中。

当队列为空时,算法结束。

在这个过程中,我们可以根据拓扑排序的顺序确定变量的取值范围。

回到我们的例子中,我们可以按照以下步骤来求解差分约束问题:1. 初始化变量x1, x2, x3的取值范围为[-∞, +∞];2. 将x1的入度设为0,并将其加入队列中;3. 从队列中取出x1,更新x2的取值范围为[-∞, +2],并将x2加入队列中;4. 从队列中取出x2,更新x3的取值范围为[-∞, +5],并将x3加入队列中;5. 队列为空,算法结束。

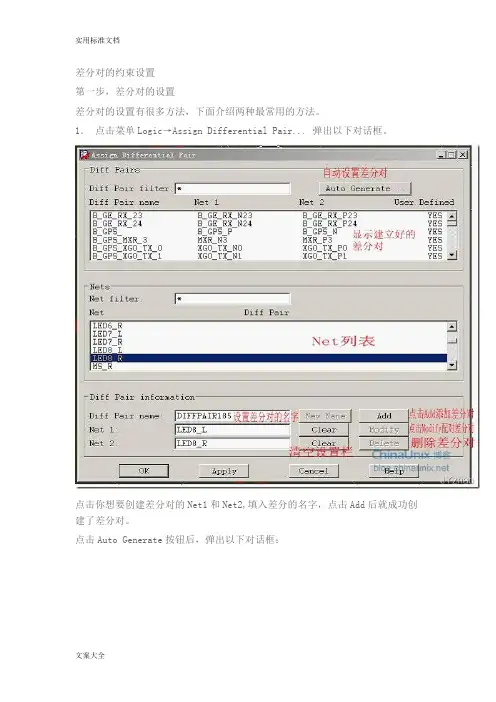

差分对的约束设置第一步,差分对的设置差分对的设置有很多方法,下面介绍两种最常用的方法。

1.点击菜单Logic→Assign Differential Pair... 弹出以下对话框。

点击你想要创建差分对的Net1和Net2,填入差分的名字,点击Add后就成功创建了差分对。

点击Auto Generate按钮后,弹出以下对话框:在第一个输入框填入Net的主要名字后,在下面的框中填入差分线的标志如N,P。

点击Generate即可自动产生差分对。

2.在约束管理器中设置差分对。

在DSN上点击右键,在菜单中选择Create→Differential Pair。

即可弹出下面的对话框。

和上一种方法的设置差不多,这里就不再叙述了。

第二步差分对约束规则的设置差分对各项约束可以在约束管理器中的Electric→Net→routing→Differential Pair中直接在各差分对上填入各项约束数值就可生效,但更好的方法是创建约束规则后赋给各个差分对。

在DSN上点击右键,在菜单中选择Create→Electrical CSet后,弹出下面的对话框;输入规则名后点Ok,在Electric→constraimt set→outing→Differential Pair中可以看到新规则。

在表格中输入各项数值即可完成新规则的设置。

如图所示差分对约束参数主要有以下几个:1coupling paramaters 主要包括了Primary Gap 差分对最优先线间距(边到边间距)。

Primary Width 差分对最优先线宽。

Neck Gap 差分对Neck模式下的线间距(边到边间距),用于差分对走线在布线密集区域时切换到Neck值。

Neck Width差分对Neck模式下的线宽,用于差分对走线在布线密集区域时切换到Neck值。

如图所示设置数值时在表格中右键菜单中选择change,会出现以下各层数值表格,可以在每一层上设置不同的数值。

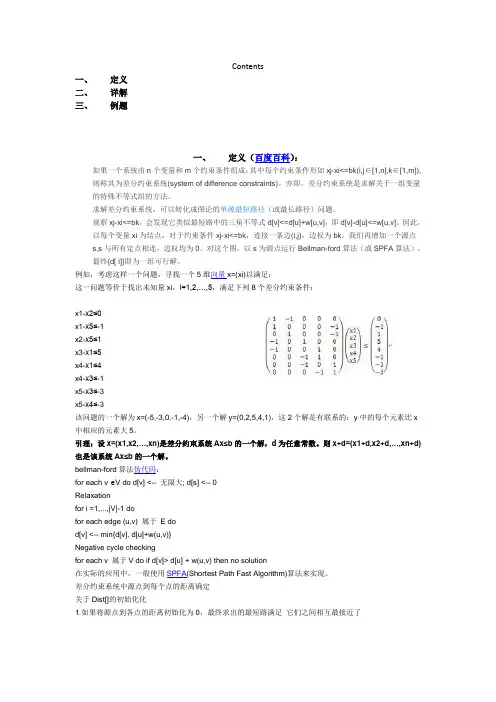

Contents一、定义二、详解三、例题一、定义(百度百科):如果一个系统由n个变量和m个约束条件组成,其中每个约束条件形如xj-xi<=bk(i,j∈[1,n],k∈[1,m]),则称其为差分约束系统(system of difference constraints)。

亦即,差分约束系统是求解关于一组变量的特殊不等式组的方法。

求解差分约束系统,可以转化成图论的单源最短路径(或最长路径)问题。

观察xj-xi<=bk,会发现它类似最短路中的三角不等式d[v]<=d[u]+w[u,v],即d[v]-d[u]<=w[u,v]。

因此,以每个变量xi为结点,对于约束条件xj-xi<=bk,连接一条边(i,j),边权为bk。

我们再增加一个源点s,s与所有定点相连,边权均为0。

对这个图,以s为源点运行Bellman-ford算法(或SPFA算法),最终{d[ i]}即为一组可行解。

例如,考虑这样一个问题,寻找一个5维向量x=(xi)以满足:这一问题等价于找出未知量xi,i=1,2,…,5,满足下列8个差分约束条件:x1-x2≤0x1-x5≤-1x2-x5≤1x3-x1≤5x4-x1≤4x4-x3≤-1x5-x3≤-3x5-x4≤-3该问题的一个解为x=(-5,-3,0,-1,-4),另一个解y=(0,2,5,4,1),这2个解是有联系的:y中的每个元素比x 中相应的元素大5。

引理:设x=(x1,x2,…,xn)是差分约束系统Ax≤b的一个解,d为任意常数。

则x+d=(x1+d,x2+d,…,xn+d)也是该系统Ax≤b的一个解。

bellman-ford算法伪代码:for each v V do d[v] <-- 无限大; d[s] <-- 0Relaxationfor i =1,...,|V|-1 dofor each edge (u,v) 属于E dod[v] <-- min{d[v], d[u]+w(u,v)}Negative cycle checkingfor each v 属于V do if d[v]> d[u] + w(u,v) then no solution在实际的应用中,一般使用SPFA(Shortest Path Fast Algorithm)算法来实现。

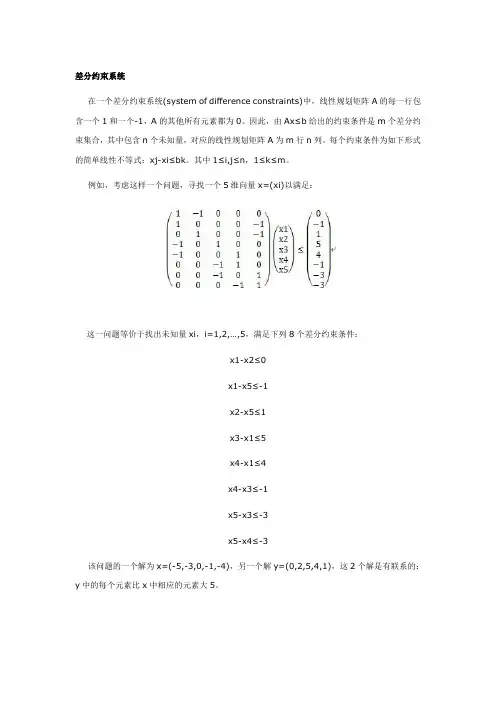

差分约束系统在一个差分约束系统(system of difference constraints)中,线性规划矩阵A的每一行包含一个1和一个-1,A的其他所有元素都为0。

因此,由Ax≤b给出的约束条件是m个差分约束集合,其中包含n个未知量,对应的线性规划矩阵A为m行n列。

每个约束条件为如下形式的简单线性不等式:xj-xi≤bk。

其中1≤i,j≤n,1≤k≤m。

例如,考虑这样一个问题,寻找一个5维向量x=(xi)以满足:这一问题等价于找出未知量xi,i=1,2,…,5,满足下列8个差分约束条件:x1-x2≤0x1-x5≤-1x2-x5≤1x3-x1≤5x4-x1≤4x4-x3≤-1x5-x3≤-3x5-x4≤-3该问题的一个解为x=(-5,-3,0,-1,-4),另一个解y=(0,2,5,4,1),这2个解是有联系的:y中的每个元素比x中相应的元素大5。

引理:设x=(x1,x2,…,xn)是差分约束系统Ax≤b的一个解,d为任意常数。

则x+d=(x1+d,x2+d,…,xn+d)也是该系统Ax≤b的一个解。

约束图在一个差分约束系统Ax≤b中,m X n的线性规划矩阵A可被看做是n顶点,m条边的图的关联矩阵。

对于i=1,2,…,n,图中的每一个顶点vi对应着n个未知量的一个xi。

图中的每个有向边对应着关于两个未知量的m个不等式中的一个。

给定一个差分约束系统Ax≤b,相应的约束图是一个带权有向图G=(V,E),其中V={v0,v1,…,vn},而且E={ (vi,vj) : xj-xi≤bk是一个约束}∪{ (v0,v1) , (v0,v2) , … , (v0,vn) }。

引入附加顶点v0是为了保证其他每个顶点均从v0可达。

因此,顶点集合V由对应于每个未知量xi的顶点vi和附加的顶点v0组成。

边的集合E由对应于每个差分约束条件的边与对应于每个未知量xi的边(v0,vi)构成。

如果xj-xi≤bk是一个差分约束,则边(vi,vj)的权w(vi,vj)=bk(注意i和j不能颠倒),从v0出发的每条边的权值均为0。

allegro差分线分组约束规则设置摘要:1.Allegro差分线分组约束规则简介2.设置差分线分组约束规则的步骤3.约束规则的应用场景及优势4.总结与建议正文:1.Allegro差分线分组约束规则简介Allegro软件是一款专业的印刷电路板(PCB)设计软件,其差分线分组约束规则是其中一项重要的功能。

通过这项功能,用户可以实现自动化布局,确保PCB上各个元件的正确位置和连接关系,从而提高整体设计的稳定性和可靠性。

2.设置差分线分组约束规则的步骤在Allegro软件中设置差分线分组约束规则,主要可以分为以下几个步骤:步骤一:创建差分线。

首先,在Allegro中创建差分线,它们用于定义分组约束规则。

步骤二:定义约束规则。

在创建差分线后,设置相应的约束规则,如最小间距、最大间距等。

步骤三:应用约束规则。

将设置好的约束规则应用于需要布局的元件,以确保它们在PCB上的位置和连接关系满足设计要求。

步骤四:检查与修复。

在布局过程中,不断检查PCB设计是否符合约束规则,如有问题,及时进行修复。

3.约束规则的应用场景及优势差分线分组约束规则在以下场景中具有显著优势:- 提高设计效率:通过自动化布局,设计者可以更快地完成PCB设计,减少重复性工作。

- 保证连接可靠性:约束规则确保了元件之间的正确连接,降低了故障风险。

- 优化电路性能:合理的布局可以降低信号干扰,提高电路性能。

- 易于维护:约束规则使得设计更加规范,便于后期维护和升级。

4.总结与建议差分线分组约束规则在Allegro软件中发挥着重要作用,能够帮助设计者实现自动化布局,提高PCB设计的质量。

在使用过程中,建议设计者熟练掌握约束规则的设置方法,并根据实际需求进行调整。

差分约束算法差分约束算法(Difference Constraint Algorithm)是一种用于求解差分约束系统的方法,差分约束系统是一种特殊的线性约束系统,其中约束关系为“某个变量的值与另一个变量的差的绝对值不超过某个常数”。

差分约束算法的基本思想是通过对约束条件进行适当的转换,构造一个有向图,并利用拓扑排序的方法求解变量的取值范围。

具体步骤如下:1. 将差分约束系统中的每个差分约束关系转化为两个线性约束关系。

例如,对于约束 a - b ≤ c,可以将其转化为a ≤ b + c 和b ≤ a - c;对于约束 a - b ≥ c,可以转化为a ≥ b +c 和b ≥ a - c。

2. 根据转化后的约束关系构造一个有向图,图中的每个变量表示一个节点,约束关系表示节点间的有向边。

对于每个约束关系a ≤ b + c,构造一条从节点 a 到节点 b 的有向边,边的权重为 c;对于每个约束关系a ≥ b + c,构造一条从节点 b 到节点a 的有向边,边的权重为 c。

3. 对构造的有向图进行拓扑排序,得到拓扑排序的顺序。

4. 根据拓扑排序的顺序,依次计算每个节点的取值范围。

对于每个节点 a,初始化其取值范围为负无穷大到正无穷大。

对于节点 a 的每个后继节点 b,更新节点 b 的取值范围为节点 a 的取值范围加上边的权重。

重复此步骤,直到没有节点的取值范围发生变化,即达到稳定状态。

5. 根据计算得到的每个节点的取值范围,判断差分约束系统是否可解。

如果存在某个节点的取值范围为负无穷大到正无穷大,则差分约束系统无解;否则,取值范围即为差分约束系统的解。

差分约束算法的时间复杂度为 O(nm),其中 n 是变量的个数,m 是约束关系的个数。

这种算法通常用于求解动态最短路径等问题,具有较高的效率。

allegro差分线分组约束规则设置摘要:I.简介- 什么是Allegro- 差分线分组约束规则的作用II.差分线分组约束规则设置- 设置规则概述- 具体设置步骤- 步骤1:定义分组- 步骤2:设置差分线属性- 步骤3:应用规则III.应用实例- 实例1:设置差分线分组约束规则- 步骤1:创建工程- 步骤2:添加元件- 步骤3:设置差分线分组约束规则- 实例2:使用差分线分组约束规则进行设计优化- 步骤1:发现问题- 步骤2:应用规则优化设计- 步骤3:验证优化结果IV.总结- 差分线分组约束规则的重要性- 在实际应用中的优势正文:I.简介Allegro 是一款广泛应用于PCB 设计领域的EDA 工具,可以帮助设计师快速、高效地完成电路板设计。

在Allegro 中,差分线分组约束规则设置是一项关键功能,它能够帮助设计师更好地管理差分线,提高设计效率和质量。

差分线分组约束规则主要用于对差分线进行分类和约束,以便在设计过程中更加方便地管理和调整。

通过设置差分线分组约束规则,可以确保差分线在设计中的正确性和一致性,避免因差分线问题导致的设计错误。

II.差分线分组约束规则设置在Allegro 中设置差分线分组约束规则主要包括以下几个步骤:1.定义分组:首先,设计师需要根据设计需求,定义差分线的分组。

分组可以根据差分线的功能、性能等特点进行划分,以便于后续的管理和调整。

2.设置差分线属性:在定义分组的基础上,设计师需要为每个分组设置差分线的属性。

这些属性包括差分线的宽度、间距、过孔等参数,可以根据设计规范和实际需求进行调整。

3.应用规则:设置好差分线属性后,设计师需要将规则应用到实际的设计中。

在Allegro 中,可以通过菜单命令或脚本语言等多种方式应用差分线分组约束规则,确保差分线在设计中的正确性和一致性。

III.应用实例以下是两个关于差分线分组约束规则设置的应用实例:实例1:设置差分线分组约束规则1.创建工程:首先,设计师创建一个新的Allegro 工程,并导入所需的元器件和设计文件。

差分约束计数差分约束计数是一种解决约束条件下的计数问题的算法。

它广泛应用于图论、排列组合等领域,可以解决求解满足特定条件的方案个数的问题。

本文将介绍差分约束计数的概念、算法流程和应用实例,以帮助读者更好地理解和运用这一算法。

差分约束计数的基本思想是通过建立一种差分约束关系,求解满足这些约束条件的计数问题。

差分约束关系指的是一组形如“y-x≤c”的约束条件,其中x和y是变量,c是一个常数。

该约束条件表示y要比x小于等于c。

差分约束计数的基本算法流程如下:1. 确定问题中的变量和约束条件。

将变量表示为图的顶点,约束条件表示为图的边。

2. 建立差分约束关系。

根据给定的约束条件,将其转换为差分约束关系。

3. 初始化距离数组。

设置一个距离数组dist,用来表示从起点出发到达每个顶点的最短路径长度。

4. 利用队列实现拓扑排序。

将图中度为0的顶点加入队列,并计算其距离数组的值。

5. 按照拓扑排序的顺序更新距离数组。

对每个顶点v,更新其相邻节点u的距离数组值dist[u]=min(dist[u], dist[v]+w(u,v)),其中w(u,v)表示边(u,v)的权值。

6. 检查是否存在负权环。

如果存在负权环,则表示无法求解满足约束条件的计数问题;否则,可以根据距离数组的值计算满足条件的方案个数。

差分约束计数的应用十分广泛。

下面以一个具体的案例来说明其应用。

案例:假设有n个城市,编号为1到n,城市之间有m条单向道路,每条道路都有一个距离值。

现在要求从城市1出发,到达城市n的方案个数,并且要求经过的道路总距离不超过k。

解决这个问题可以使用差分约束计数算法。

首先,建立n个城市的图。

每个城市表示一个顶点,每条道路表示一条边,道路的距离值作为边的权值。

然后,根据题目要求,建立差分约束关系。

对于每条道路(u,v),设置约束条件dist[v]-dist[u]≤w(u,v),其中dist[v]表示从起点城市到达城市v的最短距离,w(u,v)表示道路(u,v)的距离值。

差分进化算法约束条件

差分进化算法(Differential Evolution, DE)是一种常用的

全局优化算法,通常用于解决连续优化问题。

在应用差分进化算法时,我们经常会遇到约束条件,也就是问题的解需要满足一定的限

制条件。

这些约束条件可能包括等式约束、不等式约束或者其他形

式的约束。

在差分进化算法中处理约束条件的方法有很多种,下面我将从

不同角度来解释:

1. 罚函数法,一种常见的处理约束条件的方法是使用罚函数法。

在罚函数法中,对于违反约束条件的解,通过增加一个罚项来惩罚

这些解,使得在优化过程中不满足约束条件的解变得不利于优化。

这样可以在一定程度上保证优化的解满足约束条件。

2. 转换方法,另一种常见的处理约束条件的方法是通过一定的

变换将约束优化问题转换为无约束优化问题。

这种方法包括线性变换、非线性变换等,通过变换使得原始的约束优化问题转化为一个

无约束优化问题,然后再利用差分进化算法进行求解。

3. 修复法,修复法是指在每一代种群中,对不满足约束条件的

个体进行修复,使其满足约束条件。

这种方法的优点是可以保证每

一代种群中的解都满足约束条件,但缺点是可能会增加计算的复杂度。

4. 多目标优化,有时候约束条件可以被看作是另一个优化目标,可以将约束条件转化为多目标优化问题进行求解。

总的来说,处理约束条件是差分进化算法在实际应用中需要考

虑的一个重要问题,不同的方法适用于不同的情况。

在应用差分进

化算法时,需要根据具体的问题特点选择合适的处理约束条件的方法,以求得较好的优化效果。

如何实现差分线的约束设计?一、差分线的一般要求一般而言,在PCB设计时对差分线的约束有:基本等长,两根差分线的长度差小于20~50mil;差分线在同一层走线,并尽可能的靠近;差分线和差分线间,差分线和其他网络间,要有20mil以上的间距对于有差分阻抗要求的差分线,严格控制差分线的宽度和间距,严格控制差分线在那一层走线二、在allegro中,实现差分线的约束设计基本步骤如下:1)定义差分线,告诉规则编辑器那些网络是差分线;2)在约束设置器的“spacing rule set”中设置差分线和差分线间,差分线和其他网络的间距;设置两根差分线间最大的长度差,默认得间距和最大的间距;3)在约束设置器的“physical rule set”中设置差分线的线宽;4)打开DRC;5)设置环境变量drc_diff_pair_overide or drc_diff_pair_primary_separation_tolerance三、例子:1)定义差分线。

点击菜单“logic”→“assign differential pair”,出现如下界面:在“Net Selection Area”中的下拉框中选择一对差分线,分别出现在“Rule Information”中“NET 1”和“NET 2”的位置上,在“Rule Name”中给这一对差分线一个名字,如:DIFFPAIR1、DIFFPAIR2等等,点击按钮ADD,这对差分线出现在“Rule Selection Area”中,对所有差分线重复上述步骤。

点击按钮APPL Y,点击OK退出。

2)在规则编辑器的“Spacing Rule Set”中设置差分线和差分线间,差分线和其他网络的间距;设置两根差分线间最大的长度差,默认得间距和最大的间距;点击菜单“Setup”→“Constraints…”→“Spacing Rule Set”→“Set Vaule”,依次出现如下两种界面:设置约束名为DIFF_TEST_1和DIFF_TEST_2,适用的SUBCLASS为ALL ETCH(根据实际情况定),差分线和差分线间,差分线和其他网络的间距line to line设置为20MIL;注意:在Differential Pair一栏中设置两根差分线间最大的长度差,默认的间距和最大的间距,这一栏有四个变量:Length Tolerance:两根差分线间最大的长度差,设置为20~50milPrimary Max Sep:一般情况下两根差分线间允许的最大间距,设为8milSecondary Max Sep:特殊情况下(如打过孔,从PIN出线等)两根差分线间允许比Primary Max Sep大的间距,设置为20Mil,这样在特殊情况下,两根差分线间允许有20+8MIL的间距,超过这个间距就会出DRC。