数电试题及答案

- 格式:doc

- 大小:398.00 KB

- 文档页数:17

数电考试题及答案一、选择题(每题2分,共20分)1. 在数字电路中,一个逻辑门的输出仅取决于其输入的当前状态,这称为:A. 时序逻辑B. 组合逻辑C. 触发器逻辑D. 存储逻辑答案:B2. 以下哪个不是基本的逻辑运算?A. 与(AND)B. 或(OR)C. 非(NOT)D. 异或(XOR)答案:C3. 在数字电路中,一个触发器可以存储多少比特的信息?A. 1比特B. 2比特C. 4比特D. 8比特答案:A4. 以下哪个不是数字电路的优点?A. 高速度B. 高精度C. 低功耗D. 易于集成答案:C5. 在数字电路中,一个D触发器的输出Q在哪个时刻更新?A. 时钟上升沿B. 时钟下降沿C. 任何时候D. 从不更新答案:A6. 以下哪个不是数字电路中的信号类型?A. 模拟信号B. 数字信号C. 离散信号D. 连续信号答案:A7. 在数字电路中,一个计数器可以用于:A. 计数B. 存储数据C. 产生时钟信号D. 所有以上答案:D8. 以下哪个不是数字电路中的编码方式?A. 二进制编码B. 格雷码编码C. 十进制编码D. 八进制编码答案:C9. 在数字电路中,一个寄存器通常用于:A. 存储数据B. 产生时钟信号C. 计数D. 逻辑运算答案:A10. 以下哪个不是数字电路中的触发器类型?A. SR触发器B. JK触发器C. D触发器D. T触发器答案:D二、填空题(每题2分,共20分)1. 在数字电路中,一个逻辑门的输出仅取决于其输入的当前状态,这种逻辑称为______逻辑。

答案:组合2. 数字电路中的基本逻辑运算包括与(AND)、或(OR)和______。

答案:非(NOT)3. 一个触发器可以存储______比特的信息。

答案:14. 数字电路的优点包括高速度、高精度、______和易于集成。

答案:低功耗5. 在数字电路中,D触发器的输出Q在时钟的______更新。

答案:上升沿6. 数字电路中的信号类型包括数字信号、离散信号和______。

数电试题及答案解析一、单项选择题(每题2分,共20分)1. 以下哪个选项不是数字电路中的基本逻辑门?A. 与门B. 或门C. 非门D. 异或门答案:D2. 在数字电路中,一个二进制数1011表示十进制数多少?A. 10B. 11C. 13D. 15答案:C3. 触发器的输出状态只取决于什么?A. 当前输入B. 过去输入C. 过去和当前输入D. 外部控制信号答案:C4. 以下哪个不是数字电路的优点?A. 高抗干扰性B. 高稳定性C. 低功耗D. 易于集成答案:C5. 一个4位二进制计数器可以计数到的最大值是多少?A. 15B. 16C. 255D. 256答案:B6. 在数字电路中,一个D触发器的输出Q与输入D的关系是?A. Q = DB. Q = ¬ DC. Q = D'D. Q = ¬D'答案:A7. 以下哪个不是数字电路中的编码方式?A. 二进制编码B. 格雷码编码C. 十进制编码D. 脉冲编码答案:C8. 一个8位A/D转换器的分辨率是多少?A. 1/256B. 1/512C. 1/1024D. 1/2048答案:C9. 在数字电路中,一个3线-8线译码器可以扩展到多少个输出线?A. 16B. 32C. 64D. 128答案:B10. 以下哪个不是数字电路中的存储器类型?A. RAMB. ROMC. EPROMD. EPPROM答案:D二、多项选择题(每题3分,共15分)1. 数字电路中常用的逻辑门包括哪些?A. 与门B. 或门C. 非门D. 异或门E. 同或门答案:A, B, C, D2. 数字电路中,以下哪些因素会影响电路的性能?A. 温度B. 电源电压C. 信号传输延迟D. 环境湿度E. 电路设计答案:A, B, C, D3. 在数字电路中,以下哪些是常用的触发器?A. SR触发器B. JK触发器C. D触发器D. T触发器E. 计数器答案:A, B, C, D4. 数字电路中的计数器可以实现哪些功能?A. 计数B. 分频C. 定时D. 数据存储E. 信号放大答案:A, B, C5. 数字电路中,以下哪些是常用的存储器?A. RAMB. ROMC. EPROMD. EEPROME. 寄存器答案:A, B, C, D三、填空题(每题2分,共20分)1. 在数字电路中,一个二进制数1101表示十进制数______。

数电考试题及答案一、单项选择题(每题2分,共20分)1. 在数字电路中,最基本的逻辑运算是()。

A. 与运算B. 或运算C. 非运算D. 异或运算答案:C2. 一个触发器可以存储()位二进制信息。

A. 1B. 2C. 4D. 8答案:A3. 以下哪个不是组合逻辑电路的特点?()A. 输出只依赖于当前输入B. 输出与输入之间存在时间延迟C. 输出状态不依赖于电路的历史状态D. 输出状态不依赖于电路的初始状态答案:B4. 一个4位二进制计数器可以计数的最大值是()。

A. 15B. 16C. 255D. 256答案:B5. 以下哪个不是时序逻辑电路的特点?()A. 输出不仅依赖于当前输入,还依赖于电路的历史状态B. 输出与输入之间存在时间延迟C. 输出状态不依赖于电路的初始状态D. 输出状态依赖于电路的初始状态答案:C6. 在数字电路中,使用最多的触发器是()。

A. SR触发器B. JK触发器C. D触发器D. T触发器答案:C7. 一个3线-8线译码器可以译码()种不同的输入信号。

A. 3B. 4C. 8D. 27答案:C8. 以下哪个不是数字电路的优点?()A. 高抗干扰性B. 高稳定性C. 低功耗D. 易于集成答案:C9. 在一个二进制计数器中,如果计数器从0开始计数,那么它的第一个状态是()。

A. 0000B. 0001D. 0101答案:B10. 以下哪个不是数字电路设计中常用的简化方法?()A. 布尔代数简化B. 卡诺图简化C. 逻辑门替换D. 电阻网络简化答案:D二、多项选择题(每题3分,共15分)11. 下列哪些是数字电路中常用的逻辑门?()A. 与门B. 或门D. 异或门E. 与非门答案:ABCDE12. 在数字电路中,以下哪些因素会影响电路的稳定性?()A. 电源电压波动B. 温度变化C. 信号传输延迟D. 电路的初始状态E. 电路的负载答案:ABDE13. 以下哪些是时序逻辑电路的基本组成元素?()A. 触发器B. 计数器D. 译码器E. 编码器答案:ABC14. 在数字电路中,以下哪些是常用的计数器类型?()A. 二进制计数器B. 十进制计数器C. 约翰逊计数器D. 环形计数器E. 移位寄存器答案:ABCD15. 以下哪些是数字电路设计中常用的测试方法?()A. 功能测试B. 时序测试C. 静态测试D. 动态测试E. 模拟测试答案:ABCD三、填空题(每题2分,共20分)16. 在数字电路中,一个基本的与门电路有 ______ 个输入端和______ 个输出端。

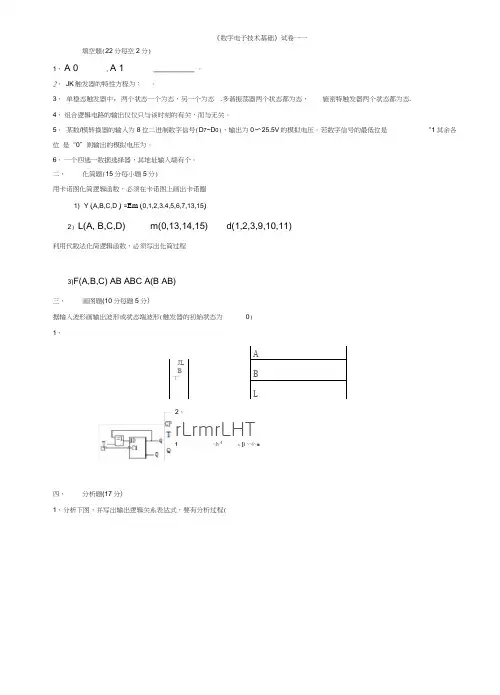

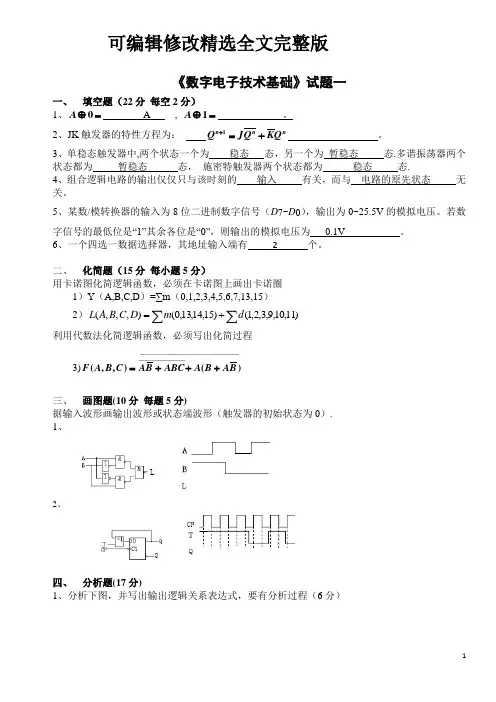

《数字电子技术基础》试卷一一填空题(22分每空2分)1、A 0 , A 1 ________ 。

2、JK触发器的特性方程为:。

3、单稳态触发器中,两个状态一个为态,另一个为态.多谐振荡器两个状态都为态,施密特触发器两个状态都为态.4、组合逻辑电路的输出仅仅只与该时刻的有关,而与无关。

5、某数/模转换器的输入为8位二进制数字信号(D7~D0),输出为0〜25.5V的模拟电压。

若数字信号的最低位是“1其余各位是“0”则输出的模拟电压为。

6、一个四选一数据选择器,其地址输入端有个。

二、化简题(15分每小题5分)用卡诺图化简逻辑函数,必须在卡诺图上画岀卡诺圈1) Y (A,B,C,D ) =Em (0,1,2,3,4,5,6,7,13,15)2) L(A, B,C,D) m(0,13,14,15) d(1,2,3,9,10,11)利用代数法化简逻辑函数,必须写岀化简过程3)F(A,B,C) AB ABC A(B AB)三、画图题(10分每题5分)据输入波形画输岀波形或状态端波形(触发器的初始状态为0)1、AJLBB丁L2、rLrmrLHT1 ~h 1< [i ~~i~■四、分析题(17分)1、分析下图,并写岀输岀逻辑关系表达式,要有分析过程(2、电路如图所示,分析该电路,画出完全的时序图,并说明电五、设计题(28分)1、用红、黄、绿三个指示灯表示三台设备的工作情况:绿灯亮表示全部正常;红灯亮表示有一台不正常;黄灯亮表示两台不正常;红、黄灯全亮表示三台都不正常。

列岀控制电路真值表,要求用74LS138和适当的与非门实现此电路(20分)2、中规模同步四位二进制计数器74LS161的功能表见附表所示;请用反馈预置回零法设计一个六进制加法计数器。

(8分)六、分析画图题(8分)画岀下图所示电路在V作用下,输岀电压的波形和电压传输特性74LS138功能表如下:2 / 26(勿74LS161功能表 清零 预置 使能 时钟 预置数据输入 输出 RD LDEP ETCPD C B AQ D Q C Q B Q A L XX X X XXXXL L L L H L X XT D C B AD C B A H H LXX XXXX 保 持 HH X LX XXXX 保 持 HHH HTXXXX计 数《数字电子技术基础》试卷一答案一、 填空题(22分每空2分)n 1nn1、A ,A2、Q JQ KQ3、稳态,暂稳态,暂稳态,稳态4、输入,电路原先状态5、0.1V6、两二、 化简题(15分 每小题5分)1) Y (A,B,C,D ) =Em (0,1,2,3,4,5,6,7,13,15) = A BDG1 G 2A G 2BC BAY 0Y 1Y 2Y 3Y 4Y 5Y 6Y 7 X H X X X XHHHHHHHHXX HX X XHHHHHHHHL XX XXXHHHHHHHHH L LL L L LHHHHHHHLL H HLHHHHHH H L LL H L HHLHHHHHLHHHHHLHHHHH L LH L L HHHHLHHH H L LH LH HHHHHLHH H L LH HLHHHHHHLHH L LH HHHHHHHHHLH L LH L L输 入输出2)L(A,B,C,D) m(0,13,14,15) d(1,2,3,9,10,11) AB AD AC3)F(A,B,C) AB ABC A(B AB) A B BC AB AB A B BC A 0 三、画图题(10分每题5分) 1、n2、 rA 1钉厂LTLrLTLRr 1 U1―r丁 H : ■ : um四、分析题(17分)1、(6 分) L A B2、(11 分) 五进制计数器12 34 5 67 8 9.JWWWWL五、设计题(28分) 1、(20 分) 1 )根据题意,列岀真值表 由题意可知,令输入为 A 、B 、C 表示三台设备的工作情况,A B C R Y G 0 0 01 1 0 00 10 1 0 0 1 0 0 1 0 0 1 1 1 0 0 1 0 0 0 1 0 1 0 1 1 0 0 11 0 1 0 0 11 10 0 1“1”表示正常,“0”表示不正常,令输岀为 R ,Y ,G 表示红、黄、绿二个批示灯的状态,“1”表示亮,“0”表示灭。

可编辑修改精选全文完整版《数字电子技术基础》试题一一、 填空题(22分 每空2分)1、=⊕0A A , =⊕1A 。

2、JK 触发器的特性方程为: n n n Q K Q J Q +=+1 。

3、单稳态触发器中,两个状态一个为 稳态 态,另一个为 暂稳态 态.多谐振荡器两个状态都为 暂稳态 态, 施密特触发器两个状态都为 稳态 态.4、组合逻辑电路的输出仅仅只与该时刻的 输入 有关,而与 电路的原先状态 无关。

5、某数/模转换器的输入为8位二进制数字信号(D 7~D 0),输出为0~25.5V 的模拟电压。

若数字信号的最低位是“1”其余各位是“0”,则输出的模拟电压为 0.1V 。

6、一个四选一数据选择器,其地址输入端有 2 个。

二、 化简题(15分 每小题5分)用卡诺图化简逻辑函数,必须在卡诺图上画出卡诺圈1)Y (A,B,C,D )=∑m (0,1,2,3,4,5,6,7,13,15)2)∑∑+=)11,10,9,3,2,1()15,14,13,0(),,,(d m D C B A L 利用代数法化简逻辑函数,必须写出化简过程3)__________________________________________________)(),,(B A B A ABC B A C B A F +++=三、 画图题(10分 每题5分)据输入波形画输出波形或状态端波形(触发器的初始状态为0). 1、2、四、 分析题(17分)1、分析下图,并写出输出逻辑关系表达式,要有分析过程(6分)2、电路如图所示,分析该电路,画出完全的时序图,并说明电路的逻辑功能,要有分析过程(11分)五、设计题(28分)1、用红、黄、绿三个指示灯表示三台设备的工作情况:绿灯亮表示全部正常;红灯亮表示有一台不正常;黄灯亮表示两台不正常;红、黄灯全亮表示三台都不正常。

列出控制电路真值表,要求用74LS138和适当的与非门实现此电路(20分)2、中规模同步四位二进制计数器74LS161的功能表见附表所示;请用反馈预置回零法设计一个六进制加法计数器。

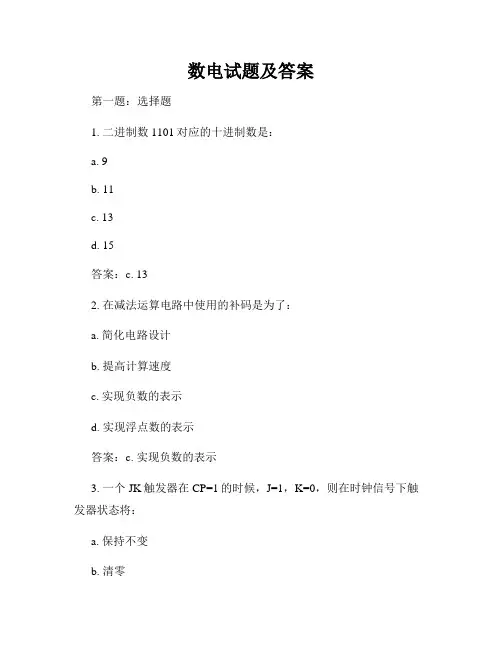

数电试题及答案第一题:选择题1. 二进制数1101对应的十进制数是:a. 9b. 11c. 13d. 15答案:c. 132. 在减法运算电路中使用的补码是为了:a. 简化电路设计b. 提高计算速度c. 实现负数的表示d. 实现浮点数的表示答案:c. 实现负数的表示3. 一个JK触发器在CP=1的时候,J=1,K=0,则在时钟信号下触发器状态将:a. 保持不变b. 清零c. 置1d. 取决于触发器的初始状态答案:a. 保持不变4. 一个带有使能引脚的逻辑门元件,在使能引脚为高电平时,输出始终为:a. 低电平b. 高电平c. 不确定d. 取决于输入信号答案:c. 不确定5. 一个8位寄存器的存储容量是:a. 8个字节b. 64个字节c. 8个位d. 64个位答案:c. 8个位第二题:填空题1. 用JK触发器构成的2位二进制计数器,下一个状态从00到01的时候,J和K的取值分别为______。

答案:J = 1, K = 02. 对于二进制补码,最高位为符号位,0表示正数,1表示负数。

那么10100001的十进制值为_______。

答案:-953. 将十进制数57转换为二进制数,需要______位二进制数来表示。

答案:64. 在门电路中,与门的输出为1当且仅当_______。

答案:所有输入的逻辑值都为1第三题:计算题1. 设有2个8位二进制数A和B,求A和B的和,并将结果转换为十进制。

请给出计算过程和结果。

解答:A = 11001010B = 00111101首先进行二进制加法,从最低位开始逐位相加:1 1 0 0 1 0 1 0 (A)+ 0 0 1 1 1 1 0 1 (B)------------------------1 0 0 0 0 1 1 1 1 (求和结果)将二进制求和结果转换为十进制:10000111 = 135所以A和B的和为135。

2. 设有一个4位二进制数补码操作,求该数的补码。

数电试题及答案 通信 071~5 班 20 08 ~20 09 学年 第 二 学期 《数字电子技术基础》 课试卷 试卷类型: A 卷

题号 一 二 三 四 五 六 七 八 九 总成

绩 得分 一、 单项选择题(每小题2分,共24分) 1、8421BCD码01101001.01110001转换为十进制数是:( c ) A:78.16 B:24.25 C:69.71 D:54.56

2、最简与或式的标准是:( c ) A:表达式中乘积项最多,且每个乘积项的变量个数最多 B:表达式中乘积项最少,且每个乘积项的变量个数最多 C:表达式中乘积项最少,且每个乘积项的变量个数最少 D:表达式中乘积项最多,且每个乘积项的变量个数最多

3、用逻辑函数卡诺图化简中,四个相邻项可合并为一项,它能:(B ) A:消去1个表现形式不同的变量,保留相同变量 B:消去2个表现形式不同的变量,保留相同变量 C:消去3个表现形式不同的变量,保留相同变量 表1 D:消去4个表现形式不同的变量,保留相同变量 4、已知真值表如表1所示,则其逻辑表达式为:( A )

A:A⊕B⊕C B:AB + BC C:AB + BC D:ABC(A+B+C)

5、函数F(A,B,C)=AB+BC+AC的最小项表达式为:( B ) A:F(A,B,C)=∑m(0,2,4) B:F(A,B,C)=∑m(3,5,6,7) C:F(A,B,C)=∑m(0,2,3,4) D:F(A,B,C)=∑m(2,4,6,7)

6、欲将一个移位寄存器中的二进制数乘以(32)10需要( C )个移位脉冲。 A:32 B: 10 C:5 D: 6

7、已知74LS138译码器的输入三个使能端(E1=1,E2A=E2B=0)时,地址码A2A1A0=011,

A B C F 0 0 0 0 0 0 1 1 0 1 0 1 0 1 1 0 1 0 0 1 1 0 1 0 1 1 0 0 1 1 1 1 则输出Y7 ~Y0是:( C ) A:11111101 B:10111111 C:11110111 D:11111111

8、要实现n1nQQ,JK触发器的J、K取值应是:(D ) A:J=0,K=0 B:J=0,K=1 C:J=1,K=0 D:J=1,K=1

9、能够实现线与功能的是:( B ) A: TTL与非门 B:集电极开路门 C:三态逻辑门 D: CMOS逻辑门

10、个四位串行数据,输入四位移位寄存器,时钟脉冲频率为1kHz,经过( B )可转换为4位并行数据输出。 A:8ms B:4ms C:8µs D:4µs

11、表2所列真值表的逻辑功能所表示的逻辑器件是:( C ) 表2

A:译码器 B:选择器

I7I6I5I4I3I2I1I0Y2Y1Y0

1×××××××111

01××××××110001×××××1010001××××10000001×××011000001××0100000001×00100000001000

输入输出 C:优先编码器 D:比较器

12、 图1所示为2个4位二进制数相加的串接全加器逻辑电路图,运算后的C4S4S3S2S1结果是:( A )

A:11000 B:11001 C:10111 D:10101

图1 二、判断题(每题1分,共6分) 1、当选用共阳极LED数码管时,应配置输出

高电平有效的七段显示译码器。 ( F ) 2、若两逻辑式相等,则它们对应的对偶式也 相等。 ( T ) 3、单稳触发器和施密特触发器是常用的脉冲信号整形电路。 ( T ) 4、与逐次逼近型ADC比较,双积分型ADC的转换速度快。 ( F ) 5、钟控RS触发器是脉冲触发方式。 (F ) 6、A/D转换过程通过取样、保持、量化和编码四个步骤。 ( T )

三、填空题(每小题1分,共20分) 1、逻辑代数的三种基本运算规则 代入定

理 、 反演定理 、 对偶定理 。 2、逻辑函数的描述方法有 逻辑真值表 、逻辑函数式 、逻辑图 、 波形图 、卡诺图 等。 3、将8k×4位的RAM扩展为64k×8位的RAM,需用 16 片8k×4位的RAM,同时还需用一片 38 译码器。 4、三态门电路的输出有 低电平 、 高电平 和 高阻态 3种状态。 5、Y= ABC+AD+C 的对偶式为YD=

(A+B+C)(A+D)C 。 6、一个10位地址码、8位输出的ROM,其存储容量为 2^13 。 7、若用触发器组成某十一进制加法计数器,需要 4 个触发器,有 5 个无效状态。 8、欲将一个正弦波电压信号转变为同频率的矩形波,应当采用 施密特触发器 电路。 9、图2所示电路中,74161为同步4位二进制加计数器,DR为异步清零端,则该电路为 6 进制计数器。 10、图3所示电路中触发器的次态方程Qn+1为 A’Q’ 。 图2 图3 四、分析题(共20 分) 1、分析用图4(a)、(b)集成十进制同步可逆计数器CT74LS192组成的计数器分别是几进制计数器。CT74LS192的CR为异步清零端(高电平有效),LD为异步置数控制端(低电平有效),CPU、CPD为加、减计数脉冲输入端(不用端接高电平),CO和BO分别为进位 和借位输出端。(4分)

6和23

图4 (a) 图4 (b)

2、 用ROM设计一个组合逻辑电路,用来 产生下列一组逻辑函数 DBBDYDCBBDAYDCABDCBABCDADCBAYABCDDCBADCBADCBAY 4321

列出ROM应有的数据表,画出存储矩阵的点阵图。 3、试画出图5所示电路在CP、DR信号作用下Q1、Q2、Q3的输出电压波形,并说明Q1、Q2、Q3输出信号的频率与CP信号频率之间的关系。(6分)

图5

五、设计题(共20分) 1、用74LS161设计一个10进制计数器。 (1)同步预置法,已知S0=0001。(2)异步清零法。(10分) 2、集成定时器555如图6(a)所示。 (1)用该集成定时器且在规格为100KΩ、200K、 500K的电阻,0.01uf、0.1uf、1uf的电容器中选择合适的电阻和电容,设计一个满足图5(b)所示波形的单稳态触发器。 (2)用该集成定时器设计一个施密特触发器,画出施密特触发器的电路图。当输入为图5(c)所示的波形时,画出施密特触发器的输出U0波形。 (10分)

图6(a) 图6(b) 图6(c) 六、综合分析计算题(共10 分) 试分析图7所示电路的工作原理,画出输出电压υ0的波形图,列出输出电压值υ0的表。表3给出了RMA的16个地址单元中所存的数据。高6位地址A9~A4始终为0,在表中没有列出。 RAM的输出数据只用了低4位,作为CB7520的输入。因RAM的高4位数据没有使用,故表中也未列出。(8分)

表3

A3 A2 A1 A0 D3 D2 D1 D0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 1 0 0 0 1 1 0 0 1 1 0 1 1 1 0 1 0 0 1 1 1 1 0 1 0 1 1 1 1 1 0 1 1 0 0 1 1 1 0 1 1 1 0 0 1 1 1 0 0 0 0 0 0 1

1 0 0 1 0 0 0 0

1 0 1 0 0 0 0 1

1 0 1 1 0 0 1 1

1 1 0 0 0 1 0 1

1 1 0 1 0 1 1 1

1 1 1 0 1 0 0 1 1 1 1 1 1 0 1 1 图7

υ0的电压值

2008 ~ _2009_学年第 二 学期 《数字电子技术基础》 课程试卷

标准答案及评分标准 A(√)卷 专业__通信____ 班级 __2007 1~5______

一、单项选择题(每小题2分,共24分) 1、C; 2、C; 3、B; 4、A; 5、B; 6、C; 7、C; 8、:D; 9、B; 10、B

11、C 12、A 二、判断题(每题1分,共6分) 1、( × ) 2、( √ ) 3、( √ ) 4、( × ) 5、( × ) 6、( √ )

三、填空题(每小题1分,共20分) 1、代入定理、反演定理、对偶定理

2、逻辑真值表、逻辑函数式、 逻辑图、波形图、卡诺图 3、16、3线-8线 4、高电平、低电平、高阻 5、(A+B+C)(A+D) C 、 6、8K 或213 7、4、5

A3 A2 A1 A0 D3 D2 D1 D0 υ0(V) 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 1 0 0 0 1 1 0 0 1 1 0 1 1 1 0 1 0 0 1 1 1 1 0 1 0 1 1 1 1 1 0 1 1 0 0 1 1 1 0 1 1 1 0 0 1 1 1 0 0 0 0 0 0 1

1 0 0 1 0 0 0 0