电子技术基础数字部分第五版康光华主编第5章习题答案(可编辑修改word版)

- 格式:docx

- 大小:31.53 KB

- 文档页数:4

第一章数字逻辑习题1.1数字电路与数字信号1。

1.2 图形代表的二进制数0101101001.1.4一周期性数字波形如图题所示,试计算:(1)周期;(2)频率;(3)占空比例MSB LSB0 1 2 11 12 (ms)解:因为图题所示为周期性数字波,所以两个相邻的上升沿之间持续的时间为周期,T=10ms频率为周期的倒数,f=1/T=1/0。

01s=100HZ占空比为高电平脉冲宽度与周期的百分比,q=1ms/10ms*100%=10%1。

2数制21.2。

2将下列十进制数转换为二进制数,八进制数和十六进制数(要求转换误差不大于4(2)127 (4)2.718解:(2)(127)D=72-1=(10000000)B-1=(1111111)B=(177)O=(7F)H(4)(2。

718)D=(10。

1011)B=(2。

54)O=(2.B)H1。

4二进制代码1.4.1将下列十进制数转换为8421BCD码:(1)43 (3)254.25解:(43)D=(01000011)BCD1。

4。

3试用十六进制写书下列字符繁荣ASCⅡ码的表示:P28(1)+ (2)@(3)you (4)43解:首先查出每个字符所对应的二进制表示的ASCⅡ码,然后将二进制码转换为十六进制数表示。

(1)“+"的ASCⅡ码为0101011,则(00101011)B=(2B)H(2)@的ASCⅡ码为1000000,(01000000)B=(40)H(3)you的ASCⅡ码为本1111001,1101111,1110101,对应的十六进制数分别为79,6F,75(4)43的ASCⅡ码为0110100,0110011,对应的十六紧张数分别为34,331。

6逻辑函数及其表示方法1。

6.1在图题1。

6。

1中,已知输入信号A,B`的波形,画出各门电路输出L的波形.解: (a)为与非, (b)为同或非,即异或第二章 逻辑代数 习题解答2.1.1 用真值表证明下列恒等式 (3)A B AB AB ⊕=+(A ⊕B )=AB+AB A B A B ⊕AB AB A B ⊕ AB +AB 0 0 0 1 0 1 1 0 1 1 0 0 0 0 1 0 1 0 0 0 0 11111由最右边2栏可知,A B ⊕与AB +AB 的真值表完全相同。

第一章数字逻辑习题1.1数字电路与数字信号1.1.2 图形代表的二进制数0101101001.1.4一周期性数字波形如图题所示,试计算:(1)周期;(2)频率;(3)占空比例MSB LSB0 1 2 11 12 (ms)解:因为图题所示为周期性数字波,所以两个相邻的上升沿之间持续的时间为周期,T=10ms 频率为周期的倒数,f=1/T=1/0.01s=100HZ占空比为高电平脉冲宽度与周期的百分比,q=1ms/10ms*100%=10%1.2数制2 1.2.2将下列十进制数转换为二进制数,八进制数和十六进制数(要求转换误差不大于4(2)127 (4)2.718解:(2)(127)D=72-1=(10000000)B-1=(1111111)B=(177)O=(7F)H(4)(2.718)D=(10.1011)B=(2.54)O=(2.B)H1.4二进制代码1.4.1将下列十进制数转换为8421BCD码:(1)43 (3)254.25解:(43)D=(01000011)BCD1.4.3试用十六进制写书下列字符繁荣ASCⅡ码的表示:P28(1)+ (2)@ (3)you (4)43解:首先查出每个字符所对应的二进制表示的ASCⅡ码,然后将二进制码转换为十六进制数表示。

(1)“+”的ASCⅡ码为0101011,则(00101011)B=(2B)H(2)@的ASCⅡ码为1000000,(01000000)B=(40)H(3)you的ASCⅡ码为本1111001,1101111,1110101,对应的十六进制数分别为79,6F,75(4)43的ASCⅡ码为0110100,0110011,对应的十六紧张数分别为34,331.6逻辑函数及其表示方法1.6.1在图题1. 6.1中,已知输入信号A,B`的波形,画出各门电路输出L的波形。

解: (a)为与非, (b)为同或非,即异或第二章 逻辑代数 习题解答2.1.1 用真值表证明下列恒等式 (3)A B AB AB ⊕=+(A ⊕B )=AB+AB 解:真值表如下A B A B ⊕ABAB A B ⊕AB +AB0 0 0 1 0 1 1 0 1 1 0 0 0 0 1 0 1 0 0 0 0 11111由最右边2栏可知,A B ⊕与AB +AB 的真值表完全相同。

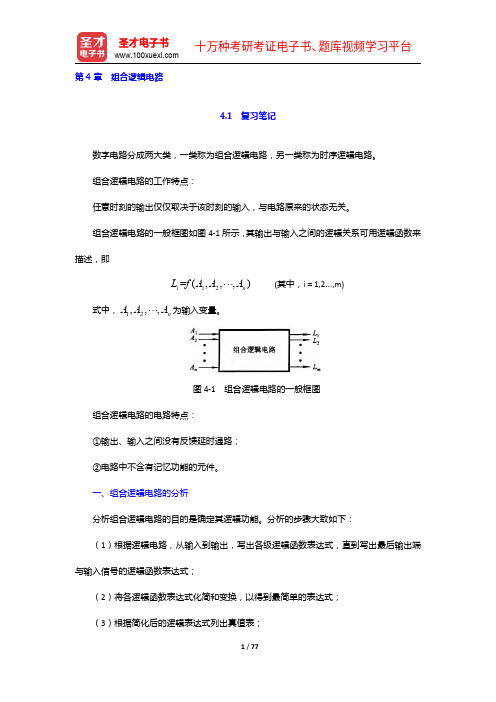

目 录第1章 绪 论1.1 复习笔记1.2 课后习题详解1.3 名校考研真题详解第2章 运算放大器2.1 复习笔记2.2 课后习题详解2.3 名校考研真题详解第3章 二极管及其基本电路3.1 复习笔记3.2 课后习题详解3.3 名校考研真题详解第4章 双极结型三极管及放大电路基础4.1 复习笔记4.2 课后习题详解4.3 名校考研真题详解第5章 场效应管放大电路5.1 复习笔记5.2 课后习题详解5.3 名校考研真题详解第6章 模拟集成电路6.1 复习笔记6.2 课后习题详解6.3 名校考研真题详解第7章 反馈放大电路7.1 复习笔记7.2 课后习题详解7.3 名校考研真题详解第8章 功率放大电路8.1 复习笔记8.2 课后习题详解8.3 名校考研真题详解第9章 信号处理与信号产生电路9.1 复习笔记9.2 课后习题详解9.3 名校考研真题详解第10章 直流稳压电源10.1 复习笔记10.2 课后习题详解10.3 名校考研真题详解第11章 电子电路的计算机辅助分析与设计第1章 绪 论1.1 复习笔记一、电子系统与信号电子系统指若干相互连接、相互作用的基本电路组成的具有特定功能的电路整体。

信号是信息的载体,按照时间和幅值的连续性及离散性可把信号分成4类:①时间连续、数值连续信号,即模拟信号;②时间离散、数值连续信号;③时间连续、数值离散信号;④时间离散、数值离散信号,即数字信号。

二、信号的频谱任意满足狄利克雷条件的周期函数都可展开成傅里叶级数(含有直流分量、基波、高次谐波),从这种周期函数中可以取出所需要的频率信号,过滤掉不需要的频率信号,也可以过滤掉某些频率信号,保留其它频率信号。

幅度频谱:各频率分量的振幅随频率变化的分布。

相位频谱:各频率分量的相位随频率变化的分布。

三、放大电路模型信号放大电路是最基本的模拟信号处理电路,所谓放大作用,其放大的对象是变化量,本质是实现信号的能量控制。

放大电路有以下4种类型:1.电压放大电路电路的电压增益为考虑信号源内阻的电压增益为2.电流放大电路电路的电流增益为考虑信号源内阻的电压增益为3.互阻放大电路电路的互阻增益为4.互导放大电路电路的互导增益为四、放大电路的主要性能指标1输入电阻:输入电压与输入电流的比值,即对输入为电压信号的放大电路,R i越大越好;对输入为电流信号的放大电路,R i越小越好。

第一章习题答案1.1.4 一周期性信号的波形如图题1.1.4所示,试计算:(1)周期;(2)频率;(3)占空比012(ms)图题1.1.4解: 周期T=10ms 频率f=1/T=100Hz 占空比q=t w /T ×100%=1ms/10ms ×100%=10%1.2.2 将下列十进制数转换为二进制数、八进制数和十六进制数,要求误差不大于2-4: (1)43 (2)127 (3)254.25 (4)2.718 解:1. 转换为二进制数:(1)将十进制数43转换为二进制数,采用“短除法”,其过程如下:2 43 ………………………余1……b 02 21 ………………………余1……b 12 1 ………………………余1……b 52 2 ………………………余0……b 42 5 ………………………余1……b 32 10 ………………………余0……b20高位低位从高位到低位写出二进制数,可得(43)D =(101011)B(2)将十进制数127转换为二进制数,除可用“短除法”外,还可用“拆分比较法”较为简单: 因为27=128,因此(127)D =128-1=27-1=(1000 0000)B -1=(111 1111)B(3)将十进制数254.25转换为二进制数,整数部分(254)D =256-2=28-2=(1 0000 0000)B -2=(1111 1110)B 小数部分(0.25)D =(0.01)B (254.25)D =(1111 1110.01)B(4)将十进制数2.718转换为二进制数 整数部分(2)D =(10)B小数部分(0.718)D =(0.1011)B 演算过程如下:0.718×2=1.436……1……b-1 0.436×2=0.872……0……b-2 0.872×2=1.744……1……b-3 0.744×2=1.488……1……b-4 0.488×2=0.976……0……b-5 0.976×2=1.952……1……b-6高位低位要求转换误差小于2-4,只要保留小数点后4位即可,这里算到6位是为了方便转换为8进制数。

电子技术基础(数字部分)第五版答案康华光电子技术基础第五版康华光课后答案第一章数字逻辑习题1、1数字电路与数字信号图形代表的二进制数0001、1、4一周期性数字波形如图题所示,试计算:周期;频率;占空比例MSBLSB0121112解:因为图题所示为周期性数字波,所以两个相邻的上升沿之间持续的时间为周期,T=10ms频率为周期的倒数,f=1/T=1/=100HZ占空比为高电平脉冲宽度与周期的百分比,q=1ms/10ms*100%=10%数制将下列进制数转换为二进制数,八进制数和六进制数127 解:D=-1=B-1=B=O=H72D=B=O=H二进制代码将下列进制数转换为8421BCD码:43解:D=BCD试用六进制写书下列字符繁荣ASCⅡ码的表示:P28+ @ you43解:首先查出每个字符所对应的二进制表示的ASCⅡ码,然后将二进制码转换为六进制数表示。

“+”的ASCⅡ码为0011,则B=H@的ASCⅡ码为1000000,B=Hyou的ASCⅡ码为本1111001,1111,1101,对应的六进制数分别为79,6F,7543的ASCⅡ码为0100,0110011,对应的六紧张数分别为34,33 逻辑函数及其表示方法在图题1、中,已知输入信号A,B`的波形,画出各门电路输出L的波形。

解: 为与非,为同或非,即异或第二章逻辑代数习题解答用真值表证明下列恒等式ABABAB⊕=+=AB+AB解:真值表如下ABAB⊕ABABAB⊕AB+AB111111111111由最右边2栏可知,与AB+AB的真值表完全相同。

用逻辑代数定律证明下列等式AABCACDCDEACDE++++=++解:AABCACDCDE++++ABCACDCDE=+++AACDCDE=++ACDCDE=++ACDE=++用代数法化简下列各式ABCBC+解:ABCBC+ABABABAB=、+、+++BABAB=++ABB=+AB=+AB=ABCDABDBCDABCBDBC++++解:ABCDABDBCDABCBDBC++++ABCDDABDBCDCBACADCDBACADBACDABBCBD=++++=+++=+++=++=++画出实现下列逻辑表达式的逻辑电路图,限使用非门和二输入与非门LABAC=+LDAC=+LABCDBCDBCDBCDABD=+++用卡诺图化简下列个式ABCDABCDABADABC++++解:ABCDABCDABADABC++++ ABCDABCDABCCDDADBBCCABCDD=+++++++++ ABCDABCDABCDABCDABCDABCDABCD=++++++LABCDmd=+ΣΣ解:LAD=+LABCDmd=+ΣΣ解:LADACAB=++已知逻辑函数LABBCCA=++,试用真值表,卡诺图和逻辑图表示解:1>由逻辑函数写出真值表ABCL1111111111111111112>由真值表画出卡诺图3>由卡诺图,得逻辑表达式LABBCAC=++用摩根定理将与或化为与非表达式LABBCACABBCAC=++=、、4>由已知函数的与非-与非表达式画出逻辑图第三章习题MOS逻辑门电路根据表题所列的三种逻辑门电路的技术参数,试选择一种最合适工作在高噪声环境下的门电路。

C

C TG 1 D

TG & G 1 TG 3 TG & G 3 1 Q C

C

1 Q C

TG 2

TG 4 CP 1 C TG C

C C TG C

& S D & G 2

G 4

R D

第五章作业答案

5.2.1 分析图题 5.2.1 所示电路的逻辑功能,列出功能表。

S Q

Q

R

图题5.2.1

解:方法(1) 将图题 5.2.1 所示电路与由与非门构成的基本 RS 锁存器比较,发现该电路与后者仅在信号输入端分别多了一个非门,而后者为低电平有效的基本 RS 锁存器,因此该电路为高电平有效的 RS 锁存器,功能表如下:

S R Q

Q

锁存器状态 0 0 不变 不变 保持 0 1 0 1 0 1 0 1 0 1 1

1

不确定

方法(2) 由逻辑电路图可以得到 Q 端和Q 端的逻辑表达式

Q S Q n Q

R Q

根据上面的逻辑表达式,可以得到该锁存器的功能表如下所示:

(略,同上表)

5.3.1 触发器的逻辑电路如图题 5.3.1 所示,确定其属于何种电路结构的触发器,并分析工作原理。

中 TG 1、TG 2 和 G 1、G 2 构成主锁存器,TG 3、TG 4 和 G 3、G 4 构成从锁存器, S D 和 R D 分别

1

& & 1

CP J K Q

为直接置 1 端和直接置 0 端。

当触发器处于工作状态时,应将他们置于高电平。

工作原理分析:

(1) 当 CP=0 时,C=0, C =1,TG 1、TG 4 导通,TG 2、TG 3 断开。

此时 D 信号进入锁

存器,G 1 输出 D ,并随 D 变化。

由于 TG 3 断开、TG 4 导通,主从锁存器相互隔离,从锁存 器构成双稳态存储单元,使触发器的输出维持原来的状态不变。

(2) 当 CP 由 0 跳变到 1 后,C=1, C =0,TG 1、TG 4 断开,TG 2、TG 3 导通。

此时 D

信号与主锁存器之间的联系被切断,TG 2 的导通使主锁存器维持在 CP 上升沿到来之前瞬间的状态。

同时由于 TG 3 导通,G 1 输出信号送到 Q 端,得到Q n 1 D ,并且在 CP=1 期间保

持不变。

(3) 当 CP 由 1 跳变到 0 后,再次重复(1)的过程。

5.4.1 上升沿和下降沿触发的 D 触发器的逻辑符号及时钟信号 CP( CP )的波形如图题 5.4.1 所示,分别画出他们 Q 端的波形。

设触发器的初始状态为 0。

解:上升沿和下降沿触发的 D 触发器 Q 端的输出分别为 Q 1 和 Q 2,输出波形如下:

CP(CP)

D Q 1

Q 2

5.4.3 设下降沿触发的 JK 触发器的初始状态为 0, CP 、J 、K 信号如图题 5.4.3 所示,试画 出触发器 Q 端的输出波形。

解:触发器 Q 端的输出波形如下:

5.4.8 两相脉冲产生电路电路如图题 5.4.8 所示,试画出在CP 作用下Φ1 和Φ2 的波形,并说 明Φ1 和Φ2 的时间关系。

各触发器的初始状态为 0。

Q 1

1 Q 2

1

Q 1

Q 2

1J C1 1K

1J C1 1K

C

Q 1

Q 1

Q 2 B CP A

Q 2

R

1K C1 1J

R 1D C1

1 Φ1

CP 1

Φ2

解:由图题 5.4.8 得到Φ1 和Φ2 的逻辑表达式:Φ1 = Q 2, 2

Q 1Q 2 Q 1 Q 2 Q 1 Q 2 。

由于图中的 JK 触发器的 J 、K 均接 1,因此两个触发器均在各自的 CP 脉冲下降沿状态翻转, 而第一个触发器的输出 Q 1 作为第二个触发器的 CP 脉冲输入,因此 Q 2 在 Q 1 的每个下降沿状态翻转,Φ1 和Φ2 的波形如下所示:

CP Q 1 Φ1(Q 2)

Q 1 Q 2 Φ2

由波形图可知,Φ1 超前Φ2 一个CP 周期

5.4.9 逻辑电路和各输入端波形如图题 5.4.9 所示,画出两触发器 Q 端的波形。

两触发器的初始状态为 0。

解:由逻辑图可以看出触发器 2 是一个下降沿触发的 JK 触发器,触发器 1 是一个上升沿触发的 D 触发器,他的 CP 脉冲来自 Q 2,并且 D 信号接在Q 1 上,即 Q 1 在 Q 2 的每一个上升沿

状态翻转一次。

C 接两个触发器的直接复位端。

Q 1、Q 2 的波形图如下:

≥1

&

&

CP

A B C

Q

2

Q

1。