门电路外特性及参数

- 格式:ppt

- 大小:545.50 KB

- 文档页数:30

常用逻辑门电路符号与功用最常用的集成门电路有TTL系列集成逻辑门和CMOS系列集成逻辑门两大类。

就其功用而言,常用的有与门、或门、非门、与非门、或非门、与或非门、异或门以及集电极开路(OC)门、三态(TS)门等。

表1给出了常用逻辑门的逻辑符号与功用。

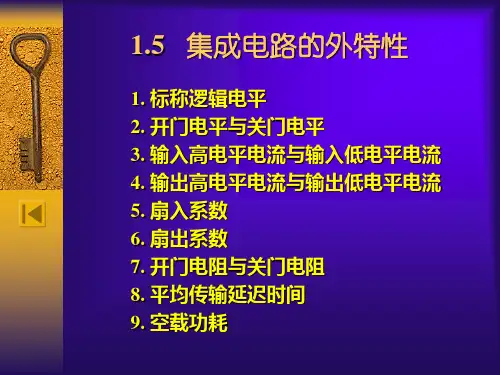

表1常用逻辑门的逻辑符号与功用称谓符号表达式称谓符号表达式与门F=Amiddot;B与或非门或门F=A+B异或门非门同或门与非门OC与非门输出端能够对接或非门三态与非门EN为使能操控1.外部特性参数集成逻辑门的首要外部特性参数有输出高、低逻辑电平,开门电平,关门电平,扇入系数,扇出系数,输入短路电流,输入漏电流,均匀传输时延和空载功耗等。

2.集成门电路的运用特征(1)在进行逻辑方案时,各类逻辑门可完结与其对应的逻辑运算功用。

(2)OC门的输出端能够直接联接,完结线与,此外可完结电平改换和直接驱动发光二极管等。

(3)TS门首要用于总线传送,多个TS门的输出端能够直接与总线联接,完结数据分时传送。

(4)用逻辑门构成实习电路时,对集成门的剩下输入端有必要恰当处理。

例如,TTL与门和与非门的剩下输入端能够经过电阻接电源,或门和或非门的剩下输入端能够经过电阻接地。

CMOS与门和与非门的剩下输入端能够直接与电源相接;CMOS或非门的剩下输入端可接地等。

总归,既要防止剩下输入端悬空构成信号搅扰,又要保证对剩下输入端的处置不影响正常的逻辑功用。

3.常用TTL集成门电路芯片(1)集成与非门电路芯片常用的TTL与非门集成电路芯片有7400、7410和7420等。

7400是一种内部有四个两输入与非门的芯片,其引脚分配图如图1(a)所示;7410是一种内部有三个三输入与非门的芯片,其引脚分配图如图1(b)所示;7420是一种内部有两个四输入与非门的芯片,其引脚分配图如图1(c)所示。

图中,VCC为电源引脚,GND为接地脚,NC为空脚。

实验十四TTL、CMOS门电路参数及逻辑特性的测试大学通信工程系林XX一.实验目的:1、掌握TTL、CMOS与非门参数的测量方法;2、掌握TTL、CMOS与非门逻辑特性的测量方法;3、掌握TTL与CMOS门电路接口设计方法。

二.实验原理:(一)TTL门电路:TTL门电路是标准的集成数字电路,其输入、输出端均采用双极型三极管结构:凡是TTL器件特性均与TTL门电路具有相同特性,故需了解TTL门电路的主要参数。

7400是TTL型中速二输入端四与非门。

图1是它的部电路原理图和管脚排列图。

1、TTL与非门的主要参数:(1)输入短路电流:I IS:与非门某输入端接地时,该输入端接入地的电流。

(2)输入高电平电流I IH:与非门某输入端接V CC(5V),其他输入端悬空或接V CC时,流入该输入端的电流。

TTL与非门特性如图2所示:(3)开门电平V ON:使输出端维持低电平V OL所需的最小输入高电平,通常以V O=0.4V时的Vi定义。

(4)关门电平V OFF:使输出端保持高电平V OH所允许的最大输入低电平,通常以Vo=0.9V OH时的Vi定义。

阀值电平V T:V T=(V OFF+V ON)/2(5)开门电阻R ON:某输入端对地接入电阻(其他悬空),使输出端维持低电平(通常以V O=0.4V)所需的最小电阻值。

(6)关门电阻R OFF:某输入端对地接入电阻(其他悬空),使输出端保持高电平V OH(通常以V O=0.9V OH 所允许的最大电阻值)。

TTL与非门输入端的电阻负载特性曲线如图3所示。

(7)输出低电平负载电流I OL:输出保持低电平V O=0.4V时允许的最大灌流(如图4);(8)输出高电平负载电流I OH:输出保持高电平V O=0.9V OH时允许的最大拉流;(9)平均传输延迟时间tpd:○1开通延迟时间t OFF:输入正跳变上升到1.5V相对输出负跳变下降到1.5V的时间间隔;○2关闭延迟时间t ON:输入负跳变上升到1.5V相对输出正跳变下降到1.5V的时间间隔;○3平均传输延迟时间:开通延迟时间与关闭延迟时间的算术平均值。

第二章 逻辑门电路集成逻辑门电路是组成各种数字电路的基本单元。

通过本章的学习,要求读者了解集成逻辑门的基本结构,理解各种集成逻辑门电路的工作原理,掌握集成逻辑门的外部特性及主要参数,掌握不同逻辑门之间的接口电路,以便于正确使用逻辑门电路。

第一节 基本知识、重点与难点一、基本知识(一) TTL 与非门 1.结构特点TTL 与非门电路结构,由输入极、中间极和输出级三部分组成。

输入级采用多发射极晶体管,实现对输入信号的与的逻辑功能。

输出级采用推拉式输出结构(也称图腾柱结构),具有较强的负载能力。

2.TTL 与非门的电路特性及主要参数 (1)电压传输特性与非门电压传输特性是指TTL 与非门输出电压U O 与输入电压U I 之间的关系曲线,即U O=f (U I )。

(2)输入特性当输入端为低电平U IL 时,与非门对信号源呈现灌电流负载,1ILbe1CC IL R U U U I −−−=称为输入低电平电流,通常I IL =-1~1.4mA 。

当输入端为高电平U IH 时,与非门对信号源呈现拉电流负载,通常I IH ≤50μA 称为输入高电平电流。

(3)输入负载特性实际应用中,往往遇到在与非门输入端与地或信号源之间接入电阻的情况。

若U i ≤U OFF ,则电阻的接入相当于该输入端输入低电平,此时的电阻称为关门电阻,记为R OFF 。

若U i ≥U ON ,则电阻的接入相当于该输入端输入高电平,此时的电阻称为开门电阻,记为R ON 。

通常R OFF ≤0.7K Ω,R ON ≥2K Ω。

(4)输出特性反映与非门带载能力的一个重要参数--扇出系数N O 是指在灌电流(输出低电平)状态下驱动同类门的个数IL OLmax O /I I N =其中OLmax I 为最大允许灌电流,I IL 是一个负载门灌入本级的电流(≈1.4mA )。

N O 越大,说明门的负载能力越强。

(5)传输延迟时间传输延迟时间表明与非门开关速度的重要参数。

TTL与非门主要外部特性参数2.主要外部特性参数TTL与非门的主要外部特性参数有输出逻辑电平、开门电平、关门电平、扇入系数、扇出系数、平均传输时延和空载功耗等。

(1)输出高电平V oH:输出高电平V oH是指至少有一个输入端接低电平时的输出电平。

V oH的典型值是3.6V。

产品规范值为V oH≥ 2.4V,标准高电平V SH=2.4V。

(2)输出低电平V oL:输出低电平V oL是指输入全为高电平时的输出电平。

V oL的典型值是0.3V,产品规范值为V oL≤ 0.4V,标准低电平V SL= 0.4V。

(3)开门电平V ON:开门电平V ON是指在额定负载下,使输出电平达到标准低电平V SL的输入电平,它表示使与非门开通的最小输入电平。

V ON的典型值为1.5V,产品规范值为V ON≤1.8V。

开门电平的大小反映了高电平抗干扰能力,V ON愈小,在输入高电平时的抗干扰能力愈强。

(4)关门电平V OFF:关门电平V OFF是指输出空载时,使输出电平达到标准高电平V SH的输入电平,它表示使与非门关断所允许的最大输入电平。

V OFF的典型值为1V,产品规范值V OFF≥ 0.8V。

关门电平的大小反映了低电平抗干扰能力,V OFF越大,在输入低电平时的抗干扰能力越强。

(5)扇入系数N i:扇入系数N i是指与非门允许的输入端数目。

一般N i为2~5,最多不超过8。

(6)扇出系数N o:扇出系数N o是指与非门输出端连接同类门的最多个数。

它反映了与非门的带负载能力。

一般N o≥ 8。

扇入和扇出是反映门电路互连性能的指标。

(7)输入短路电流I iS:输入短路电流I iS是指当与非门的某一个输入端接地而其余输入端悬空时,流过接地输入端的电流。

在实际电路中,I iS是流入前级与非门的灌电流,它的大小将直接影响前级与非门的工作情况。

因此,对输入短路电流要加以限制,产品规范值I iS≤1.6mA。

(8)高电平输入电流I iH:高电平输入电流I iH是指某一输入端接高电平,而其他输入端接地时,流入高电平输入端的电流,又称为输入漏电流。

数字电路各章知识点第1章 逻辑代数基础一、 数制和码制1.二进制和十进制、十六进制的相互转换 2.补码的表示和计算 3.8421码表示二、 逻辑代数的运算规则1.逻辑代数的三种基本运算:与、或、非 2.逻辑代数的基本公式和常用公式 逻辑代数的基本公式(P10) 逻辑代数常用公式: 吸收律:A AB A =+消去律:AB B A A =+ A B A AB =+ 多余项定律:C A AB BC C A AB +=++ 反演定律:B A AB += B A B A ∙=+ B A AB B A B A +=+三、 逻辑函数的三种表示方法及其互相转换 ★ 逻辑函数的三种表示方法为:真值表、函数式、逻辑图 会从这三种中任一种推出其它二种,详见例1-6、例1-7 逻辑函数的最小项表示法 四、 逻辑函数的化简: ★1、 利用公式法对逻辑函数进行化简2、 利用卡诺图队逻辑函数化简3、具有约束条件的逻辑函数化简例1.1 利用公式法化简 BD C D A B A C B A ABCD F ++++=)( 解:BD C D A B A C B A ABCD F ++++=)(BD C D A B A B A ++++= )(C B A C C B A +=+ BD C D A B +++= )(B B A B A =+ C D A D B +++= )(D B BD B +=+ C D B ++= )(D D A D =+ 例1.2 利用卡诺图化简逻辑函数 ∑=)107653()(、、、、m ABCD Y 约束条件为∑8)4210(、、、、m 解:函数Y 的卡诺图如下:00 01 11 1000011110AB CD111×11××××D B A Y +=第2章集成门电路一、 三极管如开、关状态 1、饱和、截止条件:截止:beTV V < 饱和:CSBSBI iIβ>=2、反相器饱和、截止判断 二、基本门电路及其逻辑符号 ★与门、或非门、非门、与非门、OC门、三态门、异或、传输门(详见附表:电气图用图形符号 P321 )二、门电路的外特性★1、电阻特性:对TTL门电路而言,输入端接电阻时,由于输入电流流过该电阻,会在电阻上产生压降,当电阻大于开门电阻时,相当于逻辑高电平。

第3章 逻辑门电路门电路是构成各种复杂集成电路的基础,本章着重理解TTL 和CMOS 两类集成电路的外部特性:输出与输入的逻辑关系,电压传输特性。

1. TTL 与CMOS 的电压传输特性 开门电平ON V —保证输出为额定低电平 时所允许的最小输入高电平值在标准输入逻辑时,ON V =1.8V关门OFF V —保证输出额定高电平90%的情况下,允许的最大输入低电平值,在标准输入逻辑时,OFF V =0.8VIL V —为逻辑0的输入电压 典型值IL V =0.3V IH V —为逻辑1的输入电压 典型值IH V =3.0V OH V —为逻辑1的输出电压 典型值OH V =3.5V OL V —为逻辑0的输出电压 典型值OL V =0.3V对于TTL :这些临界值为V V OH 4.2min =,V V OL 4.0max = V V IH 0.2min =,V V IL 8.0max = 低电平噪声容限:IL OFF NL V V V -= 高电平噪声容限:ON IH NH V V V -=例:74LS00的V V OH 5.2min =)( V V OL 4.0(=出最小) V V IH 0.2min =)( V V IL 7.0max =)(它的高电平噪声容限 ON IH NH V V V -==3-1.8=1.2V 它的低电平噪声容限 IL OFF NL V V V -==0.8-0.3=0.5VV IOFF V ONV NHIL V2.TTL与COMS关于逻辑0和逻辑1的接法74HC00为CMOS与非门采用+5V电源供电,输入端在下面四种接法下都属于逻辑0①输入端接地②输入端低于1.5V的电源③输入端接同类与非门的输出电压低于0.1V④输入端接10ΩK电阻到地74LS00为TTL与非门,采用+5V电源供电,采用下列4种接法都属于逻辑1①输入端悬空②输入端接高于2V电压③输入端接同类与非门的输出高电平3.6V④输入端接10ΩK电阻到地。

cmos门电路的特点_CMOS门电路的工作原理及特性 - 电子技术MOS逻辑门电路是继TTL之后发展起来的另一种应用广泛的数字集成电路。

由于它功耗低、抗干扰能力强、工艺简单,几乎所有的大规模、超大规模数字集成器件都采用MOS工艺。

就其发展趋势看,MOS 电路特别是CMOS电路有可能超越TTL成为占统治地位逻辑器件。

CMOS逻辑门电路是由N沟道增强型MOS管和P沟道增强型MOS管互补而成,通常称为互补型MOS逻辑电路,简称CMOS逻辑电路。

下面以CMOS非门为例介绍CMOS门电路的工作原理及特性。

1、CMOS非门图1 CMOS非门基本电路(1)电路结构及工作原理CMOS非门的基本电路结构如图1所示,其中TP是P沟道增强型MOS 管,TN是N沟道增强型MOS管。

假如TP和TN的开启电压分别为UTP和UTN,则要求VDDUTP+UTN。

当输入为低电平,即ui=0时,TN截止,TP导通,故uo≈VDD,输出高电平。

当输入为高电平,即ui=VDD时,TP截止,TN导通,故uo≈0,输出低电平。

所以该电路实现了非逻辑。

通过以上分析可以看出,在CMOS非门电路中,无论电路处于何种状态,TP、TN中总有一个截止,所以它的静态功耗极低,有微功耗电路之称。

(2)电压传输特性在图1所示的CMOS非门电路中,设VDDUTP+UTN。

,且UTP=UTN,TP 和TN具有同样的导通内阻RON和截止内阻ROFF,则输出电压随输入电压变化的曲线,即电压传输特性如图2所示。

图2 CMOS非门的电压传输特性从图2所示的曲线上可以看出,CMOS非门的电压传输特性不仅有阀值电压UT=1/2VDD的特点,而且曲线转折区的曲率很大,因此更接近于理想的开关特性,从而使CMOS非门电路获得了更大的输入端噪声容限。

2、CMOS与非门电路CMOS与非门电路如图3所示。

驱动管TN1和TN2为N沟道增强型MOS管,两者串联,负载管TP1和TP2为P沟道增强型MOS管,两者并联,负载管整体与驱动管相串联。

数字电子技术——门电路3.1 概述1. 门电路是用以实现逻辑关系的电子电路,与基本逻辑关系相对应。

门电路主要有:与门、或门、与非门、或非门、异或门等。

2. 高低电平高电平:数字电路中较高电平代数值的范围。

低电平:数字电路中较低电平代数值的范围。

3. 正负逻辑正逻辑:用高电平代表1、低点平代表0。

在数字电路中,一般采用正逻辑系统。

负逻辑:用高电平代表0、低点平代表1。

图14. 集成电路IC(Integrated Circuits):将元、器件制作在同一硅片上,以实现电路的某些功能。

SSI(Small-Scale Integration):£ 10个门电路。

MSI(Medium-Scale Integration):10~100个门电路。

LSI(Large-Scale Integration):1000~10000个门电路。

VLSI(Very Large-Scale Integration):³ 10000个门电路。

3.2 半导体二极管门电路图2二极管加正向电压时导通,伏安特性很陡、压降很小(硅管为0.7V,锗管为0.3V),可以近似看作是一个闭合的开关。

二极管加反向电压时截止,反向电流很小(nA级),可以近似看作是一个断开的开关。

把uD<UT=0.5V看成是硅二极管的截止条件。

图3在低速脉冲电路中,二极管开关由接通到断开,或由断开到接通所需要的转换时间通常是可以忽略的。

然而在数字电路中,二极管开关经常工作在高速通断状态。

由于PN结中存储电荷的存在,二极管开关状态的转换不能瞬间完成,需经历一个过程。

tre=ts+tf 叫做反向恢复时间。

该现象说明,二极管在输入负跳变电压作用下,开始仍然是导通的,只有经过一段反向恢复时间tre之后,才能进入截止状态。

由于tre的存在,限制了二极管的开关速度。

图4图53.3 CMOS门电路MOS门电路:以MOS管作为开关元件构成的门电路。

MOS门电路,尤其是CMOS门电路具有制造工艺简单、集成度高、抗干扰能力强、功耗低、价格便宜等优点,得到了十分迅速的发展。

各种门电路特点《聊聊各种门电路的特点,嘿,还挺有趣!》嘿,大家好呀!今天咱来唠唠各种门电路的特点,这可是电子世界里相当有意思的一块儿呢!先来说说那个与门吧,它就像是个特别严格的“老学究”。

只有当所有输入都符合要求时,它才肯给出个高电平。

就好比你想进这个门,所有的条件都得达标,缺一不可,真是一点商量的余地都没有啊!要是有一个输入不满足,嘿,它就把门给你关得死死的。

接着讲讲或门,这哥们可就比较豪爽啦!只要有一个输入是高电平,它就大大咧咧地给出高电平。

就像那种只要有一个理由成立,就会放行的老好人。

或门的世界里,机会多多,比较宽松,感觉还挺畅快的呢!然后是那个非门,哇,这可是个叛逆的家伙!它专门和输入对着干,你给它个高电平,它就非得给你整个低电平出来。

就好像一个爱捣蛋的小鬼头,总是要唱反调,不过这也是它的魅力所在呀。

还有与非门和或非门,这俩可以说是前面那几位的变形金刚版。

与非门是先执行与门操作,然后再叛逆一下;或非门呢,则是先豪爽一把,完了再唱反调。

这俩就像是在原本的特点上又增加了一些特别的调料,让门电路的世界更加丰富多彩了。

在实际应用中,这些门电路就像我们生活中的各种工具一样,各有各的用处。

比如我们要设计一个复杂的电路系统,那就要好好挑选这些门电路,让它们各司其职,共同完成任务。

有时候需要严格把关的地方就用与门,需要多个机会的地方就用上或门,需要反转的地方非门就闪亮登场啦!哎呀,研究这些门电路的特点就像探索一个神秘而有趣的小宇宙。

每一个门都有自己独特的性格和行为方式,懂了它们,我们就能在电子的世界里畅游,创造出各种各样奇妙的电路。

总之呢,门电路的世界既严谨又有趣。

它们虽然看起来小小的,但却蕴含着大大的能量和智慧。

我们就好好地和它们玩耍,感受电子世界的魅力吧!希望我的这番感受能让大家对门电路的特点有更深刻的认识和理解,也希望大家能在这个神奇的领域里玩得开心,发现更多的惊喜!哈哈!。