基于FPGA的HDLC协议设计

- 格式:docx

- 大小:344.98 KB

- 文档页数:19

HDLC的FPGA实现方法摘要:HDLC(高级数据链路控制)的一般实现方法为采用ASIC器件和软件编程等。

应用ASIC器件时设计简单,但灵活性较差;软件编程方法灵活,但占用处理器资源多,执行速度慢,实时性不易预测。

FPGA器件采用硬件处理技术,可以反复编程,能够兼顾速度和灵活性,并能多路并行处理,实时性能能够预测和仿真。

在中小批量通信产品的设计中,FPGA是取代ASIC实现HDLC功能的一种合适选择。

采用Altera公司的FPGA芯片,在MAX+plus II软件平台上实现了多路HDLC电路的设计,并已在某通信产品样机中应用成功。

关键词:数据通信; HDLC;CRC校验;FPGA;MAX+plus II1 引言HDLC(High-level Data Link Control Procedures, 高级数据链路控制规程)广泛应用于数据通信领域,是确保数据信息可靠互通的重要技术。

实施HDLC的一般方法通常是采用ASIC(Application Specific I ntegrated Circuit,特定用途集成电路)器件和软件编程等。

HDLC的ASIC芯片有Motorola公司的MC92460、ST公司的MK5025、Zarlink公司的MT8952B等。

这些集成电路使用简易,功能针对性强,性能可靠,适合应用于特定用途的大批量产品中。

但由于HDLC 标准的文本较多,ASIC芯片出于专用性的目的难以通用于不同版本,缺乏应用灵活性。

例如CCITT、A NSI、ISO/IEC等都有各种版本的HDLC标准,有的芯片公司还有自己的标准,对HDLC的CRC(Cycl ical Redundancy Check,循环冗余码校验)序列生成多项式等有不同的规定。

况且,专用于HDLC的A SIC芯片其片内数据存储器容量有限,通常只有不多字节的FIFO(先进先出存储器)可用。

对于某些应用来说,当需要扩大数据缓存的容量时,只能对ASIC芯片再外接存储器或其它电路,ASIC的简单易用性就被抵销掉了。

一种基于FPGA的HDLC协议控制器

王鲁平;李飚;胡敏露

【期刊名称】《电子产品世界》

【年(卷),期】2003(000)06A

【总页数】2页(PU013-U014)

【作者】王鲁平;李飚;胡敏露

【作者单位】湖南长沙国防科技大学ATR—2室

【正文语种】中文

【中图分类】TN915.04

【相关文献】

1.HDLC协议RS-485总线控制器的FPGA实现 [J], 高振斌;陈禾;韩月秋

2.基于FPGA的HDLC协议控制器 [J], 应三丛;张行

3.基于FPGA的HDLC转E1传输控制器的实现 [J], 张强;刘辉;丁新宇

4.基于FPGA+ARM的HDLC协议控制器的设计与实现 [J], 杨尧;赵立立;侯翔昊

5.基于FPGA的高速同步HDLC通信控制器设计 [J], 陈晨;李志来;徐伟;金光因版权原因,仅展示原文概要,查看原文内容请购买。

HDLC协议IP核的设计(全文)《电子设计工程杂志》2014年第十一期1HDLC的帧结构首先回顾一下HDLC基本的帧结构形式。

HDLC是面向比特的链路控制规程,其链路监控功能通过一定的比特组合所表示的命令和响应来实现,这些监控比特和信息比特一起以帧的形式传送。

每帧的起始和结束以”7E”(01111110)做标志,两个”7E”之间为数据段(包括地址数据、控制数据、信息数据)和帧校验序列。

帧校验采用CRC算法,对除了插入的”零”以外的所有数据进行校验。

为了避免将数据中的”7E”误为标志,在发送端和接收端要相应地对数据流和帧校验序列进行”插零”及”删零”操作。

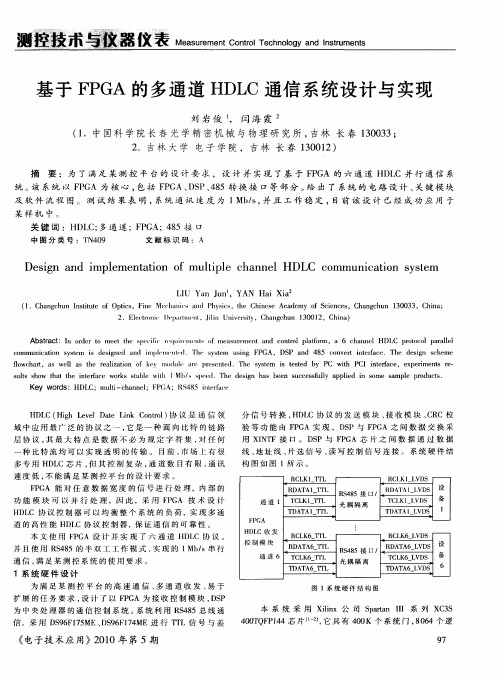

2原理框图基于FPGA的HDLC协议的实现原理框图如图1所示。

该框图包括3个部分:对外接口部分、HDLC发送部分、HDLC接收部分。

以下对3个部分的实现分别进行论述。

2.1对外接口模块对外接口部分主要实现HDLC对外的数据交换。

包括CPU接口、发送FIFO、发送接口、接收FIFO以及接收接口。

本设计是以总线的形式实现HDLC与外部CPU的通信。

当需要发送数据时,外部CPU通过总线将待发数据写入FIFO(FIFO的IP核在各开发软件中都是免费提供的,在程序中只需直接调用即可,故在此不再详细描述)。

之中。

发送数据准备就绪标志(TX_DAT_OK);接收数据时,当对外接口模块接收到数据有效信号时,根据接收模块发来的写信号(WR_MEM)将数据写入接收FIFO中。

接收完一帧数时向CPU 发送中断信号(INT),通知CPU读取数据。

2.2HDLC发送模块HDLC发送部分主要实现HDLC发送功能。

当接收到数据准备就绪标志(TX_DAT_OK)后,向对外接口模块发送读使能(RD_MEM_EN)和读信号(RD_MEM),通过局部总线将待发数据存入发送缓冲区,在T_CLK的控制下将数据从HDLC_TXD管脚发出。

数据发送模块采用状态机来完成发送各个阶段的切换。

状态切换流程图如图2所示。

HDLC协议协议名称:HDLC协议一、引言HDLC(High-Level Data Link Control)协议是一种数据链路层协议,用于在计算机网络中传输数据。

本协议定义了数据传输的规则和流程,确保数据的可靠传输和错误检测。

本协议适用于各种网络环境,包括有线和无线网络。

二、协议目的本协议的目的是规范数据的传输和控制,确保数据在网络中的可靠传输。

通过使用HDLC协议,可以提高数据传输的效率和可靠性,同时减少数据传输过程中的错误。

三、协议范围本协议适用于所有使用HDLC协议的数据传输场景,包括但不限于局域网、广域网和互联网。

四、协议规定1. 帧格式HDLC协议使用帧格式来传输数据。

帧格式如下:- 标志字节(8位):用于标识帧的开始和结束。

- 地址字节(8位):用于标识目标地址和源地址。

- 控制字节(8位):用于控制数据传输的流程。

- 数据字段(可变长度):用于传输实际的数据。

- 帧校验序列(16位):用于检测帧中的错误。

2. 帧传输流程HDLC协议使用以下流程来传输帧:- 发送方发送起始标志字节。

- 发送方发送地址字节,标识目标地址和源地址。

- 发送方发送控制字节,控制数据传输的流程。

- 发送方发送数据字段,包含实际的数据。

- 发送方发送帧校验序列,用于检测帧中的错误。

- 接收方接收帧,并进行错误检测。

- 接收方发送确认帧,表示接收成功。

- 发送方接收确认帧,并继续发送下一帧。

3. 流量控制HDLC协议使用滑动窗口机制进行流量控制,确保发送方和接收方之间的数据传输速度匹配。

发送方根据接收方的确认帧来调整发送速度,以避免数据丢失和传输错误。

4. 错误检测HDLC协议使用CRC(循环冗余校验)算法进行错误检测。

接收方在接收到帧后,计算CRC值并与帧中的校验序列进行比较,以确定帧中是否存在错误。

五、协议实施1. HDLC协议的实施应符合以下要求:- 发送方和接收方应使用相同的帧格式和流程。

- 发送方和接收方应使用相同的错误检测算法。

基于FPG平台的HDLC协议的应用与研究一、HDLC协议的介绍数据链路层协议根据数据帧操纵的格式可以分为:面向字符的数据链路层协议和面向比特的数据链路层协议。

HDLC协议是一种面向比特的数据链路协议。

在这类面向比特的数据链路协议中,帧头和帧尾都是特定的二进制序列,通过操纵字段来实现对链路的监控,可以采纳多种编码方式实现高效的、可靠的透明传输。

二、基于FPG平台的HDLC协议的实现1、初始模块的实现.在实现HDLC模块以前必须针对其完成初始化的相应流程以后方可正常进入工作运行装填。

这里的初始化具体来说是针对HDLC模块内部的各类寄存器进行参数上的配置,其中主要的寄存器类型有辅助寄存器、地址寄存器等。

而且地址寄存器的初始化尤为重要,一般当对这几类寄存器完成初始化配置后,系统会自动生成一个标识信号,如果信号显示为正常且有效的,那么其代表HDLC的初始化工作已经基本完成,且可以进入到下一步工作状态中。

而辅助配置寄存器的初始化则并不一定需要在该阶段中完成。

2、发送模块的实现。

在HDLC协议中,具体负责差错校检功能的为CRC校检模块,具体的帧发送模块的实现过程为:首先系统与CPU线路开始连接一户,然后数据开始被写入到FIFO 中,如果检测到某条线路正好处于未被资源占用的状态,那么CRC校验模块则开始对FIFO中的数据进行校验和插零程序。

同时,数据经过插零并发送以后,每一个数据序列必须添加包头和包围并以串行的形式被发送端传输出去,并且将帧标志的状态修改为“011111100”,这里笔者将以上组成发送模块的发送端分成四个部分,分别是fifomin、insert_0、crcme以及frme insert 等模块。

3、接收模块的设计。

HDLC协议中的接收模块在功能结构的组成方面和发送模块相类似,主要由CRC校验模块、操纵模块、数据锁存模块以及同步模块组成。

具体来说,系统中的操纵模块针对数据传输中的删零过程以及标识检验过程来进行。

HDLC协议协议名称:高级数据链路控制协议(HDLC)一、引言高级数据链路控制协议(HDLC)是一种数据链路层协议,用于在物理链路上进行可靠的数据传输。

本协议旨在确保数据的完整性、可靠性和有序性,并提供流量控制和错误检测机制。

本文档旨在详细描述HDLC协议的标准格式和相关内容。

二、协议结构HDLC协议采用帧结构进行数据传输,每个帧由特定的字段组成,包括起始标志(Flag)、地址字段、控制字段、信息字段、校验序列字段和结束标志(Flag)。

1. 起始标志(Flag):起始标志是一个特殊的字节,用于标识帧的开始和结束。

起始标志的值为01111110,表示一个字节的连续1后跟一个字节的0。

2. 地址字段:地址字段用于标识接收方的地址。

在单点通信中,地址字段通常为一个字节。

在多点通信中,地址字段可以是一个字节或多个字节。

3. 控制字段:控制字段用于指示帧类型和操作。

控制字段的长度可以是1个字节或2个字节,取决于具体的协议实现。

4. 信息字段:信息字段用于携带实际的数据。

信息字段的长度可以根据需求进行变化。

5. 校验序列字段:校验序列字段用于检测传输过程中的错误。

常用的校验序列算法包括循环冗余校验(CRC)和帧检验序列(FCS)。

6. 结束标志(Flag):结束标志与起始标志相同,用于标识帧的结束。

三、帧传输过程HDLC协议的帧传输过程包括帧的发送和接收两个阶段。

1. 帧的发送过程:(1)发送方检测到数据需要传输,并准备好发送帧。

(2)发送方在数据帧前插入起始标志。

(3)发送方添加地址字段,指示接收方的地址。

(4)发送方添加控制字段,指示帧类型和操作。

(5)发送方添加信息字段,携带实际的数据。

(6)发送方计算校验序列,并添加到帧中。

(7)发送方插入结束标志。

(8)发送方将帧发送到物理链路上。

2. 帧的接收过程:(1)接收方监听物理链路,等待帧的到达。

(2)接收方检测到起始标志,开始接收帧。

(3)接收方解析地址字段,判断是否为自己的地址。

多通道HDLC协议的FPGA实现

李娜;王英民

【期刊名称】《计算机测量与控制》

【年(卷),期】2009(017)008

【摘要】为满足某遥控遥测平台的特定要求,提出了一种新的基于FPGA的并行机制HDLC协议控制器,在实验中,分别对发送和接收电路模块进行了分析,给出了在ModelSim SE 6.1环境下的仿真波形;同时考虑到单板的影响,在单板上进行回环测试,实验结果表明验证了设计的正确性和可靠性,目前该设计已成功应用于某通信样机中.

【总页数】3页(P1608-1609,1612)

【作者】李娜;王英民

【作者单位】西北工业大学航空调放声纳研究中心,陕西,西安,710072;西北工业大学航空调放声纳研究中心,陕西,西安,710072

【正文语种】中文

【中图分类】TN919

【相关文献】

1.一种HDLC协议多通道通信卡的设计与实现 [J], 邓凤军;张龙;王益忠

2.基于FPGA的USB-HDLC协议转换器的设计与实现 [J], 杨峰;秦兆涛

3.基于FPGA的多通道HDLC协议处理器设计与实现 [J], 席利君

4.符合中国移动标准协议转换器中的HDLC协议的FPGA设计与实现 [J], 刘宇;张

斌;徐东明

5.基于FPGA的多通道HDLC通信系统设计与实现 [J], 刘岩俊;闫海霞

因版权原因,仅展示原文概要,查看原文内容请购买。