译码器和编码器实验

- 格式:doc

- 大小:94.00 KB

- 文档页数:5

QCA编码器和译码器摘要:基于量子元胞自动机的双稳态特性和数字电路,依据不同设计原理设计了编码器和译码器,采用半经典仿真方法进行仿真,同时与E.N.Ganesh 等人设计的译码器进行了比较,结果显示,在同样实现译码器功能的前提下,电路结构较为简单并且规模较小,运用基本功能电路的组合使电路容易分析,对以后的电路设计也有一定的借鉴意义。

关键词: 量子通信编码器译码器QCA电路设计与仿真1.引言微电子器件的集成度和运算速度已持续呈指数级增长近40 年, 为了保持这种快速的增长,集成电路制造的各个方面都需有快速的改进【1】。

但当电子器件的尺寸达到70 nm 时, 由于功率耗散和相互连接等问题使得基于传统CMOS 技术的器件尺寸的进一步减小变得不太可能[2]。

有研究认为, 到2020 年, 晶体管的尺寸将达到它的物理极限。

这就需要发展一种不同于传统CMOS 的器件技术来使电子器件能继续朝纳米级方向发展。

近年来, 有些学者提出量子细胞自动机[ 3- 5] ( quantum cellular automaton, QCA)的结构, 在用分子实现时, 其特征尺寸仅为几纳米。

它是通过电子在细胞上占据的位置来携带二进制信息, 而不是通过传统的电流开关来表示二进制信息。

它提供了一种新的计算和信息转换的方式, 具有低功耗、高集成度和无引线集成等优点, 将是新一代的电子元件之一。

本文结合QCA和数字电路相关知识和化简思想的设计了编码器和译码器,对于2线-4线译码器,与E.N.Ganesh等人设计的译码器[6]进行了比较,显示出本文设计的同级别的译码器电路结构简单和规模小的优点,同时对于提出编码器及译码器位数扩展的方法。

此外,此电路设计中采用基本QCA器件组合和相同逻辑功能电路合并的思想,具较强的普适性,对以后的电路设计也有一定的借鉴意义。

2.量子元胞自动机的基本元素QCA是由基本的逻辑器件组成的,这些基本量子器件主要有含有两个静电子的标准元胞和旋转元胞,每个元胞通过内部电子所处的位置定义它的极性,元胞之间极性的传递或改变是依靠两元胞间电子的库仑作用和元胞内电子的隧穿作用,每个元胞中的电子被高度极化,电子云密度沿元胞两个垂直的对角分布中的一个方向分布,一个元胞的极化能引起临近元胞的极化,从而实现数据的传递。

编码器与译码器的结构与功能分析编码器与译码器是数字电子领域中两个重要的电路器件。

编码器用于将不同类型的输入信号转换为特定的输出编码形式,而译码器则将编码后的信号转换回原始信号。

本文将分析编码器与译码器的结构和功能,并探讨它们在现代电子技术中的应用。

一、编码器的结构与功能编码器通常有多种不同的输入,但只有一种输出。

其主要功能是将输入信号转换为特定的编码形式,以方便传输、存储或处理。

编码器可根据输入信号的类型和数量的不同而各异。

以下是几种常见的编码器类型及其结构和功能:1. 优先级编码器:优先级编码器是一种将多个输入信号转换为二进制编码的器件。

它包括输入端口、编码器电路和输出端口。

优先级编码器的输出是一个二进制编码,它表示最高优先级的输入信号。

2. 行程编码器:行程编码器常用于检测和测量旋转或线性运动的位置。

它能够将物理位置转换为二进制编码形式,并输出到接口电路进行进一步处理。

3. 绝对值编码器:绝对值编码器将旋转或线性位置转换为唯一的二进制编码序列。

每个位置都对应一个特定的编码,不会受到电源中断等干扰的影响。

旋转编码器用于检测旋转运动,如手柄、旋钮等。

它通过旋转产生的脉冲数来确定方向和速度,并将其转换为二进制编码输出。

5. 模数转换器:模数转换器是一种将模拟信号转换为数字信号的编码器。

它常用于数据采集、音频处理和传感器信号数字化等领域。

二、译码器的结构与功能译码器是编码器的逆过程,用于将编码信号恢复为原始信号。

它的结构和功能与编码器正好相反。

以下是几种常见的译码器类型及其结构和功能:1. 优先级译码器:优先级译码器能够将编码信号转换为对应的优先级输入信号。

它包括译码器电路和输出端口。

2. 行程译码器:行程译码器常用于将二进制编码转换为对应的位置信息。

它通过解码从编码器中获取的编码信号来确定物理位置。

3. 绝对值译码器:绝对值译码器将二进制编码转换为对应的旋转或线性位置信息。

它能够恢复旋转编码器或模数转换器编码后的数据。

编码器实验报告编码器实验报告引言编码器是一种重要的数字电路设备,用于将输入的信息转换为特定的编码形式。

在现代科技发展中,编码器广泛应用于通信、计算机、电子设备等领域。

本实验旨在通过设计和实现一个简单的编码器电路,深入了解编码器的原理和应用。

实验目的1. 了解编码器的基本原理和分类;2. 学习编码器的设计方法和实现技巧;3. 掌握编码器的应用场景和使用方法。

实验原理编码器是一种多对一的数字电路设备,通过对输入信号进行编码,将多个输入状态映射为唯一的输出状态。

常见的编码器有优先编码器、旋转编码器、格雷码编码器等。

1. 优先编码器优先编码器是一种将多个输入状态按照优先级进行编码的设备。

当多个输入同时有效时,只有优先级最高的输入被编码输出。

优先编码器常用于优先级译码器和多路选择器中。

2. 旋转编码器旋转编码器是一种通过旋转操作来改变输出状态的设备。

它通常由一个旋转轮和两个感应器组成,感应器用于检测旋转轮的方向和速度。

旋转编码器常用于旋钮、鼠标滚轮等设备中。

3. 格雷码编码器格雷码编码器是一种将二进制输入信号转换为格雷码输出信号的设备。

格雷码是一种特殊的二进制编码形式,相邻的两个码字只有一位不同,避免了二进制编码中的多位错误。

格雷码编码器常用于数字显示器、光电编码器等设备中。

实验过程本实验以优先编码器为例,设计和实现一个4输入优先编码器电路。

1. 确定输入和输出端口根据实验要求,我们需要设计一个4输入优先编码器,因此需要确定4个输入端口和1个输出端口。

2. 绘制逻辑电路图根据优先编码器的原理,我们可以绘制出如下的逻辑电路图:(图略)3. 确定逻辑门类型根据逻辑电路图,我们可以确定每个逻辑门的类型。

在本实验中,我们选择使用与门和或门。

4. 搭建电路实验平台根据逻辑电路图,我们可以搭建实验平台,连接逻辑门和输入输出端口。

5. 进行实验测试将不同输入信号输入到优先编码器中,观察输出信号的变化。

测试不同输入组合下的编码输出结果。

实验九 (2,1,5)卷积码编码译码技术一、实验目的1、掌握(2,1,5)卷积码编码译码技术2、了解纠错编码原理。

二、实验内容1、(2,1,5)卷积码编码。

2、(2,1,5)卷积码译码。

三、预备知识1、纠错编码原理。

2、(2,1,5)卷积码的工作原理。

四、实验原理/卷积码是将发送的信息序列通过一个线性的,有限状态的移位寄存器而产生的编码。

通常卷积码的编码器由K级(每级K比特)的移位寄存器和n个线性代数函数发生器(这里是模2加法器)组成。

若以(n,k,m)来描述卷积码,其中k为每次输入到卷积编码器的bit数,n 为每个k元组码字对应的卷积码输出n元组码字,m为编码存储度,也就是卷积编码器的k元组的级数,称m+1= K为编码约束度m称为约束长度。

卷积码将k 元组输入码元编成n元组输出码元,但k和n通常很小,特别适合以串行形式进行传输,时延小。

与分组码不同,卷积码编码生成的n元组元不仅与当前输入的k元组有关,还与前面m-1个输入的k元组有关,编码过程中互相关联的码元个数为n*m。

卷积码的纠错性能随m的增加而增大,而差错率随N的增加而指数下降。

在编码器复杂性相同的情况下,卷积码的性能优于分组码。

编码器随着信息序列不断输入,编码器就不断从一个状态转移到另一个状态并同时输出相应的码序列,所以图3所示状态图可以简单直观的描述编码器的编码过程。

因此通过状态图很容易给出输入信息序列的编码结果,假定输入序列为110100,首先从零状态开始即图示a状态,由于输入信息为“1”,所以下一状态为b并输出“11”,继续输入信息“1”,由图知下一状态为d、输出“01”……其它输入信息依次类推,按照状态转移路径a->b->d->c->b->c->a输出其对应的编码结果“”。

译码方法⒈代数代数译码是将卷积码的一个编码约束长度的码段看作是[n0(m+1),k0(m+1)]线性分组码,每次根据(m+1)分支长接收数字,对相应的最早的那个分支上的信息数字进行估计,然后向前推进一个分支。

4-2 编码器与译码器1 .问题引入 (introduction)•从对实训 4 的实验结果分析,引入编码器和译码器的概念。

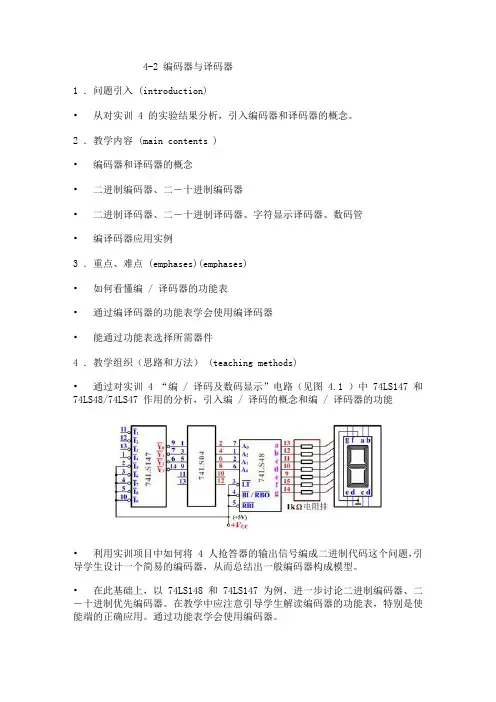

2 .教学内容 (main contents )•编码器和译码器的概念•二进制编码器、二-十进制编码器•二进制译码器、二-十进制译码器、字符显示译码器、数码管•编译码器应用实例3 .重点、难点 (emphases)(emphases)•如何看懂编 / 译码器的功能表•通过编译码器的功能表学会使用编译码器•能通过功能表选择所需器件4 .教学组织(思路和方法) (teaching methods)•通过对实训 4 “编 / 译码及数码显示”电路(见图 4.1 )中 74LS147 和74LS48/74LS47 作用的分析,引入编 / 译码的概念和编 / 译码器的功能•利用实训项目中如何将 4 人抢答器的输出信号编成二进制代码这个问题,引导学生设计一个简易的编码器,从而总结出一般编码器构成模型。

•在此基础上,以 74LS148 和 74LS147 为例,进一步讨论二进制编码器、二-十进制优先编码器。

在教学中应注意引导学生解读编码器的功能表,特别是使能端的正确应用。

通过功能表学会使用编码器。

•对常用编码的特点及如何选择编码器等内容可要求学生自学。

•在前面的分析中,学生已经建立了译码的概念,通过分析一个简单的两位二进制代码译码器的构成,总结出一般译码器的构成模型,如图 4.6 所示。

图 4.6 译码器示意图•在此基础上,以 74LS138 、 74LS42 和 74LS47 为例,进一步讨论二进制译码器、二-十进制译码器和字符显示译码器。

在教学中应注意引导学生解读译码器的功能表,特别是使能端的正确应用,通过功能表学会使用译码器。

•显示器件只介绍 LED 显示电路,注意强调数码管的共阴和共阳极连接的区别,以及它们和显示译码器的连接使用。

• LCD 显示电路为学生自学内容。

•编 / 译码器应用实例一节,可在编码器和译码器的应用中各选一个应用实例介绍,例如“微控制器报警编码电路”和“译码器作地址译码器”。

实验四 译码器、编码器及其应用实验人员: 班号: 学号:一、实验目的(1) 掌握中规模集成译码器的逻辑功能和使用方法; (2) 熟悉掌握集成译码器和编码器的应用; (3) 掌握集成译码器的扩展方法。

二、实验设备数字电路实验箱,74LS20,74LS138。

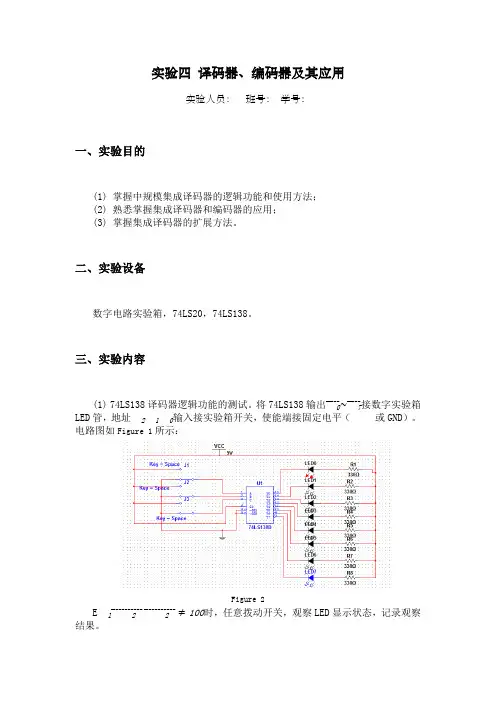

三、实验内容(1) 74LS138译码器逻辑功能的测试。

将74LS138输出Y 0̅̅̅̅~Y 7̅̅̅̅接数字实验箱LED 管,地址Y 2Y 1Y 0输入接实验箱开关,使能端接固定电平(Y YY 或GND )。

电路图如Figure 1所示:Figure 2E Y 1YY 2Y ̅̅̅̅̅̅̅̅̅̅ YY 2Y ̅̅̅̅̅̅̅̅̅̅≠100时,任意拨动开关,观察LED 显示状态,记录观察结果。

E Y 1YY 2Y ̅̅̅̅̅̅̅̅̅̅ YY 2Y̅̅̅̅̅̅̅̅̅̅=100时,按二进制顺序拨动开关,观察LED 显示状态,并与功能表对照,记录观察结果。

用Multisim 进行仿真,电路如Figure 3所示。

将结果与上面实验结果对照。

Figure 4(2) 利用3-8译码器74LS138和与非门74LS20实现函数:Y =Y ̅̅̅Y ̅̅̅+Y ̅̅̅Y ̅̅̅+YYY四输入与非门74LS20的管脚图如下:对函数表达式进行化简:Y =Y ̅̅̅Y ̅̅̅+Y ̅̅̅Y ̅̅̅+YYY =Y ̅̅̅Y ̅̅̅Y ̅̅̅+Y ̅̅̅Y ̅̅̅Y +A Y ̅̅̅Y ̅̅̅+YYY=Y 0+Y 1+Y 4+Y 7=Y 0̅̅̅̅Y 1̅̅̅̅Y 4̅̅̅̅Y 7̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅按Figure 5所示的电路连接。

并用Multisim 进行仿真,将结果对比。

Figure 6(3) 用两片74LS138组成4-16线译码器。

因为要用两片3-8实现4-16译码器,输出端子数目8×2=16刚好够用。

而输入端只有A、B、C三个,故要另用使能端进行片选使两片138译码器进行分时工作。

第1篇一、实验目的1. 熟悉数字电路实验的基本操作流程;2. 掌握基本数字电路的组成和原理;3. 培养动手能力和问题解决能力。

二、实验设备1. 数字电路实验箱;2. 万用表;3. 导线;4. 面包板;5. 计算器。

三、实验内容1. 基本逻辑门电路实验2. 组合逻辑电路实验3. 时序逻辑电路实验四、实验原理1. 基本逻辑门电路:逻辑门电路是数字电路的基础,包括与门、或门、非门、异或门等。

通过这些逻辑门电路的组合,可以实现复杂的逻辑功能。

2. 组合逻辑电路:组合逻辑电路由基本逻辑门电路组成,其输出仅取决于当前输入信号。

常见的组合逻辑电路有编码器、译码器、多路选择器等。

3. 时序逻辑电路:时序逻辑电路由触发器组成,其输出不仅取决于当前输入信号,还与电路的历史状态有关。

常见的时序逻辑电路有计数器、寄存器、触发器等。

五、实验步骤1. 基本逻辑门电路实验(1)按照实验指导书的要求,搭建与门、或门、非门、异或门等逻辑门电路;(2)使用万用表测量各逻辑门的输入、输出电压;(3)根据实验数据,验证各逻辑门的功能。

2. 组合逻辑电路实验(1)按照实验指导书的要求,搭建编码器、译码器、多路选择器等组合逻辑电路;(2)使用万用表测量各组合逻辑电路的输入、输出电压;(3)根据实验数据,验证各组合逻辑电路的功能。

3. 时序逻辑电路实验(1)按照实验指导书的要求,搭建计数器、寄存器、触发器等时序逻辑电路;(2)使用万用表测量各时序逻辑电路的输入、输出电压;(3)根据实验数据,验证各时序逻辑电路的功能。

六、实验结果与分析1. 基本逻辑门电路实验实验结果显示,与门、或门、非门、异或门等逻辑门电路的功能与理论分析一致。

2. 组合逻辑电路实验实验结果显示,编码器、译码器、多路选择器等组合逻辑电路的功能与理论分析一致。

3. 时序逻辑电路实验实验结果显示,计数器、寄存器、触发器等时序逻辑电路的功能与理论分析一致。

七、实验总结通过本次实验,我熟悉了数字电路实验的基本操作流程,掌握了基本数字电路的组成和原理,提高了动手能力和问题解决能力。

项目十ASK编码器与译码器设计1.实训目标1)设计m序列发生器;2)设计ASK编码器;3)设计ASK译码器;4)在EDA-V平台上实现该设计,并使用示波器观察并记录输出波形。

2.实训内容1)根据系统框图完成信号发生器的设计。

2)在EDA-V系统上实现该设计。

3)使用示波器观察ASK译码器的输出波形,将此波形与ASK编码器的输入波形进行比较,看ASK编译码是否成功,并记录波形的频率以及幅值。

3.实训数据1)画出所设计的系统原理图,并附上每个模块的程序代码。

Mser代码如下:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity mser isport( clk : in std_logic;load : in std_logic;mserout : out std_logic);end mser;architecture one of mser issignal msecom : std_logic_vector(3 downto 0); beginprocess(clk)beginif clk'event and clk = '1' thenif load = '0' thenmsecom <= "1110";mserout <= msecom(3);elsemsecom(3 downto 1) <= msecom(2 downto 0);msecom(0) <= msecom(3) xor msecom(0);mserout <= msecom(3);end if;end if;end process;end one;askdec代码如下:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity askdec isgeneric(cntperiod : integer:= 7);port(clk : in std_logic;askcodein : in std_logic;dataout : out std_logic);end askdec;architecture behave of askdec issignal cnt :integer range 0 to 255;signal datacom : std_logic_vector(1 downto 0);signal datareg : std_logic;beginprocess(clk)beginif clk'event and clk = '1' thendatacom <= askcodein & datacom(1);end if;end process;process(clk)beginif clk'event and clk = '1' thenif datacom = "10" thenif (cnt < cntperiod + 2) and (cnt > cntperiod - 2) then dataout <= '1';cnt <= 0;end if;elsif cnt > (cntperiod + 1) thendataout <= '0';cnt <= 0;elsecnt <= cnt + 1;end if;end if;end process;end behave;askcode代码如下:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all; entity askcode isgeneric(cnthigh : integer:= 3;cntperiod : integer:= 7);port(clk : in std_logic;datain : in std_logic; askcodeout : out std_logic);end askcode;architecture behave of askcode is signal fsig : std_logic;signal cnt : integer range 0 to 255; beginprocess(clk)beginif clk'event and clk = '1' thenif cnt = cnthigh thenfsig <= '1';cnt <= cnt + 1;elsif cnt = cntperiod thenfsig <= '0';cnt <= cnt + 1;cnt <= 0;elsecnt <= cnt + 1;end if;end if;end process;process(clk)beginif clk'event and clk = '1' thenif datain = '1' thenaskcodeout <= fsig;elseaskcodeout <= '0';end if;end if;end process;end behave;2) 记录仿真结果,要求至少包括10个周期的仿真输出数据。

第1篇一、实验目的本次逻辑电路实验实训旨在使学生掌握逻辑电路的基本原理和设计方法,提高学生动手实践能力和分析问题、解决问题的能力。

通过实验,使学生能够熟练运用逻辑门电路、触发器、计数器等基本逻辑电路,设计简单的数字电路系统。

二、实验内容1. 逻辑门电路实验(1)实验目的:掌握逻辑门电路的基本原理,验证逻辑门电路的功能。

(2)实验内容:实验电路包括与门、或门、非门、异或门等,通过搭建电路,观察输入输出关系,验证逻辑门电路的功能。

(3)实验步骤:① 搭建与门电路,观察输入输出关系;② 搭建或门电路,观察输入输出关系;③ 搭建非门电路,观察输入输出关系;④ 搭建异或门电路,观察输入输出关系。

2. 触发器实验(1)实验目的:掌握触发器的基本原理,验证触发器的功能。

(2)实验内容:实验电路包括D触发器、JK触发器、T触发器等,通过搭建电路,观察输入输出关系,验证触发器的功能。

(3)实验步骤:① 搭建D触发器电路,观察输入输出关系;② 搭建JK触发器电路,观察输入输出关系;③ 搭建T触发器电路,观察输入输出关系。

3. 计数器实验(1)实验目的:掌握计数器的基本原理,验证计数器的功能。

(2)实验内容:实验电路包括二进制计数器、十进制计数器等,通过搭建电路,观察输入输出关系,验证计数器的功能。

(3)实验步骤:① 搭建二进制计数器电路,观察输入输出关系;② 搭建十进制计数器电路,观察输入输出关系。

4. 译码器实验(1)实验目的:掌握译码器的基本原理,验证译码器的功能。

(2)实验内容:实验电路包括2-to-4译码器、3-to-8译码器等,通过搭建电路,观察输入输出关系,验证译码器的功能。

(3)实验步骤:① 搭建2-to-4译码器电路,观察输入输出关系;② 搭建3-to-8译码器电路,观察输入输出关系。

5. 编码器实验(1)实验目的:掌握编码器的基本原理,验证编码器的功能。

(2)实验内容:实验电路包括2-to-4编码器、3-to-8编码器等,通过搭建电路,观察输入输出关系,验证编码器的功能。

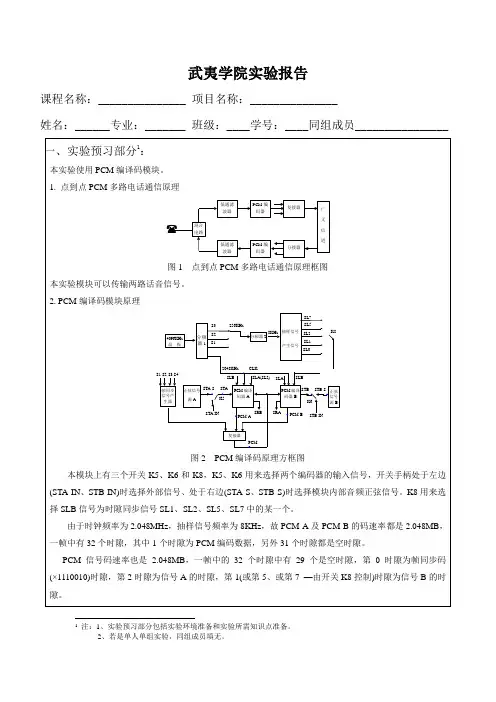

实验四脉冲编码调制(pcm)实验一、实验目的通过本实验,学生应达到以下要求: 1,了解语音信号pcm编译码的工作原理及实现过程. 2,验证pcm编译码原理. 3,初步了解pcm专用大规模集成电路的工作原理和应用. 4,了解语音信号数字化技术的主要指标,学习并掌握相应的测试方法.二、实验内容本实验可完成以下实验内容:? 观察测量pcm调制解调的各种时隙信号 ? 观察编译码波形? 测试动态范围、信噪比和系统频率特性 ? 对系统性能指标进行测试和分析? 系统输出信噪比特性测量? 编码动态范围和系统动态范围测量 ? 系统幅频特性测量 ? 空载噪声测量三、基本原理脉冲编码(pcm)技术已经在数字通信系统中得到了广泛的应用.十多年来,由于超大规模集成技术的发展,pcm通信设备在缩小体积,减轻重量,降低功耗,简化调试以及方便维护等方面都有了显著的改进.目前,数字电话终端机的关键部件,如编译码器(codec)和话路滤波器等都实现了集成化.本实验是以这些产品编排的 pcm 编译码系统实验,以期让实验者了解通信专用大规模集成电路在通信系统中应用的新技术. pcm 数字电话终端机的构成原理如图 4.1 所示.实验只包括虚线框内的部分,故名 pcm编译码实验.发滤波器voice编码器合路发混合装置收滤波器译码器分路收图4.1 pcm数字电话终端机的结构示意图1、实验原理和电路说明pcm编译码系统由定时部分和pcm编译码器构成,电路原理图附于本章后. ? pcm编译码原理为适应语音信号的动态范围,实用的pcm编译码必须是非线性的.目前,国际上采用的均是折线近似的对数压扩特性.itu-t 的建议规定以 13 段折线近似的 a 律(a=87.56)和 15段折线近似的μ律(μ=255)作为国际标准.a 律和μ律的量化特性初始段如图 4.2 和图 4.3所示.a律和μ律的编译码表分别列于表1和表2.(附本章后) 这种折线近似压扩特性的特点是:各段落间量阶关系都是 2 的幂次,在段落内为均匀分层量化,即等间隔16个分层,这些对于用数字电路实现非线性编码与译码是极为方便的. ? pcm编译码器简介鉴于我国国内采用的是a律量化特性,因此本实验采用tp3067专用大规模集成电路,它是cmos工艺制造的单片pcma律编译器,并且片内带输入输出话路滤波器. tp3067的管脚如图4.4所示,内部组成框图如图4.5所示. tp3067的管脚定义简述如下:(1)vpo+ 收端功率放大器的同相输出端.(2)gnda 模拟地.所有信号都以此管脚为参考. (3)vpo- 收端功放的反相输出端.(4)vpi 收端功放的反相输入端.(5)vfro 接收部分滤波器模拟输出端. (6)vcc +5v电压输入.(7)fsr接收部分帧同步时隙信号,是一个8khz脉冲序列. (8)dr接收部分pcm码流解码输入端.(9)bclkr/clksel位时钟(bitclock),它使pcm码流随着fsr上升沿逐位移入dr端,位时钟可以为从 64khz 到 2048mhz 的任意频率.或者作为一个逻辑输入选择 1536mhz,1544mhz或2048mhz,用作同步模式的主时钟.(10)mclkr/pdn接收部分主时钟,它的频率必须为1536mhz,1544mhz或2048mhz.可以和mcklx异步,但是同步工作时可达到最佳状态.当 mclkx 接低电平,mclkr被选择为内部时钟,当 mclkx接高电平,该芯片进入低功耗状态.(11)mclkx发送部分主时钟,必须为1536mhz,1544mhz或2048mhz.可以和mclkr异步,但是同步工作时可达到最佳状态.(12)bclkx发送部分时钟,使pcm码流逐位移入dr端.可以为从64khz到2048mhz的任意频率,但必须和mclkx同步.(13)dx发送部分pcm码流编码输出端.(14)fsx发送部分帧同步时隙信号,为一个8khz的脉冲序列. (15)tsx漏极开路输出端,它在编码时隙输出低电平.(16)anlb 模拟反馈输入端.在正常工作状态下必须置成逻辑0.当置成逻辑1时,发送部分滤波器的输入端并不与发送部分的前置滤波器相连,而是和接收部分功放的vpo+相连.(17)gsx发送部分输入放大器的模拟基础,用于在外部同轴增益. (18)vfxi发送部分输入放大器的反相输入端。

一、实验目的1. 理解译码器的原理和功能。

2. 掌握译码器的应用和实现方法。

3. 培养动手能力和团队协作精神。

二、实验原理译码器是一种将二进制编码信号转换为特定信号的电路。

在数字系统中,译码器广泛应用于地址译码、数据译码、指令译码等方面。

本实验主要研究译码器的原理、设计和实现。

三、实验设备1. 74LS138译码器芯片;2. 数字实验箱;3. 逻辑电平测试仪;4. 线路板;5. 连接线。

四、实验内容1. 译码器原理分析;2. 译码器设计;3. 译码器电路搭建;4. 译码器功能测试。

五、实验步骤1. 译码器原理分析首先,分析译码器的工作原理。

译码器由编码器、译码电路和输出电路组成。

编码器将输入信号转换为二进制编码信号,译码电路根据编码信号输出对应的信号,输出电路将译码电路输出的信号转换为所需的信号。

2. 译码器设计根据实验要求,设计译码器电路。

本实验采用74LS138译码器芯片,该芯片具有3个输入端和8个输出端。

根据输入信号的不同组合,输出对应的信号。

3. 译码器电路搭建(1)将74LS138译码器芯片插入数字实验箱的相应位置。

(2)根据译码器电路原理图,将输入端和输出端连接到实验箱的相应位置。

(3)检查电路连接是否正确,确保无短路和断路现象。

4. 译码器功能测试(1)将译码器输入端连接到逻辑电平测试仪。

(2)设置输入端信号,观察输出端信号。

(3)验证译码器输出信号是否符合预期。

六、实验结果与分析1. 实验结果实验过程中,根据译码器原理和设计,成功搭建了译码器电路。

在输入端设置不同的信号组合,输出端信号符合预期。

2. 实验分析本实验验证了译码器的原理和功能。

通过实验,我们了解到译码器在数字系统中的应用和实现方法。

在实验过程中,我们学会了如何设计译码器电路,如何搭建电路,以及如何进行功能测试。

七、实验总结1. 通过本次实验,掌握了译码器的原理和功能。

2. 学会了译码器的设计方法和实现过程。

3. 培养了动手能力和团队协作精神。

实验三译码器和编码器

一实验目的

1.掌握译码器、编码器的工作原理和特点。

2.熟悉常用译码器、编码器的逻辑功能和它们的典型应用。

二、实验原理和电路

按照逻辑功能的不同特点,常把数字电路分两大类:一类叫做组合逻辑电路,另一类称为时序逻辑电路。

组合逻辑电路在任何时刻其输出的稳态值,仅决定于该时刻各个输入信号取值组合的电路。

在这种电路中,输入信号作用以前电路所处的状态对输出信号无影响。

通常,组合逻辑电路由门电路组成。

组合逻辑电路的分析方法:根据逻辑图进行二步工作:

a.根据逻辑图,逐级写出函数表达式。

b.进行化简:用公式法、图形法或真值表进行化简、归纳。

组合逻辑电路的设计方法:就是从给定逻辑要求出发,求出逻辑图。

一般分四步进行。

a.分析要求;将问题分析清楚,理清哪些是输入变量,哪些是输出函数。

b.列真值表。

c.进行化简:变量比较少时,用图形法。

变量多时,可用公式化简。

d.画逻辑图:按函数要求画逻辑图。

进行前四步工作,设计已基本完成,但还需选择元件——集成电路,进行实验论证。

值得注意的是,这些步骤并不是固定不变的程序,实际设计时,应根据具体情况和问题难易程度进行取舍。

1.译码器

译码器是组合电路的一部分,所谓译码,就是把代码的特定含义“翻译”出来的过程,而实现译码操作的电路称为译码器。

译码器分成三类:

a.二进制译码器:如中规模2—4线译码器74LS139。

,3—8线译码器74LS138等。

b.二—十进制译码器:实现各种代码之间的转换,如BCD码—十进制译码器74LS145等。

c.显示译码器:用来驱动各种数字显示器,如共阴数码管译码驱动74LS48,(74LS248),共阳数码管译码驱动74LS47(74LS247)等。

2.编码器

编码器也是组合电路的一部分。

编码器就是实现编码操作的电路,编码实际上是译码相反的过程。

按照被编码信号的不同特点和要求,编码器也分成三类:

a.二进制编码器:如用门电路构成的4—2线,8—3线编码器等。

b.二—十进制编码器:将十进制的0~9编成BCD码,如:10线十进制—4线BCD码编码器74LS147等。

c.优先编码器:如8—3线优先编码器74LS148等。

三、实验内容及步骤

1.译码器实验

(1)将二进制2-4线译码器74LS139,及二进制3-8译码器74LS138分别插入实验系统IC 空插座中。

按图1.3.1接线,输入G、A、B信号(开关开为“1”、关为“0”),观察LED输出Yo、Y1、Y2、Y3的状态(亮为“1”,灭为“0”),并将结果填入表1.3.1中。

表 1.3.1 74LS139 2-4线译码器功能表

图1.3.1 74LS139 2-4线译码器实验线路

表1.3.2 74LS138 3-8线译码器功能表

图1.3.2 74LS138 3-8线译码实验线路

按图1.3.2接线,使能信号G 1,G 2A ,G 2B 满足表1.3.2条件时(开关开为“1”、关为“0”),

译码器选通。

输入G 1、G 2A 、G 2B 、A 、B 、C 信号(开关开为“1”、关为“0”),观察LED 输出Yo ~Y 7(亮为“1”,灭为“0”)。

(2)将BCD 码—十进制译码器74LS145插入实验箱中,按图1.3.3接线。

其中BCD 码是用XK 系列实验系统的8421码拨码开关,输出“0~9”与发光二极管LED 相连。

按动拨码开关,观察输出LED 是否和拨码开关所指示的十进制数字一致。

(3)将译码驱动器74LS48(或74LS248)和共阴极数码管LC5011-11(547R )插入实验箱空IC 插座中,按图1.3.5接线。

图1.3.4为共阴极数码管管脚排列图。

接通电源后,观察数码管显示结果是否和拨码开关指示数据一致( )。

如实验箱中无8421码拨码开关,可用四位逻辑开关代替。

输 入

输 出 G B A Yo Y 1 Y 2 Y 3

1 0 0 0 0

× 0 0 1 1

× 0 1 0 1

1

1

1

1

输 入 输 出

使能

选择

YO Y1 Y2 Y3 Y4 Y5 Y6 Y7 G1 G2=(G2A+G2B ) C B A

× 1 0 × 1 0 1 0 1 0 1 0 1 0 1 0 1 0

1 0

× × × × × × 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1

1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

图1.3.3 BCD码—十进制译码器实验线路图图1.3.4 共阴极数码管LC5011-11管脚排

列图

图1.3.5译码显示实验图

2.编码器

(1)将10-4线(十进制-BCD码)优先编码器74LS147插入实验系统IC空插座中,按照图1.3.6接线,其中输入接9位逻辑0-1开关,输出QD、QC、QB、QA接4个LED发光二极管。

接通电源,按表1.3.3输入各逻辑电平(开关开为“1”、关为“0”),观察输出结果并填入表1.3.3中(亮为“1”,灭为“0”)。

(2)将8-3线八进制优先编码器按上述同样方法进行实验论证。

其接线图如图1.3.7所示。

功能表见表1.3.4。

表1.3.3 十进制/BCD码编码器功能表

输入输出

1 2 3 4 5 6 7 8 9 Q D Q C Q B Q A

1 1 1 1

1 1 1 1 1 1 1 1 1

×××××××× 0

××××××× 0 1

×××××× 0 1 1

××××× 0 1 1 1

×××× 0 1 1 1 1

图1.3.6 10-4线编码器实验接线图

×:状态随意

表1.3.4 8/3线优先编码器功能表

图 1.3.7 8-3线编码器实验接线图

×:状态随意

四、实验器材

1.X K 系列数字电子技术实验系统 1台

2.直流稳压电源 1台

3.集成电路:74L S138 2片 74L S 147、74L S 148、74L S 248、74L S 139、74L S 145 各1片

4.显示器LC5011-11 1片

五、预习要求

1.复习译码器、编码器的工作原理和设计方法。

2.熟悉实验中所用译码器、编码器集成电路的管脚排列和逻辑功能。

3.画好实验用逻辑状态表。

六、实验报告要求

1.整理实验线路图和实验数据、表格。

2.总结用集成电路进行各种扩展电路的方法。

3.比较用门电路组成组合电路和应用专门集成电路各有什么优缺点。

× × × 0 1 1 1 1 1

× × 0 1 1 1 1 1 1

× 0 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1

输入

输出 E 1 0 1 2 3 4 5 6 7

Q C Q B Q A E O G S

1 0 0 0 0 0 0 0 0 0 × × × × × × × × 1 1 1 1 1 1 1 1 × × × × × × × 0 × × × × × × 0 1 × × × × × 0 1 1 × × × × 0 1 1 1 × × × 0 1 1 1 1 × × 0 1 1 1 1 1 × 0 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 1 1 1 1。