教你读懂逻辑电路图之编码器和译码器

- 格式:pdf

- 大小:63.15 KB

- 文档页数:2

二、编码器和译码器1.编码器在数字电路中,用二进制代码表示特定含义的信息称为编码,编码器就是将有特定意义的输入数字信号、文字信号等编成相对应的若干位二进制代码形式输出的组合逻辑电路。

(1)普通编码器4线-2线编码器其四个输入0I 到3I 为高电平有效信号,输出是两位二进制代码10Y Y ,任何时刻03~I I 中只能有一个取值为1,并且有一组对应的二进制代码输出。

如果03~I I 中有2个或2个以上的取值同时为1时,输出会出现错误编码。

对于此类问题,可以用优先编码器解决。

(2)优先编码器在优先编码器电路中,允许同时输入两个或两个以上的编码信号。

设计优先编码器时,将所有输入信号按优先顺序排队,在同时存在两个或两个以上输入信号时,优先编码器只按优先级别高的输入信号编码,优先级别低的信号则不起作用。

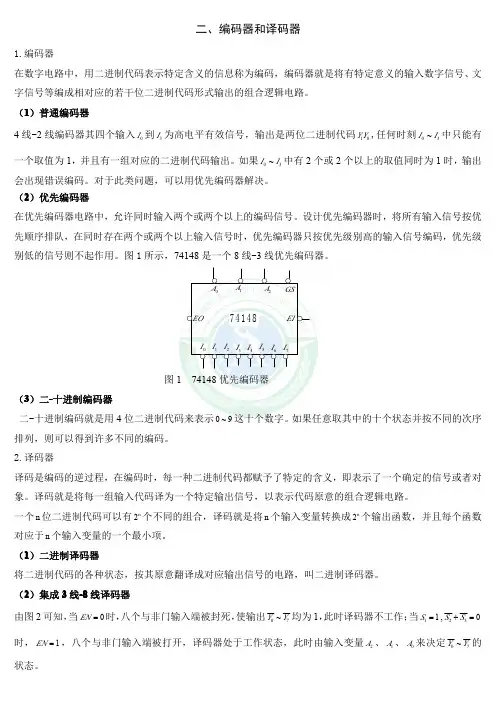

图1所示,74148是一个8线-3线优先编码器。

74148A 1A 2A GSEOEI0I 1I 2I 3I 4I 5I 6I 7I 图174148优先编码器(3)二-十进制编码器二-十进制编码就是用4位二进制代码来表示0~9这十个数字。

如果任意取其中的十个状态并按不同的次序排列,则可以得到许多不同的编码。

2.译码器译码是编码的逆过程,在编码时,每一种二进制代码都赋予了特定的含义,即表示了一个确定的信号或者对象。

译码就是将每一组输入代码译为一个特定输出信号,以表示代码原意的组合逻辑电路。

一个n 位二进制代码可以有n 2个不同的组合,译码就是将n 个输入变量转换成n 2个输出函数,并且每个函数对应于n 个输入变量的一个最小项。

(1)二进制译码器将二进制代码的各种状态,按其原意翻译成对应输出信号的电路,叫二进制译码器。

(2)集成3线-8线译码器由图2可知,当0EN =时,八个与非门输入端被封死,使输出07~Y Y 均为1,此时译码器不工作;当11S =,230S S +=时,1EN =,八个与非门输入端被打开,译码器处于工作状态,此时由输入变量2A 、1A 、0A 来决定07~Y Y 的状态。

编码器和译码器教学目标:1、理解编码器、译码器、显示器的电路结构和工作原理;2、掌握组合逻辑电路的分析方法;教学重点:编码器、译码器、显示器的功能和正确使用教学难点:编码器、译码器的工作原理分析教学过程:一、复习各种进制之间的转换二、新授课基础知识基本组合逻辑电路在实际生产和日常生活中所遇到的逻辑问题无穷无尽,解决这些问题相应的数字电路也不可胜数,但若按电路逻辑功能分类,数字电路可分为组合逻辑电路和时序逻辑电路。

组合逻辑电路在任一时刻的输出仅取决于该时刻电路的输入,而与电路过去的输入状态无关;时序逻辑电路在任一时刻的输出不仅取决于该时刻电路的输入,而且还取决于电路原来的状态,或者说与电路过去的输入及输出也有关系。

本任务涉及的是组合逻辑电路,时序逻辑电路将在后续任务中学习。

组合逻辑电路应用十分广泛,常见的基本组合逻辑电路有编码器、译码器、数据选择器、数据分配器和加法器等。

㈠编码器在二进制运算系统中,每一位二进制数只有0和1两个数码,只能表达两个不同的信号或信息。

如果要用二进制数码表示更多的信号,就必须采用多位二进制数,并按照一定的规律进行编排。

把若干个0和1按一定的规律编排在一起,组成不同的代码,并且赋予每个代码以固定的含意,这就叫做编码。

例如,可以用三位二进制数的八组编码表示十进制数的0~7,把十进制数的0编成二进制数码000,把十进制数的1编成二进制数码001,……,把十进制数7编成二进制数码111。

这样,每组二进制数码都被赋予了十进制数0~7的固定含意。

能完成上述编码功能的逻辑电路称为编码器。

⒈二进制编码器将所需信号编为二进制代码的电路称为二进制编码器。

一位二进制代码可以表示两个信号,两位二进制代码有00、01、10、11四种组合,因而可以表示四个信号。

以此类推,用n位二进制代码,则有2n种数码组合,可以表达2n个不同的信号。

反之,要表示N个信息所需的二进制代码应满足2n N。

图5-20是3位二进制编码器示意图,I0~I7是编码器的8路输入,分别代表十进制数0~7的八个数字(或八个要区分的不同信号);Y0、Y1、Y2是编码器的三个输出。

实验二组合逻辑电路编码器译码器的设计与测试一、实验目的1.掌握编码器的原理和基本结构;2.了解译码器的原理和基本结构;3.掌握编码器和译码器的设计方法;4.通过实验,验证编码器和译码器的功能。

二、实验原理编码器是一种将多个输入信号转换为二进制编码输出的组合逻辑电路。

编码器的输入信号可以是多个,输出信号是二进制编码。

编码器主要用于将多个不同的输入信号通过编码转换为数字输出,使得电路的复杂度得到简化。

译码器就是编码器的逆过程,译码器是一种将二进制编码转换为多个输出信号的组合逻辑电路。

译码器的输入信号是二进制编码,输出信号可以是多个。

编码器和译码器是数字电路中非常重要的组合逻辑电路,广泛应用于计算机、通信、控制等领域。

三、实验内容根据所给的真值表,设计并实现一个2-4线的编码器;设计和实现一个4-2线的译码器;验证实验结果。

四、实验仪器和器件五、实验步骤1.编码器的设计和实现根据所给的真值表,设计并实现一个2-4线的编码器。

首先,根据编码器的输入和输出关系,设计出2-4线的编码器的真值表,并根据真值表进行逻辑设计。

编码器的输入信号有2个,输出信号是4位的二进制编码。

最后,将开关和LED灯连接到逻辑电路上,进行测试和验证。

调试完毕后,记录下测试结果。

2.译码器的设计和实现设计和实现一个4-2线的译码器。

首先,根据译码器的输入和输出关系,设计出4-2线的译码器的真值表,并根据真值表进行逻辑设计。

译码器的输入信号是4位的二进制编码,输出信号有2个。

最后,将开关和LED灯连接到逻辑电路上,进行测试和验证。

调试完毕后,记录下测试结果。

3.验证实验结果通过对编码器和译码器的测试,验证实验结果是否符合设计要求。

当输入信号发生变化时,观察LED灯的亮灭情况,确认编码器和译码器的功能是否正确。

六、实验结果与分析经过实验测试,编码器和译码器的功能正常,符合设计要求。

输入信号的变化能够正确地转换为二进制编码输出;输入二进制编码信号能够正确地转换为输出信号。

编码器和译码器编码器(Encoder)z在数字系统中,常常需要将某一信息(输入)变换为某一特定的代码(输出)z把二进制码按一定的规律编排,例如8421码、格雷码等,使每组代码具有一特定的含义(代表某个数或控制信号)称为编码z具有编码功能的逻辑电路称为编码器z它的逻辑功能是将输入的每一个高、低电平信号编成一个对应的二进制代码。

目前经常使用的编码器有普通编码器和优先编码器两类。

优先编码器(74LS148)功能表译码器(Decoder)z译码是编码的逆过程z译码器将每个二进制代码赋予的特定含义“翻译”过来,转换成相应的信息符号(输出信号)z具有译码功能的逻辑电路被称为译码器z它的逻辑功能是将每个输入的二进制代码译成对应的输出高、低电平信号或另一个代码。

常用的译码器电路有二进制译码器、二–十进制译码器和显示译码器。

3线–8线译码器(74LS138)功能表输出低电平有效4511真值表一、验证编码器74LS148和译码器74LS138的逻辑功能:按上图连接电路,根据74LS148和74LS138的输出状态,填写下表,并分析结果。

二、用两片74LS138扩展为一个4线–16线译码器:按上图连接电路,根据实验结果,填写下表,并分析电路的工作原理。

三、用74LS138和74LS20双与非门设计下面的多输出函数,画出逻辑电路图。

四、一把密码锁有三个按键,分别为A、B、C。

当三个键都不按下时,锁打不开,也不报警;当只有一个键按下时,锁打不开,但发出报警信号;当有两个键同时按下时,锁打开,也不报警;当三个键同时按下时,锁被打开,但要报警。

试使用74LS138和74LS20双与非门实现此逻辑电路。

五、思考题:设计一个5–32的二进制译码器提示:用四片74LS138及一片74LS139(2–4译码器)组成一个树状结构的级联译码器。

用74LS139的输入端做5–32译码器高二位输入端,74LS138的译码输入端做5–32译码器的低三位输入端。

教你读懂逻辑电路图之编码器和译码器

逻辑电路图其实并不难解释,各类图形符号按照逻辑功能进行组合,而组成的电路就是逻辑电路图。

而阅读逻辑电路图也是按照这种思路来进行分解进行的。

在逻辑电路中,将数字和字母转化为二进制代码的电路被称为编码器,本文就将为大家带来如何读懂逻辑电路中的编码器和译码器。

编码器

图1(a)是一个能把十进制数变成二进制码的编码器。

一个十进制数被表示成二进制码必须4位,常用的码是使从低到高的每一位二进制码相当于十进制数的1、2、4、8,这种码称为8-4-2-1码或简称BCD码。

所以这种编码器就称为”10线-4线编码器”或“DEC/BCD编码器”。

从图看到,它是由与非门组成的。

有10个输入端,用按键控制,平时按键悬空相当于接高电平1。

它有4个输出端ABCD,输出8421码。

如果按下“1”键,与“1”键对应的线被接地,等于输入低电平0、于是门D输出为1,整个输出成0001。

图1

如按下“7”键,则B门、C门、D门输出为1,整个输出成0111。

如果把这些电路都做在一个集成片内,便得到集成化的10线4线编码器,它的逻辑符号见图1(b)。

左侧有10个输入端,带小圆圈表示要用低电平,右侧有4个输出端,从上到下按从低到高排列。

使用时可以直接选用。

译码器

要把二进制码还原成十进制数就要用译码器。

它也是由门电路组成的,现。