16学时数字逻辑实验要求及芯片引脚图

- 格式:doc

- 大小:260.50 KB

- 文档页数:5

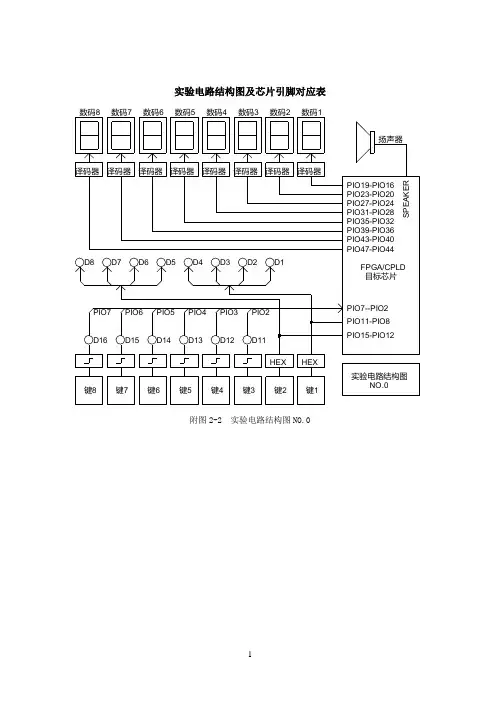

实验电路结构图及芯片引脚对应表NO.0实验电路结构图HEXPIO2PIO3PIO4PIO5PIO7PIO6D1D2D3D4D5D6D7D8D16D15D14D13D12D11数码1数码2数码3数码4数码5数码6数码7数码8S P E A K E R扬声器译码器译码器译码器译码器译码器译码器译码器译码器FPGA/CPLD PIO15-PIO12PIO11-PIO8PIO7--PIO2HEX 键1键2键3键4键5键6键7键8PIO47-PIO44PIO43-PIO40PIO39-PIO36PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16目标芯片附图2-2 实验电路结构图NO.0附图2-3 实验电路结构图NO.1附图2-4 实验电路结构图NO.2ʵÑéµç·½á¹¹Í¼NO.3ÒëÂëÆ÷ÒëÂëÆ÷ÒëÂëÆ÷ÒëÂëÆ÷ÒëÂëÆ÷ÒëÂëÆ÷ÒëÂëÆ÷ÒëÂëÆ÷D9D16D15D14D13D12D11D10D8D7D6D5D4D3D2D1PIO8PIO9PIO10PIO11PIO12PIO13PIO14PIO15S P E A K E RÑïÉùÆ÷12345678Ä¿±êоƬFPGA/CPLD PIO0PIO1PIO2PIO3PIO4PIO5PIO6PIO7¼ü1¼ü2¼ü3¼ü4¼ü5¼ü6¼ü7¼ü8PIO15-PIO8PIO47-PIO44PIO43-PIO40PIO39-PIO36PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16附图2-5 实验电路结构图NO.3附图2-6 实验电路结构图NO.4GNDPIO45PIO46513PS/2接口VCCJ74接PC 机串行通讯接口接口电路单片机接口电路235RS-232B412MHZA键复位P34P33P32X1X2P31P30P35RST GND12345678910VCCPIO11PIO12PIO13PIO14AT89C2051EU3P37P10P11P12P13P14P15P16P17VCC 11121314151617181920PIO15PIO24PIO25PIO26PIO27PIO28PIO29PIO30PIO317.2K P29->A14)27512(PIN30->VCC,PIN3->A15,PIN29->WE)628128(PIN30->VCC,PIN3->A14,RAM/ROMP29->WE)62256(PIN30->VCC,PIN3->A14,6264(PIN30->VCC,PIN29->WR)PIN30->A17,PIN3->A15,PIN29->A14)29C040(PIN31->WE,PIN1->A18,PIN3->A15,PIN29->A14)27040(PIN31->A18,PIN30->A17,PIN29->A14)27020(PIN30->A17,PIN3->A15,P29->A14)27010(PIN30->VCC,PIN3->A15,PIO40PIO41PIO42PIO43PIO44R78 200R77 200R76 20010548761413321 视频接口VGA J6A18/A19A18/A15/WE PIO49VCC SLA17RAM_ENVCC GND SLRAMPIO26PIO25PIO24PIO32PIO33PIO34PIO35PIO36PIO37PIO38PIO39PIO14PIO47PIO10PIO48PIO9PIO46PIO45PIO11PIO12PIO13PIO8PIO15PIO31PIO30PIO29PIO28PIO273231302928272625242322212019181716151413121110987654321VCC GND2708027040270202701027512272562764628128622566264VCC A17/VCC WR/A14A13A8A9A11OE A10CS1D7D6D5D4D3GND D2D1D0A0A1A2A3A4A5A6A7A12A14(A15)A1610K VCCVR1PIO31PIO29PIO30PIO28PIO27PIO26PIO25PIO24131415164D7D6D5D4D35D26D1D07PIO37+5JP251pFC27JP2(COMP)COMP LM311VCC10K -12+124823TL082/1AIN0AOUT1021035.1KR72765TL082/2841+12-12滤波0滤波1FITCOMMEU2DAC0832118171032WR1FB93211IOUT1IOUT212/CS WR2XFER A GND D GNDVREF8VCC 20VCCJP2(1/2,3/4)D1PIO8D2D3D4D5D6D7D8PIO9PIO10PIO11PIO12PIO15PIO14PIO13实验电路结构图NO.5S P E A K E R扬声器FPGA/CPLD 目标芯片12345678D16D15D14D13D12D11D10D9PIO47-PIO44PIO43-PIO40PIO39-PIO36PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16译码器译码器译码器译码器译码器译码器译码器译码器PIO15-PIO8PIO0PIO1PIO2PIO3PIO4PIO5PIO6PIO7键1键2键3键4键5键6键7键8P I O 8J P 2(5/6)P I O 8(23)(24)1216272610C L O C K 750K H Z A F I T102C 30103C 29P I O 37P I O 35C O M MC O M PA D E O C A D E NJ P 22018161412108642191715131197531021+5V A I N 0A I N 1r e f (-)r e f (+)I N -1I N -06922257171415818192021E U 1A D C 0809P I O 16P I O 17P I O 18P I O 19P I O 20P I O 21P I O 22P I O 23P I O 32P I O 33P I O 35P I O 34m s b 2-12-22-32-42-52-62-7l s b 2-8E O C A D D -A A D D -B A D D -C A L E E N A B L E S T A R T附图2-7 实验电路结构图NO.5附图2-8 实验电路结构图NO.6D16D15D14D13D12D11D9D8PIO47D7PIO46D6PIO45D5PIO44D4PIO43D3PIO42D2PIO41PIO40D1NO.7实验电路结构图S P E A K E R扬声器FPGA/CPLD 目标芯片12345678PIO0PIO2PIO3PIO4PIO5PIO6PIO7单脉冲单脉冲单脉冲键1键2键3键4键5键6键7键8PIO47-PIO40PIO39-PIO36PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16译码器译码器译码器译码器译码器译码器附图2-9 实验电路结构图NO.7附图2-10 实验电路结构图NO.8附图2-11 实验电路结构图NO.9附图2-12 实验电路结构图NO.BD22D21D20D19D18D17VCC87654321SDA (PIO79)SCL (PIO78)24C01GNDVCCPIO77PIO766PS/254321GNDVCCD-(PIO76)D+(PIO77)SLAVEUSB GND键12键11键9键1010K X 4PIO75PIO74PIO72PIO73VCCP I O 71P I O 76P I O 77P I O 70P I O 69P I O 68数码14数码13数码12数码11数码10数码9PIO67PIO66PIO65PIO64PIO63PIO62PIO61PIO60hg f e d c b a 888888附图2-13 实验电路结构图COM万能接插口与结构图信号/与芯片引脚对照表附录二:《EDA技术》部分实验参考源程序一、8位硬件加法器设计程序如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY ADDER8 ISPORT ( CIN : IN STD_LOGIC;A, B : IN STD_LOGIC_VECTOR(7 DOWNTO 0);S : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);COUT : OUT STD_LOGIC );END ADDER8;ARCHITECTURE behav OF ADDER8 ISSIGNAL SINT : STD_LOGIC_VECTOR(8 DOWNTO 0);BEGINSINT <= ('0'& A) + B + CIN ;S <= SINT(7 DOWNTO 0); COUT <= SINT(8);END behav;选择实验电路NO.1验证此加法器的功能。

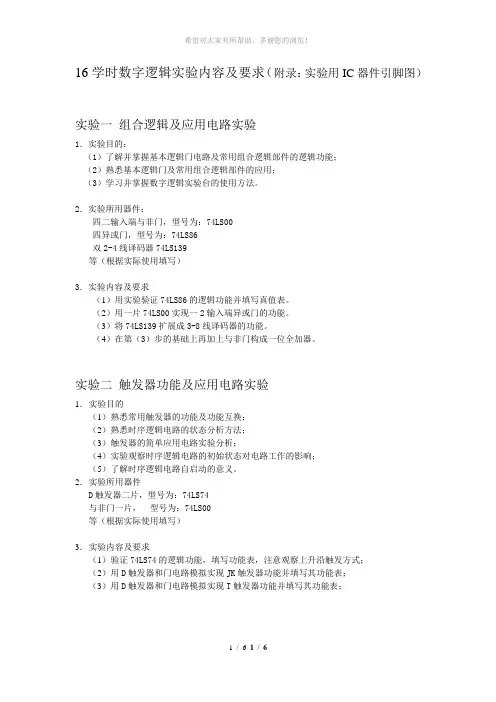

16学时数字逻辑实验内容及要求(附录:实验用IC器件引脚图)实验一组合逻辑及应用电路实验1.实验目的:(1)了解并掌握基本逻辑门电路及常用组合逻辑部件的逻辑功能;(2)熟悉基本逻辑门及常用组合逻辑部件的应用;(3)学习并掌握数字逻辑实验台的使用方法。

2.实验所用器件:四二输入端与非门,型号为:74LS00四异或门,型号为:74LS86双2-4线译码器74LS139等(根据实际使用填写)3.实验内容及要求(1)用实验验证74LS86的逻辑功能并填写真值表。

(2)用一片74LS00实现一2输入端异或门的功能。

(3)将74LS139扩展成3-8线译码器的功能。

(4)在第(3)步的基础上再加上与非门构成一位全加器。

实验二触发器功能及应用电路实验1.实验目的(1)熟悉常用触发器的功能及功能互换;(2)熟悉时序逻辑电路的状态分析方法;(3)触发器的简单应用电路实验分析;(4)实验观察时序逻辑电路的初始状态对电路工作的影响;(5)了解时序逻辑电路自启动的意义。

2.实验所用器件D触发器二片,型号为:74LS74与非门一片,型号为:74LS00等(根据实际使用填写)3.实验内容及要求(1)验证74LS74的逻辑功能,填写功能表,注意观察上升沿触发方式;(2)用D触发器和门电路模拟实现JK触发器功能并填写其功能表;(3)用D触发器和门电路模拟实现T触发器功能并填写其功能表;由D触发器及门电路构成有用的四位环型计数器,实验观察并记录电路运行状态。

实验三时序电路功能组件及应用电路实验1.实验目的(1)熟悉中规模集成移位寄存器74LS194的逻辑功能及简单应用;(2)熟悉中规模集成计数器74LS161功能及简单应用;(3)学会使用七段字形译码器及共阴极七段LED数字显示器。

2.实验所用器件四位二进制加法计数器1片,型号为:74LS161寄存器1片,型号为:74LS194等(根据实际使用填写)3.实验内容及要求(1)验证寄存器(74LS194)、计数器(74LS161)的逻辑功能,通过实验填写功能表;(2)用74LS161及门电路分别采用复位法和置数法构成一位8421BCD码计数显示电路;(3)用74LS194及门电路构成有用的四位环型计数器。

淮北师范大学计算机学院School of Computer Science & Technology,HuaiBei Normal University计算机学院编写实验注意事项1、电源的打开顺序是:先开交流开关(实验箱中的船形开关),再开直流开关,最后打开各个模块的控制开关。

电源关掉的顺序刚好与此相反。

2、切忌在实验中带电连接线路,正确的方法是断电后再连线,进行实验。

3、实验箱主电路板上所有的芯片出厂时已全部经过严格检验,因此在做实验时切忌随意插拔芯片。

4、实验箱中的叠插连接线的使用方法为:连线插入时要垂直,插入后稍做旋转,切忌用力,拔出时用手捏住连线靠近插孔的一端,然后左右旋转几下,连线自然会从插孔中松开、弹出,切忌用力向上拉线,这样很容易造成连线和插孔的损坏。

5、实验中应该严格按照老师的要求和实验指导书来操作,不要随意乱动开关,芯片及其它元器件,以免造成实验箱的损坏。

6、如果在实验中由于操作不当或其它原因而出现异常情况,如数码管显示不稳定、闪烁,芯片发烫等,首先立即断电,然后报告老师,切忌无视现象,继续实验,以免造成严重后果。

7、实验中所用的元件都需要自行配置,元件名称都在实验设备与器件中写出,在实验中不同公司和国家的同种功能的元件可替换,比如CD系列的与CC系的同各功能的集成芯片可替换。

8、注意保持卫生,下课后将桌面附近的垃圾全部带走,并有打扫实验室的义务。

目录实验一数字电路仪器的使用及门电路 (1)实验二加法器实验 (2)实验三数据选择器及其应用 (3)实验四组合电路的设计与测试 (5)实验五触发器及其应用 (7)实验六移位寄存器及其应用 (10)实验七异步时序电路实验 (13)实验八综合设计实验 (14)数字逻辑与数字电路实验项目实验一数字电路仪器的使用及门电路一、实验目的1、数字电路仪器的各功能模块见实验箱使用说明。

2、测试TTL集成芯片中的与门、或门、非门、与非门、或非门与异或门的逻辑功能。

数字电路实验芯片引脚图数字电路实验一、芯片引脚图真值表:二、组合逻辑电路实验设计题1.举重比赛有3个裁判,一个主裁判A和两个辅裁判B和C,杠铃完全举上的裁决由每个裁判按下自己的按键来决定。

当3个裁判判为成功或两个裁判(其中一个为主裁判)判为成功则成功绿色指示灯亮,否则红色指示灯亮。

试用74LS151设计此逻辑电路。

2.设输入数据为4位二进制数,当该数据能被3整除时绿色指示灯亮,否则红色指示灯亮。

试用74LS151设计此逻辑电路。

3.设输入数据为4位二进制数,当该数据能被5整除时绿色指示灯亮,否则红色指示灯亮。

试用74LS151设计此逻辑电路。

4.试设计一个四人表决器,当四个人中有3个人或4个人赞成时绿灯亮表示建议被通过,否则红灯亮表示建议被否决。

试用74LS151设计此逻辑电路。

5.设输入数据为4位二进制数,设计由此二进制数决定的偶校验逻辑电路,即当此二进制数中有偶数个1时绿色指示灯亮,否则红色指示灯亮。

试用74LS151设计此逻辑电路。

6.某楼道内住着A、B、C、D 四户人家,楼道顶上有一盏路灯。

请设计一个控制电路,要求A、B、C、D 都能在自己的家中独立地控制这盏路灯。

试用74LS151设计此逻辑电路。

7.用74LS151实现一个函数发生器,其功能是:当S1S0=00时,Y=AB;当S1S0=01时,Y=A+B;当S1S0=10时,Y=A B;当S1S0=11时,Y=。

试用74LS151设计此逻辑电路。

8.试用两片74LS151实现16选1数据选择器。

三、时序逻辑电路实验设计题1.用十进制计数-译码器CC4017设计一个8盏灯的流水灯电路。

2.用74LS161设计一个12进制的加1计数器。

其代码转换图为:0000→0001→0010→…→1011循环。

每循环一次产生一个进位脉冲。

3.用74LS161设计一个12进制的加1计数器。

其代码转换图为:0100→0101→0110→…→1111循环。

课程名称:数字逻辑电路实验指导书课时:8学时集成电路芯片一、简介数字电路实验中所用到的集成芯片都是双列直插式的,其引脚排列规则如图1-1所示。

识别方法是:正对集成电路型号<如74LS20)或看标记<左边的缺口或小圆点标记),从左下角开始按逆时针方向以1,2,3,…依次排列到最后一脚<在左上角)。

在标准形TTL集成电路中,电源端V一般排在左上CC,7脚为端,接地端GND一般排在右下端。

如74LS20为14脚芯片,14脚为VCCGND。

若集成芯片引脚上的功能标号为NC,则表示该引脚为空脚,与内部电路不连接。

二、TTL集成电路使用规则1、接插集成块时,要认清定位标记,不得插反。

2、电源电压使用范围为+4.5V~+5.5V之间,实验中要求使用Vcc=+5V。

电源极性绝对不允许接错。

3、闲置输入端处理方法(1> 悬空,相当于正逻辑“1”,对于一般小规模集成电路的数据输入端,实验时允许悬空处理。

但易受外界干扰,导致电路的逻辑功能不正常。

因此,对于接有长线的输入端,中规模以上的集成电路和使用集成电路较多的复杂电路,所有控制输入端必须按逻辑要求接入电路,不允许悬空。

<也可以串入一只1~10KΩ的固定电阻)或接至某一 (2> 直接接电源电压VCC固定电压(+2.4≤V≤4.5V>的电源上,或与输入端为接地的多余与非门的输出端相接。

(3> 若前级驱动能力允许,可以与使用的输入端并联。

4、输入端通过电阻接地,电阻值的大小将直接影响电路所处的状态。

当R ≤680Ω时,输入端相当于逻辑“0”;当R≥4.7 KΩ时,输入端相当于逻辑“1”。

对于不同系列的器件,要求的阻值不同。

5、输出端不允许并联使用<集电极开路门(OC>和三态输出门电路(3S>除外)。

否则不仅会使电路逻辑功能混乱,并会导致器件损坏。

6、输出端不允许直接接地或直接接+5V电源,否则将损坏器件,有时为,一般取R 了使后级电路获得较高的输出电平,允许输出端通过电阻R接至Vcc=3~5.1 KΩ。

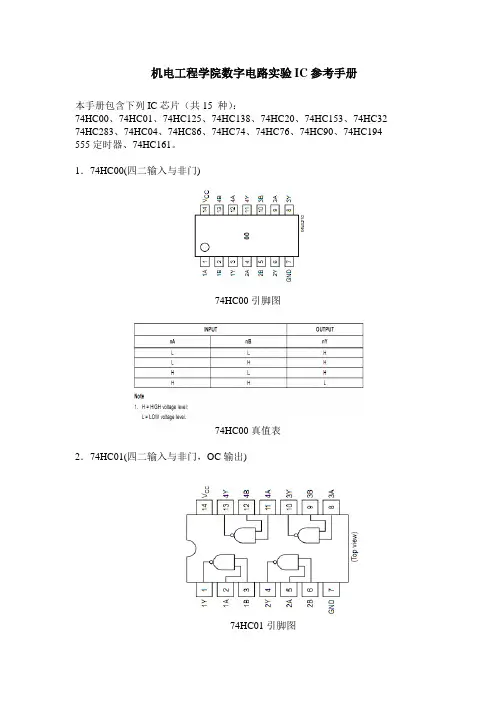

机电工程学院数字电路实验IC参考手册本手册包含下列IC芯片(共15 种):74HC00、74HC01、74HC125、74HC138、74HC20、74HC153、74HC32 74HC283、74HC04、74HC86、74HC74、74HC76、74HC90、74HC194 555定时器、74HC161。

1.74HC00(四二输入与非门)74HC00引脚图74HC00真值表2.74HC01(四二输入与非门,OC输出)74HC01引脚图74HC01真值表3.74HC125(四三态门)74HC125引脚图74HC125真值表4.74HC138(3-8译码器)74HC138引脚图74HC138真值表5.74HC20(双4输入与非门)74HC20引脚图74HC20真值表6.74HC153(双四选一数据选择器)74HC153引脚图74HC153真值表7.74HC32(四2输入端或门)74HC32引脚图74HC32真值表8.74HC283(4位二进制全加器)74HC283引脚图74HC283真值表9.74HC04(六位反相器)74HC04引脚图74HC04真值表10.74HC86(四2输入端异或门)74HC86引脚图74HC86真值表11.74HC74(双上升沿D型触发器)74HC74引脚图74HC74真值表12.74HC76(双j-k触发器)74HC76引脚图74HC76真值表13.74HC90(二/五分频十进制计数器)74HC90引脚图74HC90真值表14.74HC194(4位并入/串入-并出/串出移位寄存)74HC194引脚图74HC194真值表15.555定时器555引脚图16.74ls4717. 74hc161。

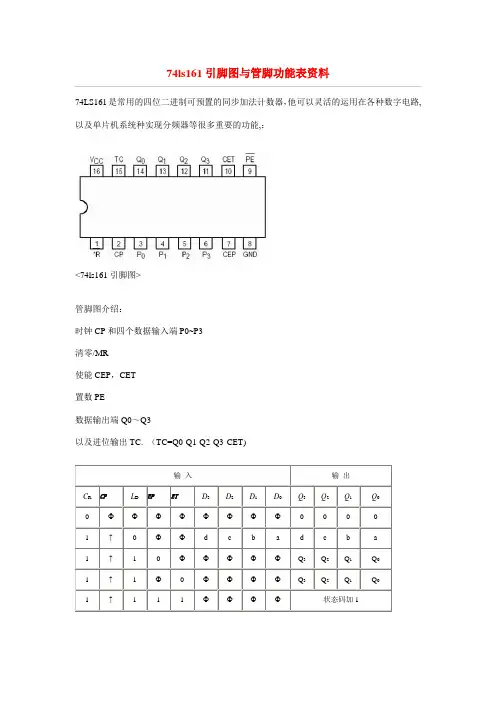

74ls161引脚图与管脚功能表资料74LS161是常用的四位二进制可预置的同步加法计数器,他可以灵活的运用在各种数字电路,以及单片机系统种实现分频器等很多重要的功能,:<74ls161引脚图>管脚图介绍:时钟CP和四个数据输入端P0~P3清零/MR使能CEP,CET置数PE数据输出端Q0~Q3以及进位输出TC. (TC=Q0·Q1·Q2·Q3·CET)输入输出C R CP LD EP ET D3D2D1D0Q3 Q2Q1Q00 Ф Ф Ф Ф Ф Ф Ф Ф 0 0 0 01 ↑ 0 Ф Ф d c b a d c b a1 ↑ 1 0 Ф Ф Ф Ф Ф Q3 Q2Q1Q01 ↑ 1 Ф 0 Ф Ф Ф Ф Q3 Q2Q1Q01 ↑ 1 1 1 Ф Ф Ф Ф 状态码加1<74LS161功能表〉从74LS161功能表功能表中可以知道,当清零端CR=“0",计数器输出Q3、Q2、Q1、Q0立即为全“0",这个时候为异步复位功能。

当CR=“1”且LD=“0”时,在CP信号上升沿作用后,74LS161输出端Q3、Q2、Q1、Q0的状态分别与并行数据输入端D3,D2,D1,D0的状态一样,为同步置数功能。

而只有当CR=LD=EP=ET=“1"、CP脉冲上升沿作用后,计数器加1。

74LS161还有一个进位输出端CO,其逻辑关系是CO= Q0·Q1·Q2·Q3·CET。

合理应用计数器的清零功能和置数功能,一片74LS161可以组成16进制以下的任意进制分频器。

16学时数字逻辑实验内容及要求(附录:实验用IC器件引脚图)

实验一组合逻辑及应用电路实验

1.实验目的:

(1)了解并掌握基本逻辑门电路及常用组合逻辑部件的逻辑功能;

(2)熟悉基本逻辑门及常用组合逻辑部件的应用;

(3)学习并掌握数字逻辑实验台的使用方法。

2.实验所用器件:

四二输入端与非门,型号为:74LS00

四异或门,型号为:74LS86

双2-4线译码器74LS139

等(根据实际使用填写)

3.实验内容及要求

(1)用实验验证74LS86的逻辑功能并填写真值表。

(2)用一片74LS00实现一2输入端异或门的功能。

(3)将74LS139扩展成3-8线译码器的功能。

(4)在第(3)步的基础上再加上与非门构成一位全加器。

实验二触发器功能及应用电路实验

1.实验目的

(1)熟悉常用触发器的功能及功能互换;

(2)熟悉时序逻辑电路的状态分析方法;

(3)触发器的简单应用电路实验分析;

(4)实验观察时序逻辑电路的初始状态对电路工作的影响;

(5)了解时序逻辑电路自启动的意义。

2.实验所用器件

D触发器二片,型号为:74LS74

与非门一片,型号为:74LS00

等(根据实际使用填写)

3.实验内容及要求

(1)验证74LS74的逻辑功能,填写功能表,注意观察上升沿触发方式;

(2)用D触发器和门电路模拟实现JK触发器功能并填写其功能表;

(3)用D触发器和门电路模拟实现T触发器功能并填写其功能表;

(4)由D触发器及门电路构成有用的四位环型计数器,实验观察并记录电路运行状态。

实验三时序电路功能组件及应用电路实验

1.实验目的

(1)熟悉中规模集成移位寄存器74LS194的逻辑功能及简单应用;

(2)熟悉中规模集成计数器74LS161功能及简单应用;

(3)学会使用七段字形译码器及共阴极七段LED数字显示器。

2.实验所用器件

四位二进制加法计数器1片,型号为:74LS161

寄存器1片,型号为:74LS194

等(根据实际使用填写)

3.实验内容及要求

(1)验证寄存器(74LS194)、计数器(74LS161)的逻辑功能,通过实验填写功能表;(2)用74LS161及门电路分别采用复位法和置数法构成一位8421BCD码计数显示电路;(3)用74LS194及门电路构成有用的四位环型计数器。

实验四串行加法器的设计

1.实验目的

较复杂数字逻辑电路的设计方法及实验分析。

2.实验所用器件

4位移位寄存器组件2片,型号为:74LS194

D触发器1片,型号为:74LS74

等(根据实际使用填写)

3.实验内容及要求

(1)按如下串行加法器框图设计电路图实现四位二进制的加法;

4位被加数移位寄存器

为了清楚地看到逐位相加情况,时钟脉冲应采用单脉冲,注意电路清“0”作用。

(2)任意给定X,Y,给电路加入4个单脉冲,逐一观察并记录电路工作情况;

(3)4个脉冲后,X+Y的和存放在A中,X+Y的最高位即进位存放在何处。

串行加法器的加法速度如何计算。

附录:实验用IC器件引脚图74LS00

74LS10

74LS20

74LS86

74LS139

74LS194。