基于Libero的数字逻辑设计仿真和验证实验报告(实验1)

- 格式:docx

- 大小:21.86 KB

- 文档页数:10

一、实验目的1. 理解和掌握数字逻辑设计的基本原理和方法。

2. 熟悉数字电路的基本门电路和组合逻辑电路。

3. 培养动手能力和实验技能,提高逻辑思维和解决问题的能力。

4. 熟悉数字电路实验设备和仪器。

二、实验原理数字逻辑设计是计算机科学与技术、电子工程等领域的基础课程。

本实验旨在通过实际操作,让学生掌握数字逻辑设计的基本原理和方法,熟悉数字电路的基本门电路和组合逻辑电路。

数字逻辑电路主要由逻辑门组成,逻辑门是数字电路的基本单元。

常见的逻辑门有与门、或门、非门、异或门等。

根据逻辑门的功能,可以将数字电路分为组合逻辑电路和时序逻辑电路。

组合逻辑电路的输出只与当前输入有关,而时序逻辑电路的输出不仅与当前输入有关,还与之前的输入有关。

三、实验内容1. 逻辑门实验(1)实验目的:熟悉逻辑门的功能和特性,掌握逻辑门的测试方法。

(2)实验步骤:① 将实验箱中的逻辑门连接到测试板上。

② 根据实验要求,将输入端分别连接高电平(+5V)和低电平(0V)。

③ 观察输出端的变化,记录实验数据。

④ 分析实验结果,验证逻辑门的功能。

2. 组合逻辑电路实验(1)实验目的:掌握组合逻辑电路的设计方法,熟悉常用组合逻辑电路。

(2)实验步骤:① 根据实验要求,设计组合逻辑电路。

② 将电路连接到实验箱中。

③ 根据输入端的不同组合,观察输出端的变化,记录实验数据。

④ 分析实验结果,验证电路的功能。

3. 时序逻辑电路实验(1)实验目的:掌握时序逻辑电路的设计方法,熟悉常用时序逻辑电路。

(2)实验步骤:① 根据实验要求,设计时序逻辑电路。

② 将电路连接到实验箱中。

③ 观察电路的输出变化,记录实验数据。

④ 分析实验结果,验证电路的功能。

四、实验结果与分析1. 逻辑门实验结果:通过实验,验证了逻辑门的功能和特性,掌握了逻辑门的测试方法。

2. 组合逻辑电路实验结果:通过实验,掌握了组合逻辑电路的设计方法,熟悉了常用组合逻辑电路。

3. 时序逻辑电路实验结果:通过实验,掌握了时序逻辑电路的设计方法,熟悉了常用时序逻辑电路。

数字电路仿真 实验报告一、实验目的(1)学会组合逻辑电路的特点;(2)利用逻辑转换仪对组合逻辑电路进行分析与设计。

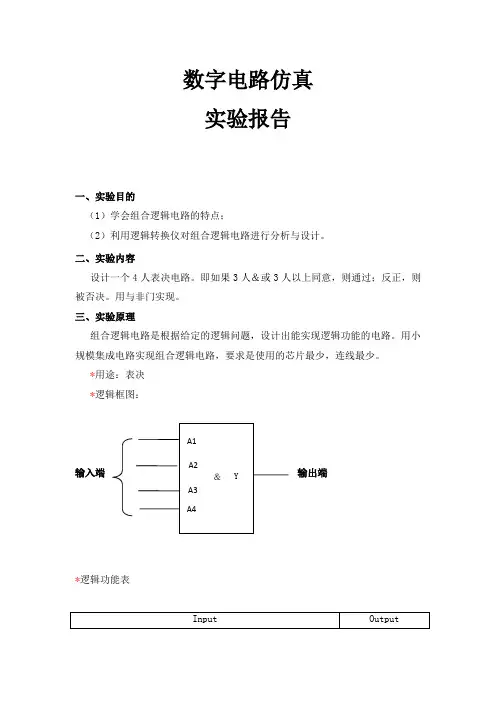

二、实验内容设计一个4人表决电路。

即如果3人&或3人以上同意,则通过;反正,则被否决。

用与非门实现。

三、实验原理组合逻辑电路是根据给定的逻辑问题,设计出能实现逻辑功能的电路。

用小规模集成电路实现组合逻辑电路,要求是使用的芯片最少,连线最少。

*用途:表决 *逻辑框图: 输入端 输出端*逻辑功能表InputOutputA1A2A3 A4 & YA1 A2 A3 A4Sum 1000 (任意顺序,只在乎最后结果) >30 1100(任意顺序,只在乎最后结果) 1110(任意顺序,只在乎最后结果) >=311111(任意顺序,只在乎最后结果)电平的个数之和,其和小于3则输出0,表决不成功,其和大于或者等于3则输出1,表决成功。

*逻辑框图:*逻辑功能表inputs and sum output A1 sum A2 sum A3 sumA4 sum 1112 1314 1输入端0 3 10 2 1 3 1 0 2 00 1 1 21 3 10 2 00 11 2 00 1 00 0 1 11 21 3 10 2 00 11 2 00 1 00 01 11 2 00 1 00 01 1 00 0 0输入的数据依次相加,若最后和的结果大于等于3则输出1,否则输出0四、实验步棸1、编写源代码。

(1)打开QuartusⅡ软件平台,点击File中得New Project新建工程,将工程名称建得跟文件夹名称一样为ren。

在File 中New建立一个VHDL文件。

VHDL语言设计如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY ren ISPORT (A1,A2,A3,A4:IN STD_LOGIC;Y:OUT STD_LOGIC);END;ARCHITECTURE bhv OF ren ISBEGINPROCESS(A1,A2,A3,A4)VARIABLE SUM:INTEGER RANGE 0 TO 4;BEGINSUM:=0;IF A1='1'THEN SUM:=SUM+1;END IF;IF A2='1'THEN SUM:=SUM+1;END IF;IF A3='1'THEN SUM:=SUM+1;END IF;IF A4='1'THEN SUM:=SUM+1;END IF;IF SUM>=3 THEN Y<='1';ELSE Y<='0';END IF;END PROCESS;END;(2)点击File/Save as以“.vhd”为扩展名存盘文件,命名为“ren.vhd”,保存时勾选“Add file to current file”选项。

数字逻辑实验报告(1)姓名:学号:班级:CS指导教师:计算机科学与技术学院2018年5 月22 日数字逻辑实验报告系列二进制加法器设计预习报告一、系列二进制加法器设计1、实验名称系列二进制加法器设计。

2、实验目的要求同学采用传统电路的设计方法,对5种二进制加法器进行设计,并利用工具软件,例如,“logisim”软件的虚拟仿真功能来检查电路设计是否达到要求。

通过以上实验的设计、仿真、验证3个训练过程使同学们掌握传统逻辑电路的设计、仿真、调试的方法。

3、实验所用设备Logisim2.7.1软件一套。

4、实验内容对已设计的5种二进制加法器,使用logisim软件对它们进行虚拟实验仿真,除逻辑门、触发器外,不能直接使用logisim软件提供的逻辑库元件,具体内容如下。

(1)一位二进制半加器设计一个一位二进制半加器,电路有两个输入A、B,两个输出S和C。

输入A、B分别为被加数、加数,输出S、C为本位和、向高位进位。

(2)一位二进制全加器设计一个一位二进制全加器,电路有三个输入A、B和Ci ,两个输出S和Co。

输入A、B和Ci 分别为被加数、加数和来自低位的进位,输出S和Co为本位和和向高位的进位。

(3)串行进位的四位二进制并行加法器用四个一位二进制全加器串联设计一个串行进位的四位二进制并行加法器,电路有九个输入A3、A2、A1、A、B3、B2、B1、B和C,五个输出S3、S2、S1、S和C 4。

输入A= A3A2A1A、B= B3B2B1B和C分别为被加数、加数和来自低位的进位,输出S= S3S2S1S和Co为本位和和向高位的进位。

(4)先行进位的四位二进制并行加法器利用超前进位的思想设计一个先行进位的四位二进制并行加法器,电路有九个输入A3、A2、A1、A、B3、B2、B1、B和C,五个输出S3、S2、S1、S和C4。

输入A= A3A2A1A、B= B3B2B1B和C分别为被加数、加数和来自低位的进位,输出S= S3S2S1S和Co为本位和和向高位的进位。

数字逻辑实验报告数字逻辑实验报告引言:数字逻辑是计算机科学中的基础知识,它研究的是数字信号的处理与传输。

在现代科技发展的背景下,数字逻辑的应用越来越广泛,涉及到计算机硬件、通信、电子设备等众多领域。

本实验旨在通过设计和实现数字逻辑电路,加深对数字逻辑的理解,并掌握数字逻辑实验的基本方法和技巧。

实验一:逻辑门电路设计与实现逻辑门是数字电路的基本组成单元,由与门、或门、非门等构成。

在本实验中,我们设计了一个4位全加器电路。

通过逻辑门的组合,实现了对两个4位二进制数的加法运算。

实验过程中,我们了解到逻辑门的工作原理,掌握了逻辑门的真值表和逻辑方程的编写方法。

实验二:多路选择器的设计与实现多路选择器是一种常用的数字逻辑电路,它可以根据控制信号的不同,从多个输入信号中选择一个输出信号。

在本实验中,我们设计了一个4位2选1多路选择器电路。

通过对多路选择器的输入信号和控制信号的设置,实现了对不同输入信号的选择。

实验过程中,我们了解到多路选择器的工作原理,学会了多路选择器的真值表和逻辑方程的编写方法。

实验三:时序逻辑电路的设计与实现时序逻辑电路是一种能够存储和处理时序信息的数字逻辑电路。

在本实验中,我们设计了一个简单的时序逻辑电路——D触发器。

通过对D触发器的输入信号和时钟信号的设置,实现了对输入信号的存储和传输。

实验过程中,我们了解到D触发器的工作原理,掌握了D触发器的真值表和逻辑方程的编写方法。

实验四:计数器电路的设计与实现计数器是一种能够实现计数功能的数字逻辑电路。

在本实验中,我们设计了一个4位二进制计数器电路。

通过对计数器的时钟信号和复位信号的设置,实现了对计数器的控制。

实验过程中,我们了解到计数器的工作原理,学会了计数器的真值表和逻辑方程的编写方法。

结论:通过本次实验,我们深入了解了数字逻辑的基本原理和应用方法。

通过设计和实现逻辑门电路、多路选择器、时序逻辑电路和计数器电路,我们掌握了数字逻辑实验的基本技巧,并加深了对数字逻辑的理解。

一、实习目的本次数字逻辑实习的主要目的是通过实际操作和理论学习,加深对数字逻辑电路基本原理的理解,掌握数字逻辑电路的设计、分析和仿真方法,提高解决实际问题的能力。

二、实习内容1. 数字逻辑电路基本原理的学习在实习过程中,我们首先学习了数字逻辑电路的基本原理,包括逻辑门、触发器、计数器、寄存器等基本逻辑元件及其组合逻辑和时序逻辑电路的设计方法。

2. 逻辑门电路的设计与仿真通过Logisim软件,我们设计并仿真了各种逻辑门电路,如与门、或门、非门、异或门等。

通过实验,我们验证了所设计的逻辑门电路的正确性。

3. 触发器电路的设计与仿真我们学习了D触发器、JK触发器、T触发器等基本触发器电路的设计方法,并利用Logisim软件进行仿真,验证了所设计的触发器电路的功能。

4. 计数器电路的设计与仿真我们学习了同步计数器、异步计数器等计数器电路的设计方法,并利用Logisim软件进行仿真,验证了所设计的计数器电路的正确性。

5. 寄存器电路的设计与仿真我们学习了移位寄存器、同步寄存器等寄存器电路的设计方法,并利用Logisim软件进行仿真,验证了所设计的寄存器电路的功能。

三、实习过程1. 实验准备在实习开始前,我们查阅了相关资料,了解了数字逻辑电路的基本原理和设计方法。

同时,我们预习了实验指导书,明确了实验目的、内容和步骤。

2. 实验操作在实验过程中,我们按照实验指导书的要求,利用Logisim软件设计并仿真了各种数字逻辑电路。

在实验过程中,我们遇到了一些问题,通过查阅资料、请教老师等方式解决了这些问题。

3. 结果分析通过对所设计的数字逻辑电路进行仿真,我们验证了电路的正确性。

同时,我们分析了电路的性能,如速度、功耗等。

四、实习收获1. 提高了数字逻辑电路设计能力通过本次实习,我们掌握了数字逻辑电路的设计方法,提高了数字逻辑电路的设计能力。

2. 增强了实践操作能力在实习过程中,我们学会了使用Logisim软件进行数字逻辑电路的仿真,提高了实践操作能力。

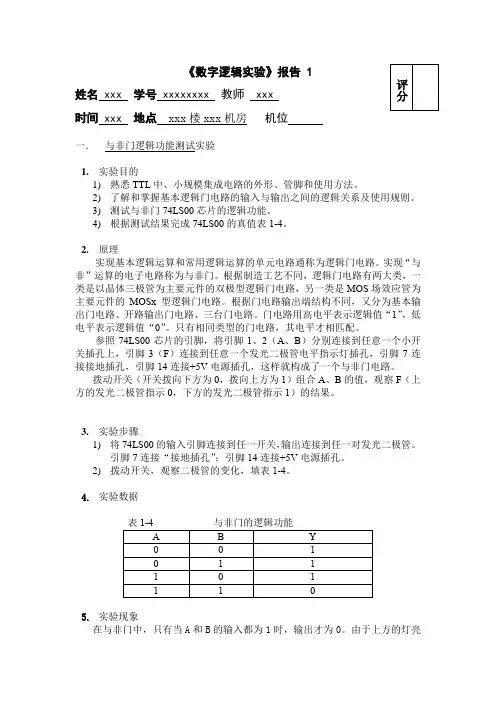

姓名 xxx 学号 xxxxxxxx 教师 xxx时间 xxx 地点xxx楼xxx机房机位一.与非门逻辑功能测试实验1.实验目的1)熟悉TTL中、小规模集成电路的外形、管脚和使用方法。

2)了解和掌握基本逻辑门电路的输入与输出之间的逻辑关系及使用规则。

3)测试与非门74LS00芯片的逻辑功能。

4)根据测试结果完成74LS00的真值表1-4。

2.原理实现基本逻辑运算和常用逻辑运算的单元电路通称为逻辑门电路。

实现“与非”运算的电子电路称为与非门。

根据制造工艺不同,逻辑门电路有两大类,一类是以晶体三极管为主要元件的双极型逻辑门电路,另一类是MOS场效应管为主要元件的MOSx型逻辑门电路。

根据门电路输出端结构不同,又分为基本输出门电路、开路输出门电路、三台门电路。

门电路用高电平表示逻辑值“1”,低电平表示逻辑值“0”。

只有相同类型的门电路,其电平才相匹配。

参照74LS00芯片的引脚,将引脚1、2(A、B)分别连接到任意一个小开关插孔上,引脚3(F)连接到任意一个发光二极管电平指示灯插孔,引脚7连接接地插孔,引脚14连接+5V电源插孔,这样就构成了一个与非门电路。

拨动开关(开关拨向下方为0,拨向上方为1)组合A、B的值,观察F(上方的发光二极管指示0,下方的发光二极管指示1)的结果。

3.实验步骤1)将74LS00的输入引脚连接到任一开关,输出连接到任一对发光二极管。

引脚7连接“接地插孔”;引脚14连接+5V电源插孔。

2)拨动开关,观察二极管的变化,填表1-4。

4.实验数据5.实验现象在与非门中,只有当A和B的输入都为1时,输出才为0。

由于上方的灯亮说明输出为0,下方的灯亮说明是1,所以只有在A和B的输入都为1时(即开关打在上方时),上方的等才会亮,其余时候都是下方的灯亮。

6.体会通过学习、操作与非门逻辑功能测试实验,我初步体会到了数字逻辑电路的基本连接和测试方法,对测试了与非门的逻辑功能,且此元件工作正常。

_计算机__学院网络工程专业 2 班________组、学号3110006512 姓名杨远军协作者______________ 教师评定_________________ 实验题目___________基于Libero的数字逻辑设计仿真实验_____________1.基本门电路2.组合逻辑电路3.时序逻辑电路4.补充实验(选做)实验报告基本门电路一、实验目的1、了解基于Verilog的基本门电路的设计及其验证。

2、熟悉利用EDA工具进行设计及仿真的流程。

二、实验环境Libero仿真软件(参考附录C)。

三、实验内容1、参考附录C掌握Libero软件的使用方法。

2、参考附录C中“一个完整的例子”,进行针对74系列基本门电路的设计,并完成相应的仿真实验。

3、参考附录D的设计代码、测试平台代码(可自行编程)及附录C的步骤,完成74HC00、74HC02、74HC04、74HC08、74HC32、74HC86相应的设计、综合及仿真。

4、提交针对74HC00、74HC02、74HC04、74HC08、74HC32、74HC86(任选一个)的综合结果,以及相应的功能仿真结果。

四、实验结果和数据处理1、模块及测试平台代码清单module HC00(A,B,Y); input [4:1]A,B; output[4:1]Y;assign Y=~(A&B); endmodule`timescale 1ns/1ns module testbench;reg a,b;wire y; HC00 test(a,b,y);initialbegina=0;b=0;#5 a=1;#5 b=1;#5 a=0;#5 b=0;end endmodule2、第一次仿真结果。

(将相关窗口调至合适大小,使波形能完整显示,对窗口截图。

1后面实验中的仿真使用相同方法处理)3、综合结果。

(将相关窗口调至合适大小,使RTL图能完整显示,对窗口截图,后面实验中的综合使用相同方法处理)4、第二次仿真结果(综合后)。

数字逻辑第一次实验报告-模板n数字逻辑实验报告(1)数字逻辑实验1一、系列二进制加法器设计50% 二、小型实验室门禁系统设计50%总成绩姓名:学号:班级:CS指导教师:计算机科学与技术学院评语:(包含:预习报告内容、实验过程、实验结果及分析)2018年5 月22 日数字逻辑实验报告系列二进制加法器设计预习报告一、系列二进制加法器设计1、实验名称系列二进制加法器设计。

2、实验目的要求同学采用传统电路的设计方法,对5种二进制加法器进行设计,并利用工具软件,例如,“logisim”软件的虚拟仿真功能来检查电路设计是否达到要求。

通过以上实验的设计、仿真、验证3个训练过程使同学们掌握传统逻辑电路的设计、仿真、调试的方法。

3、实验所用设备Logisim2.7.1软件一套。

4、实验内容对已设计的5种二进制加法器,使用logisim软件对它们进行虚拟实验仿真,除逻辑门、触发器外,不能直接使用logisim软件提供的逻辑库元件,具体内容如下。

(1)一位二进制半加器设计一个一位二进制半加器,电路有两个输入A、B,两个输出S和C。

输入A、B分别为被加数、加数,输出S、C为本位和、向高位进位。

(2)一位二进制全加器设计一个一位二进制全加器,电路有三个输入A、B和Ci ,两个输出S和Co。

输入A、B和Ci 分别为被加数、加数和来自低位的进位,输出S和Co为本位和和向高位的进位。

(3)串行进位的四位二进制并行加法器用四个一位二进制全加器串联设计一个串行进位的四位二进制并行加法器,电路有九个输入A3、A2、A1、A、B3、B2、B1、B和C,五个输出S3、S2、S1、S 0和C4。

输入A= A3A2A1A、B= B3B2B1B和C分别为被加数、加数和来自低位的进位,输出S= S3S2S1S和Co为本位和和向高位的进位。

(4)先行进位的四位二进制并行加法器利用超前进位的思想设计一个先行进位的四位二进制并行加法器,电路有九个输入A3、A2、A1、A、B3、B2、B1、B和C,五个输出S3、S2、S1、S和C4。

数字逻辑实验报告(1)团队成员:报告人:实验指导教师:报告批阅教师:计算机科学与技术学院20 年月日学生姓名:学号:所在班级:一、实验内容组合逻辑电路的设计二、实验目的1.熟悉DICE-SEM数字逻辑实验箱的使用方法;2.掌握逻辑门功能的测试方法;3.掌握组合逻辑电路的分析和设计方法;4.掌握组合逻辑电路的功能测试方法。

三、实验所用组件四、实验要求1.一位全加/全减法器的实现(必选)设计一个全加全减法器,电路有四个输入M、A、B、和C in,两个输出S和C o。

要求如下:(1)M=0时,电路实现加法运算。

输入端A、B、和C in分别为被加数、加数和来自低位的进位,输出S和C o为本位和和向高位的进位;(2)M=1时,电路实现减法运算。

输入端A、B、和C in分别为被减数、减数和来自低位的借位,输出S和C o为本位差和向高位的借位。

2.舍入与奇偶检测电路的设计(必选)设计一个舍入与奇偶检测电路,该电路输入为8421码,输出为F1和F2。

要求如下:F1为四舍五入的输出信号,F2为奇偶检测输出信号。

当电路检测到输入的代码大于或等于(5)10时,输出F1=1,否则F1=0;当输入代码中的1的个数为奇数个时,输出F2=1,否则F2=0。

3.四路选择器的实现(可选)设计一个四路选择器,电路有6个输入端A1,A0,OE,D0,D1,D2,D3,一个输出学生姓名:学号:所在班级:端Y 。

要求如下:OE 为使能控制端,A 1,A 0为数据选择控制端,D 0,D 1,D 2,D 3为数据输入端。

当1=OE 时,电路不工作,输出为高阻状态; 当0=OE 时,电路工作,输出Y 由A 1,A 0决定,即: 当A 1A 0=00时,Y= D 0; 当A 1A 0=01时,Y= D 1; 当A 1A 0=10时,Y= D 2; 当A 1A 0=11时,Y= D 3。

附:三态、六总线驱动器74LS244的管脚图和逻辑表达式如图1和表1所示。

一、实验目的本次实验旨在通过实际操作,加深对数字逻辑基本原理和设计方法的理解,提高学生在数字电路设计、仿真和调试方面的实践能力。

通过完成以下实验任务,使学生掌握以下技能:1. 理解数字逻辑电路的基本概念和原理。

2. 掌握数字逻辑电路的设计方法和步骤。

3. 学会使用仿真软件进行电路设计和仿真测试。

4. 掌握数字逻辑电路的调试和优化方法。

二、实验内容本次实验主要包含以下三个部分:1. 组合逻辑电路设计:设计一个四位加法器,并使用Logisim软件进行仿真测试。

2. 时序逻辑电路设计:设计一个简单的计数器,并使用Verilog语言进行描述和仿真。

3. 数字逻辑电路综合应用:设计一个简单的数字信号处理器,实现基本的算术运算。

三、实验步骤1. 组合逻辑电路设计(1)分析题目要求,确定设计目标和输入输出关系。

(2)根据输入输出关系,设计四位加法器的逻辑电路。

(3)使用Logisim软件搭建电路,并设置输入信号。

(4)观察仿真结果,验证电路功能是否正确。

2. 时序逻辑电路设计(1)分析题目要求,确定设计目标和状态转移图。

(2)使用Verilog语言描述计数器电路,包括模块定义、输入输出定义、状态定义和状态转移逻辑。

(3)使用仿真软件进行测试,观察电路在不同状态下的输出波形。

3. 数字逻辑电路综合应用(1)分析题目要求,确定设计目标和功能模块。

(2)设计数字信号处理器电路,包括算术运算单元、控制单元和存储单元等。

(3)使用仿真软件进行测试,验证电路能否实现基本算术运算。

四、实验结果与分析1. 组合逻辑电路设计实验结果:通过仿真测试,四位加法器电路功能正常,能够实现两个四位二进制数的加法运算。

分析:在设计过程中,遵循了组合逻辑电路设计的基本原则,确保了电路的正确性。

2. 时序逻辑电路设计实验结果:通过仿真测试,计数器电路功能正常,能够实现从0到9的计数功能。

分析:在设计过程中,正确描述了状态转移图,并使用Verilog语言实现了电路的功能。

一、实验名称布尔逻辑实验二、实验目的1. 理解布尔逻辑的基本概念和运算规则。

2. 掌握布尔逻辑门(与门、或门、非门、异或门等)的电路原理和功能。

3. 通过实验加深对布尔逻辑在数字电路中的应用理解。

三、实验器材1. 布尔逻辑门实验板2. 数字信号发生器3. 测试仪器4. 导线、连接器等四、实验原理布尔逻辑是一种基于二值(0和1)运算的数学体系,广泛应用于数字电路和计算机科学中。

布尔逻辑门是布尔逻辑的基本组件,通过组合不同的逻辑门可以构建复杂的逻辑电路。

五、实验内容1. 与门实验- 实验目的:验证与门(AND Gate)的输出逻辑。

- 实验步骤:1. 将输入端A和B分别接入数字信号发生器。

2. 调整信号发生器,使其输出端分别为0和1,观察与门的输出。

3. 重复步骤2,分别调整A和B的输入,记录与门的输出。

- 实验结果:与门的输出符合逻辑与运算规则。

2. 或门实验- 实验目的:验证或门(OR Gate)的输出逻辑。

- 实验步骤:1. 将输入端A和B分别接入数字信号发生器。

2. 调整信号发生器,使其输出端分别为0和1,观察或门的输出。

3. 重复步骤2,分别调整A和B的输入,记录或门的输出。

- 实验结果:或门的输出符合逻辑或运算规则。

3. 非门实验- 实验目的:验证非门(NOT Gate)的输出逻辑。

- 实验步骤:1. 将输入端A接入数字信号发生器。

2. 调整信号发生器,使其输出端为0,观察非门的输出。

3. 重复步骤2,调整信号发生器输出为1,记录非门的输出。

- 实验结果:非门的输出符合逻辑非运算规则。

4. 异或门实验- 实验目的:验证异或门(XOR Gate)的输出逻辑。

- 实验步骤:1. 将输入端A和B分别接入数字信号发生器。

2. 调整信号发生器,使其输出端分别为0和1,观察异或门的输出。

3. 重复步骤2,分别调整A和B的输入,记录异或门的输出。

- 实验结果:异或门的输出符合逻辑异或运算规则。

六、实验结果分析通过实验,验证了布尔逻辑门的基本逻辑运算规则。

___计算机__学院计算机科学与技术专业班、学号姓名协作者______________ 教师评定_________________实验题目_________基于Libero的数字逻辑设计仿真及验证实验_________1、熟悉EDA工具的使用;仿真基本门电路。

2、仿真组合逻辑电路。

3、仿真时序逻辑电路。

4、基本门电路、组合电路和时序电路的程序烧录及验证。

5、数字逻辑综合设计仿真及验证。

实验报告1、基本门电路一、实验目的1、了解基于Verilog的基本门电路的设计及其验证。

2、熟悉利用EDA工具进行设计及仿真的流程。

3、学习针对实际门电路芯片74HC00、74HC02、74HC04、74HC08、74HC32、74HC86进行VerilogHDL设计的方法。

二、实验环境Libero仿真软件。

三、实验内容1、掌握Libero软件的使用方法。

2、进行针对74系列基本门电路的设计,并完成相应的仿真实验。

3、参考教材中相应章节的设计代码、测试平台代码(可自行编程),完成74HC00、74HC02、74HC04、74HC08、74HC32、74HC86相应的设计、综合及仿真。

4、提交针对74HC00、74HC02、74HC04、74HC08、74HC32、74HC86(任.)的综合结果,以及相应的仿真结果。

选一个...四、实验结果和数据处理模块及测试平台代码清单1、所有..//74HC00代码-与非// 74HC00.vmodule HC00(A, B, Y);input [3:0] A, B;output [3:0] Y;assign Y = ~(A&B);endmodule//74HC00测试平台代码// test_00.v`timescale 1ns/1nsmodule test_00;reg [3:0] a,b;wire [3:0] y;HC00 u(a, b, y);initialbegina = 4'b0000;b = 4'b0001;#10 b = b<<1;//0010#10 b = b<<1;//0100#10 b = b<<1;//1000a = 4'b1111;b = 4'b0001;#10 b = b<<1;#10 b = b<<1;#10 b = b<<1;endendmodule//74HC02代码-或非// 74HC02.vmodule HC02(A, B, Y);input [3:0] A, B;output [3:0]Y;assign Y = ~(A|B); endmodule//74HC02测试平台代码// test_02.v`timescale 1ns/1nsmodule test_02;reg [3:0] a,b,c;wire [3:0] y;HC02 u(a, b, y);initialbegina = 4'b1111;c = 4'b0001;b = ~c;c = c<<1;#10 b = ~c;c = c<<1;#10 b = ~c;c = c<<1;#10 b = ~c;a = 4'b0000;c = 4'b0001;b = ~c;c = c<<1;#10 b = ~c;c = c<<1;#10 b = ~c;c = c<<1;#10 b = ~c;endendmodule//74HC04代码-非// 74HC04.vmodule HC04(A, Y);input [3:0] A;output [3:0]Y;assign Y = ~A; endmodule//74HC04测试平台代码// test_04.v`timescale 1ns/1ns module test_04;reg [3:0] a;wire [3:0] y;HC04 u (a, y);initialbegina = 4'b0001;#10 a = a<<1;#10 a = a<<1;#10 a = a<<1;end endmodule//74HC08代码-与// 74HC08.vmodule HC08(A, B, Y);input [3:0] A, B;output [3:0]Y;assign Y = A&B; endmodule//74HC08测试平台代码// test_08.v`timescale 1ns/1nsmodule test_08;reg [3:0] a,b;wire [3:0] y;HC00 u(a, b, y);initialbegina = 4'b0000;b = 4'b0001;#10 b = b<<1;#10 b = b<<1;#10 b = b<<1;a = 4'b1111;b = 4'b0001;#10 b = b<<1;#10 b = b<<1;#10 b = b<<1;endendmodule//74HC32代码-或//74HC32.vmodule HC32(A, B, Y);input [3:0] A, B;output [3:0]Y;assign Y = A|B; endmodule//74HC32测试平台代码// test_32.v`timescale 1ns/1nsmodule test_32;reg [3:0] a,b,c;wire [3:0] y;HC02 u(a, b, y);initialbegina = 4'b1111;c = 4'b0001;b = ~c;c = c<<1;#10 b = ~c;c = c<<1;#10 b = ~c;c = c<<1;#10 b = ~c;a = 4'b0000;c = 4'b0001;b = ~c;c = c<<1;#10 b = ~c;c = c<<1;#10 b = ~c;c = c<<1;#10 b = ~c;endendmodule//74HC86代码-异或module HC86(A, B, Y);input [3:0] A, B;output [3:0]Y;assign Y = A^B; endmodule//74HC86测试平台代码// test_86.v`timescale 1ns/1nsmodule test_86;reg [3:0] a, b;wire [3:0] y;HC86 u (a, b, y);initialbegina = 4'b0000;b = 4'b0001;#10 b = b<<1;#10 b = b<<1;#10 b = b<<1;#10a = 4'b1111;b = 4'b0001;#10 b = b<<1;#10 b = b<<1;#10 b = b<<1;endendmodule2、第一次仿真结果(任选一个门,请注明,插入截图,下同.................)。

计算机____学院___专业___班________组学号______姓名____协作者______________ 教师评定_________________实验题目_________基于Libero的数字逻辑设计仿真及验证实验_________1、熟悉EDA工具的使用;仿真基本门电路。

2、仿真组合逻辑电路。

3、仿真时序逻辑电路。

4、基本门电路、组合电路和时序电路的程序烧录及验证。

5、数字逻辑综合设计仿真及验证。

实验报告1、基本门电路一、实验目的1、了解基于Verilog的基本门电路的设计及其验证。

2、熟悉利用EDA工具进行设计及仿真的流程。

3、学习针对实际门电路芯片74HC00、74HC02、74HC04、74HC08、74HC32、74HC86进行VerilogHDL设计的方法。

二、实验环境Libero仿真软件。

三、实验内容1、掌握Libero软件的使用方法。

2、进行针对74系列基本门电路的设计,并完成相应的仿真实验。

3、参考教材中相应章节的设计代码、测试平台代码(可自行编程),完成74HC00、74HC02、74HC04、74HC08、74HC32、74HC86相应的设计、综合及仿真。

4、提交针对74HC00、74HC02、74HC04、74HC08、74HC32、74HC86(任.选一个...)的综合结果,以及相应的仿真结果。

四、实验结果和数据处理1、所有..模块及测试平台代码清单//74HC00代码-和非// HC00.vmodule HC00(A,B,Y);input [4:1]A,B;output [4:1]Y;assign Y=~(A&B);endmodule//74HC00测试平台代码// test.v`timescale 1ns/1nsmodule test1();reg [4:1]a,b;wire [4:1]y;HC00 u1(a,b,y);initialbegina=4'b0000; b=4'b0001;#10 b=b<<1;#10 b=b<<1;#10 b=b<<1;a=4'b1111; b=4'b0001;#10 b=b<<1;#10 b=b<<1;#10 b=b<<1;endendmodule//74HC02代码-或非// HC02.vmodule HC02(A,B,Y);input [4:1]A,B;output [4:1]Y;assign Y=~(A|B);endmodule//74HC02测试平台代码// test.v`timescale 1ns/1nsmodule test2();reg [4:1]a,b;wire [4:1]y;HC02 u2(a,b,y);initialbegina=4'b0000; b=4'b0001; #10 b=b<<1;#10 b=b<<1;#10 b=b<<1;a=4'b1111; b=4'b0001; #10 b=b<<1;#10 b=b<<1;#10 b=b<<1;endendmodule//74HC04代码-非// HC04.vmodule HC04(A,Y); input [6:1]A;output [6:1]Y;assign Y=~A; endmodule//74HC04测试平台代码// test.v`timescale 1ns/1ns module test3();reg [6:1]a;wire [6:1]y;HC04 u3(a,y);initialbegina=4'b000001;#10 a=a<<1;#10 a=a<<1;#10 a=a<<1;#10 a=a<<1;#10 a=a<<1;endendmodule//74HC08代码-和// HC08.vmodule HC08(A,B,Y); input [4:1]A,B;output [4:1]Y;assign Y=A&B; endmodule//74HC08测试平台代码// test.v`timescale 1ns/1ns module test4();reg [4:1]a,b;wire [4:1]y;HC08 u4(a,b,y);initialbegina=4'b0000; b=4'b0001; #10 b=b<<1;#10 b=b<<1;#10 b=b<<1;a=4'b1111; b=4'b0001; #10 b=b<<1;#10 b=b<<1;#10 b=b<<1;endendmodule//74HC32代码-或// HC32.vmodule HC32(A,B,Y); input [4:1]A,B;output [4:1]Y;assign Y=A|B; endmodule//74HC32测试平台代码// test.v`timescale 1ns/1ns module test5();reg [4:1]a,b;wire [4:1]y;HC32 u5(a,b,y);initialbegina=4'b0000; b=4'b0001; #10 b=b<<1;#10 b=b<<1;#10 b=b<<1;a=4'b1111; b=4'b0001; #10 b=b<<1;#10 b=b<<1;#10 b=b<<1;endendmodule//74HC86代码-异或// HC86.vmodule HC86(A,B,Y);input [4:1]A,B;output [4:1]Y;assign Y=A^B;endmodule//74HC86测试平台代码// test.v`timescale 1ns/1nsmodule test6();reg [4:1]a,b;wire [4:1]y;HC86 u6(a,b,y);initialbegina=4'b0000; b=4'b0001;#10 b=b<<1;#10 b=b<<1;#10 b=b<<1;a=4'b1111; b=4'b0001;#10 b=b<<1;#10 b=b<<1;#10 b=b<<1;endendmodule2、第一次仿真结果(任选一个门,请注明,插入截图,下同.................)。

6、数字逻辑综合设计仿真及验证一、实验目的1、进一步熟悉利用EDA工具进行设计及仿真的流程。

2、熟悉利用EDA工具中的图形化设计界面进行综合设计。

3、熟悉芯片烧录的流程及步骤。

4、掌握分析问题、解决问题的综合能力,通过EDA工具设计出能解决实际问题的电路。

二、实验环境1、Libero仿真软件。

2、DIGILOGIC-2011数字逻辑及系统实验箱。

3、Actel Proasic3 A3P030 FPGA核心板及Flash Pro4烧录器。

三、实验内容1、循环数码显示在学生自己的工程项目文件中,新建一SmartDesign文件,命名要求:姓名拼音首字母+下划线+cp1,测试文件名:test+下划线+cp1使用SmartDesign工具进行设计,要求如下:(1)使用已设计的74HC161、74HC85、74HC4511模块,及IP核中Actel Macros 库中的反相器模块(INV),在SmartDesign画布中设计下图左框中的模块。

abcdefg 设计完成后,将SmartDesign画布中的设计截图。

(截图)(2)设计相应的测试平台。

测试平台中的数据要求所输入的A3A2A1A0及B3B2B1B0分别为学生学号末四位的最小数及最大数所对应的二进制数。

//测试平台代码(3)第一次仿真结果(4)综合结果(5)布局布线(引脚分配截图)。

注意,布局布线时输入引脚应避开FPGA板中上(6)第三次仿真结果(布局布线后)(7)烧录。

完成后给老师检查。

2、4位学号显示设计要求:4位数码管依次显示本人学号末4位。

SmartDesign文件命名要求:姓名拼音首字母+下划线+cp2,测试文件名:test+下划线+cp23、交通灯控制器设计要求:交通路口东西向和南北向各有红、黄、绿三种交通灯,按“东西向红灯亮,南北向绿灯亮→东西向红灯亮,南北向黄灯亮→东西向绿灯亮,南北向红灯亮→东西向黄灯亮,南北向红灯亮”顺序循环变化,试设计状态机实现此功能。

计算机学院专业班学号姓名教师评定实验题目_________基于Libero的数字逻辑设计仿真及验证实验_________1、熟悉EDA工具的使用;仿真基本门电路。

2、门电路的综合实验3、组合逻辑电路实验4、时序逻辑电路实验5、数字逻辑综合设计仿真及验证。

注:所有基于Libero的实验,都在一个工程项目中完成,文件命名要求工程文件名(Project Name):学号+下划线+姓名拼音首字母(例:学号3115000001姓名张小童,工程文件名为:3115000001_zxt)实验报告1、基本门电路一、实验目的1、了解基于Verilog的基本门电路的设计及其验证。

2、熟悉利用EDA工具进行设计及仿真的流程。

3、学习针对实际门电路芯片74HC00、74HC02、74HC04、74HC08、74HC32、74HC86进行VerilogHDL设计的方法。

4、掌握Libero软件的使用方法。

二、实验环境Libero仿真软件。

三、实验内容1、在自己的工程文件中,新建一个设计代码文件(Verilog Source File),文件命名规则:学号+下划线+BasGate例:3115000001_BasGate.v在自己的工程文件中,新建一个测试平台文件(HDL Stimulus File),文件命名规则:test_BasGate.v2、进行针对74系列基本门电路的设计,并完成相应的仿真实验。

3、参考教材中相应章节的设计代码、测试平台代码(可自行编程),完成2输入与非门、2输入或非门、2输入与门、2输入或门、2输入异或门、非门的设计、综合及仿真。

4、提交针对基本门电路的综合结果,以及相应的仿真结果。

四、实验结果和数据处理1、门电路...模块清单及测试平台代码清单(1)所有硬件功能模块的代码清单(关键代码应有注释)(2)测试平台模块的代码清单(关键语句应有注释)2、第一次仿真结果(截图..)。

先将波形窗口背景设为白色..,调整窗口至合适大小,使波形能完整显示,再对窗口截图..。

4、组合逻辑电路综合一、实验目的1、了解基于Verilog的时序逻辑电路的设计及其验证。

2、熟悉利用EDA工具进行设计及仿真的流程。

3、掌握使用SmartDesign进行设计的方法。

二、实验环境Libero仿真软件。

三、实验内容在同学自己的工程文件中,新建一个设计文件和一个测试代码文件,命名要求:(1)SmartDesign设计文件命名为“学号+下划线+ Comparator”(例3115000001_Comparator.v)。

(2)测试文件命名为test_Comparator。

1、利用已经完成的74HC85模块,设计一个8位的数值比较器。

2、编写该设计的测试平台模块,完成该设计的综合前仿真、综合、综合后仿真、布局布线、布局布线后仿真。

四、实验结果和数据处理1、SmartDesign画布的截图。

2、测试平台代码`timescale 1ns/1nsmodule test_Comparator;reg [7:0] ina,inb;reg ig,ie,is;wire qg,qe,qs;hyf5_Comparatoru10(.DataA(ina),.DataB(inb),.ing(ig),.ine(ie),.ins(is),.Qg(qg),.Qe(qe),.Qs(qs));initialbeginina=0;repeat(20)#20 ina=$random;endinitialbegininb=0;repeat(20)#20 inb=$random;endinitialbeginig=0;ie=0;is=0;repeat(40)#10 {ig,ie,is}=$random; endinitial#400 $finish;endmodule3、综合前仿真截图4、综合的截图5、综合后仿真截图6、布局布线后仿真的截图。

5、时序逻辑电路一、实验目的1、了解基于Verilog的时序逻辑电路的设计及其验证。

2、熟悉利用EDA工具进行设计及仿真的流程。

《数字逻辑》实验报告

实验序号:1 实验项目名称:各种门功能的熟悉

计科1001

学号姓名专业、班

实验地点文波实验室指导教师时间2011.3

一、实验目的及要求

1、目的

熟悉各种门的功能,包括与门、非门、或门、与非、或非等等。

掌握各种门的真值表。

2、要求:

使用门来验证其真值表。

二、实验设备(环境)及要求

1、数字逻辑实验箱一套。

2、连结导线若干。

三、实验内容与步骤

使用实验室提供的芯片来验证各种门的功能,使用了与门,或门,非门,与非,或非,异或等等,每个芯片各使用了两个输入0和1,使用了不同的组合。

四、实验结果

与门:输入:00 01 10 11

输出:0 0 0 1

或门:输入:00 01 10 11

输出:0 1 1 1

非门:输入:0 1

输出:1 0与非:输入:00 01 10 11

输出:1 1 1 0

或非:输入:00 01 10 11

输出:1 0 0 0

五、分析讨论

需要看准指导书上写的芯片引脚的编号,而不能想当然的认为哪些是输入,哪些是输出。

六、教师评语:能按时完成实验报告,实验步骤清晰,分析合理,结论正确

签名:朱平

日期:2011年6月成绩

见成绩表。

实验报告

1、基本门电路

一、实验目的

1、熟悉EDA工具的使用;仿真基本门电路。

掌握基于Verilog的基本门电路的设计及其验证。

2、熟悉利用EDA工具进行设计及仿真的流程。

基本门电路的程序烧录及验证。

3、学习针对实际门电路芯片74HC00、74HC02、74HC0

4、74HC08、74HC32、74HC86进行VerilogHDL设计的方法。

二、实验环境

Libero仿真软件。

三、实验内容

1、掌握Libero软件的使用方法。

2、进行针对74系列基本门电路的设计,并完成相应的仿真实验。

3、参考教材中相应章节的设计代码、测试平台代码(可自行编程),完成74HC00、74HC02、74HC0

4、74HC08、74HC32、74HC86相应的设计、综合及仿真。

4、提交针对74HC00、74HC02、74HC04、74HC08、74HC32、74HC86(任选一个

....)的综合结果,以及相应的仿真结果。

四、实验结果和数据处理

1、所有

..模块及测试平台代码清单

//74HC00代码-与非门

//

module HC00(A,B,Y);

input [4:1]A,B;

assign Y=~(A&B);

endmodule

//74HC00测试平台代码

//

`timescale 1ns/1ns

module testbench();

reg [4:1]a,b;

wire [4:1]y;

HC00 u1(a,b,y);

initial

begin

a=4'b0000;b=4'b0001;

#10 b=b<<1;

#10 b=b<<1;

#10 b=b<<1;

a=4'b1111;b=4'b0001;

#10 b=b<<1;

#10 b=b<<1;

#10 b=b<<1;

end

endmodule

//74HC02代码-或非门

//

module HC02(A,B,Y);

output [4:1]Y;

assign Y=~(A|B);//或非

endmodule

//74HC02测试平台代码

`timescale 1ns/1ns

module test02();

reg [4:1]a,b;

wire [4:1]y;

HC02 u2(a,b,y);

initial

begin

a=4'b0000; b=4'b0001;

#10 b=b<<1;

#10 b=b<<1;

#10 b=b<<1;

#10

a=4'b1111; b=4'b0001;

#10 b=b<<1;

#10 b=b<<1;

#10 b=b<<1;

end

endmodule

//74HC04代码-非门

module HC04(A,Y);

input [6:1]A;

assign Y=~A;//非

endmodule

//74HC04测试平台代码

`timescale 1ns/1ns

module test04();

reg [6:1]a;

wire [6:1]y;

HC04 u4(a,y);

initial

begin

a=6'b000001;

#10 b=b<<1;

#10 b=b<<1;

#10 b=b<<1;

#10 b=b<<1;

#10 b=b<<1;

end

endmodule

//74HC08代码-与门

module HC08(A,B,Y);

input [4:1]A,B;

output [4:1]Y;

assign Y=A&B;//与

endmodule

//74HC08测试平台代码

`timescale 1ns/1ns

module test08();

reg [4:1]a,b;

wire [4:1]y;

HC08 u8(a,b,y);

initial

begin

a=4'b0000; b=4'b0001;

#10 b=b<<1;

#10 b=b<<1;

#10 b=b<<1;

#10

a=4'b1111; b=4'b0001;

#10 b=b<<1;

#10 b=b<<1;

#10 b=b<<1;

end

endmodule

//74HC32代码-或门

module HC32(A,B,Y);

input [4:1]A,B;

output [4:1]Y;

assign Y=A|B;//或

endmodule

//74HC32测试平台代码

`timescale 1ns/1ns

module test32();

reg [4:1]a,b;

wire [4:1]y;

HC32 u32(a,b,y);

initial

begin

a=4'b0000; b=4'b0001;

#10 b=b<<1;

#10 b=b<<1;

#10 b=b<<1;

#10

a=4'b1111; b=4'b0001;

#10 b=b<<1;

#10 b=b<<1;

#10 b=b<<1;

end

endmodule

//74HC86代码-异或门

module HC86(A,B,Y);

input [4:1]A,B;

output [4:1]Y;

assign Y=A&(~B)|(~A&B);//异或

endmodule

//74HC86测试平台代码

`timescale 1ns/1ns

module test86();

reg [4:1]a,b;

wire [4:1]y;

HC86 u86(a,b,y);

initial

begin

a=4'b0000; b=4'b0001;

#10 b=b<<1;

#10 b=b<<1;

#10 b=b<<1;

#10

a=4'b1111; b=4'b0001;

#10 b=b<<1;

#10 b=b<<1;

#10 b=b<<1;

end

endmodule

2、第一次仿真结果(任选一个门,请注明,

..)。

(将波形窗口背景设为

.....下同

..........插入截图,

白色

..。

后面实验中的仿真使用相..,调整窗口至合适大小,使波形能完整显示,对窗口截图

同方法处理)

3、综合结果(截图

..)。

(将相关窗口调至合适大小,使RTL图能完整显示,对窗口截图,后面实验中的综合使用相同方法处理)

4、第二次仿真结果(综合后)(截图

..)。

回答输出信号是否有延迟,延迟时间约为多少?

5、第三次仿真结果(布局布线后)(截图

..)。

回答输出信号是否有延迟,延迟时间约为多少?分析是否有出现竞争冒险。

2、基本门电路的程序烧录及验证

一、实验目的

1、熟悉利用EDA工具进行设计及仿真的流程。

2、熟悉实验箱的使用和程序下载(烧录)及测试的方法。

二、实验环境及仪器

1、Libero仿真软件。

2、DIGILOGIC-2011数字逻辑及系统实验箱。

3、Actel Proasic3 A3P030 FPGA核心板及Flash Pro4烧录器。

三、实验内容

1、新建一个工程文件,将前面已经设计好的74HC00、74HC0

2、74HC04、74HC08、74HC32、74HC86实例文件导入,(在SmartDesign窗口分别添加这6个模块,可选),完成相应连线。

按实验指导书P175的附录中所列引脚对应表来分配引脚,最后通过烧录器烧录至FPGA核心板上。

按分配的引脚连线,实测相应功能并记录结果。

详细步骤请参考教材及实验指导书的相关内容。

四、实验结果和数据处理

6、写入程序文件(烧录)

表4-1 74HC00输入输出状态

表4-2 74HC02输入输出状态

表4-3 74HC04输入输出状态

表4-4 74HC08输入输出状态

表4-5 74HC32输入输出状态

表4-6 74HC86输入输出状态

五、结论

六、问题与讨论。