三位二进制减法计数器与芯片仿真进制减法计数器

- 格式:docx

- 大小:289.17 KB

- 文档页数:10

1.二进制数(1011.1001)2转换为八进制数为 13.41 ,转换为十六进为B9 。

2.数字电路按照是否具有记忆功能通常可分为两类:组合逻辑电路、时序逻辑电路。

3.已知逻辑函数F =A ⊕B ,它的与非-与非表达式为 A B A B ,或与非表达式为 ()()A B A B++ 。

4.5个变量可构成 32 个最小项,变量的每一种取值可使 1 个最小项的值为1。

5.555定时器构成的施密特触发器,若电源电压V CC =12V ,电压控制端经0.01µF 电容接地,则上触发电平U T+ = 8 V ,下触发电平U T –= 4 V 。

6.逻辑函数的两种标准形式分别为7.将2004个“1”异或起来得到的结果是 08.半导体存储器的结构主要包含三个部分,分别是地址译码器、存储矩阵、输出缓冲器9.8位D/A 转换器当输入数字量10000000为5v 。

若只有最低位为高电平,则输出电压为( 0.039 )v ;当输入为10001000,则输出电压为( 5.31 )v 。

10.就逐次逼近型和双积分型两种A/D 转换器而言,(双积分型)的抗干扰能力强,(逐次逼近型)的转换速度快。

11.由555定时器构成的三种电路中,(施密特触发器)和(单稳态触发器)是脉冲的整形电路。

12.与PAL 相比,GAL 器件有可编程的输出结构,它是通过对(结构控制字)进行编程设定其(输出逻辑宏单元)的工作模式来实现的,而且由于采用了(E 2CMOS )的工艺结构,可以重复编程,使它的通用性很好,使用更为方便灵活。

13.逻辑函数有四种表示方法,它们分别是真值表、逻辑图、逻辑表达式、卡诺图。

14.将2004个“1”异或起来得到的结果是 0 。

15.目前我们所学的双极型集成电路和单极型集成电路的典型电路分别是(TTL )电路和(CMOS )电路。

16.施密特触发器有(两)个稳定状态.,多谐振荡器有(0)个稳定状态。

17.已知Intel2114是1K* 4位的RAM 集成电路芯片,它有地址线(10)条,数据线(4)条。

中南大学网络教育课程考试复习题及参考答案电子技术一、填空题:1。

在本征半导体中掺入微量三价元素形成型半导体,掺入微量五价元素形成型半导体。

2。

晶体管工作在截止区时,发射结向偏置,集电结向偏置。

3.硅稳压管的工作为 _ 区。

4。

为了避免50Hz电网电压的干扰进入放大器,应选用滤波电路。

5。

已知输入信号的频率为10kHz~12kHz,为了防止干扰信号的混入,应选用滤波电路。

6.为了获得输入电压中的低频信号,应选用滤波电路.7.为了稳定静态工作点,应引入负反馈.8.为了稳定放大倍数,应引入负反馈。

9.为了使放大电路的输出电阻增大应引入负反馈;深度负反馈的条件是。

10。

为了减小放大电路的输入电阻,应引入负反馈。

11.为了减小放大电路的输出电阻,应引入负反馈。

12.当集成运放组成运算电路时中,运放一般工作在状态。

13.在运放组成的电压比较器中,运放一般工作在或状态.14.在图1所示电路中,调整管为,采样电路由组成,基准电压电路由组成,比较放大电路由组成.图115。

在整流电路的输入电压相等的情况下,半波与桥式两种整流电路中,输出电压平均值最低的是整流电路.16。

直流电源由、、和四部分组成。

17。

串联型稳压电路由、、和四部分组成。

18.欲将方波电压转换成三角波电压,应选用运算电路。

19。

NPN型共集电极放大电路中的输出电压顶部被削平时,电路产生的是失真;乙类功放电路的主要缺点是输出有失真。

20. 比例运算电路的比例系数大于1,而比例运算电路的比例系数小于零。

21.正弦波自激振荡的幅值平衡条件为,相位平衡条件为。

22。

存储器按功能不同可分为存储器和存储器;23.RAM按存储单元结构特点又可分为和。

24.半导体存储器的结构主要包含三个部分,分别是、、。

25。

某存储器容量为8K×8位,则它的地址代码应取位。

26。

将Intel2114(1K*4位)RAM扩展成为8K*4位的存储器,需要Intel2114芯片数是 ,需要增加的地址线是条。

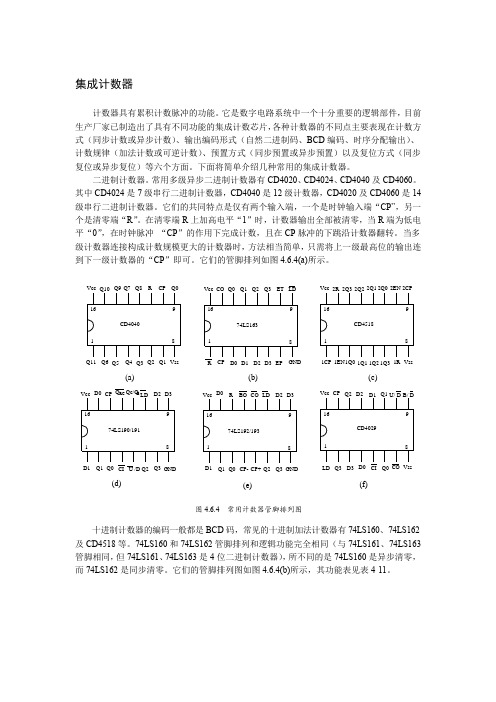

集成计数器计数器具有累积计数脉冲的功能。

它是数字电路系统中一个十分重要的逻辑部件,目前生产厂家已制造出了具有不同功能的集成计数芯片,各种计数器的不同点主要表现在计数方式(同步计数或异步计数)、输出编码形式(自然二进制码、BCD 编码、时序分配输出)、计数规律(加法计数或可逆计数)、预置方式(同步预置或异步预置)以及复位方式(同步复位或异步复位)等六个方面。

下面将简单介绍几种常用的集成计数器。

二进制计数器。

常用多级异步二进制计数器有CD4020、CD4024、CD4040及CD4060。

其中CD4024是7级串行二进制计数器,CD4040是12级计数器,CD4020及CD4060是14级串行二进制计数器。

它们的共同特点是仅有两个输入端,一个是时钟输入端“CP”,另一个是清零端“R ”。

在清零端R 上加高电平“1”时,计数器输出全部被清零,当R 端为低电平“0”,在时钟脉冲 “CP ”的作用下完成计数,且在CP 脉冲的下跳沿计数器翻转。

当多级计数器连接构成计数规模更大的计数器时,方法相当简单,只需将上一级最高位的输出连到下一级计数器的“CP ”即可。

它们的管脚排列如图4.6.4(a)所示。

图4.6.4 常用计数器管脚排列图十进制计数器的编码一般都是BCD 码,常见的十进制加法计数器有74LS160、74LS162及CD4518等。

74LS160和74LS162管脚排列和逻辑功能完全相同(与74LS161、74LS163管脚相同,但74LS161、74LS163是4位二进制计数器),所不同的是74LS160是异步清零,而74LS162是同步清零。

它们的管脚排列图如图4.6.4(b)所示,其功能表见表4-11。

CD4040Q11Q6Q5Q4Q3Q2Q1VssQ0CP R Q8Q7Q9Q10Vcc 18916Vcc 1891674LS163GNDRCP D0D1D2D3EPET LD Q3Q2Q1Q0CO 169Vcc 81Vss1CP 1EN1Q01Q11Q21Q31R 2CP 2EN 2Q02Q12Q22Q32R CD4518(a)(b)(c)Vcc 18916D1Q1Q0Q2Q3D3D2LD D08169Vcc 1D1Q1Q0CP-CP+Q2Q3D3D2LD CO BO R D074LS192/193CI U /D Qc/QB Q RC CP 74LS190/19181Vcc Vss169GND GNDLD Q3D3D0CI Q0CO B/ D U/ D Q1D1D2Q2CP CD4029(d)(e)(f)表4-11 74LS163的功能表表4-12 CD4518的功能表CD4518是双BCD 码计数器,图4.6.4(c)是其管脚排列图,其功能表见表4-12。

三位二进制减法计数器的设计-CAL-FENGHAI.-(YICAI)-Company One1目录1设计目的与作用 (1)设计目的及设计要求 (1)设计作用 (1)2设计任务 (1)3三位二进制减法计数器的设计 (1)设计原理 (1)设计过程 (2)4 74161构成227进制同步计数器并显示 (4)设计原理 (4)设计过程 (4)5仿真结果分析 (5)三位二进制减法计数器仿真结果 (5)74161构成227进制同步计数器的仿真结果 (8)6设计总结 (8)7参考文献 (9)1设计目的与作用设计目的及设计要求按要求设计三位二进制减法计数器(无效状态001,011)及用74161构成227进制同步计数器并显示,加强对数字电子技术的了解,巩固课堂上学到的知识,了解计数器,并且加强对软件multisim的了解。

设计作用multisim仿真软件的使用,可以使我们对计数器及串行检测器有更深的理解,并且学会分析仿真结果,与理论结果作比较。

加强了自我动手动脑的能力。

2设计任务1.三位二进制减法计数器(无效状态001,011)构成227进制同步计数器并显示3三位二进制减法计数器的设计设计原理设计一个三位二进制减法计数器(无效状态001,011)000 /0 010 /0 100 /0 101 /0 110 /0 111Q Q Q排列210图状态图设计过程a.选择触发器由于JK触发器的功能齐全,使用灵活,在这里选用3个CP上升沿触发的边沿JK触发器。

b .求时钟方程采用同步方案,故取012CP CP CP CP ===c .求状态方程由所示状态图可直接画出电路次态n+1n+1n+1210Q Q Q 卡诺图。

再分解开便可以得到如图各触发器的卡诺图。

Q 1n Q 0nQ 2n1图次态n+1n+1n+1210Q Q Q 卡诺图Q 1n Q 0nQ 1图n+12Q 的卡诺图Q 1n Q 0nQ 2n 0 1图 n+11Q 的卡诺图Q 1n Q 0nQ 2n 图 n+10Q 的卡诺图状态方程:nn Q Q Q Q Q Q 01n 2n 1n 21n 2++=+ (1)nn n n n Q Q Q Q Q 010111+=+ (2)n0n1n 2n 1n 21n 0Q Q Q Q Q Q +=+ (3)(2)求驱动方程JK 触发器的特性方程为n n 1n Q K Q J Q +=+120Q Q J ⊕=,n Q Q K 1n 20+=n 011Q K J ==n 0n 12Q Q J +=,n 0n 12Q Q K =(3)画逻辑电路图选用触发器,写出时钟方程,输出方程,驱动方程,便可以画出如图所示的逻辑电路图。

三位二进制减法计数器真值表在计算机科学和数字电子技术中,二进制是一种常用的计数系统。

它由两个数字0和1组成,可以用来表示数字、字符和其他信息。

在许多计算机中,使用二进制进行加法和减法运算是非常常见的。

而二进制减法是通过将减数与被减数相减得到差值的过程。

为了进行二进制减法运算的实现,我们可以使用一个二进制减法计数器。

这个计数器可以将两个二进制数相减,并输出差值。

一个三位二进制减法计数器由三个二进制位构成,每个位可以取0或1的值。

这样的计数器可以表示从0到7之间的数字范围。

下面是一个三位二进制减法计数器的真值表:被减数(A)减数(B)差值(D)000 000 000001 000 001010 000 010011 000 011100 000 100101 000 101110 000 110111 000 111000 001 111001 001 000010 001 001011 001 010 100 001 011 101 001 100 110 001 101 111 001 110 000 010 110 001 010 111 010 010 000 011 010 001 100 010 010 101 010 011 110 010 100 111 010 101 000 011 101 001 011 110 010 011 111 011 011 000 100 011 001 101 011 010 110 011 011 111 011 100000 100 011 001 100 100 010 100 101 011 100 110 100 100 111 101 100 000 110 100 001 111 100 010 000 101 010 001 101 011 010 101 100 011 101 101 100 101 110 101 101 111 110 101 000 111 101 001 000 110 001 001 110 010 010 110 011 011 110 100 100 110 101101 110 110110 110 111111 110 000000 111 000001 111 001010 111 010011 111 011100 111 100101 111 101110 111 110111 111 111在这个真值表中,被减数(A)和减数(B)分别取0和1的所有情况下,都列出了对应的差值(D)。

1 三位二进制同步减法计数器的设计(000、010)1.1 课程设计的目的1、学会利用触发器和逻辑门电路,实现六进制同步减法计数器的设计2、学会掌握并能使用常用芯片74LS112、74LS08芯片的功能3、学会使用实验箱、使用软件画图4、了解计数器的工作原理1.2 设计的总体框图1.3 设计过程1逻辑抽象分析CP为输入的减法计数脉冲,每当输入一个CP脉冲,计数器就减一个1,当不够减时就向高位借位,即输出借位信号。

当向高位借来1时应当为8,减一后为7。

状态图中,状态为000输入一个CP脉冲,不够减,向高位借1当8,减1后剩7,计数器的状态应由000转为111,同时向高位输出借位信号,总体框图中C为借位信号。

2状态图状态000、010为无效状态,据分析状态图为:/0 /0 /0 /0 /0001011100101110111/13 选择触发器,求时钟方程、输出方程和状态方程● 选择触发器由于状态数M=6,触发器的个数n 满足122n n M -≤≤,故n 的取值为3。

选用3个下降沿触发的JK 触发器。

● 求时钟方程因为是同步,故012CP CP CP CP ===● 求输出方程1.3.1 输出C 的卡诺图根据输出C 的卡诺图可得输出方程为C=Q 2n Q 1n● 求状态方程计数器的次态的卡诺图为1.3.2 次态210n n nQ Q Q 的卡诺图各个触发器的次态卡诺图如下:1.3.3 2nQ 次态卡诺图1.3.4 1n Q 的次态卡诺图1.3.5 0nQ 的次态卡诺图根据次态卡诺图可得次态方程为:Q 2n+1=Q 1n Q 0n +Q 2n Q 1nQ 1n+1= Q 1n Q 0n + Q 2n Q 1n + Q 2n Q 1n Q 0n Q 0n+1 =Q 2n +Q 0n4 求驱动方程Q 2n+1 =Q 1n Q 2n + Q 0n Q 1n Q 2n Q 1n+1=Q 0n Q 2n Q 1n +Q 0n Q 2n Q 1n Q 0n+1=Q 2n Q 0n +Q 2n Q 0n驱动方程是:J 0 = Q 2n K 0 =Q 2n J 1 =Q 0n Q 2n K 1= Q 0n Q 2J 2 = Q 1n K 2=Q 0n Q 1n5 检查是否能自启动将无效状态100、101分别代入输出方程、状态方程进行计算,结果如下:/0 /0000 111 010 001而000、010都是有效状态,故设计的电路能够自启动。

单独招生(机电类)模拟题与参考答案一、单选题(共52题,每题1分,共52分)1.在电动机的继电-接触控制电路中,熔断器的功能是实现A、过载保护B、短路保护C、零压保护D、失压保护正确答案:B2.平面度公差属于( )A、形状公差B、定位公差C、定向公差D、跳动公差正确答案:A3.某电容器的电容为C,如不带电时它的电容是()A、0B、CC、大于CD、小于C正确答案:B4.滚动轴承与滑动轴承相比,其优点是A、承受冲击载荷能力好B、高速运转时噪声小C、起动及运转时摩擦力距小D、径向尺寸小正确答案:C5.加工两种或两种以上工件的同一夹具,称为( )A、专用夹具B、通用夹具C、车床夹具D、组合夹具正确答案:B6.环境十分潮湿的场合应采用( )电动机A、封闭式B、防护式C、开启式D、防爆式正确答案:A7.正弦交流电的有效值( )A、不随交流电的变化而变化B、在正半周变化,负半周不变化C、不能确定D、在正半周不变化,负半周变化正确答案:A8.额定电压相等的两只灯泡,额定功率大的灯泡电阻A、相等B、无法确定C、小D、大正确答案:C9.三相异步电动机旋转磁场的方向由三相电源的()决定。

A、频率B、相序C、最大值D、相位正确答案:B10.变压器一次、二次绕组中不能改变的物理量是( D )A、电压B、电流C、阻抗D、频率正确答案:D11.判断磁场对通电导线的作用力方向用A、左手螺旋定律B、右手定则C、左手定律D、右手螺旋定律正确答案:C12.20V,25W白炽灯正常发光(),消耗的电能为1KW.h。

A、25hB、20hC、40hD、5h正确答案:C13.工艺尺寸链的封闭环是( )A、尺寸最小的环B、精度要求最高的环C、经过加工直接保证的尺寸D、经过加工后间接得到的尺寸正确答案:D14.十进制整数转换为二进制数一般采用A、除2取余法B、除10取整法C、除10取余法D、除2取整法正确答案:A15.在桥式整流电容滤波电路中,变压器二次侧电压V2=20V,二极管承受的最高反向电压是A、20VB、28VC、56VD、24V正确答案:B16.导体作切割磁力线运动,其运动方向与磁场方向的夹角为()时,导体感应的电动势为最大A、0度B、90度C、180度D、难以确定其角度正确答案:B17.某放大器输出电压V1=1.0MV,输出电压V0=0.1V,则电压增益为A、10dBB、20dBC、40dBD、100dB正确答案:C18.三极管基本放大电路中,设置静态工作点的目的是A、减小放大电路的非线性失真B、减小放大电路的放大倍数C、计算放大电路的静态工作点D、计算放大电路的放大倍数正确答案:A19.直流放大电路主要放大对象是()A、变化缓慢的直流信号B、大电压C、高频信号D、大电流正确答案:A20.精密测量工件直径的量具是( )A、千分尺B、百分表C、游标卡尺D、钢尺正确答案:A21.应用叠加原理计算线性电路时,()叠加。

目录1 课程设计的目的与作用 01.1课程设计目的 02 所用multisim软件环境介绍 02.1 Multisim软件环境介绍 02.2 Multisim软件界面介绍 (1)3设计任务 (2)3.1设计的总体框图 (2)3.1.1三位二进制减法计数器的总体框图 (2)3.1.2 串行序列信号检测器的总体框图 (2)3.1.3 74193芯片仿真63进制减法计数器原理 (2)3.2设计过程 (2)3.2.1 三位二进制同步减法计数器 (2)3.2.2串行序列信号检测器 (4)3.2.3 74193芯片仿真63进制减法计数器 (5)4实验仪器 (6)4.1三位二进制减法器 (6)4.2串行序列检测器 (6)4.3 74193芯片仿真63进制减法器计数 (6)5仿真结果分析 (6)5.1三位二进制同步减法计数器的电路原理图及结果 (6)5.2串行序列信号检测器电路原理图及结果 (7)5.3 74193芯片仿真63进制减法计数器的电路原理图及结果 (7)6设计总结和体会 (8)7参考文献 (8)1 课程设计的目的与作用1.1课程设计目的1.通过Multisim的仿真设计,掌握Multisim软件的基本使用方法;2.学会在multisim环境下建立电路模型,能进行正确的仿真;3.通过Multisim的仿真,熟练掌握三位二进制同步加法计数器和串行序列检测器电路,10000串行序列检测器电路设计;4.学会分析仿真结果的正确性,与理论计算值进行比较;5.通过课程设计,加强动手,动脑的能力。

2 所用multisim软件环境介绍2.1 Multisim软件环境介绍Multisim是美国国家仪器(NI)有限公司推出的以Windows为基础的仿真工具,适用于板级的模拟/数字电路板的设计工作。

它包含了电路原理图的图形输入、电路硬件描述语言输入方式,具有丰富的仿真分析能力。

Multisim 10 启动画面图工程师们可以使用Multisim交互式地搭建电路原理图,并对电路进行仿真。

Multisim提炼了SPICE仿真的复杂内容,这样工程师无需懂得深入的SPICE技术就可以很快地进行捕获、仿真和分析新的设计,这也使其更适合电子学教育。

通过Multisim和虚拟仪器技术,PCB设计工程师和电子学教育工作者可以完成从理论到原理图捕获与仿真再到原型设计和测试这样一个完整的综合设计流程。

NI Multisim软件结合了直观的捕捉和功能强大的仿真,能够快速、轻松、高效地对电路进行设计和验证。

凭借NI Multisim,您可以立即创建具有完整组件库的电路图,并利用工业标准SPICE模拟器模仿电路行为。

借助专业的高级SPICE分析和虚拟仪器,您能在设计流程中提早对电路设计进行的迅速验证,从而缩短建模循环。

与NI LabVIEW和SignalExpress软件的集成,完善了具有强大技术的设计流程,从而能够比较具有模拟数据的实现建模测量。

突出优点1.通过直观的电路图捕捉环境, 轻松设计电路2.通过交互式SPICE仿真, 迅速了解电路行为3.借助高级电路分析, 理解基本设计特征4.通过一个工具链, 无缝地集成电路设计和虚拟测试5.通过改进、整合设计流程, 减少建模错误并缩短上市时间2.2 Multisim软件界面介绍Multisim 10主界面。

启动Multisim,就会看到其主界面,主要是由菜单栏、系统工具栏、设计工具栏、元件工具栏、仪器工具栏使用中元件列表、仿真开关、状态栏以及电路图编辑窗口等组成。

如图A所示。

图2.3.1 A图 Multisim软件编辑窗口Multisim 10提供了丰富的元器件。

这些元器件按照不同的类型和种类分别存放在若干个分类库中。

这些元件包括现实元件和虚拟元件。

所谓的现实元件给出了具体的型号,它们的模型数据根据该型号元件参数的典型值确定。

而所谓的虚拟元件没有型号,它的模型参数是根据这种元件各种元件各种型号参数的典型值,而不是某一种特定型号的参数典型值确定。

另外,Multisim 10元件库中还提供一种3D虚拟元件,这种元件以三维的方式显示,比较形象、直观.。

Multisim 10容许用户根据自己的需要创建新的元器件,存放在用户元器件库中。

如B图所示。

Multisim 10提供了品种繁多、方便实用的虚拟仪器。

比如数字万用表、信号发生器、示波器等17种虚拟仪器。

点击主界面中仪表栏的相应的按钮即可方便地取用所需的虚拟仪器如C图所示。

图2.3.2 B图用户元器件库图图2.3.3 C图虚拟仪器图示Multisim 10提供了各种不同功能的分析工具。

点击分析按钮,即可拉出分析菜单,其中列出了Multisim 10的各种分析工具,例如直流工作点分析、交流分析、瞬态分析等。

Multisim为用户提供了丰富的元器件,并以开放的形式管理元器件,使得用户能够自己添加所需要的元器件,如D图所示的界面。

图2.3.4 D图元器件库图示3设计任务3.1设计的总体框图3.1.1三位二进制减法计数器的总体框图CP Y输入脉冲 串行序列输出3.1.2 串行序列信号检测器的总体框图CP Y输入脉冲 串行序列输出3.1.3 74193芯片仿真63进制减法计数器原理CR 异步清零端,高电平有效;是异步置数端;是减法计数脉冲输入端;是进位脉冲输出端;是借位脉冲输出端;A 到D 是并行数据输入端;是计数器状态输出端。

当多个74193级联时,只要把低位的端端分别与高位的C 端、C 端连接起来,各个芯片的CR 端连接在一起、端连接在一起就可以了。

3.2设计过程3.2.1 三位二进制同步减法计数器1)状态图/0 /0 /0 /0 /0 010 011 100 101 110 111 /12)选择的触发器名称:选用三个CP 下降沿触发的边沿JK 触发器(3)输出方程:Y=nn n Q Q Q 012 (4)状态方程三位二进制同步减法计数器次态卡诺图: Q 1n Q 0nQ 2n 00 01 11 10XXXXXX010111串行序列信号检测器三位二进制同步减法计数器011 100 110 1011三位二进制同步减法计数器次态卡诺Q 2n+1的卡诺图:Q 1n Q 0nQ 2n 00 01 11 101 Q 1n+1的卡诺图:Q 1n Q 0nQ 2n 00 01 11 100 1 Q 0n+1的卡诺图:Q 1n Q 0nQ 2n 00 01 11 10由卡诺图得出状态方程为:1n 2+Q =nQ 2(nQ 0+nQ 1)+nQ 2n Q 01n 1+Q =nQ 0nQ 1+n Q 1nQ 0nQ 21n 0+Q =nQ 0(5)驱动方程0J =1 1J =2J = nQ 00K =1 1K =nQ 2n Q 0 2K =n Q 0nQ 1(6)时钟方程 CP=1CP =2CP =3CP (7)检查能否自启动001 /0 000 /0 111(有效状态)3.2.2串行序列信号检测器((1)状态图 0/11/0 0/0 0/0XX 0 1 0 111X X 1 1 11X X 0 1 110/01/0 1/0 0/1 (2)选择的触发器名称:选用三个CP 下降沿触发的边沿JK 触发器(3)输出方程:Y= nn Q Q X 01(4)串行序列检测器次态卡诺图:X 00 01 11 100 00 11 10 00101000000 Q 1n+1的卡诺图:X 00 01 11 100 0 1 1 0 1Q 0n+1的卡诺图:X 00 01 11 100 0 1 0 0 11由卡诺图得出状态方程为:1n 1+Q ==1n 0+Q = X nQ 0+(5)驱动方程0J = X1J =nQ 00K =1 1K =3.2.3 74193芯片仿真63进制减法计数器=1 1 1 1 1 1=4实验仪器4.1三位二进制减法器根据设计的需要可知所需的元器件如下所示(仿真软件)74LS112 三个 74LS08 三个74LS00 一个发光灯泡三支直流电源若干导线一个开关4.2串行序列检测器74LS112 两个 74LS08 两个74LS00 两个 74LS04 一个74LS151 一个发光灯泡三支直流电源若干导线一个开关4.3 74193芯片仿真63进制减法器计数74LS04 七个 74LS30 一个74LS193 两个计数器两个脉冲触发器直流电源5仿真结果分析5.1三位二进制同步减法计数器的电路原理图及结果图 5.1.1三位二进制同步减法计数器电路图5.1.2 111仿真结果图5.1.3 110仿真结果图5.1.4 101仿真结果图5.1.5 100仿真结果图5.1.6 011仿真结果图5.1.7 010仿真结果由上面的结果可以知道两个无效态100 ,000没有出现。

5.2串行序列信号检测器电路原理图及结果图 5.2.1串行序列信号检测器连线图图5.2.1 X=1 仿真结果(1)(2)(3)图4.2.2 (1)(2)(3)X=0仿真结果5.3 74193芯片仿真63进制减法计数器的电路原理图及结果(—)74193芯片仿真63进制减法器图4.3.1 74193芯片仿真63进制减法计数器电路图图4.3.2 仿真结果之一电路图6设计总结和体会1.设计总结经过实验可知,满足时序图的变化,且可以进行自启动。

实验过程中很顺利,没有出现问题。

2.心得体会本次课程设计从确定题目到完成报告通过自己动手操作Multisim软件,使我对此软件有了透彻的了解,能够熟练的操作和使用此软件进行仿真,画电路图等功能。

并且通过这次课程设计,加强了我们动手、思考和解决问题的能力。

在设计的过程遇到了不少的问题,但是最终都被自己解决了。

这种经历将是我终生受益。

7参考文献[1] 余孟尝《数字电子技术基础简明教程》高等教育出版社2007年12月[2] 吴翔,苏建峰《Multisim10&Ultiboard原理图仿真与PCB设计》电子工业出版社[3] 黄培根奚慧平主编浙江大学出版社 2005年2月第一版《Multisim 7&电子技术实验》[4] 杨志忠主编机械工业出版社 2008年7月第一版《电子技术课程设计》。