SRAM的工作原理——超简单

- 格式:pptx

- 大小:80.04 KB

- 文档页数:8

SRAM工作原理说明SRAM(Static Random-Access Memory,静态随机存取存储器)是一种常用的计算机存储器,其工作原理涉及到计算机存储系统的基本概念。

一、SRAM的基本结构SRAM的基本结构包括一个交叉反接晶体管(Cross-Coupled Transistor)和一个存储单元(Cell)。

交叉反接晶体管由两个P型晶体管和两个N型晶体管组成,它们之间通过交叉反接的方式连接在一起。

存储单元则由一个晶体管和两个电容组成,晶体管用于控制存储单元的读/写操作,电容用于存储数据。

二、SRAM的工作原理1.写入操作在写入操作时,首先将数据写入到存储单元的两个电容中。

具体来说,通过控制晶体管的栅极电压,将数据写入到电容中。

例如,如果要将数据“1”写入到存储单元中,可以将晶体管的栅极电压设置为高电平,这样电容中存储的电荷就会减少,表示数据“0”;如果要将数据“0”写入到存储单元中,可以将晶体管的栅极电压设置为低电平,这样电容中存储的电荷就会增加,表示数据“1”。

1.读取操作在读取操作时,首先将晶体管的栅极电压设置为中间值,这样存储单元中的电荷就会发生变化。

然后通过读取电容中的电荷变化来判断存储单元中的数据。

具体来说,如果读取到的电荷增加,说明存储单元中的数据为“1”;如果读取到的电荷减少,说明存储单元中的数据为“0”。

三、SRAM的特点1.速度快:由于SRAM的读写操作是通过晶体管和电容的电荷变化来实现的,因此读写速度非常快。

2.功耗低:由于SRAM的读写操作不需要外部电源供电,因此功耗非常低。

3.容量小:由于SRAM的每个存储单元都需要使用多个晶体管和电容,因此SRAM的容量相对较小。

4.可靠性高:由于SRAM的每个存储单元都有多个晶体管和电容进行备份,因此SRAM的可靠性非常高。

总之,SRAM是一种非常重要的计算机存储器,其工作原理涉及到计算机存储系统的基本概念。

sram的名词解释SRAM,即静态随机存储器(Static Random Access Memory),是一种常用的计算机内存储器。

与动态随机存储器(DRAM)相比,SRAM具有更高的工作速度和更低的能耗。

一、SRAM的结构和工作原理SRAM一般由六个晶体管组成,包括两个交叉连接的CMOS反相器(CMOS Inverter)和两个存储每位数据的传输门(Transmission Gate)。

SRAM的工作原理相对简单,当输入信号时钟引脚为高电平时,反相器的输出会被存储在另一个反相器中。

当时钟引脚为低电平时,SRAM的存储内容不会发生改变。

二、SRAM与DRAM的区别SRAM与DRAM是计算机内存中最为常见的两种技术,它们在结构和性能上存在明显区别。

1.结构区别:SRAM由多个晶体管构成,每个存储位使用4-6个晶体管来保持数据。

而DRAM则使用一对存储电容器(一个存储位一个电容器)来存储数据。

2.性能区别:SRAM具有更快的访问速度和更低的延迟,因为数据直接存储在晶体管中,而不需要刷新电容,这使得SRAM适用于高性能计算任务。

而DRAM需要周期性地刷新电容以保持数据的稳定性,因此访问速度较慢。

3.功耗区别:由于SRAM的存储位不需要刷新,因此相对较低的功耗是SRAM的优势之一。

而DRAM的刷新过程需要消耗额外的能量,导致功耗较高。

4.容量区别:由于SRAM每个存储位所需晶体管多,因此相对于DRAM来说,相同容量的SRAM所占面积更大,造成成本上的不利因素。

三、SRAM的应用领域SRAM由于其快速的访问速度和低能耗等优势,在许多领域得到了广泛的应用。

1.高性能计算SRAM常被用作高性能计算设备的缓存,用于存储经常使用的数据,以提高读写速度和整体性能。

2.嵌入式系统由于SRAM具有较低的延迟和功耗,它在嵌入式系统中得到了广泛的应用,例如智能手机、平板电脑和物联网设备等。

3.网络交换机与路由器SRAM在网络交换机和路由器中用于存储路由表、缓存数据包以及管理数据包转发等任务,提高了网络设备的运行效率。

sram的读写操作原理

SRAM,即静态随机存储器,是一种常见的计算机内存类型。

相比于动态随机存储器(DRAM),它具有更快的读写速度和更低的功耗。

SRAM的读写操作原理相对简单。

首先,SRAM是由多个存储单元组成的。

每个存储单元包含一个存储位(bit),即0或1。

存储单元通常被组织成一个矩阵形式,从而形成一个存储芯片。

每个存储单元都有一个地址,可以用来寻址存储器中的特定单元。

SRAM的写操作是这样的:当写入数据时,先把数据存储到一个内部的缓冲区中。

然后,通过地址线选择要写入的存储单元,并将已存放在缓冲区的数据写入选择的单元中。

在写入之前,SRAM会先读取存储单元中原来的数据,并使用写入的数据覆盖它。

这样,原来存储的数据将被新数据替换。

写操作的过程非常快速,只需要几个时钟周期即可完成。

SRAM的读操作是这样的:通过地址线选择要读取的存储单元,并将数据读出该单元。

读操作发生在几个时钟周期内,而且通常比写操作更快。

读操作同时也不会破坏存储单元中原来的数据。

总的来说,SRAM的读写操作原理相对简单而有效。

它具有快速的读写速度和低功耗等优点,成为了计算机内存中不可缺少的一部分。

sram的wsnm原理

SRAM (Static Random Access Memory) 是一种静态随机存取存

储器,而WSNM (Write-Static-Noise-Margin) 是指写入静态噪声

裕度。

SRAM的WSNM原理涉及到SRAM的写入操作和噪声裕度的概念。

首先,让我们了解一下SRAM的基本工作原理。

SRAM由一组存

储单元组成,每个存储单元由多个存储器单元组成。

每个存储单元

由一个双稳态触发器构成,可以存储一个比特的数据。

SRAM的写入

操作涉及将数据写入存储单元中,而WSNM则是指写入操作时存储单

元对噪声的容忍程度。

在SRAM中,写入操作涉及将数据写入存储单元。

在写入操作期间,存储单元的状态会发生变化,这可能会受到来自环境或电路本

身的噪声的影响。

WSNM原理涉及到存储单元在写入操作期间对噪声

的容忍程度。

高的WSNM意味着存储单元对噪声的容忍程度较高,写

入操作不太容易受到干扰。

而低的WSNM意味着存储单元对噪声的容

忍程度较低,写入操作更容易受到干扰。

为了提高SRAM的WSNM,可以采取一些设计和工艺上的措施。

例如,优化存储单元的设计,采用合适的电路布局和材料,以减少

对噪声的敏感度。

此外,还可以采用一些错误校正码或纠错码的技术来提高写入操作的可靠性,从而提高WSNM。

总的来说,SRAM的WSNM原理涉及到写入操作时存储单元对噪声的容忍程度。

通过优化设计和工艺,可以提高SRAM的WSNM,从而提高写入操作的可靠性和稳定性。

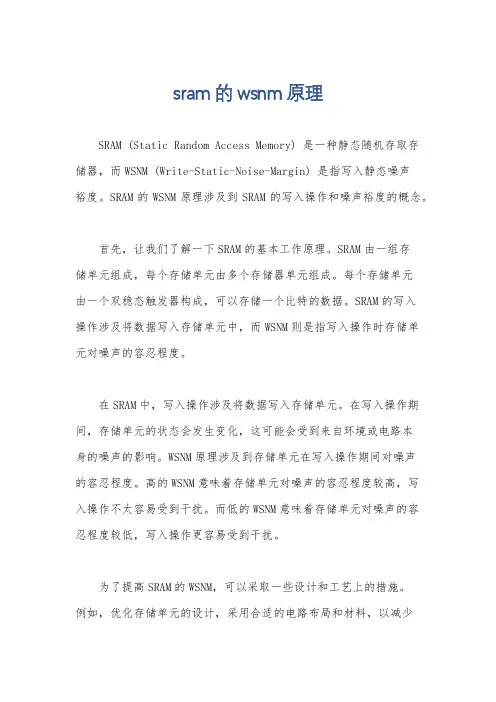

SRAM的工作原理:在静态存储器器件中,一位由6只晶体管组成,称为一个存储元,如图所示:N1和N2构成触发器,P1和P2分别作为Q1和Q2的负载电阻。

N1截止而N2导通时的状态称为"1"。

相反的状态称为"0"。

读出时,置选择线为高电平,使两个开关管导通,从读/写线输出原存的信息。

写入时,写入数据使读/写线呈相应电平(例如写"1"时,读/写线"1"为高电平,读/写线"0"为低电平),再使选择线为高电平,于是触发器被置为相应的状态(写"1"时,置为"1"状态,即N1截止N2导通)。

显然,无论存储元保存的信息是"1"还是"0",N1,N2,P1和P2,4只MOS管总有两只处于导通状态。

DRAM的工作原理和静态RAM一样,动态RAM也是由许多基本存储元按照行和列来组成的。

(1)3管DRAM的3管动态RAM的基本存储电路如右图所示。

在这个电路中,读选择线和写选择线是分开的,读数据线和写数据线也是分开的。

写操作时,写选择线为"1",所以Q1导通,要写入的数据通过Q1送到Q2的栅极,并通过栅极电容在一定时间内保持信息。

读操作时,先通过公用的预充电管Q4使读数据线上的分布电容CD充电,当读选择线为高电平有效时,Q3处于可导通的状态。

若原来存有"1",则Q2导通,读数据线的分布电容CD通过Q3、Q2放电,此时读得的信息为"0",正好和原存信息相反;若原存信息为"0",则Q3尽管具备导通条件,但因为Q2截止,所以,CD 上的电压保持不变,因而,读得的信息为"1"。

可见,对这样的存储电路,读得的信息和原来存入的信息正好相反,所以要通过读出放大器进行反相再送往数据总线。

sram的读写原理SRAM(Static Random Access Memory)是一种常用的存储器件,它采用静态存储原理,速度快,使用方便。

SRAM的读写原理可以通过以下几个步骤进行解释:1. 存储结构SRAM的存储单元由存储电路和访问电路组成。

存储电路用于存储数据,包括若干个存储元(bit),访问电路用于访问存储元,可以读取或写入数据。

SRAM存储单元通常由六个 MOSFET(金属氧化物半导体场效应晶体管)器件组成,其中有两个主要用于存储,称为存储器件(M1和M2),其余四个用于构建读写电路,称为开关器件(M3,M4,M5和M6)。

2. 读取操作在读取操作过程中,访问电路将地址信号(Address)输入到SRAM内,存储单元的地址译码器会根据地址信号找到存储单元的位置。

接着,由于被读取的存储元是静态存储的,因此不需要刷新电容,可以直接读取。

读取操作的主要流程如下:(1)地址输入(2)地址译码(3)选择要读取的存储元具体细节如下:(1)在地址线上输入地址信号,告诉存储器需要访问哪个存储元。

(2)存储单元的地址译码器解码地址信号,并向选中的存储器件(M1或M2)传递驱动脉冲。

(3)经过一系列放大和反相放大的信号处理,被选中的存储器件将数据信号(Data)输出到输出线上。

(4)访问电路接收到输出的数据信号,并通过接口输出到外部系统。

3. 写入操作在写入操作过程中,访问电路会先输入地址信号,找到所需要写入的存储单元,然后将写入数据输入到存储器件中进行存储。

(4)写入数据(3)经过一系列放大和反相放大的信号处理,输出到存储器件的数据信号被写入存储电路中,存储器件充当了一个带有反向反馈的放大器,将输入信号放大到存储器件的饱和区,实现存储的功能。

4. 总体结构在SRAM存储单元中,存储器件充当了数据存储的工具,访问电路充当了读写操作的调度和控制器。

存储单元根据地址信号选择存储器件,访问电路负责将数据信号写入或者读出。

sram工作原理

SRAM(静态随机存取存储器)是电子计算机中常见的一种存储器类型。

它的工作原理是利用MOSFET(金属-氧化-半导体场效应晶体管)的特性,通过MOSFET 的通断控制实现数据的存储和读取。

SRAM由许多存储单元组成,每个存储单元由一个MOSFET 和一个电容器组成。

MOSFET分为P 型和N 型两种,在SRAM 中使用的是NMOS(N型场效应晶体管)和PMOS(P型场效应晶体管)。

当NMOS 和PMOS 都处于通断状态时,存储单元将保存一个0 或1 的数值,这个数值会一直保持,直到下一次改变时才会更新。

SRAM的读写操作都是通过改变MOSFET 的通断状态实现的。

当要读取SRAM 中的数据时,访问电路会根据地址信号选择相应的存储单元,并将读取单元的MOSFET 通断状态改变,将存储单元中的数据传递到读取电路中。

当要写入数据时,访问电路会同样根据地址信号选择相应的存储单元,并将写入单元的MOSFET 通断状态改变,将输入数据存储到指定的存储单元中。

总之,SRAM 的主要特点是读写速度快、功耗低、数据保持时间长。

这使其成为高速缓存和寄存器等硬件设计中常见的组成部分。

sram 工作原理SRAM(Static Random Access Memory)是一种存储数据的集成电路,它具有快速、功耗低以及易于集成等优点。

SRAM的工作原理基于一种称为“双稳态”(bi-stable)的存储单元。

每个存储单元由一个多晶硅的存储器互补金属氧化物半导体场效应晶体管(CMOS)构成,其中包含两个互补的反相输出。

这两个反相输出通过两个输入端口写入数据并读取数据。

SRAM的核心是六个传输门(TO1~TO6),其中TO3和TO4是两个互补的传输门,负责输入数据;TO1, TO2, TO5和TO6是两个交叉反馈的传输门,负责输出数据。

SRAM的读写过程如下:1. 写操作:在写入数据之前,先将写使能信号(Write Enable)设置为高电平,以保证输入数据能够被写入。

将要写入的数据通过写数据端口输入到存储单元的传输门TO3和TO4上。

此时,TO1和TO2处于关闭状态,不传输数据。

通过传输门TO3和TO4,将输入数据写入存储单元。

写入完成后,将写使能信号设置为低电平,以防止误操作。

2. 读操作:在读取数据之前,先将读使能信号(Read Enable)设置为高电平,以使得读数据端口能够读取正确的数据。

通过读数据端口,将存储单元中的数据通过传输门TO1和TO2输出。

此时,TO3和TO4处于关闭状态,不影响输出数据。

读取完成后,将读使能信号设置为低电平。

通过以上的读写过程,SRAM能够实现高速的数据读写操作。

而且,由于SRAM采用了双稳态存储单元,不需要周期性地刷新数据,因此功耗相对较低。

此外,SRAM还可以方便地进行集成,因为存储单元不需要辅助电路,只需要相应的传输门就能够实现数据的读写。

sram的读写原理SRAM(Static Random Access Memory)是一种静态随机存取存储器,它的读写原理是基于存储单元的电容和晶体管的开关状态。

SRAM的读写速度非常快,因此被广泛应用于高速缓存和其他需要快速访问的应用中。

SRAM的存储单元由一个电容和一个晶体管组成。

电容存储了一个比特的信息,而晶体管则用于控制电容的读写操作。

当晶体管处于导通状态时,电容的电荷可以被读取或写入。

当晶体管处于截止状态时,电容的电荷将被保持,以便在下一次读取时使用。

SRAM的读操作非常简单。

当需要读取存储单元中的数据时,控制电路会将地址信号发送到SRAM芯片中。

地址信号将被解码,以确定要读取的存储单元。

一旦存储单元被确定,控制电路将向该单元的晶体管发送一个读取信号。

晶体管将变为导通状态,允许电容中的电荷流入读取电路中。

读取电路将电荷转换为数字信号,并将其发送到CPU或其他设备中。

SRAM的写操作也很简单。

当需要向存储单元中写入数据时,控制电路将地址信号发送到SRAM芯片中。

地址信号将被解码,以确定要写入的存储单元。

一旦存储单元被确定,控制电路将向该单元的晶体管发送一个写入信号。

晶体管将变为导通状态,允许电容中的电荷流入或流出。

写入电路将数字信号转换为电荷,并将其发送到电容中。

一旦电容中的电荷被改变,晶体管将被关闭,以保持电容中的电荷。

SRAM的读写原理是基于存储单元的电容和晶体管的开关状态。

读取操作将电容中的电荷转换为数字信号,而写入操作将数字信号转换为电荷,并将其存储在电容中。

由于SRAM的读写速度非常快,因此它被广泛应用于高速缓存和其他需要快速访问的应用中。

SRAM鐗圭偣鍙婂伐浣滃師鐞?SRAM鏄嫳鏂嘢tatic RAM鐨勭缉鍐欙紝瀹冩槸涓€绉嶅叿鏈夐潤姝㈠瓨鍙栧姛鑳界殑鍐呭瓨锛屼笉闇€瑕佸埛鏂扮數璺嵆鑳戒繚瀛樺畠鍐呴儴瀛樺偍鐨勬暟鎹? 鍩烘湰绠€浠? SRAM涓嶉渶瑕佸埛鏂扮數璺嵆鑳戒繚瀛樺畠鍐呴儴瀛樺偍鐨勬暟鎹€傝€孌RAM(Dynamic Random Access Memory)姣忛殧涓€娈垫椂闂达紝瑕佸埛鏂板厖鐢典竴娆★紝鍚﹀垯鍐呴儴鐨勬暟鎹嵆浼氭秷澶憋紝鍥犳SRAM鍏锋湁杈冮珮鐨勬€ц兘锛屼絾鏄疭RAM涔熸湁瀹冪殑缂虹偣锛屽嵆瀹冪殑闆嗘垚搴﹁緝浣庯紝鐩稿悓瀹归噺鐨凞RAM鍐呭瓨鍙互璁捐涓鸿緝灏忕殑浣撶Н锛屼絾鏄疭RAM鍗撮渶瑕佸緢澶х殑浣撶Н锛屼笖鍔熻€楄緝澶с€傛墍浠ュ湪涓绘澘涓奡RAM瀛樺偍鍣ㄨ鍗犵敤涓€閮ㄥ垎闈㈢Н銆? 涓昏瑙勬牸涓€绉嶆槸缃簬CPU涓庝富瀛橀棿鐨勯珮閫熺紦瀛橈紝瀹冩湁涓ょ瑙勬牸锛氫竴绉嶆槸鍥哄畾鍦ㄤ富鏉夸笂鐨勯珮閫熺紦瀛?Cache Memory);鍙︿竴绉嶆槸鎻掑湪鍗℃Ы涓婄殑COAST(Cache On A Stick)鎵╁厖鐢ㄧ殑楂橀€熺紦瀛橈紝鍙﹀鍦–MOS鑺墖1468l8鐨勭數璺噷锛屽畠鐨勫唴閮ㄤ篃鏈夎緝灏忓閲忕殑128瀛楄妭SRAM锛屽瓨鍌ㄦ垜浠墍璁剧疆鐨勯厤缃暟鎹€傝繕鏈変负浜嗗姞閫烠PU鍐呴儴鏁版嵁鐨勪紶閫侊紝鑷?0486CPU璧凤紝鍦–PU鐨勫唴閮ㄤ篃璁捐鏈夐珮閫熺紦瀛橈紝鏁呭湪Pentium CPU灏辨湁鎵€璋撶殑L1 Cache(涓€绾ч珮閫熺紦瀛?鍜孡2Cache(浜岀骇楂橀€熺紦瀛?鐨勫悕璇嶏紝涓€鑸琇1 Cache鏄唴寤哄湪CPU鐨勫唴閮紝L2 Cache鏄璁″湪CPU鐨勫閮紝浣嗘槸Pentium Pro鎶奓1鍜孡2 Cache鍚屾椂璁捐鍦–PU鐨勫唴閮紝鏁匬entium Pro鐨勪綋绉緝澶с€傛渶鏂扮殑Pentium II鍙堟妸L2 Cache绉昏嚦CPU鍐呮牳涔嬪鐨勯粦鐩掑瓙閲屻€係RAM鏄剧劧閫熷害蹇紝涓嶉渶瑕佸埛鏂扮殑鎿嶄綔锛屼絾鏄篃鏈夊彟澶栫殑缂虹偣锛屽氨鏄环鏍奸珮锛屼綋绉ぇ锛屾墍浠ュ湪涓绘澘涓婅繕涓嶈兘浣滀负鐢ㄩ噺杈冨ぇ鐨勪富瀛樸€? 鍩烘湰鐗圭偣鐜板皢瀹冪殑鐗圭偣褰掔撼濡備笅锛? 鈼庝紭鐐癸紝閫熷害蹇紝涓嶅繀閰嶅悎鍐呭瓨鍒锋柊鐢佃矾锛屽彲鎻愰珮鏁翠綋鐨勫伐浣滄晥鐜囥€? 鈼庣己鐐癸紝闆嗘垚搴︿綆锛屽姛鑰楄緝澶э紝鐩稿悓鐨勫閲忎綋绉緝澶э紝鑰屼笖浠锋牸杈冮珮锛屽皯閲忕敤浜庡叧閿€х郴缁熶互鎻愰珮鏁堢巼銆? 鈼嶴RAM浣跨敤鐨勭郴缁燂細鈼婥PU涓庝富瀛樹箣闂寸殑楂橀€熺紦瀛樸€? 鈼婥PU鍐呴儴鐨凩1/L2鎴栧閮ㄧ殑L2楂橀€熺紦瀛樸€? 鈼婥PU澶栭儴鎵╁厖鐢ㄧ殑COAST楂橀€熺紦瀛樸€? 鈼婥MOS 146818鑺墖(RT&CMOS SRAM)銆? 涓昏鐢ㄩ€?SRAM涓昏鐢ㄤ簬浜岀骇楂橀€熺紦瀛?Level2 C ache)銆傚畠鍒╃敤鏅朵綋绠℃潵瀛樺偍鏁版嵁銆備笌DRAM鐩告瘮锛孲RAM鐨勯€熷害蹇紝浣嗗湪鐩稿悓闈㈢Н涓璖RAM鐨勫閲忚姣斿叾浠栫被鍨嬬殑鍐呭瓨灏忋€?SRAMSRAM鐨勯€熷害蹇絾鏄傝吹锛屼竴鑸敤灏忓閲忕殑SRAM浣滀负鏇撮珮閫烠PU鍜岃緝浣庨€烡RAM 涔嬮棿鐨勭紦瀛?cache).SRAM涔熸湁璁稿绉嶏紝濡侫syncSRAM (Asynchronous SRAM,寮傛SRAM)銆丼ync SRAM (Synchronous SRAM,鍚屾SRAM)銆丳BSRAM (Pipelined Burst SRAM, 娴佹按寮忕獊鍙慡RAM)锛岃繕鏈塈NTEL娌℃湁鍏竷缁嗚妭鐨凜SRAM绛夈€? 鍩烘湰鐨凷RAM鐨勬灦鏋勶紝SRAM涓€鑸彲鍒嗕负浜斿ぇ閮ㄥ垎:瀛樺偍鍗曞厓闃靛垪(core cells array)锛岃/鍒楀湴鍧€璇戠爜鍣?decode)锛岀伒鏁忔斁澶у櫒(Sense Amplifier)锛屾帶鍒剁數璺?control circuit)锛岀紦鍐?椹卞姩鐢佃矾(FFIO)銆? SRAM鏄潤鎬佸瓨鍌ㄦ柟寮忥紝浠ュ弻绋虫€佺數璺綔涓哄瓨鍌ㄥ崟鍏冿紝SRAM涓嶈薄DRAM涓€鏍烽渶瑕佷笉鏂埛鏂帮紝鑰屼笖宸ヤ綔閫熷害杈冨揩锛屼絾鐢变簬瀛樺偍鍗曞厓鍣ㄤ欢杈冨锛岄泦鎴愬害涓嶅お楂橈紝鍔熻€椾篃杈冨ぇ銆? 宸ヤ綔鍘熺悊鍥? 鍏鍗曞厓鐢佃矾鍥維RAM鐨勫伐浣滃師鐞嗭細鍋囪鍑嗗寰€鍥?鐨?T瀛樺偍鍗曞厓鍐欏叆“1”锛屽厛灏嗘煇涓€缁勫湴鍧€鍊艰緭鍏ュ埌琛屻€佸垪璇戠爜鍣ㄤ腑锛岄€変腑鐗瑰畾鐨勫崟鍏冿紝鐒跺悗浣垮啓浣胯兘淇″彿WE鏈夋晥锛屽皢瑕佸啓鍏ョ殑鏁版嵁“1”閫氳繃鍐欏叆鐢佃矾鍙樻垚“1”鍜?ldquo;0”鍚庡垎鍒姞鍒伴€変腑鍗曞厓鐨勪袱鏉′綅绾緽L,BLB涓婏紝姝ゆ椂閫変腑鍗曞厓鐨刉L=1锛屾櫠浣撶N0,N5鎵撳紑锛屾妸BL,BLB涓婄殑淇″彿鍒嗗埆閫佸埌Q,QB鐐癸紝浠庤€屼娇Q=1锛孮B=0锛岃繖鏍锋暟鎹?ldquo;1”灏辫閿佸瓨鍦ㄦ櫠浣撶P2,P3,N3,N4鏋勬垚鐨勯攣瀛樺櫒涓€傚啓鍏ユ暟鎹?ldquo;0”鐨勮繃绋嬬被浼笺€? SRAM鐨勮杩囩▼浠ヨ“1”涓轰緥锛岄€氳繃璇戠爜鍣ㄩ€変腑鏌愬垪浣嶇嚎瀵笲L,BLB杩涜棰勫厖鐢靛埌鐢垫簮鐢靛帇VDD锛岄鍏呯數缁撴潫鍚庯紝鍐嶉€氳繃琛岃瘧鐮佸櫒閫変腑鏌愯锛屽垯鏌愪竴瀛樺偍鍗曞厓琚€変腑锛岀敱浜庡叾涓瓨鏀剧殑鏄?ldquo;1”锛屽垯WL=1銆丵=1銆丵B=0銆傛櫠浣撶N4銆丯5瀵奸€氾紝鏈夌數娴佺粡N4銆丯5鍒板湴锛屼粠鑰屼娇BLB鐢典綅涓嬮檷锛孊L銆丅LB闂寸數浣嶄骇鐢熺數鍘嬪樊锛屽綋鐢靛帇宸揪鍒颁竴瀹氬€煎悗鎵撳紑鐏垫晱搴︽斁澶у櫒锛屽鐢靛帇杩涜鏀惧ぇ锛屽啀閫佸埌杈撳嚭鐢佃矾锛岃鍑烘暟鎹€? 缁撴瀯鍘熺悊 SRAM ( Static RAM)锛屽嵆闈欐€丷AM.瀹冧篃鐢辨櫠浣撶缁勬垚銆傛帴閫氫唬琛?锛屾柇寮€琛ㄧず0锛屽苟涓旂姸鎬佷細淇濇寔鍒版帴鏀朵簡涓€涓敼鍙樹俊鍙蜂负姝€傝繖浜涙櫠浣撶涓嶉渶瑕佸埛鏂帮紝浣嗗仠鏈烘垨鏂數鏃讹紝瀹冧滑鍚孌RAM涓€鏍凤紝浼氫涪鎺変俊鎭€係RAM鐨勯€熷害闈炲父蹇紝閫氬父鑳戒互20ns鎴栨洿蹇殑閫熷害宸ヤ綔銆備竴涓狣RAM瀛樺偍鍗曞厓浠呴渶涓€涓櫠浣撶鍜屼竴涓皬鐢靛.鑰屾瘡涓猄RAM鍗曞厓闇€瑕佸洓鍒板叚涓櫠浣撶鍜屽叾浠栭浂浠躲€傛墍浠ワ紝闄や簡浠锋牸杈冭吹澶栵紝SRAM鑺墖鍦ㄥ褰笂涔熻緝澶э紝涓嶥RAM鐩告瘮瑕佸崰鐢ㄦ洿澶氱殑绌洪棿銆傜敱浜庡褰㈠拰鐢垫皵涓婄殑宸埆锛孲RAM鍜孌RAM鏄笉鑳戒簰鎹㈢殑銆? SRAM鐨勯珮閫熷拰闈欐€佺壒鎬т娇瀹冧滑閫氬父琚敤鏉ヤ綔涓篊ache瀛樺偍鍣ㄣ€傝绠楁満鐨勪富鏉夸笂閮芥湁Cache鎻掑骇銆係RAM涓嬪浘鎵€绀虹殑鏄竴涓猄RAM鐨勭粨鏋勬鍥俱€? 鐢变笂鍥剧湅鍑篠RAM涓€鑸敱浜斿ぇ閮ㄥ垎缁勬垚锛屽嵆瀛樺偍鍗曞厓闃靛垪銆佸湴鍧€璇戠爜鍣?鍖呮嫭琛岃瘧鐮佸櫒鍜屽垪璇戠爜鍣?銆佺伒鏁忔斁鐏櫒銆佹帶鍒剁數璺拰缂撳啿/椹卞姩鐢佃矾銆傚湪鍥句腑锛孉0-Am-1涓哄湴鍧€杈撳叆绔紝CSB.WEB鍜孫EB涓烘帶鍒剁锛屾帶鍒惰鍐欐搷浣滐紝涓轰綆鐢靛钩鏈夋晥锛?100-11ON-1涓烘暟鎹緭鍏ヨ緭鍑虹銆傚瓨鍌ㄩ樀鍒椾腑鐨勬瘡涓瓨鍌ㄥ崟鍏冮兘涓庡叾瀹冨崟鍏冨湪琛屽拰鍒椾笂鍏变韩鐢靛杩炴帴锛屽叾涓按骞虫柟鍚戠殑杩炵嚎绉颁负“瀛楃嚎”锛岃€屽瀭鐩存柟鍚戠殑鏁版嵁娴佸叆鍜屾祦鍑哄瓨鍌ㄥ崟鍏冪殑杩炵嚎绉颁负“浣嶇嚎”銆傞€氳繃杈撳叆鐨勫湴鍧€鍙€夋嫨鐗瑰畾鐨勫瓧绾垮拰浣嶇嚎锛屽瓧绾垮拰浣嶇嚎鐨勪氦鍙夊灏辨槸琚€変腑鐨勫瓨鍌ㄥ崟鍏冿紝姣忎竴涓瓨鍌ㄥ崟鍏冮兘鏄寜杩欑鏂规硶琚敮涓€閫変腑锛岀劧鍚庡啀瀵瑰叾杩涜璇诲啓鎿嶄綔銆傛湁鐨勫瓨鍌ㄥ櫒璁捐鎴愬浣嶆暟鎹4浣嶆垨8浣嶇瓑鍚屾椂杈撳叆鍜岃緭鍑猴紝杩欐牱鐨勮瘽锛屽氨浼氬悓鏃舵湁4涓垨8涓瓨鍌ㄥ崟鍏冩寜涓婅堪鏂规硶琚€変腑杩涜璇诲啓鎿嶄綔銆? 鍦⊿RAM 涓紝鎺掓垚鐭╅樀褰㈠紡鐨勫瓨鍌ㄥ崟鍏冮樀鍒楃殑鍛ㄥ洿鏄瘧鐮佸櫒鍜屼笌澶栭儴淇″彿鐨勬帴鍙g數璺€傚瓨鍌ㄥ崟鍏冮樀鍒楅€氬父閲囩敤姝f柟褰㈡垨鐭╅樀鐨勫舰寮忥紝浠ュ噺灏戞暣涓姱鐗囬潰绉苟鏈夊埄浜庢暟鎹殑瀛樺彇銆備互涓€涓瓨鍌ㄥ閲忎负4K浣嶇殑SRAM涓轰緥锛屽叡闇€12鏉″湴鍧€绾挎潵淇濊瘉姣忎竴涓瓨鍌ㄥ崟鍏冮兘鑳借閫変腑(212 =-4096)銆傚鏋滃瓨鍌ㄥ崟鍏冮樀鍒楄鎺掑垪鎴愬彧鍖呭惈涓€鍒楃殑闀挎潯褰紝鍒欓渶瑕佷竴涓?2/4K浣嶇殑璇戠爜鍣紝浣嗗鏋滄帓鍒楁垚鍖呭惈64琛屽拰64鍒楃殑姝f柟褰紝杩欐椂鍒欏彧闇€涓€涓?/64浣嶇殑琛岃瘧鐮佸櫒鍜屼竴涓?/64浣嶇殑鍒楄瘧鐮佸櫒锛岃銆佸垪璇戠爜鍣ㄥ彲鍒嗗埆鎺掑垪鍦ㄥ瓨鍌ㄥ崟鍏冮樀鍒楃殑涓よ竟锛?4琛屽拰64鍒楀叡鏈?096涓氦鍙夌偣锛屾瘡涓€涓偣灏卞搴斾竴涓瓨鍌ㄤ綅銆傚洜姝わ紝灏嗗瓨鍌ㄥ崟鍏冩帓鍒楁垚姝f柟褰㈡瘮鎺掑垪鎴愪竴鍒楃殑闀挎潯褰㈣澶уぇ鍦板噺灏戞暣涓姱鐗囧湴闈㈢Н銆傚瓨鍌ㄥ崟鍏冩帓鍒楁垚闀挎潯褰㈤櫎浜嗗舰鐘跺寮傚拰闈㈢Н澶т互澶栵紝杩樻湁涓€涓己鐐癸紝閭e氨鏄帓鍦ㄥ垪鐨勪笂閮ㄧ殑瀛樺偍鍗曞厓涓庢暟鎹緭鍏?杈撳嚭绔殑杩炵嚎灏变細鍙樺緱寰堥暱锛岀壒鍒槸瀵逛簬瀹归噺姣旇緝澶у緱瀛樺偍鍣ㄦ潵璇达紝鎯呭喌灏辨洿涓轰弗閲嶏紝鑰岃繛绾跨殑寤惰繜鑷冲皯鏄笌瀹冪殑闀垮害鎴愮嚎鎬у叧绯伙紝杩炵嚎瓒婇暱锛岀嚎涓婄殑寤惰繜灏辫秺澶э紝鎵€浠ュ氨浼氬鑷磋鍐欓€熷害鐨勯檷浣庡拰涓嶅悓瀛樺偍鍗曞厓杩炵嚎寤惰繜鐨勪笉涓€鑷存€э紝杩欎簺閮芥槸鍦ㄨ璁′腑闇€瑕侀伩鍏嶇殑銆。

sram和dram的工作原理(一)SRAM和DRAM的工作原理什么是SRAM和DRAMSRAM和DRAM都是计算机内存的类型,它们分别表示“静态随机存储器”和“动态随机存储器”。

SRAM和DRAM的最大不同在于它们如何存储数据和访问数据。

SRAM的工作原理SRAM使用稳定的电流来存储数据,需要更少的电能才能维持存储数据。

SRAM的单元非常简单,由6个晶体管组成,这6个晶体管可以以一定的规律连接起来来形成一个存储单位。

SRAM存储的数据可以非常快地被访问,这是因为它的工作方式更加高效。

不需要预充电或刷新,SRAM可以立即访问和使用,这使得SRAM非常适合处理高速计算和处理。

DRAM的工作原理DRAM使用电容来存储数据,需要更多的电能来维持存储的状态。

由于DRAM使用电容来存储数据,因此需要定期刷新它们以防止丢失数据。

DRAM内的电容需要定期预充电,以确保它们保持在正确的状态并能够快速读取或写入。

DRAM的单元较为复杂,由至少一个晶体管和一个电容器组成,这使得DRAM的成本比SRAM更低。

SRAM和DRAM的优点和缺点SRAM和DRAM都有各自的优点和缺点。

SRAM:•速度快,响应速度高•不需要刷新,不会产生”闪屏”等现象•需要更少的电能来维持存储数据•SRAM的单元较为简单,更加容易设计DRAM:•容量大,成本更低•更容易存储大量数据•每个单元需要更少的面积,可以更高效地使用芯片空间总的来说,SRAM更适用于需要快速、可靠计算和处理的情况,而DRAM更适用于需要更大的存储容量和较低的成本的情况。

感谢您阅读本文!SRAM和DRAM的应用领域SRAM和DRAM都被广泛地使用在计算机内存中,SRAM通常用来作为CPU 缓存。

由于它的快速响应速度,能够有效地缓存处理器需要的数据,并且可以减少程序执行时间。

DRAM则通常用于主存或虚拟内存中,它的存储能力强,能够存储大量数据,但响应速度较慢,需要较长的等待时间。

sram 原理SRAM原理及其应用SRAM(Static Random Access Memory)是一种常见的存储器类型,它具有快速读写速度和易于集成的特点,被广泛应用于计算机内存、高速缓存和其他存储系统中。

本文将介绍SRAM的工作原理以及其在现代电子设备中的应用。

一、SRAM的工作原理SRAM是一种基于触发器的存储器,它由一组存储单元组成,每个存储单元由一个触发器和一对传输门组成。

触发器是由多个逻辑门构成的电路,用于存储一个比特的数据。

SRAM的工作原理可以简单概括为以下几个步骤:1. 写操作:当写入数据时,写入信号被传输到SRAM的写入线路上。

写入线路将写入信号传递给存储单元的传输门,使得数据能够被写入触发器中。

2. 读操作:当需要读取数据时,读取信号被传输到SRAM的读取线路上。

读取线路将读取信号传递给存储单元的传输门,使得触发器中的数据能够被传输到输出线路上。

3. 刷新操作:由于SRAM是一种静态存储器,需要定期进行刷新操作以保持数据的稳定性。

刷新操作会将存储单元中的数据重新写入触发器,以防止数据丢失。

二、SRAM的应用1. 计算机内存:SRAM被广泛应用于计算机的主存储器中。

由于SRAM具有快速的读写速度和较低的功耗,它能够提供高性能的数据存取能力,满足计算机对于快速数据交换的需求。

2. 高速缓存:SRAM也被用作处理器的高速缓存。

高速缓存是位于处理器和主存储器之间的一层存储器,用于加速数据的访问。

SRAM作为高速缓存的存储介质,能够提供更快的数据读取速度,减少处理器对主存储器的访问时间。

3. 嵌入式系统:由于SRAM具有较小的面积和较低的功耗,它在嵌入式系统中得到广泛应用。

嵌入式系统通常具有有限的资源和功耗限制,SRAM能够满足这些要求,并提供高效的数据存储和处理能力。

4. 图形处理器:SRAM也被广泛应用于图形处理器(GPU)中。

GPU需要大量的存储器来存储图像数据和计算结果,SRAM能够提供快速的数据读写能力,满足GPU对于高带宽和低延迟的存储需求。

SRAM的工作原理——超简单SRAM(静态随机访问存储器)是一种常见的存储器类型,用于在计算机中存储数据。

它是一种容量相对较小但工作速度快的存储器,常用于高速缓存和寄存器等需要快速访问的场景。

SRAM的工作原理相对复杂,但可以用一个简单的流程来概括其工作过程。

SRAM由一组存储单元组成,每个存储单元通常由一个双稳态触发器构成,以保持数据的稳定性。

每个存储单元可存储一个比特(0或1),并具有一个地址来标识其位置。

SRAM中的所有存储单元都连接到一个控制器,以便读取和写入数据。

1.写入地址:在进行读取操作之前,需要先指定要读取的存储单元的地址。

控制器将地址信号发送到SRAM的地址输入端口。

2.读取操作:读取操作开始后,控制器将控制信号发送到SRAM中的所有存储单元。

这些控制信号包括读使能信号和读取时钟信号。

3.存储单元响应:当读使能信号和读取时钟信号到达存储单元时,它们会激活存储单元并产生输出。

输出将通过输出端口发送到数据总线上。

接下来,我们来看看写入操作的工作原理:1.写入地址:与读取操作类似,写入操作之前需要指定要写入的存储单元的地址。

控制器将地址信号发送到SRAM的地址输入端口。

2.数据输入:将要写入的数据发送到数据输入端口。

这些数据将通过数据总线传输到SRAM。

3.写入操作:写入操作开始后,控制器将控制信号发送到SRAM中的所有存储单元。

这些控制信号包括写使能信号和写入时钟信号。

4.存储单元记录:当写使能信号和写入时钟信号到达存储单元时,存储单元将记录输入的数据,并将其存储在内部存储电路中。

需要注意的是,SRAM在写入操作完成后可以立即进行读取操作,而无需等待存储单元稳定。

这是因为SRAM是一种静态存储器,可以保持存储的数据不变,而无需刷新操作。

总结起来,SRAM的工作原理包括读取和写入两个主要阶段。

在读取操作中,控制器发送地址和读取信号到SRAM,存储单元响应并通过输出端口发送数据。

在写入操作中,控制器发送地址、数据和写入信号到SRAM,存储单元记录输入的数据。

SRAM的工作原理——超简单SRAM(Static Random Access Memory)是一种静态随机存储器,用于在计算机中存储和访问数据。

与动态随机存储器(DRAM)相比,SRAM 具有更快的速度和更高的可靠性,但代价是更高的成本和功耗。

SRAM由一组存储单元组成,每个存储单元可以存储一个位(1或0)。

SRAM的工作原理可以简单概括为读和写两个过程。

在读取数据时,首先需要将要读取的地址传送给SRAM芯片。

这个地址用来确定要读取的存储单元。

然后,在SRAM芯片的内部,数据从存储单元中读取出来并通过输出线路传送给CPU或其他设备。

在写入数据时,首先将要写入的地址和数据传送给SRAM芯片。

然后,SRAM芯片将数据写入到对应的存储单元中。

SRAM的核心是一个存储单元,由一个触发器(flip-flop)和一些传输门(transistor)组成。

存储单元有两个稳定的状态:高电位(1)和低电位(0)。

SRAM使用触发器存储数据,它是一种双稳态设备,可以保持在两种状态之一、触发器的状态是由输入控制信号设置的,当控制信号发生改变时,触发器将保持在新的状态。

为了实现存储单元的读取和写入操作,SRAM使用传输门来控制数据的流动。

传输门是根据特定的控制信号来开启或关闭的开关。

对于读取操作,传输门将存储单元的数据传送到输出线路上。

对于写入操作,传输门将输入数据传输到存储单元。

控制信号是由地址线和读/写控制信号生成的。

当发生读取操作时,地址信号被传送到SRAM芯片。

地址信号被解码,用于选择要读取的存储单元。

读/写控制信号将传输门设置为打开状态,使得存储单元中的数据能够通过输出线路发送给CPU或其他设备。

当发生写入操作时,地址和数据信号被传送到SRAM芯片。

地址信号用于选择要写入的存储单元。

读/写控制信号将传输门设置为打开状态,将输入数据传输到存储单元中,覆盖原有的数据。

SRAM的特点是速度快、可靠性高。

由于SRAM使用触发器存储数据,不需要周期性的刷新操作,所以速度比DRAM更快。

sram工作原理clka clkb

SRAM(Static Random-Access Memory,靜態隨機存取記憶體)的工作原理可以簡單描述為以下兩點:

1. 存儲數據:SRAM使用六個TTL(Transistor-Transistor Logic,晶體管晶體管邏輯)儲存每一位數據。

這六個TTL是

成對存在,即兩個TTL組成一對,對稱地放置在晶體管閘極

和晶體管集電極之間。

這樣的結構形成一個電容記憶元件(DRAM需要一個電容元件)。

每一對TTL只有在位線(Word Line)和兩個位線駕動線上出現相位出現特定電位時,才會將對稱的TTL輸出電位儲存起來。

比較正確的說法是SRAM可以說是直接由NLDM(Negative Level Dynamic Memory)演變而來的。

2. 進行讀寫操作:SRAM通過對「位儲存元件」放電或充電

來進行讀寫操作。

當「位線駕動線」正確輸出一種「寫入信號」時,SRAM將把「位線駕動線」所輸出的信號儲存起來;當「位線駕動線」正確輸出另一種「讀取信號」時,SRAM將

通過位線向外部輸出所儲存的數據。

這種從位線向存儲電界駕動的方式稱為「位元組」(Word-Line)方式。

其中,兩位元

組分為「文碼位元組」(Word-Line)和「字碼位元組」(Bit-Line)。

簡單來說,SRAM在儲存數據方面使用TTL電路,通過位線

和位線駕動線的電位控制將數據儲存或輸出。