FPGA开发板

- 格式:doc

- 大小:153.50 KB

- 文档页数:3

Gowin FPGA开发板RISCV编程快速应用手册IPUG546-1.1,2022-11-11版权所有© 2022广东高云半导体科技股份有限公司、Gowin以及高云均为广东高云半导体科技股份有限公司注册商标, 本手册中提到的其他任何商标,其所有权利属其拥有者所有。

未经本公司书面许可,任何单位和个人都不得擅自摘抄、复制、翻译本文档内容的部分或全部,并不得以任何形式传播。

免责声明本文档并未授予任何知识产权的许可,并未以明示或暗示,或以禁止发言或其它方式授予任何知识产权许可。

除高云半导体在其产品的销售条款和条件中声明的责任之外,高云半导体概不承担任何法律或非法律责任。

高云半导体对高云半导体产品的销售和/或使用不作任何明示或暗示的担保,包括对产品的特定用途适用性、适销性或对任何专利权、版权或其它知识产权的侵权责任等,均不作担保。

高云半导体对文档中包含的文字、图片及其它内容的准确性和完整性不承担任何法律或非法律责任,高云半导体保留修改文档中任何内容的权利,恕不另行通知。

高云半导体不承诺对这些文档进行适时的更新。

版本信息目录目录 (i)图目录 (ii)表目录 (iii)1 前言 (1)1.1 AE250简介 (1)1.2 准备工作 (2)1.3 开发/调试步骤 (3)2 Debug Cable连接说明 (4)3 RDS使用说明 (6)3.1 RDS安装 (6)3.2 新建工程 (6)3.3 导入/导出工程 (8)3.4 下载程序到Flash (10)3.5 片上调试 (13)3.6 RDS内置的串口终端使用方法 (15)4 参考设计 (16)4.1 工程代码 (16)4.2 参考设计 (17)图目录图1-1 AE250结构框图 (1)图1-2开发/调试系统结构框图 (2)图2-1 AICE-MINI+ Debug Cable及其引脚示意图 (4)图3-1新建工程 (7)图3-2 Import/Export a Project (8)图3-3导入工程界面 (9)图3-4导出工程界面 (9)图3-5设置System Reset Vector Default (10)图3-6设置SPI1 Configuration (11)图3-7设置MSPI接口为普通IO (12)图3-8 ae250.sag中bootloader参数设置 (12)图3-9 Debug参数设置界面 (13)图3-10 Debug按钮介绍 (14)图3-11汇编指令代码窗口 (14)图3-12 RDS内置串口终端 (15)表目录表目录表2-1 AICE-MINI+ Debug Cable引脚定义 (4)表3-1 SPI1接口物理约束 (11)1 前言 1.1 AE250简介1前言1.1AE250简介AE250是一个32位RISC-V MCU系统,其主要结构如图1-1所示。

Spartan-3E XC3S250E-4VQ100实验板用户使用说明第一章概述1、实验板资源Xilinx器件:Spartan-3E XC3S250E-4VQ100,XCF02SV020C(Platform Flash)时钟:50MHz晶体时钟振荡器;电源:USB接口供电,三路电源管理IC;接口:JTAG下载接口,PS/2,RS-232串行接口,4个按键开关,八个LED灯,4*4矩阵键盘,蜂鸣器;显示:VGA显示端口,4位七段数码管;存储器:EEPROM;图1-1 实验板资源示意图图1-2 实验板2、Spartan-3E XC3S250E-4VQ100简介主芯片:Spartan-3E XC3S250E-4VQ100CLB资源:•Rows: 34•Columns: 26•Total CLBs: 612Slice资源:•Total Slices: 2,448存储资源:•Distributed RAM Bits: 38K•Block RAM Bits: 216K时钟管理器:•DCM: 4逻辑单元:•System Gates: 250K•Equivalent Logic Cells: 5,508乘法器:•Dedicated Multipliers: 12I/O:•Total I/O:100•User I/O: 683、电源管理模块输入:5V DC,由USB接口提供;输出:3.3V DC,2.5V DC,1.2V DC。

图1-3 电源管理电路•VDD=3.3V:VDD引脚为I/O引脚,为I/O提供驱动电压。

•V AUX=2.5V:为JTAG模块和程序下载配置模块供电•VINT=1.2V:为内部调压器供电4、时钟/复位模块图1-4 时钟电路系统时钟由外部晶振提供,频率为50MHz,时钟的输入直接连到Bank0的输入全局缓冲I/O,时钟输入也可以连接到相应的DCM。

FPGA的Bank0的I/O的电压是由P82和P97供给的,板上已经将这两个引脚连接到3.3V,晶振可以达到预期的工作效果。

basys3开发板例程

Basys3开发板是一款FPGA开发板,可用于学习和开发数字电路和嵌入式系统。

以下是一些Basys3开发板的例程:

1. LED闪烁:通过FPGA控制Basys3开发板上的LED灯进行闪烁操作。

这是最基本的例程,用于检查Basys3开发板是否正常工作以及了解FPGA的开发流程。

2. 七段数码管显示:通过FPGA控制Basys3开发板上的七段数码管显示数字。

可以实现数字计数、时钟显示等功能。

3. 按键检测:通过FPGA检测Basys3开发板上的按键按下事件,并在数码管或LED上显示相应的结果。

可以用于制作简单的交互式应用程序。

4. 蜂鸣器控制:通过FPGA控制Basys3开发板上的蜂鸣器发出不同的声音。

可以实现简单的音乐播放、警报系统等功能。

5. VGA显示:通过FPGA控制Basys3开发板上的VGA接口,实现在显示器上显示图形和文字。

可以实现简单的游戏、图形界面等应用。

这些例程可以帮助学习者逐步了解FPGA的开发流程和基本原理,并实践一些简单的数字电路和嵌入式系统设计。

可以通过Basys3开发板的官方网站或者一些在线论坛找到更详细的例程和教程。

Application Note AC401January 20141© 2014 Microsemi Corporation SmartFusion2 SoC FPGA - SPI Master ProgrammingTable of ContentsPurposeThis application note describes how to use the serial peripheral interface (SPI) Master Programming mode on SmartFusion ®2 system-on-chip (SoC) field programmable gate array (FPGA) Development Kit board DVP-102-000400-001 Rev C.Note:Rev A and Rev B Development Kit Board are not supported.Two software utilities, SPI_Memory.exe and SetMuxes.exe, are described in this document. The SPI_Memory.exe is used to program Atmel ® AT25DF641 and SetMuxes.exe is used to configure the multiplexers on the Development Kit board to either perform SPI Memory Programming or initiate SPI Master Programming.IntroductionSPI Master Programming mode, also known as auto-update or reflash is one of the programming methods available to program SmartFusion2 devices. Refer to the SmartFusion2 Programming User's Guide for more information on the available programming modes. On power-up or resetting the device with FLASH_GOLDEN_N pin asserted (driven low), the SmartFusion2 device configures the dedicated SPI port to operate in Master mode. It also reads the attached external SPI memory device from address zero. Auto programming is executed if a valid programming image is found. Figure 1 shows a high level system design to execute auto programming.Purpose . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1Development Kit Board Programming Circuit Design Description . . . . . . . . . . . . . . . . . . . . 2Programming the SPI Master . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4List of Changes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6Appendix A - SPI Memory Utility . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7Appendix B - SetMuxes Utility . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7SmartFusion2 SoC FPGA - SPI Master Programming2Development Kit Board Programming Circuit Design DescriptionThe Development Kit board programming circuitry has an on board FT4232H module from Future Technology Devices International (FTDI). This module is a universal serial bus (USB)-to-serial interface converter. For more information on FT432H module, see FTDI website at /Products/Modules/DevelopmentModules.htm. This module is connected to the M2S dedicated SPI port and the SPI memory device using the multiplexers. The multiplexers can then be configured either manually or through SetMuxes.exe utility described below to program the Atmel SPI memory device or to initiate an auto-programming operation. The Development Kit board is designed in this fashion to program the SPI memory device on board through the FTDI chip. Figure 2 shows how the multiplexers are connected.Figure 1 • Auto Programming (SPI- Master) ModeDevelopment Kit Board Programming Circuit Design Description3Figure 2 • Connection of MultiplexersFigure 3 • Development Kit Board Programming Circuit - Auto Programming ModuleSmartFusion2 SoC FPGA - SPI Master Programming4Note:Some of the FT4232H I/O pins control the enable and select signals of the multiplexers.SetMuxes.exe configures these pins to either perform the SPI memory programming manually or initiate auto-programming.Programming the SPI MasterThe following steps describe how to program the SPI master.1.Set the jumpers on the Development Kit board as:–J43 (Pin 1 - Pin 2)–J55 (Pin 1 - Pin 2)–J70 (Pin 2 - Pin 3)2.Install the FTDI drivers based on the operating system as described in the FTDI driver installationguide available at: /Support/Documents/InstallGuides.htm.3.Copy the following files into a local directory on your PC.–FTCJTAG.dll: Used for interfacing FT2232 to devices using the JTAG protocol.Note:Click the file name to download a ZIP file containing the library.–libMPSSE.dll : This library has been created to aid the implementation of I2C designs using FTDI devices which incorporate the FTDI MPSSE.–SetMuxes.exe: Refer "Appendix B - SetMuxes Utility"for more information.–SPI_Memory.exe: Refer "Appendix A - SPI Memory Utility"for more information.–Click here to download a sample demo project containing both the exe files.4.Copy the programming file (.spi) to a local directory on the PC. Use one of the .spi files included inthis demo package or generate a design and export it through Libero ® System-on-Chip (SoC)software. For more information on how to use Libero software, refer /download/software/liberosoc/default.aspx.5.Open the Command Prompt and navigate to the directory where the files are saved.6.Connect the Development Kit board mini USB (J24) to the PC.7.Power-up the Development Kit board.Figure 4 • Development Kit Board Programming Circuit - FT4232H ModuleProgramming the SPI Master58.In the command prompt, type:SetMuxes MEMThis application sets the multiplexers for the FTDI chip to access the Atmel memory device on the board. Figure 4 shows an example message on successful setting-up of the multiplexers.9.In the command prompt, type:SPI_Memory -aprogram <file name>.spiThis updates the Atmel spi memory device, as shown in Figure 6.10.In the command prompt type the following:SetMuxes REFFigure 5 • SetMuxes MEMFigure 6 • aprogram <file name>.spiSmartFusion2 SoC FPGA - SPI Master Programming6This command sets the multiplexers for the M2S chip to access the Atmel memory device on the board and initiates reflash, as shown in Figure 7. The M2S device functions with a delay of approximately a minute. The functioning is based on the design that you programmed.Note:With this configuration, any subsequent resets to the device or board power cycle initiate thereflash operation again.11.In the command prompt type the following:SetMuxes SPIThis application sets the multiplexers for the FTDI chip to access the M2S device, as shown in Figure 8.List of ChangesThe following table lists critical changes that were made in the current version of the document.Figure 7 • SetMuxes REFFigure 8 • SetMuxes SPIRevisionChanges in Current Version (51900145-2/2.08*)Page Revision 1January 2014Updated the section "Programming the SPI Master"(SAR 53223).4Appendix A - SPI Memory Utility7Appendix A - SPI Memory UtilitySPI_Memory.exe is a standalone command line utility that uses the FTDI chip to program the SPI file into the Atmel AT25DF641 memory device used in the Development Kit board. This supports the following platforms:•Windows XP •Windows Vista •Windows 7Usage: spi_memory [options] <filename> Available options:•-h : show help message •-a<action>: Specify action name as follows:–read_id: Read device ID.–Blank: Checks to see if device is in erased state.–Erase: Erases the entire device.–Program: Programs the content of the file into the device starting at address 0.–Verify: Verifies the content of the device against the file.–Read: Reads the content of the device and saves it in ReadBuffer.bin.Appendix B - SetMuxes UtilitySetMuxes.exe configures the multiplexers on the Development Kit board based on the desired operation.This supports the following platforms:•Windows XP •Windows Vista •Windows 7Usage: SetMuxes [options]MEM: Configures the multiplexers to enable FTDI connection to the SPI memory device on the dedicated SPI port.REF: Configures the multiplexers to connect the M2S device to the SPI memory device and initiate reflash.SPI: Configures the multiplexers to connect the M2S device to FTDI for SPI- Slave programming.51900269-1/01-14© 2013 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.Microsemi Corporation (NASDAQ: MSCC) offers a comprehensive portfolio of semiconductor solutions for: aerospace, defense and security; enterprise and communications; and industrial and alternative energy markets. Products include high-performance, high-reliability analog and RF devices, mixed signal and RF integrated circuits, customizable SoCs, FPGAs, and complete subsystems. Microsemi is headquartered in Aliso Viejo, Calif. Learn more at .Microsemi Corporate HeadquartersOne Enterprise, Aliso Viejo CA 92656 USAWithin the USA: +1 (949) 380-6100Sales: +1 (949) 380-6136Fax: +1 (949) 215-4996。

开发板发展史开发板(Development Board)是为了方便开发者进行软硬件开发和测试而设计的一种单板计算机。

以下是开发板发展史的简要概述:1.单片机开发板:在计算机技术早期,单片机是最常用的开发平台之一。

单片机开发板提供了一种便捷的方式,让开发者能够以低成本和低功耗来开发嵌入式系统。

2.微控制器开发板:随着芯片技术的发展,微控制器开发板逐渐取代了单片机开发板。

它们提供了更强大的处理能力、更多的IO接口和更丰富的功能集,使得开发者能够更灵活地设计和测试各种应用。

3.FPGA开发板:随着可编程逻辑技术的进步,FPGA开发板在现代开发中扮演着重要的角色。

FPGA提供了强大的可重构能力,使得开发者能够定制化硬件逻辑,加速处理速度,并灵活适应不同的应用场景。

4.Raspberry Pi:在2012年推出的Raspberry Pi开发板引领了一股新的开发板潮流。

Raspberry Pi采用了ARM架构的处理器和丰富的接口,成为了一种非常流行的低成本开发平台,广泛应用于物联网、教育、嵌入式系统等领域。

5.Arduino:Arduino是另一个非常受欢迎的开发板品牌。

它基于开源硬件和软件平台,简化了电子原型设计的流程,并为想要进行物联网和互动创作的开发者提供了一个友好的开发环境。

6.边缘计算开发板:近年来,随着物联网和边缘计算的兴起,各种适用于AI、机器视觉、自动驾驶等应用场景的边缘计算开发板开始崭露头角。

这些开发板通常搭载高性能处理器和机器学习芯片,以支持复杂的计算和深度学习任务。

总的来说,开发板的发展是与计算机技术的不断进步和应用需求的演变相互关联的。

从最初的单片机到现代的边缘计算开发板,它们不断推动着软硬件开发的进步,为开发者提供了更多的工具和平台来实现创新和应用。

FPGA开发入门教程FPGA(Field-Programmable Gate Array)是一种可重新配置的集成电路,能够根据用户需求实现不同的功能。

作为硬件开发的重要技术之一,FPGA具有灵活性高、性能强、功耗低等优点,因此受到了广泛的关注和应用。

本文将介绍FPGA开发的入门教程,帮助初学者快速上手FPGA开发。

第一步:了解FPGA第二步:选择开发工具和开发板FPGA开发需要选择合适的开发工具和开发板。

常用的FPGA开发工具有Xilinx的Vivado和Altera的Quartus等。

这些工具提供了图形化界面以及一些示例代码,方便用户进行开发和调试。

开发板是用户在FPGA开发中搭建硬件平台的重要部分,通过开发板可以将FPGA芯片与其他外设相连接,进行实际的验证和测试。

选择开发工具和开发板时要考虑到自己的需求和预算。

第三步:学习HDL编程语言HDL(Hardware Description Language)是用于描述数字电路的编程语言,FPGA开发中常用的HDL有Verilog和VHDL。

要掌握FPGA开发,我们必须学习和熟悉HDL编程语言。

HDL语言可以描述数字电路的结构、功能和时序等信息,通过HDL编写的代码可以被FPGA开发工具转化成对应的硬件电路。

学习HDL编程语言需要掌握其语法规则和基本概念,理解时序逻辑和组合逻辑的原理,并通过练习和实践进行巩固。

第四步:学习FPGA开发流程第五步:完成第一个FPGA项目通过以上几个步骤的学习和实践,我们已经具备了进行FPGA开发的基本能力。

接下来我们可以尝试完成一个简单的FPGA项目,例如实现一个LED闪烁的功能。

我们可以使用HDL语言编写一个简单的计数器,将计数值输出到FPGA开发板上的LED灯,通过改变计数值的频率实现LED的闪烁。

完成这个项目可以加深对FPGA开发流程的理解,并为后续更复杂的项目奠定基础。

总结FPGA开发入门需要掌握FPGA的基本概念和工作原理,选择合适的开发工具和开发板,学习HDL编程语言,了解FPGA开发流程,并通过实践完成一个简单的FPGA项目。

电赛买方案1. 背景近年来,电子设计竞赛(简称电赛)在全球范围内逐渐兴起,并吸引了越来越多的学生参与其中。

电赛作为一项综合性的竞赛项目,对参赛的选手提出了很高的要求。

为了在电赛中获得好的成绩,购买适合的电赛设备是至关重要的。

2. 目标本文旨在为参与电赛的选手提供一个买方案,以帮助选手在购买电赛设备时更加明智地做出决策。

本买方案将根据电赛的性质和要求,从设备的选购、价格、性能等多个方面进行详细介绍和分析。

3. 选购设备3.1 FPGA开发板在电赛中,FPGA开发板是必不可少的设备之一。

选购一个适合的FPGA开发板可以提高电赛的设计效率和实现准确性。

推荐选购Xilinx Kintex-7 XC7K410T FPGA开发板。

该开发板具有较大的逻辑单元数量和丰富的外设接口,支持高级的逻辑设计和数据处理能力。

此外,该开发板具有较高的性价比,适合中小型电赛项目使用。

3.2 单片机开发板除了FPGA开发板外,选购一个适合的单片机开发板也是必要的。

单片机开发板可以用于控制和通信等功能,在电赛中具有重要的作用。

推荐选购STMicroelectronics STM32F407VG单片机开发板。

该开发板具有较强的处理能力和丰富的外设接口,适合复杂的控制任务和通信需求。

此外,该开发板的开发环境和资源丰富,有助于快速开发和调试。

3.3 可编程电源为了满足电赛中对电源的稳定性要求,选购一个可编程电源是十分重要的。

可编程电源可以提供稳定的电压和电流输出,以保证电路设计的可靠性和准确性。

推荐选购Rigol DP832可编程电源。

该电源具有高精度的电压和电流输出,支持编程控制和自动化测试。

此外,该电源还具有较大的输出功率和丰富的保护功能,适合电赛中各种需求的电源供应。

4. 价格与性能比较4.1 FPGA开发板比较下表列出了几款常用的FPGA开发板的价格和性能比较:FPGA开发板价格(人民币)逻辑资源外设接口Xilinx Kintex-7 ¥1500 325,200 PCIe, Ethernet, USBAltera Cyclone IV ¥1200 26,288 Ethernet, USBFPGA2013 ¥1000 20,000 HDMI, VGA, USB从表中可以看出,Xilinx Kintex-7 FPGA开发板在价格和性能上都具有较大的优势,适合大型电赛项目使用。

ARTIX-7FPGA开发平台用户手册AX7202REV1.2版芯驿电子科技(上海)有限公司黑金动力社区目录目录 (2)一、开发板简介 (4)二、FPGA核心板 (7)(一)简介 (7)(二)FPGA (9)(三)有源差分晶振 (10)(四)DDR3 (12)(五)QSPI Flash (16)(六)LED灯 (18)(七)复位按键 (19)(八)JTAG接口 (20)(九)电源接口 (21)(十)扩展接口 (21)(十一)电源 (28)(十二)结构图 (29)三、扩展板 (30)(一)简介 (30)(二)千兆以太网接口 (31)(三)光纤接口 (33)(四)VGA显示接口 (36)(五)USB2.0 (38)(六)SD卡槽 (40)(七)USB转串口 (41)(八)RS232接口 (43)(九)EEPROM24LC04 (44)(十)实时时钟DS1302 (45)(十一)扩展口 (47)(十二)JTAG接口 (50)(十三)按键 (51)(十四)LED灯 (52)(十五)供电电源 (53)黑金ARTIX-7系列的高端FPGA开发平台(型号:AX7202)正式发布了,为了让您对此开发平台可以快速了解,我们编写了此用户手册。

这款ARTIX-7FPGA开发平台采用核心板加扩展板的模式,方便用户对核心板的二次开发利用。

在底板设计上我们设计了丰富的外围接口,比如2路光纤模块接口,一路千兆以太网接口,一路USB2.0接口,VGA输出接口,Uart接口,RS232接口等等。

满足用户各种高速数据传输,视频处理和工业控制的要求,是一款"全能级“的FPGA 开发平台。

为高速视频传输,网络和光纤通信及数据处理的前期验证和后期应用提供了可能。

相信这样的一款产品非常适合从事FPGA开发的学生、工程师等群体。

一、开发板简介在这里,对这款AX7202FPGA开发平台进行简单的功能介绍。

开发板的整个结构,继承了我们一贯的核心板+扩展板的模式来设计的。

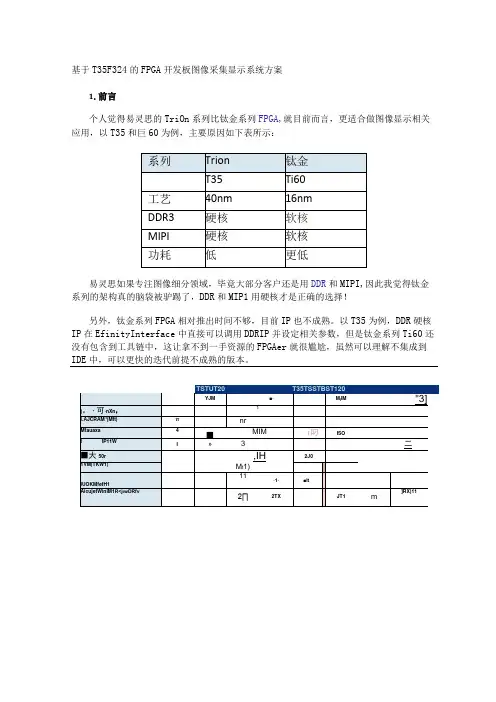

基于T35F324的FPGA开发板图像采集显示系统方案1.前言个人觉得易灵思的TriOn系列比钛金系列FPGA,就目前而言,更适合做图像显示相关应用,以T35和巨60为例,主要原因如下表所示:易灵思如果专注图像细分领域,毕竟大部分客户还是用DDR和MIPI,因此我觉得钛金系列的架构真的脑袋被驴踢了,DDR和MIP1用硬核才是正确的选择!另外,钛金系列FPGA相对推出时间不够,目前IP也不成熟。

以T35为例,DDR硬核IP在EfinityInterface中直接可以调用DDRIP并设定相关参数,但是钛金系列Ti60还没有包含到工具链中,这让拿不到一手资源的FPGAer就很尴尬,虽然可以理解不集成到IDE中,可以更快的迭代前提不成熟的版本。

M1P1TX/RX 接口,山谷0.8mm40P 接口如上图所示,T35F324的FPGA 开发板,我都做了快半年了,一直没有做一个基于视频图像的像样点的DCm0,甚是惭愧。

为了给当下煎熬的大家送点福利,我打算分2步走,如下:DVP 相机+DDR3+1VDS-1CD 实时显示系统 MIPI 相机+DDR3+1VDS-1CD 实时显示系统前者更关注DDR3硬核、1VDSTX,以及进行并口相机的配置与图像采集,完成实时图像采集、缓存、显示系统;后者则借用1)的基础,更关注MIP1相机的开发,进一步把易灵思FPGA 进行图像采集的优势,发挥一下。

当然这过程肯定还是有不少的坑,有些坑只有自己趟过,才有发言权。

底板串口DC3-40用户接口,兼容兼容@01⑥MT拨动开关BMW 0V5生0等模MIP1摄像头Jr兼容树莓派rOV5640 Efint FPQABOa1Q CraZyfpg>iomEfin1tyT3SF324-Cor∙V1.1一«... M2X>S12202305152.FPGA设计详解言归正传,我们开始干正事:基于T35的摄像头采集、存储、显示系统的介绍。

FPGA开发入门教程FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,它的功能和电路结构可以通过配置来定义和改变。

FPGA开发是一门广泛应用于数字电路设计和嵌入式系统开发的技术,为了让初学者能够快速入门FPGA开发,下面将为你介绍一些基本的知识和步骤。

首先,你需要准备一块FPGA开发板,这是进行FPGA开发的基础设备。

常用的开发板有Xilinx的Zynq开发板和Altera的Cyclone开发板。

选择适合自己的开发板并购买好后,你需要将其连接到计算机上,可以使用USB接口或者以太网接口。

在进行FPGA开发之前,你需要了解一些基本的概念和概述。

首先,了解FPGA的基本结构和工作原理,掌握FPGA的内部资源如LUT(Look-Up Table)、寄存器、片上内存等。

其次,学习硬件描述语言(HDL),比如Verilog或VHDL,这是描述FPGA电路的语言。

一般来说,进行FPGA开发的流程包括以下几个步骤:1.确定设计目标:首先,你需要明确自己的设计目标,包括所要实现的功能、性能要求等。

这将为你后面的设计和实现提供指导。

2.设计电路:使用HDL语言,根据设计目标,将电路进行描述。

你可以使用模块化设计的思想,将电路划分为多个模块,然后逐个进行设计和实现。

4.综合和布局布线:综合是将HDL代码转换为FPGA的逻辑电路的过程,布局布线是将逻辑电路映射到FPGA的物理资源的过程。

这两个步骤是将电路从逻辑描述转换为实际可用的FPGA电路的关键步骤。

通过上述步骤,你就可以完成一次简单的FPGA开发了。

当然,FPGA 开发涉及到的知识还有很多,包括时序设计、高级优化技术等。

希望通过这篇文章,你能对FPGA开发有一个初步的了解,并能够为你的学习和实践提供一些指导。

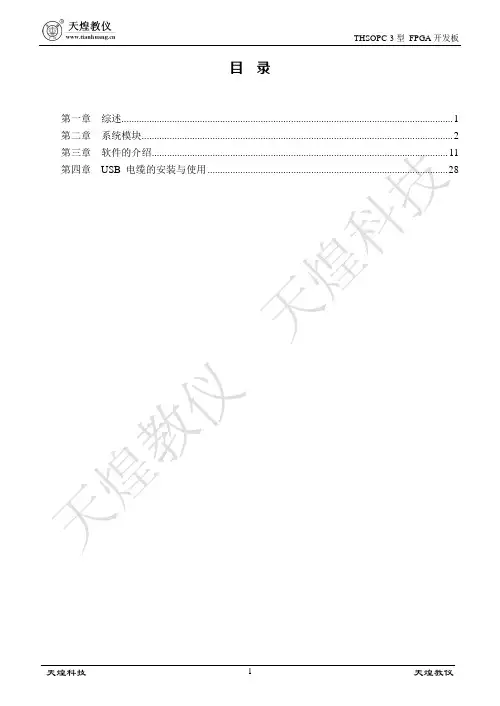

目录第一章综述 (1)第二章系统模块 (2)第三章软件的介绍 (11)第四章USB 电缆的安装与使用 (28)第一章综述THSOPC-3型FPGA开发板是根据现代电子发展的方向,集EDA和SOPC系统开发为一体的综合性实验开发板,除了满足高校专、本科生和研究生的SOPC教学实验开发之外,也是电子设计和电子项目开发的理想工具。

一、实用范围:●自主创新应用开发;●单片机与FPGA联合开发;●IC设计硬件仿真;●科研项目硬件验证与开发;●高速高档自主知识产权电子产品开发;●毕业设计平台;●研究生课题开发;●电子设计竞赛培训;●现代DSP开发应用;●针对各类CPU IP核的片上系统开发;●DSP Biulder系统设计。

二、硬件配置:THSOPC-3型FPGA开发板基于Altera Cyclone II 器件的嵌入式系统开发提供了一个很好的硬件平台,它可以为开发人员提供以下资源:●支持+5V 电源适配器直接输入或者USB接口供电,5V、3.3V、1.2V混合电压源;●FPGACycloneII FPGA EP2C8,40万门,2个锁相环;●isp单片机AT89S8253。

isp单片机AT89S8253及开发编程工具,MCS51兼容,12KB isp可编程Flash ROM,2KB ispEEPROM,都是10万次烧写周期;2.7-5.5V工作电压;0-24MHz工作时钟;可编程看门狗;增强型SPI串口,9个中断源等。

此单片机可与FPGA联合开发,十分符合实现当今电子设计竞赛项目的功能与指标实现;●EPM3032 CPLD;● 4 Mbits 的EPCS4 配置芯片;●512KB高速SRAM;●20MHz 高精度时钟源(可倍频到300MHz);● 4 个用户自定义按键;●8 个用户自定义开关;●8 个用户自定义LED;● 2 个七段码LED;●标准AS 编程接口和JTAG调试接口;●两个标准2.54mm扩展接口,供用户自由扩展;●RS-232 DB9串行接口;●PS/2键盘接口;●VGA接口;●4X4键盘;●液晶显示屏20字X4行;●USB-Blaster编程器,可对FPGA通过JTAG口编程、调试、测试;单片机编程ByterBlasreMV 编程器;●光盘:配套子程序库、资料、编程软件、实验指导书。

FPGA开发板使用手册一、硬件概述FPGA开发板是一种基于可编程逻辑器件(FPGA)的嵌入式系统开发板,它为电子工程师提供了一个高度灵活和可定制的平台,可用于开发各种数字系统,如通信、控制、数据处理等。

本手册旨在帮助用户了解和使用这款FPGA开发板,充分发挥其性能和功能。

二、开发板规格本开发板规格如下:1. 尺寸:90mm x 60mm x 1.6mm。

2. FPGA型号:Xilinx XC7020。

3. 内存容量:128MB DDR3。

4. 存储器:8GB eMMC。

5. 接口类型:USB 2.0,以太网 10/100Mbps,RS232等。

6. 电源电压:5V。

7. 重量:约15克。

三、硬件连接本开发板可通过以下方式与外围设备连接:1. USB接口:用于连接电脑进行编程和调试。

2. 以太网接口:用于连接网络。

3. RS232接口:用于连接其他串口设备。

4. GPIO接口:用于连接其他数字设备。

5. I2C接口:用于连接I2C总线设备。

6. SPI接口:用于连接SPI总线设备。

7. HDMI接口:用于显示输出。

8. SRAM接口:用于高速数据存储。

9. UART接口:用于串口通信。

四、FPGA设计工具安装与使用FPGA设计工具是用于编写和调试FPGA逻辑代码的软件环境。

本开发板支持的FPGA设计工具有Xilinx Vivado和Intel Quartus等。

用户需要根据所选工具,下载并安装相应的软件,然后按照软件说明进行安装和配置。

在安装过程中,请注意选择与本开发板兼容的版本和配置。

安装完成后,用户可以使用FPGA设计工具编写逻辑代码,并通过开发板的接口将代码下载到FPGA中运行。

五、FPGA设计基本原则在FPGA设计中,需要遵循以下基本原则:1. 模块化设计:将复杂问题分解为多个简单的子问题,逐个解决,便于调试和维护。

2. 尽量使用硬件加速器:利用FPGA的并行处理能力,提高系统性能。

ARTIX-7 FPGA 开发平台用户手册1.0目录1、开发板简介: (3)2、开发板功能描述 (6)2.1 Artix-7 FPGA 引脚分配 (6)2.2 扩展接口 (6)2.3 电源 (10)2.3.1 电源变换 (10)2.3.2电源分配功能 (10)2.3.3电源启动顺序 (10)2.4 有源晶振 (10)2.5 FPGA启动 (11)2.6 LED和按键 (12)2.6.1 LED (12)2.6.2 按键 (15)2.7 XADC (17)2.8 DDR3 (18)2.9 SPI FLASH (19)2.9.1 FLASH (19)2.9.2 USER FLASH (19)2.10 / JTAG接口 (20)2.10.1 JTAG (20)2.10.2 USER JTAG (20)2.11 蜂鸟与FPGA连接 (21)1、开发板简介:正面背面此款开发板使用的是 Xilinx 公司的 Artix-7 系列 FPGA ,型号XC7A35T-1FTG256C ,256个引脚的 FBGA 封装。

此款 FPGA 的资源如下图所示:其中,主要的参数:逻辑单元 Logic Cells :33280; 乘法器 DSP48:90;可配置逻辑块 CLBs :400Kb ; Block RAM :1800Kb ; 时钟单元 CMTs :5; 可用 IO 数量:210 个; 内核电压:1.0V ;工作温度:0——﹢85℃;图为整个系统的结构示意图:FPGAXC7A35T晶振+5V电源接口 JTAG 口USER_JTAG 口PMOD口FLASHUSER_ FLASH256MByte DDR33.3V 电源1.0V电源1.8V电源DDR 电源 用户按键拨动开关配置指示灯用户LED 灯用户RGB 灯高速接插件电源指示灯电源开关Arduino兼容接口1.5V 电源Arduino 兼容接口2、开发板功能描述2.1 Artix-7 FPGA 引脚分配XC7A35T-1FTG256C共有5个I/0 Bank,其中U2E是FPGA专用的配置Bank,其2.2 扩展接口开发板有P1、P2、JP1三个用户接口。

FPGA烧写步骤简介FPGA(现场可编程门阵列)是一种可编程逻辑设备,通常用于实现各种数字电路和系统。

在FPGA烧写过程中,需要按照一定的步骤进行操作。

下面是一份FPGA 烧写的步骤:1.准备开发板和FPGA芯片首先需要准备一个开发板和一块FPGA芯片。

开发板通常包括FPGA芯片、电源电路、晶振、复位电路等,而FPGA芯片则需要根据具体的设计需求选择合适的型号。

2.安装开发环境在烧写FPGA之前,需要安装相应的开发环境,例如Quartus或Vivado等。

这些开发环境通常包括编译器、仿真器、调试器等工具,可以帮助用户完成FPGA设计、编译、仿真和调试等任务。

3.设计FPGA电路使用硬件描述语言(如Verilog或VHDL)设计FPGA电路。

在设计过程中,需要考虑电路的功能、性能和可扩展性等因素。

4.编译设计文件将设计文件编译成二进制文件,以便烧写到FPGA芯片中。

在编译过程中,需要对设计文件进行优化,以提高FPGA的性能和可扩展性。

5.烧写二进制文件到FPGA芯片使用烧写器将编译后的二进制文件烧写到FPGA芯片中。

在烧写过程中,需要注意FPGA芯片的配置方式和烧写速度等因素。

6.验证FPGA电路功能通过仿真器或调试器验证FPGA电路的功能是否正确。

如果发现问题,需要及时进行修改和调试。

7.上板测试将烧写好的FPGA芯片安装到开发板上进行测试。

测试时需要注意电源、信号质量等因素,以确保FPGA芯片能够正常工作。

以上是FPGA烧写的步骤,具体操作可能会因不同的开发环境和FPGA芯片型号而有所不同。

在进行FPGA烧写时,需要注意安全操作,避免因操作不当导致设备损坏或数据丢失等问题。

FPGA开发板快速教程(一)---基础知识FPGA开发板作者:古文章来源:本站原创点击数:2284 更新时间:2007-5-24前言FPGA在复杂逻辑电路以及数字信号处理领域中扮演者越来越重要的角色,SOC(片上系统)以其低功耗,高性能,低成本,高可靠性等优点成为嵌入式系统的发展趋势。

作为一个简明的教程,主要宗旨是让初学者快速地了解FPGA/SOPC (可编程片上系统)开发的流程。

目前IT技术的发展可以说是一日千里,以本人的观点来讲,如果希望在电子设计领域有所作为,则必须具备快速掌握新技术的能力。

电子设计最重要的是实践的积累,我们只要具备了一定的基础,应当马上投入实践,否则很多概念都无法真正理解。

有不少人包括我,当下决心要成为一个合格的电子设计工程师的时候,总是想如果把有关电路方面的理论都掌握了才能所向披靡,有底气参加实际项目设计。

当然如果能做到“把有关理论都掌握了”这样的境界,我想应该是很理想的,但经验发现这并不实际。

据我所知,我所认识的不少电子设计牛人,他们的理论知识可能都比不上我们的本科生,但很多不错的产品都是从他们的手中开发出来的,有了实践的经验后,他们掌握新技第二节基于Q u a r t u s I I的实例…………………………………………………………………………………实验一实验板上的K E Y1按钮控制F P G A核心板上的第一个L E D灯介绍………………………………实验二7段数码管实验…………………………………………………………………………………实验三用F P G A设计串口数据收发…………………………………………………………………………第三章S O P C的基本开发流程…………………………………………………………………………………第一节第一节S O P C v s M C U、D S P和F P G A………………………………………………………………………第二节第二节基于QuantusII和NiosII的SOPC基本开发流程……………………………………………………第三节第三节基于Q u a n t u s I I和N i o s I I的S O P C实例……………………………………………………………实验一核心板上的两个L E D交替闪烁…………………………………………………………………实验二4位7段数码管I P c o r e设计以及f l a s h的烧写教程…………………………………实验三L C D设备驱动开发………………………………………………………………………实验四A L L_T E S T综合设计……………………………………………………………………………第四章FPGA开发板中嵌入Uclinux的步骤和方法……………………………………………………第一章 CPLD/FPGA的基本知识(二)FPGA、CPLD 概述FPGA(现场可编程门阵列)与 CPLD(复杂可编程逻辑器件)都是可编程逻辑器件,它们是在PAL,GAL等逻辑器件的基础之上发展起来的。

FPGA助学板教材-睿智FPGA开发板硬件详解睿智FPGA助学板硬件详解开发板套件硬件是保证实验学习的基础,这部分内容主要针对硬件部分做简单描述,可适当阅读或翻查,特别是涉及到硬件接⼝定义等信息时,了解这部分内容很有必要。

同时,可与光盘附带的硬件原理图⼀并参考使⽤。

1.睿智FPGA助学板硬件1.1 总体介绍图1 助学板硬件实拍图主硬件资源1 .主芯⽚采⽤ALTERA公司最新四代FPGA CycloneIV系列EP4CE6E22C8N;2 .板载EPCS4N/EPCS16⼤容量串⾏配置芯⽚,⽀持JTAG/AS模式;3. 板载64MbitSDRAM,⽀持SOPC,NIOSII开发(很多价低的板不带SDRAM,⽆法⽀持NIOS SOPC开发);4 .板载50MHz有源晶振,提供系统⼯作主时钟;5 .采⽤1117-3.3V稳压芯⽚,提供3.3V电压输出;6 .采⽤1117-1.2V稳压芯⽚,提供FPGA内核电压;7 .采⽤1117-2.5V稳压芯⽚,提供PLL电压;8 .精⼼的去耦设计,采⽤⼤量去耦电容;9. 提供5V直流电源插座;10. 提供⽅⼝USB接⼝电源插座;11. ⼀个系统复位按键Reset,也可做为⽤户输⼊按键;12. ⾃锁按键电源开关;13. LED电源指⽰灯;14. 精⼼设计分配的IO资源,所有IO引出,3个扩展接⼝,通⽤2.54mm间距,任由您⾃⼰扩展;15.JTAG下载接⼝对应下载的⽂件是.SOF,速度快,平常学习推荐使⽤此接⼝;16. AS下载接⼝对应下载的⽂件是.POF,速度较慢,需要固化程序时使⽤。

丰富外设资源1 .板载4个独⽴按键,可做按键控制,数字逻辑基础实验等;2 .板载4位LED发光⼆极管,可做LED控制,数字逻辑基础实验等;3. 板载4位数码管,频率计,秒表;4. 板载4位拨码开关,可做开关控制等实验;5 .设有1X20液晶屏排座,⽀持LCD1602,LCD12864,TFT液晶屏(不包括LCD,需另购);6 .精密可调电阻,调节液晶背光;7 .板载1路蜂鸣器,可做发声及⾳乐实验;8 .PS2接⼝,可做PS/2键盘实验;9 .板载全新原装进⼝温度传感器芯⽚LM75A,可以做温度计实验;10 .RS232串⼝,可做串⼝通讯实验;11 .VGA接⼝,可做显⽰器实验等;12. I2C串⾏EEPROM AT24C08,做IIC总线实验;13 .红外线接收模块;1.2 FPGA的IO分配FPGA的硬件设计与单⽚机,ARM或DSP还是有所不同,MCU的IO通常功能都是固定好的,Datasheet要求某个引脚什么功能,就必须是什么功能。

FPGA开发板

FPGA开发板ALTERA FPGA是世界上十几家生产CPLD/FPGA的公司中最大的可编程逻辑器件供应商之一,生产的FPGA产品有:FLEX6000/8000/10K、APEX20K、ACEX1K、APEXⅡ、Mercury、Excalibur、Cyclone、Stratix、CycloneⅡ和StratixⅡ等系列。

Altera的FPGA器件采用钢铝布线的先进CMOS技术,具有非常低的功耗和相当高的速度,而且采用连续式互连结构,提供快速的、连续的信号延时。

Altera器件密度从300门到400万门,能很容易地集成现有的各种逻辑器件,高集成度的FPGA提供更高的系统性能,更高的可靠性,更高的性能价格比。

Altera Cyclone系列FPGA是Altera公司2003年9月份推出的,基于1.5V,0.13μm 工艺,Cyclone 是一个性价比很高的FPGA系列。

其中EP1C3T144是Cyclone系列中的一员,共有2910逻辑单元,59904RAM bits,1个PLLs,最多有104个用户I/O,可以说这款FPGA的资源非常丰富,足够满足大型设计的需要。

本公司因此特推出Cyclone EP1C3T144C8 FPGA开发板,该开发板功能强大,接口丰富,可做大型综合实验。

FPGA开发板硬件资源主要有:

1、Altera EP1C3T144C8 FPGA芯片

2、Altera 串行配置芯片EPCS1

3、DAC0832芯片

4、ADC0809芯片

5、液晶接口

6、TP3057PCM编解码芯片

7、八位高亮数码管

8、八位拨码开关

9、4×4阵列键盘

10、4个复位轻触按键

11、9个高亮发光二极管(红、绿、黄色各三灯)

12、双刀双掷继电器

13、异步通信串口(UART)

14、双有源晶振(24MHz和32.768MHz)

15、5V,3.3V,1.5V电源管理系统

FPGA开发板带以下DEMO程序:

1、FPGA实现流水灯实验

2、FPGA实现电子钟实验

3、FPGA实现串口发送实验

4、FPGA实现串口接收、点阵显示实验

5、FPGA实现矩阵键盘和点阵显示(实时扫描方式)

6、FPGA实现矩阵键盘和数码管显示(延时扫描方式)

7、FPGA实现AD转换、数码显示和拨码选择通道实验

8、FPGA实现DA转换,产生锯齿、三角、正弦波;拨码开关选择波形

9、FPGA实现液晶显示(并行控制)

10、FPGA实现液晶显示(串行控制)

11、FPGA实现TP3057音频编解码

12、简单密码锁实验(按键+继电器实验)

FPGA开发板上的所有模块单元都已连线,省去了连线的烦恼,同时FPGA芯片所有可用I/O都通过自锁紧插座引出,方便做扩展实验,而且FPGA芯片由于管脚密集,在引脚插座旁都标有对应的管脚号,使您对所用的管脚一目了然。

开发板上FPGA芯片带有JTAG和Active Serial两个下载插座,因此开发板在使用时,可以通过JTAG和AS两种下载方式进行调试,大大的节省了您的开发成本和时间。

FPGA开发板电源输入为直流9V~15V。

FPGA开发板除FPGA芯片(EP1C3T144C8)和配置芯片(EPCS1)外享受本站的质量保修条例,保修期外,本站负责维修,只收取成本费。

注意事项:

开发板一定要关闭电源后,才可以插拔下载线!否则会烧坏FPGA芯片以及下载线!

附件包括:并口延长线一条,Altera ByteBlastⅡ下载线一条(可以对FPGA JTAG和Active Serial在线编程),串口延长线(孔对孔交叉)一条,音频延长线一条,光盘一张(包含电路原理图,印刷电路板图,使用说明书,QuartusⅡ4.2版,DEMO程序,串口调试软件,VHDL相关设计教程和相关芯片资料)

若需要9V稳压电源的用户,需另加15元

若需要128×64带中文字库液晶的用户,需另加150元。