基于Matlab的卷积码译码器的 设计与仿真 学生姓名:指导老师:** 摘要本课程设计主要解决对一个卷积码序列进行维特比(Viterbi)译码输出, 并通过Matlab软件进行设计与仿真,并进行误码率分析。在课程设计中,系统开发平台为Windows Vista Ultimate,程序设计与仿真均采用Matlab R2007a(7.4),最后仿真详单与理论分析一致。 关键词课程设计;卷积码译码器;Matlab;Simulink;设计与仿真 1引言 本课程设计主要解决对一个卷积码序列进行维特比(Viterbi)译码输出,并通 过Matlab软件进行设计与仿真。卷积码的译码有两种方法——软判决和硬判决,此课程设计采用硬判决的维特比译码。 1.1课程设计目的 卷积码是一种向前纠错控制编码。它将连续的信息比特序列映射为连续的编码器输出符号。这种映射是高度结构化的,使得卷积码的译码方法与分组码译码所采用的方法完全不同。可以验证的是在同样复杂度情况下,卷积码的编码增益要大于分组码的编码增益。对于某个特定的应用,采用分组编码还是采用卷积编码哪一种更好则取决于这一应用的具体情况和进行比较时可用的技术[1]。 本课程设计便是通过Matlab设计一个硬判决维特比译码输出的完整电路,并进行误码率分析。

1.2 课程设计的原理 卷积码,又称连环码,是由伊莱亚斯(P.elias)于1955年提出来的一种非分组码。 卷积编码的最佳译码准则为:在给定已知编码结构、信道特性和接收序列的情况下,译码器将把与已经发送的序列最相似的序列作为传送的码字序列的估值。对于二进制对称信道,最相似传送序列就是在汉明距离上与接收序列最近的序列。 卷积码的译码方法有两大类:一类是大数逻辑译码,又称门限译码(硬判决,编者注);另一种是概率译码(软判决,编者注),概率译码又分为维特比译码和序列译码两种。门限译码方法是以分组码理论为基础的,其译码设备简单,速度快,但其误码性能要比概率译码法差[2]。 当卷积码的约束长度不太大时,与序列译码相比,维特比译码器比较简单,计算速度快。维特比译码算法是1967年由Viterbi提出,近年来有大的发展。目前在数字通信的前向纠错系统中用的较多,而且在卫星深空通信中应用更多,该算法在卫星通信中已被采用作为标准技术。 2维特比译码原理 采用概率译码的基本思想是:把已接收序列与所有可能的发送序列做比较,选择其中码距最小的一个序列作为发送序列。如果发送L组信息比特,那么对于(n,k)卷积码来说,可能发送的序列有2kL个,计算机或译码器需存储这些序列并进行比较,以找到码距最小的那个序列。当传信率和信息组数L较大时,使得译码器难以实现。维特比算法则对上述概率译码做了简化,以至成为了一种实用化的概率算法。它并不是在网格图上一次比较所有可能的2kL条路径(序列),而是接收一段,计算和比较一段,选择一段最大似然可能的码段,从而达到整个码序列是一个最大似然值得序列。 下面以图2.1的(2,1,3)卷积码编码器所编出的码为例,来说明维特比解码的方法和运作过程。为了能说明解码过程,这里给出该码的状态图,如图2.2所

1、F PGA技术简介 现场可编程门阵列FPGA是80年代末开始使用的大规模可编程数字IC器件,它充分利用EDA技术进行器件的开发与应用。用户借助于计算机不仅能自行设计自己的专用集成电路芯片,还可在计算机上进行功能仿真和时序仿真,及时发现问题,调整电路,改进设计方案。这样,设计者不必动手搭接电路、调试验证,只需短时间内在计算机上操作即可设计出与实际系统相差无几的理想电路。而且,FPGA器件采用标准化结构,体积小、集成度高、功耗低、速度快,可无限次反复编程,因此成为科研产品开发及其小型化的首选器件,其应用极为广泛。 3.1 FPGA工作原理 FPGA采用了逻辑单元阵列LCA(Logic Cell Array)这样一个概念,内部包括可配置逻辑模块CLB(Configurable Logic Block)、输入输出模块IOB(Input Output Block)和内部连线(Interconnect)三个部分。现场可编程门阵列(FPGA)是可编程器件,与传统逻辑电路和门阵列(如PAL,GAL及CPLD器件)相比,FPGA具有不同的结构。FPGA利用小型查找表(16×1RAM)来实现组合逻辑,每个查找表连接到一个D触发器的输入端,触发器再来驱动其他逻辑电路或驱动I/O,由此构成了既可实现组合逻辑功能又可实现时序逻辑功能的基本逻辑单元模块,这些模块间利用金属连线互相连接或连接到I/O模块。FPGA的逻辑是通过向内部静态存储单元加载编程数据来实现的,存储在存储器单元中的值决定了逻辑单元的逻辑功能以及各模块之间或模块与I/O间的联接方式,并最终决定了FPGA所能实现的功能,FPGA允许无限次的编程。 3.2 FIR滤波器特点 1)采用FPGA设计ASIC电路(专用集成电路),用户不需要投片生产,就能得到合用的芯片。 2)FPGA可做其它全定制或半定制ASIC电路的中试样片。 3)FPGA内部有丰富的触发器和I/O引脚。 4)FPGA是ASIC电路中设计周期最短、开发费用最低、风险最小的器件之一。 5) FPGA采用高速CMOS工艺,功耗低,可以与CMOS、TTL电平兼容。同时,FPGA还存在以下五大优势。 1)性能:利用硬件并行的优势,FPGA打破了顺序执行的模式,在每个时钟周 期内完成更多的处理任务,超越了数字信号处理器(DSP)的运算能力。著名 的分析与基准测试公司BDTI,发布基准表明在某些应用方面,FPGA每美元的 处理能力是DSP解决方案的多倍。2在硬件层面控制输入和输出(I/ O)为满足应用需求提供了更快速的响应时间和专业化的功能。 2)上市时间:尽管上市的限制条件越来越多,FPGA技术仍提供了灵活性和快 速原型的能力。用户可以测试一个想法或概念,并在硬件中完成验证,而无需

卷积码的编解码Matlab仿真摘要 卷积码是一种性能优越的信道编码。它的编码器和译码器都比较容易实现,同时它具有较强的纠错能力D随着纠错编码理论研究的不断深入,卷积码的实际应用越来越广泛。本文简明地介绍了卷积码的编码原理和译码原理o并在SIMULINK模块设计中,完成了对卷积码的编码和译码以及误比特统计整个过程的模块仿真。最后,通过在仿真过程中分别改变卷积码的重要参数来加深理解卷积码的这些参数对卷积码的误码性能的影响。经过仿真和实测,并对测试结果作了分析。得出了以下三个结论z (1)当改变卷积码的码率时,系统的误码性能也将随之发生变化。 (2)对于码率一定的卷积码,当约束长度N发生变化时,系统的误码性能也会随之发生变化。 (3)回溯长度也会不同程度上地影响误码性能。 关键词:卷积码:码率:约束长度:回溯长度

Simulation and Research on Encoding and Decoding of Convolution Code Abstract Convolution code has a superior performance of the channel code. It is easy to coding and decoding.An d it has a strong ability to correct e盯ors. As correcting coding theory has a long development,the practice of convolution code is more and more extensive.In由1S由esis,the principle of convolution coding and decoding is introduced simply白rstly. Then由e whole simulation module process of encoding,decoding and the Error Rate Calculation is completed in由is design. Finally,in order to understand 由eir performances of error rate,many changes in parameters of convolution code are calculated in the simulation process.Af ter simulation and me皿UTe,an analysis of test results is presented.Th e following由ree conclusions are draw: (l)Wh en the rate of convolution Code ch皿ges,HER performance of the systemwill change. (2) For a certain rate of convolution code,when由ere is a change in the constraint length of N,BER perfonnance of由e system will change. (3) Re位ospec咀ve length will affect BE R. Key words: convolution code; rate; cons缸aint leng由; retrospective length;

实验九 (2,1,5)卷积码编码译码技术 一、实验目的 1、掌握(2,1,5)卷积码编码译码技术 2、了解纠错编码原理。 二、实验内容 1、(2,1,5)卷积码编码。 2、(2,1,5)卷积码译码。 三、预备知识 1、纠错编码原理。 2、(2,1,5)卷积码的工作原理。 四、实验原理 卷积码是将发送的信息序列通过一个线性的,有限状态的移位寄存器而产生的编码。通常卷积码的编码器由K级(每级K比特)的移位寄存器和n个线性代数函数发生器(这里是模2加法器)组成。 若以(n,k,m)来描述卷积码,其中k为每次输入到卷积编码器的bit数,n 为每个k元组码字对应的卷积码输出n元组码字,m为编码存储度,也就是卷积编码器的k元组的级数,称m+1= K为编码约束度m称为约束长度。卷积码将k 元组输入码元编成n元组输出码元,但k和n通常很小,特别适合以串行形式进行传输,时延小。与分组码不同,卷积码编码生成的n元组元不仅与当前输入的k元组有关,还与前面m-1个输入的k元组有关,编码过程中互相关联的码元个数为n*m。卷积码的纠错性能随m的增加而增大,而差错率随N的增加而指数下降。在编码器复杂性相同的情况下,卷积码的性能优于分组码。 编码器 随着信息序列不断输入,编码器就不断从一个状态转移到另一个状态并同时输出相应的码序列,所以图3所示状态图可以简单直观的描述编码器的编码过程。因此通过状态图很容易给出输入信息序列的编码结果,假定输入序列为110100,首先从零状态开始即图示a状态,由于输入信息为“1”,所以下一状态为b并输出“11”,继续输入信息“1”,由图知下一状态为d、输出“01”……其它输入信息依次类推,按照状态转移路径a->b->d->c->b->c->a输出其对应的编码结果“110101001011”。 译码方法 ⒈代数 代数译码是将卷积码的一个编码约束长度的码段看作是[n0(m+1),k0(m+1)]线性分组码,每次根据(m+1)分支长接收数字,对相应的最早的那个分支上的信息数字进行估计,然后向前推进一个分支。上例中信息序列 =(10111),相应的码序列 c=(11100001100111)。若接收序列R=(10100001110111),先根据R 的前三个分支(101000)和码树中前三个分支长的所有可能的 8条路径(000000…)、(000011…)、(001110…)、(001101…)、(111011…)、(111000…)、(110101…)和(110110…)进行比较,可知(111001)与接收

湖南文理学院课程设计报告 课程名称:通信系统课程设计 院部:电气与信息工程学院 专业班级: 学生姓名: 指导教师: 完成时间: 2011 年 12 月 29日 报告成绩:

目录 目录 (2) 摘要 (3) Abstract (4) 一、引言 (5) 1.1设计任务及基本要求 (5) 1.2设计目的 (6) 1.3 设计所用仪器设备.................................................................................. 错误!未定义书签。 二、基本概念 (6) 2.1 卷积码的编码原理 (6) 2.2 卷积码编码描述 (6) 2.3 卷积码译码描述 (6) 三、卷积码的编译码原理 (6) 3.1卷积码的图形描述 (6) 3.1.1 树状图 (8) 3.1.2 网格图 (8) 3.1.3 状态图 (9) 3.2 卷积积码的编码算法 (9) 3.3卷积码的Viterbi译码 (10) 四、卷积码的仿真及性能分析 (12) 4.1 SIMULINK仿真模块 (12) 4.2 卷积码的参数对误码率的影响 (13) 4.2.1 码率对误码性能的影响 (13) 4.2.2 约束长度对误码性能的影响 (15) 4.2.3 回溯长度对卷积码性能的影响 (16) 4.3 仿真分析 (17) 总结 (18) 参考文献: (19)

摘要 卷积码是深度空间通信系统和无线通信系统中常用的一种差错控制编码。在编码过程中,卷积码充分利用了各码字间的相关性。在与分组码同样的码率和设备复杂性的条件下,无论从理论上还是从实践上都证明,卷积码的性能都比分组码具有优势。而且卷积码在实现最佳译码方面也较分组码容易。因此卷积码广泛应用于卫星通信,CDMA数字移动通信等通信系统,是很有前途的一种编码方式。对其进行研究有很大的现实意义。为了解决传统的维特比译码器结构复杂、译码速度慢、消耗资源大的问题,提出一种新型的适用于FPGA 特点,路径存储于译码输出并行工作,同步存储路径矢量和状态矢量的译码器设计方案。该设计方案通过在ISE.2i中仿真验证,译码结果正确,得到编码前的原始码元,速度显著提高,译码器复杂程度明显降低。并在实际的软件无线电通信系统中信道编解码部分得到应用,性能优良。 关键词:卷积码;误码性能;原理

摘要 自适应滤波器是统计信号处理的一个重要组成部分。在现代滤波处理技术中,自适应滤波器的处理效果尤为突出。在众多滤波器中,特别是在一些对信号处理的实时性要求比较高,体积功耗有严格限制的场合,使用FPGA硬件实现的数字滤波器更为广泛。 本论文从自适应滤波器研究的重要意义入手,介绍了线性自适应滤波器的算法,对几种基于最小均方误差准则或最小平方误差准则的自适应滤波器算法进行研究,就滤波器的基本原理及设计方法做了简单的介绍,最终设计基于FPGA的LMS算法设计复数自适应滤波器,对设计方法进行叙述,并以VHDL语言编写程序进行仿真测试。 关键词:自适应滤波器;FPGA;自适应算法LMS;有限冲激响应滤波器

FPGA-based design of adaptive filter Student:TAN xx Teacher:CHEN xx Abstract:Adaptive filter is a statistical signal processing as an important component. Processing technology in the modern filter, the adaptive filter, particularly in the treatment effect. Among the filters, especially in some of the real-time signal processing requirements of higher power, there are strict restrictions on the size of the occasion, the use of FPGA hardware to achieve a wider range of digital filters. In this paper, adaptive filter from the importance of research to start to introduce the linear adaptive filter algorithm, based on several criteria MMSE or least square error criteria for the study of adaptive filter algorithm, it filters The basic principle and design method of a brief introduction, the final design of FPGA-based design of complex LMS adaptive filter algorithm, the design methods described, and VHDL languages in maxplus simulation test platform. Keywords: adaptive filter;FPGA;LMS adaptive algorithm;finite impulse response filter

基于MATLAB的卷积码的分析与应用

毕业设计(论文)任务书

基于MATLAB的卷积码的分析与应用 摘要 随着现代通信的发展,特别是在未来4G通信网络中,高速信息传输和高可靠性传输成为信息传输的两个主要方面,而可靠性尤其重要。因为信道状况的恶劣,信号不可避免会受到干扰而出错。为实现可靠性通信,主要有两种途径:一种是增加发送信号的功率,提高接收端的信号噪声比;另一种是采用编码的方法对信道差错进行控制。前者常常受条件限制,不是所有情况都能采用。因此差错控制编码得到了广泛应用。 介绍了多种信道编码方式,着重介绍了卷积码的编码方法和解码方式。介绍了MATLAB的使用方法、编程方法、语句、变量、函数、矩阵等。介绍了TD-SCDMA通信系统和该系统下的卷积码,搭建了系统通信模型。编写卷积码的编码和解码程序。用MATLAB仿真软件对TD-SCDMA系统的卷积码编解码进行仿真。对其纠正错码性能进行验证,并且对误码率进行仿真和分析。卷积码的编码解码方式有很多,重点仿真Viterbi算法。Viterbi算法就是利用卷积码编码器的格图来计算路径度量,选择从起始时刻到终止时刻的惟一幸存路径作为最大似然路径。沿着最大似然路径回溯到开始时刻,所走过的路径对应的编码输出就是最大似然译码输出序列。它是一种最大似然译码方法,当编码约束长度不大、或者误码率要求不是很高的情况下,Viterbi译码器设备比较简单,计算速度快,因而Viterbi译码器被广泛应用于各种领域。 关键词:卷积码;信道编码;TD-SCDMA;MATLAB

目录 毕业设计(论文)任务书 ............................................................................................I 摘要........................................................................................................................... II Abstract......................................................................................... 错误!未定义书签。第1章绪论 . (1) 1.1课题研究的背景和来源 (1) 1.2主要内容 (2) 第2章相关理论介绍 (3) 2.1信道编码 (3) 2.1.1 信道编码的分类 (3) 2.1.2 编码效率 (3) 2.2线性分组码 (3) 2.3循环码 (5) 2.4卷积码 (6) 2.4.1 卷积码简介 (7) 2.4.2 卷积码的编码 (7) 2.4.3 卷积码的解码 (13) 第3章MATLAB应用 (21) 3.1数和算术的表示方法 (21) 3.2向量与矩阵运算 (21) 3.2.1 通过语句和函数产生 (21) 3.2.2 矩阵操作 (22) 3.3矩阵的基本运算 (22) 3.3.1 矩阵乘法 (22) 3.3.2 矩阵除法 (23) 3.4MATLAB编程 (23) 3.4.1 关系运算 (23) 3.4.2 控制流 (25) 第4章卷积码的设计与仿真 (27) 4.1TD-SCDMA系统 (27) 4.1.1 系统简介 (27) 4.1.2 仿真通信系统模型 (27)

本科生毕业论文(设计) 题目:MATLAB实现卷积码编译码 专业代码: 作者姓名: 学号: 单位: 指导教师: 年月日

目录 前言----------------------------------------------------- 1 1. 纠错码基本理论---------------------------------------- 2 1.1纠错码基本理论 ----------------------------------------------- 2 1.1.1纠错码概念 ------------------------------------------------- 2 1.1.2基本原理和性能参数 ----------------------------------------- 2 1.2几种常用的纠错码 --------------------------------------------- 6 2. 卷积码的基本理论-------------------------------------- 8 2.1卷积码介绍 --------------------------------------------------- 8 2.1.1卷积码的差错控制原理----------------------------------- 8 2.2卷积码编码原理 ---------------------------------------------- 10 2.2.1卷积码解析表示法-------------------------------------- 10 2.2.2卷积码图形表示法-------------------------------------- 11 2.3卷积码译码原理---------------------------------------------- 15 2.3.1卷积码三种译码方式------------------------------------ 15 2.3.2V ITERBI译码原理---------------------------------------- 16 3. 卷积码编译码及MATLAB仿真---------------------------- 18 3.1M ATLAB概述-------------------------------------------------- 18 3.1.1M ATLAB的特点------------------------------------------ 19 3.1.2M ATLAB工具箱和内容------------------------------------ 19 3.2卷积码编码及仿真 -------------------------------------------- 20 3.2.1编码程序 ---------------------------------------------- 20 3.3信道传输过程仿真-------------------------------------------- 21 3.4维特比译码程序及仿真 ---------------------------------------- 22 3.4.1维特比译码算法解析------------------------------------ 23 3.4.2V ITERBI译码程序--------------------------------------- 25 3.4.3 VITERBI译码MATLAB仿真----------------------------------- 28 3.4.4信噪比对卷积码译码性能的影响 -------------------------- 28

湖南文理学院 课程设计报告 课程名称:通信系统课程设计 专业班级:通信工程11102班09 学生姓名:朱涛 指导教师:侯清莲 完成时间:2014-11-18 报告成绩:

目录 一、设计要求 (1) 二、设计作用与目的 (1) 三、所用设备及软件 (1) 四、卷积码编码的概念 (1) 4.1卷积码的编码描述方法 (1) 4.2 卷积编码 (2) 4.3 卷积码的树状图 (3) 4.4 卷积码的网格图 (3) 五、 EDA设计方法及工具软件QUARTUSⅡ (4) 六、改变卷积编码器的参数仿真以及结论 (4) 6.1 不同回溯长度对卷积编码器性能的影响 (4) 6.2 不同码率对卷积编码器误码性能的影响 (5) 6.3 不同约束长度对卷积编码器的误码性能影响 (6) 七、卷积码编码器的VHDL设计与仿真 (8) 7.1 VHDL设计的优点与设计方法 (8) 7.2 卷积码编码器的VHDL实现 (10) 八、心得体会 (10) 九、参考文献 (11)

卷积编码器的设计 一、设计要求 (1)画出卷积码的原理框图,说明系统中各主要组成部分的功能。 (2)使用EDA技术及VHDL语言对卷积编码器进行设计与仿真并对结果分析。 二、设计作用与目的 (1)巩固加深对通信基本知识分析以及卷积码的掌握,提高综合运用通信知识的能力。(2)掌握采用仿真软件对系统进行仿真分析。 (3)培养学生查阅参考文献,独立思考,设计,钻研电子技术相关问题的能力。 (4)掌握相关电子线路工程技术规范以及常规电子元器件的性能技术指标。 (5)培养严肃认真的工作作风与科学态度,建立严谨的工程技术观念。 (6)了解电气图国家标准,并利用电子CAD等正确绘制电路图。 (7)培养工程实践能力,创新能力与综合设计能力。 三、所用设备及软件 (1)QUARTUSⅡ (2)PC机 四、卷积码编码的概念 4.1卷积码的编码描述方法 编码描述方法有5种:冲激响应描述法、生成矩阵描述法、多项式乘积描述法、状态图描述法和网格图描述法。卷积码的纠错能力随着N的增加而增大,而差错率随着N的增加而指数下降。在编码器复杂性相同的情况下,卷积码的性能优于分组码。分组码有严格的代数结构,但卷积码至今尚未找到如此严密的数学手段。分组码的译码算法可以由其代数特性得到。卷积码虽然可以采用适用于分组码的门限译码(即大数逻辑译码),但性能不如维特比译码和序列译码[2]。 以二元码为例,输入信息序列为u=(u0,u1,…),其多项式表示为u(x)=u0+u1x+…+…。编码器的连接可用多项式表示为g (1,1) (x)=1+x+x2和g(1,2)(x)=1+x2,称为码的子生 成多项式。它们的系数矢量g (1,1)=(111)和g (1,2) =(101)称作码的子生成元。以子生成多项式 为阵元构成的多项式矩阵G(x)=[g (1,1)(x),g (1,2) (x)],称为码的生成多项式矩阵。由生成 元构成的半无限矩阵。

基于System View的卷积码译码器的设计 摘要本课程设计在SystemView 平台上设计了卷积码译码器,SystemView系统中提供了专门的卷积码编码和译码图符,使用户能快速地建立基于卷积码的仿真系统,本课程设计对(2,1,6)的大数逻辑译码原理,以及维比特译码原理进行了解释,利用SystemView 进行了(2,1,3)卷积码译码器的仿真。系统运行以后将译码后得到的波形与原始的码元输入信号进行比较,系统参数经过修改以后能够正确地将编码后的信号译码为原始的码元。 关键字卷积码译码器,System View,(2,1,3)卷积码译码器 1 引言 卷积码的译码方法主要有两类,代数译码和概率译码。代数译码是根据卷积码的本身编码结构进行译码,译码时不考虑信道的统计特性。概率译码在计算时要考虑信道的统计特性。典型的算法如:最大似然译码、维比特译码、序列译码等。本课程设计利用SystemView 平台进行卷积码译码器的实现,SystemView系统中提供了专门的卷积码编码和译码图符,使用户能快速地建立基于卷积码的仿真系统,本课程设计对(2,1,6)的大数逻辑译码原理,以及维比特译码原理进行了解释,利用System View进行了(2,1,3)卷积码译码仿真,系统参数经过修改以后能够正确地将编码后的信号译码为原始的码元。 1.1 卷积码简介 卷积码也称为连环码是一种非分组码,分组码编码时,先将输入的信息序列分为长度为k的码元的字段,然后按照一定的编码规则,给含k个信息元的段附加上r长的监督元,于是生成n 长的码组。在编码时,各n长码组是分别编码的,各码组之间没有约束关系,因此译码时各码组之间是分别独立进行的。卷积码则不同于此,卷积编码属于信道编码,主要用来纠正码元的随机差错,它是以牺牲效率来换取可靠性的,利用增加监督位,进行检错和纠错。卷积码把k个信息位编成n位,k和n通常很小,特别适宜于串行形式传输,延时小,n个码元与当前段的k个信息位有关,而且与前N-1段的信息有关,编码过程相互关联的码元为Nn个,N或Nn称为卷积码的约束长度,常把卷

基于FPGA的数字滤波器的设计Graduation Design(Thesis) of Chongqing University Design of Digital Filter Based on FPGA Undergraduate: Huang Jianhua Supervisor: Yang Lisheng Major:ElectronicInformation Engineering

College of Communication Engineering Chongqing University June 2013

摘要 数字信号处理在通信、雷达、声纳等中有着广泛的应用。数字滤波器的设计是数字信号处理的关键技术之一,有着十分重要的理论和实际意义。随着数字技术的不断发展,在许多场合,数字滤波器正在快速取代模拟滤波器。FPGA(现场可编程门阵列)在现代数字电路设计中发挥着越来越重要的作用。从设计简单的接口电路到设计复杂的状态机,FPGA所扮演的角色已经不容忽视。 本论文完成了基于FPGA的FIR和IIR数字滤波器的设计与实现。本论文首先理论分析讨论了数字滤波器的设计方法,并使用MATLAB工具验证采用哪种窗函数来设计FIR数字滤波器,使用哪种模拟滤波器原型映射IIR数字滤波器。然后根据模拟滤波器的技术指标来确定数字滤波器的技术指标,在MATLAB环境下按照数字滤波器的技术指标设计数字滤波器,并得到滤波器系数,编程实现系数量化,并且比较分析量化前后系统响应的差异,由此得到合适的量化等级。然后在ISE软件平台下根据MATLAB工具得到的量化系数,使用VHDL语言进行FIR和IIR滤波器算法模块编程,同时对AMP电路(可编程预放大器)模块、AD电路(模拟到数字转换器)模块和DA电路(数字到模拟转换器)模块分别进行编程配置,并且对各模块进行严格的软件仿真验证,其中AMP电路模块、AD电路模块和DA电路模块必须进行硬件验证。最后将所有软件和硬件验证无误的模块整合,下载到FPGA硬件中,进行功能验证。验证结果符合设计要求。 关键词:FIR滤波器,IIR滤波器,MATLAB,FPGA,VHDL

卷积码的编解码仿真与研究 摘要 卷积码是一种性能优越的信道编码。它的编码器和译码器都比较容易实现,同时它具有较强的纠错能力。随着纠错编码理论研究的不断深入,卷积码的实际应用越来越广泛。本文简明地介绍了卷积码的编码原理和译码原理。并在SIMULINK模块设计中,完成了对卷积码的编码和译码以及误比特统计整个过程的模块仿真。最后,通过在仿真过程中分别改变卷积码的重要参数来加深理解卷积码的这些参数对卷积码的误码性能的影响。经过仿真和实测,并对测试结果作了分析。得出了以下三个结论: (1)当改变卷积码的码率时,系统的误码性能也将随之发生变化。 (2)对于码率一定的卷积码,当约束长度N 发生变化时,系统的误码性能也会随之发生变化。 (3)回溯长度也会不同程度上地影响误码性能。 关键词:卷积码;码率;约束长度;回溯长度

Simulation and Research on Encoding and Decoding of Convolution Code Abstract Convolution code has a superior performance of the channel code. It is easy to coding and decoding. And it has a strong ability to correct errors. As correcting coding theory has a long development, the practice of convolution code is more and more extensive. In this thesis, the principle of convolution coding and decoding is introduced simply firstly. Then the whole simulation module process of encoding, decoding and the Error Rate Calculation is completed in this design. Finally, in order to understand their performances of error rate, many changes in parameters of convolution code are calculated in the simulation process. After simulation and measure, an analysis of test results is presented. The following three conclusions are draw: (1) When the rate of convolution Code changes, BER performance of the system will change. (2) For a certain rate of convolution code, when there is a change in the constraint length of N, BER performance of the system will change. (3) Retrospective length will affect BER. Key words: convolution code; rate; constraint length; retrospective length;

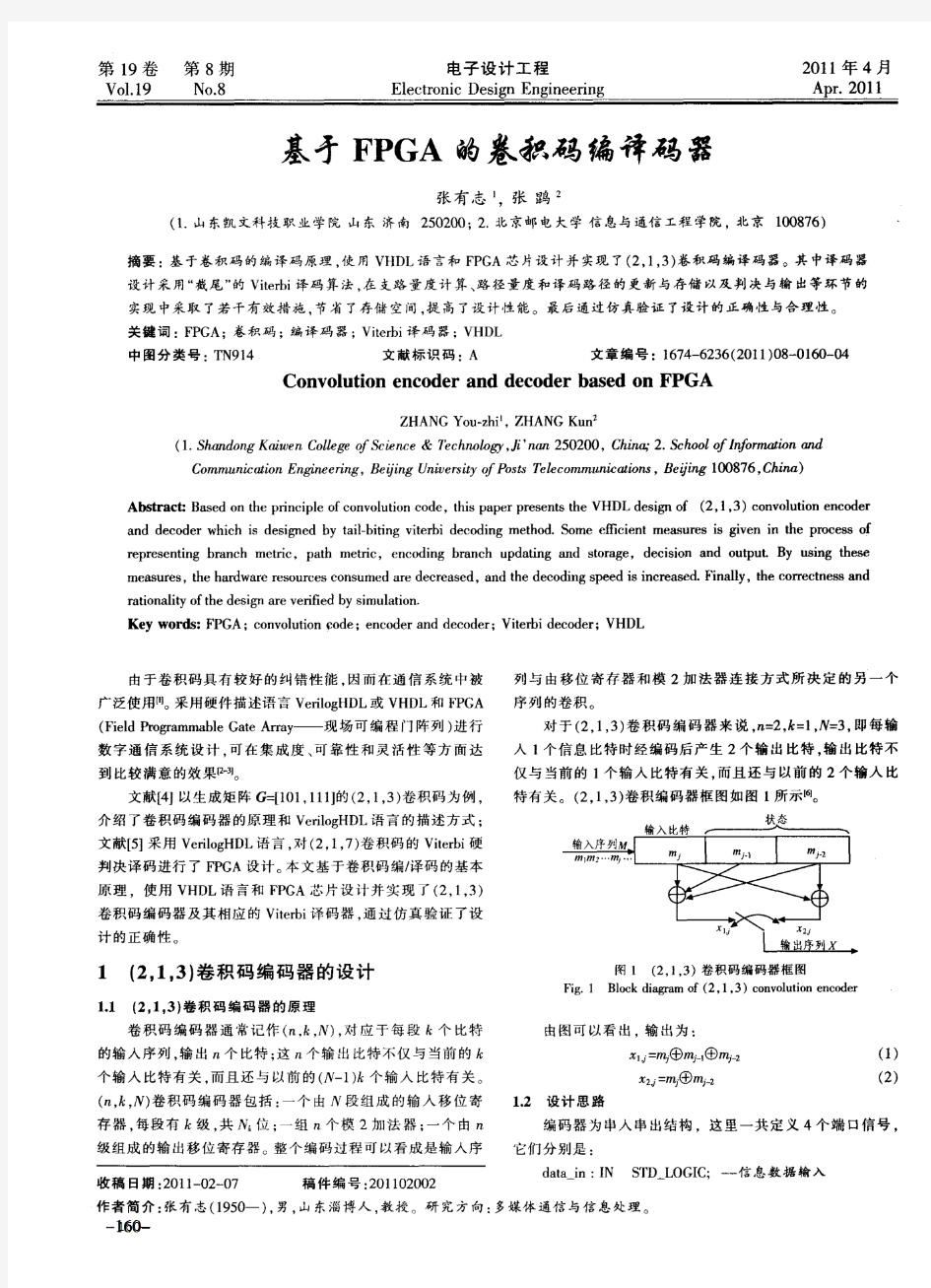

实验四 卷积码的编解码 一、实验目的 1、掌握卷积码的编解码原理。 2、掌握卷积码的软件仿真方法。 3、掌握卷积码的硬件仿真方法。 4、掌握卷积码的硬件设计方法。 二、预习要求 1、掌握卷积码的编解码原理和方法。 2、熟悉matlab 的应用和仿真方法。 3、熟悉Quatus 的应用和FPGA 的开发方法。 三、实验原理 1、卷积码编码原理 在编码器复杂度相同的情况下,卷积码的性能优于分组码,因此卷积码几乎被应用在所有无线通信的标准之中,如GSM , IS95和CDMA 2000 的标准中。 卷积码通常记作( n0 , k0 , m) ,它将k 0 个信息比特编为n 0 个比特, 其编码效率为k0/ n0 , m 为约束长度。( n0 , k0 , m ) 卷积码可用k0 个输入、n0 个输出、输入存储为m 的线性有限状态移位寄存器及模2 加法计数器来实现。 本实验以(2,1,3)卷积码为例加以说明。图1就是卷积码编码器的结构。 图1 (2,1,3)卷积码编码器 其生成多项式为: 21()1G D D D =++; 2 2()1G D D =+; 如图1 所示的(2,1,3)卷积码编码器中,输入移位寄存器用转换开关代替,每输入一个信息比特经编码产生二个输出比特。假设移位寄存器的初始状态为全0,当第一个输入比特为0时,输出比特为00;若输入比特为1,则输出比特为11。随着第二个比特输入,第一个比特右移一位,此时输出比特同时受到当前输入比特和前一个输入比特的影响。第三个比特输入时,第一、二个比特分别右移一位,同时输出二个由这三位移位寄存器存储内容所共同决定的比特。依次下去就完成了编码过程。 下面是卷积码的网格图表示。他是比较清楚而又紧凑的描述卷积码的一种方式,它是最常用的描述方

目录 引言 (4) 第一章FPGA的设计流程 (5) 1.1 FPGA概述 (5) 1.2 FPGA设计流程 (9) 1.3硬件描述语言HDL(Hardware Description Language) (10) 1.4 FPGA开发工具Quartus Ⅱ软件设计流程 (13) 第二章有限冲激响应(FIR)滤波器的原理及设计 (16) 2.1数字信号处理基础原理 (16) 2.2 FIR滤波器背影知识 (19) 2.3 FIR数字滤波器原理 (21) 2.4 利用窗函数法设计FIR滤波器 (26) 第三章FIR 数字滤波器的FPGA实现 (31) 3.1串行FIR滤波器原理 (31) 3.2分布式算法基础 (32) 3.3直接型FIR滤波器的原理结构图 (34) 3.4具有转置结构的FIR滤波器 (36) 第四章结论与总结 (40) 谢辞 (42) 参考文献 (43)

摘要:本论文课题是《基于FPGA的FIR滤波器设计与实现》。数字滤波器是语音与图象处理、模式识别、雷达信号处理、频谱分析等应用中的一种基本的处理部件,它能满足滤波器对幅度和线性相位的严格要求,避免模拟滤波器所无法克服的电压漂移、温度漂移和噪声等问题。有限冲激响应(FIR)滤波器能在设计任意幅频特性的同时保证严格的线性相位特性。因此在许多应用领域都显示了强大的生命力,具有重要应用意义。本文介绍了用VHDL实现线性相位FIR(有限长单位冲激响应)滤波器。提出了一种基于FPGA的FIR滤波器设计方案。介绍了基于FPGA的FIR滤波器的数字信号处理的算法设计,采用直接型和转置型的基本结构来设计,其运算效率明显提高,并结合先进的EDA软件进行高效的设计和实现,并给出了用Quartus Ⅱ运行的仿真结果。该设计对FPGA硬件资源的利用高效合理,用VHDL编程,在PFGA中实现了高采样率的FIR滤波器。关键字:FIR滤波器;FPGA;VHDL;MATLAB;Quartus Ⅱ

学士学位论文论文题目: 基于FPGA的数字滤波器设计 院 (部)名称:电气信息工程学院 学生姓名: 专业:测控技术与仪器学号: 指导教师姓名:

摘要 本论文设计了一个基于FPGA(现场可编程逻辑门阵列)FIR(有限脉冲响应)31阶低通滤波器,通带截止频率为0.1MHz,通带波纹最大1dB,阻带最小衰减-50dB,数据的输入输出宽度为8位,采样频率5MHz。 滤波器分为模拟滤波器和数字滤波器,在信号系统邻域中,一般除了A/D 转换前期的滤波和D/A转换后的滤波使用模拟滤波器,基本上其他的滤波一般优先考虑数字滤波器。数字滤波器与模拟滤波器相比有许多的优点:频域易控制,性能指标好;容易实现线性相位的系统,而且稳定,基本上不受外界影响;可重用性和灵活性比较高,只需编程就可以修改其特性,设计周期短。 数字滤波是推动数字信号处理与相关芯片快速发展的一个要素。本论文的FPGA芯片选用Altera公司Cyclone2系列的EP2C8Q208C8N芯片,模数转换使用ADC9280,数模转换使用DAC9708,来实现数字滤波器,FPGA与ASIC、DSP相比,具有明显的优势,在功耗,体积,成本都优于ASIC、DSP,并且处理效率高,可编程性好,并行处理能力非常强,能完成DSP很难完成的许多功能。 本论文首先简单的介绍数字滤波器、FIR滤波器、FIR的窗口函数选择以及FPGA分布式算法的实现,并对系统硬件各功能模块进行了说明;然后根据系统总体设计的要求指标,使用MATLAB来设计确定系数,因为FPGA不能表示浮点数,所以对系数进行了量化,使用verilog HDL硬件语言编程,Modelsim进行功能仿真;最后使用实物来验证结果,并达到预期的目的。 关键词:FPGA,FIR滤波器,MATLAB,分布式算法

西南科技大学 方向设计报告 课程名称:通信工程方向设计 设计名称:2/3卷积码编译码器仿真与性能分析 姓名: 学号: 班级: 指导教师: 起止日期:2011.12.12-2012.1.6 西南科技大学信息工程学院制

方向设计任务书 学生班级:学生姓名:学号: 设计名称:2/3卷积码编译码器仿真与性能分析 起止日期:2011.12.12-2012.1.6指导教师: 设计要求: (1)分析2/3卷积码编码器结构; (2)分析2/3卷积码译码的Viterbi算法; (3)基于SIMULINK进行2/3卷积码的纠错性能仿真; 方向设计学生日志 时间设计内容 12.15-12.17 查看题目及设计要求。 12.18-12.23 查阅相关资料,设计方案。 12.23-12.27 编写报告及调试程序。 12.28-12.29 完善修改课程设计报告。 12.30-12.31 答辩。

方向设计考勤表 周星期一星期二星期三星期四星期五 方向设计评语表 指导教师评语: 成绩:指导教师: 年月日

2/3卷积码编译码器仿真与性能分析 摘要: 卷积码是一种性能优越的信道编码。它的编码器和译码器都比较容易实现,同时它具有较强的纠错能力。随着纠错编码理论研究的不断深入,卷积码的实际应用越来越广泛。本文简明地介绍了卷积码的编码原理和Viterbi译码原理。并在SIMULINK模块设计中,完成了对卷积码的编码和译码以及误比特统计整个过程的模块仿真。最后,通过在仿真过程中分别改变卷积码的重要参数来加深理解卷积码的这些参数对卷积码的误码性能的影响。经过仿真和实测,并对测试结果作了分析。 关键词: 卷积码编码器、viterbi译码器、SIMULINK