基于System View的卷积码译码器的设计

摘要本课程设计在SystemView 平台上设计了卷积码译码器,SystemView系统中提供了专门的卷积码编码和译码图符,使用户能快速地建立基于卷积码的仿真系统,本课程设计对(2,1,6)的大数逻辑译码原理,以及维比特译码原理进行了解释,利用SystemView 进行了(2,1,3)卷积码译码器的仿真。系统运行以后将译码后得到的波形与原始的码元输入信号进行比较,系统参数经过修改以后能够正确地将编码后的信号译码为原始的码元。

关键字卷积码译码器,System View,(2,1,3)卷积码译码器

1 引言

卷积码的译码方法主要有两类,代数译码和概率译码。代数译码是根据卷积码的本身编码结构进行译码,译码时不考虑信道的统计特性。概率译码在计算时要考虑信道的统计特性。典型的算法如:最大似然译码、维比特译码、序列译码等。本课程设计利用SystemView 平台进行卷积码译码器的实现,SystemView系统中提供了专门的卷积码编码和译码图符,使用户能快速地建立基于卷积码的仿真系统,本课程设计对(2,1,6)的大数逻辑译码原理,以及维比特译码原理进行了解释,利用System View进行了(2,1,3)卷积码译码仿真,系统参数经过修改以后能够正确地将编码后的信号译码为原始的码元。

1.1 卷积码简介

卷积码也称为连环码是一种非分组码,分组码编码时,先将输入的信息序列分为长度为k的码元的字段,然后按照一定的编码规则,给含k个信息元的段附加上r长的监督元,于是生成n 长的码组。在编码时,各n长码组是分别编码的,各码组之间没有约束关系,因此译码时各码组之间是分别独立进行的。卷积码则不同于此,卷积编码属于信道编码,主要用来纠正码元的随机差错,它是以牺牲效率来换取可靠性的,利用增加监督位,进行检错和纠错。卷积码把k个信息位编成n位,k和n通常很小,特别适宜于串行形式传输,延时小,n个码元与当前段的k个信息位有关,而且与前N-1段的信息有关,编码过程相互关联的码元为Nn个,N或Nn称为卷积码的约束长度,常把卷

积码记作(n,k,N) ,一般来说对于卷积码k 和n 时较小的整数,常把卷积码记作(n 、k 、

N)卷积码,它的编码效率为k/n 。

1.2 卷积码的译码原理

卷积码的译码方法有两类:一类是大数逻辑译码,又称门限译码;另一类是概率译

码,概率译码又分为维比特译码和序列译码两种。门限译码方法是以分组码理论为基础

的,其译码设备简单且速度较快,但是误码性能要比概率译码法差。

(1) 大数逻辑译码

该译码方法是从线性码的伴随式出发,找到一组特殊的能够检查信息位置是否发

生错误的方程组,从而实现纠错译码。下面通过一各例子来说明该译码的工作原理。设

有(2,1,6)卷积码的编码器,它的监督矩阵为:

H=?????????

???????????111010100000101000001110000011000011001111 像分组码那样,由H 可得伴随式EH T ,E=(e 11,e 21,e 12,e 22….e 16,e 26)是信道传输后所

产生得错误图样。这样就有式中EH T =S=(S1,S2,S3,S4,S5,S6)

S1= e 11+ e 21

S2= e 12+ e 22

S3= e 13+e 23

S4= e 11+e 14+e 24

S5= e 11+ e 12+e 15+e 25

S6= e 11+ e 12+ e 13+e 16+e 26

由上面的方程,可以得到下列方程2:

S1= e 11+ e 21

S4= e 11+e 14+e 24

S5= e 11+ e 12+e 15+e 25

S2+ S6=e

11+ e

22

+ e

13

+ e

16

+e

26

该方程的特点是,错误元e

11

在各个方程中都出现,其他的错误元在方程中出现的次

数不超过一次,我们称具有该特点的方程为正交于e

11

错误元的一致检验和。这样一来,

在相邻的12个码元中,若错误图样E中的错误个数不多余2个,且其中一个发生在e

11位上,那么方程组2中至少有三个方程位,即∑Si大于或等于3。如果E中错误个数不

多于2个,且e

11

位上未发生错误,则方程组中的的∑Si小于或等于2,由此可以根据∑Si来进行大数判决,以决定对收到e11进行纠正或不纠正。

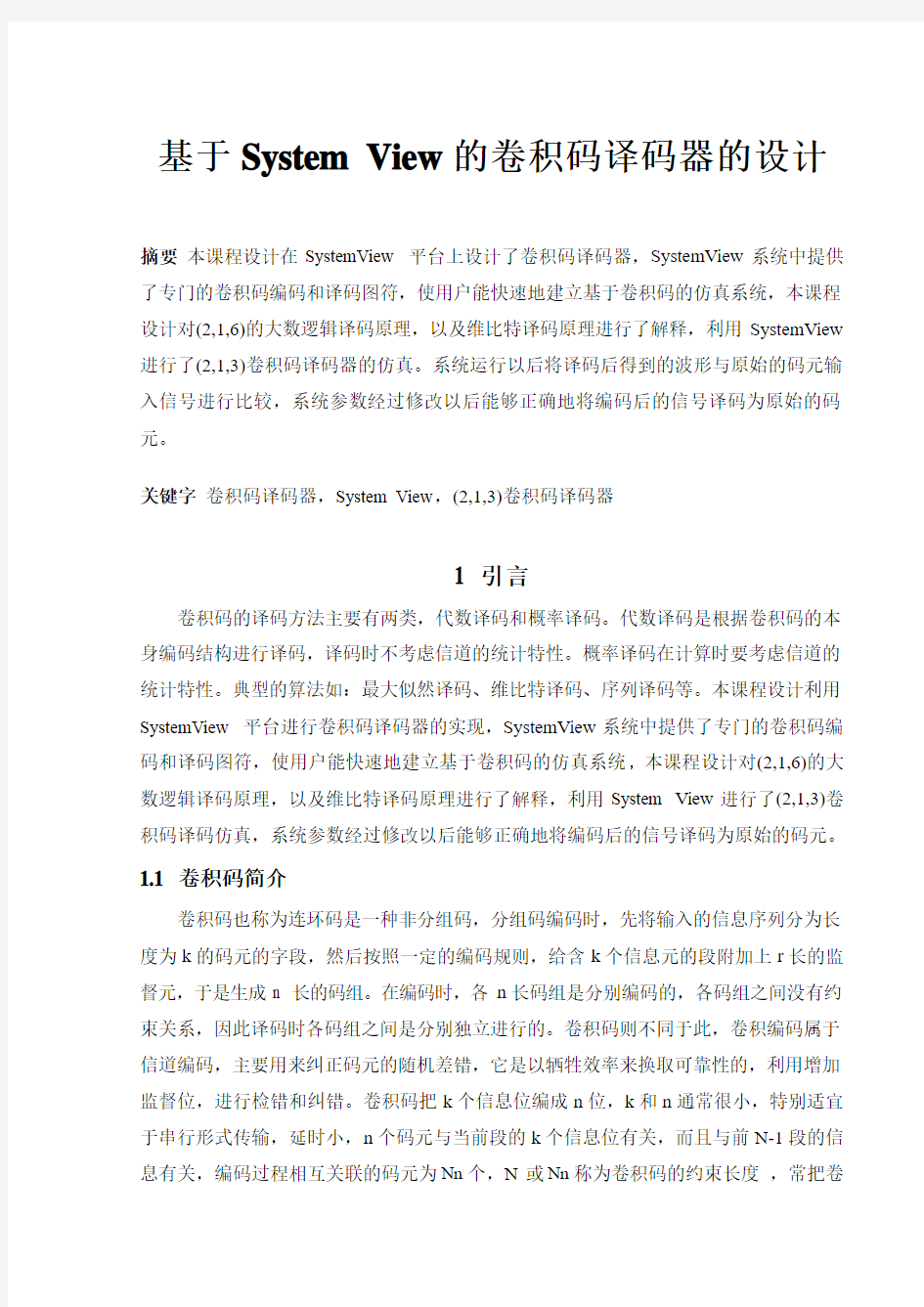

下图1.1为卷积码的门限译码器:

图1.1 (2,1,6)卷积码的门限译码器

该译码器由输入分路开关、两组移位寄存器、四个模2加法器和大数判决门组成。

开关把收到的序列进行信息位和监督位的分路,信息移位寄存器存入6格信息于“1”,

模2加法器在输出端产生移位监督位,该监督位同收到的监督位在“2”模2加法器处

相加,从而得到校正子送给“校正子移位寄存器”组,校正子移位寄存器在得到连续六

格校正子以后,按照方程组2输出校正子值,在门限电路也就是大数判决门处实现门限

判决,若Si的和大于或等于3则输出位1,反之则输出0。判决门输出1就可通过“4”,

模2加法器改变e

11

位置上的信息位,纠正了错误,反之判决器输出位0则不会改变检

验是正确的信息位,判决门输出位1时,则还用来改变有关的已发生错误的校正子,为后续码元的纠正做好准备,可以看到该译码器可以纠正在约束长度内的两位随机错误,如果要纠正多于2位的随机差错,则需要找约束长度更长且性能更好的卷积码。

(2)维比特译码

维特比的译码和序列译码都属于概率译码,当卷积码的约束长度不大时,与序列译码相比,维比特译码器更简单且计算速度更快。概率译码的译码基本思想是:把接收序列与所有可能的发送序列做比较,选择其中码距最小的时译格序列作为发送序列。如果发送的L信息比特,对于(n、k)卷积码来说可能发送的序列有2kL个,计算机或译码器需存储这些序列并进行比较,以找到码距最小的那个序列,当传输率和信息组数L比较大时使得译码器难以实现。VB算法则对上述概率译码做了简化,以至成为了一种实用化的概率算法,它是接收字段、计算和比较字段,丛冢选择一段有最大似然可能的码段,从而使整个码序列是一个有最大似然值的序列。

维比特译码缺点是,随着约束长度的增加,算法的复杂度增加也很快。约束长度N 为7时,要比较的路径就有64条,为8时路径变为128条(2<<(N-1)),所以维比特译码一般应用在约束长度小于10的场合中。编码(举例约束长度为7):编码器7个延迟器的状态(0,1)组成了整个编码器的64个状态,每个状态在编码器输入0或1时,会跳转到另一个之中。比如110100输入1时,变成101001(其实就是移位寄存器)。并且输出也是随之而改变的。

解码的过程就是逆过程。算法规定t时刻收到的数据都要进行64次比较,就是64个状态每条路有两条分支(因为输入0或1)。同时,跳转到不同的两个状态中去,将两条相应的输出和实际接收到的输出比较,量度值大的抛弃(也就是比较结果相差大的),留下来的就叫做幸存路径,将幸存路径加上上一时刻幸存路径的量度然后保存,这样64条幸存路径就增加了一步。在译码结束的时候,从64条幸存路径中选出一条量度最小的,反推出这条幸存路径(叫做回溯),得出相应的译码输出。这样的算法在TI的C54x的dsp上使用100M的速率运行,都无法达到数传速度的要求,主要的时间消耗在每条路径的两次比较上,两次比较的时间一共需要从内存中取3个数(上一时刻幸存路径的量度,两个状态跳转相应的输出值),比较结束以后,还需要对内存写入2个数(幸存路径新的总量度,下一个跳转的状态)。这样,每个时钟节拍需要比较的次数就是64*2次,每次存取数就要5次,一个数据包是256byte,知道解码一包所大概需要的时间,加上其他的开销,最后实验出来的结果是大概0.06m,但是用64k速率传输的

时候只要0.03m即可传完。

2 SystemView介绍

2.1 SystemView简介

SystemView是ELANIX公司一个完整的Win/95/98/NT单机和网络平台的动态系统设计、仿真和分析的可视化设计工具。它提供开发各种系统的模拟和数字工具,这些系统包括DSP、信号处理、通信和控制以及构造通用数字系统模型。SystemView的环境包括一套可以选择的能够增加核心库功能的用于特殊应用的库。这些库包括:通讯库、DSP 库、逻辑库、射频/模拟库(RF)、支持使用VC/BC编程的用户扩充代码库、自动程序生成(APG)、TI C6XX/54X DSP实时仿真(与TI code Compoer Studio协同仿真)、CDMA/APS,数字影象广播(DVB)、自适应滤波器库、联合Matlab仿真库等。System View的XiLinx FPGA库,能准确迅速地直接用XiLinx FPGA实现DSP系统设计,另外Elanix最新推出符合第三代移动通讯的3GPP库, Turbo Code (TPC) 库。

SystemView是一个用于现代系统设计,仿真的动态分析工具。从信号处理,滤波器设计,通信系统直到一般的系统数学模型,SystemView在友好而且功能齐全的窗口环境下,为用户提供了一个嵌入式精密分析引擎。SystemView 利用图符和亚系统功能,可以定义一些简单的功能组,再通过对这些简单功能组的连接进而实现一个大系统。SystemView 能自动执行系统连接检查,通知用户连接出错并通过显示指出出错的图符。SystemView 属于一个系统级的工作平台,可以进行包括数字信号处理(DSP)系统,模拟与数字通信系统,信号处理和控制系统的仿真分析,通过时域波形,眼图,功率谱,星座图和各类曲线给出系统的仿真分析结果。

2.2 SystemView功能简介

Systemview主要由库中的图符来完成不同的仿真功能。它由以下的库组成:

(1)基本库:SystemView的基本库包括信源库、算子库、函数库、信号接收器库等,它为该系统仿真提供了最基本的工具。

(2)信号源:SystemView为我们提供了16种信号源,可以用它来产生任意信号。(3)算子库:功能强大的算子库多达31种算子,可以满足您所有运算的要求。

(4)函数库:32种函数尽显函数库的强大库容。

(5)信号接收方式库:12种信号接收方式可以任意选择,满足不同的显示要求,有图象显示,数据显示等。

(6)展功能库:扩展功能库提供可选择的能够增加核心库功能的用于特殊应用的库。它允许通信、DSP、射频/模拟和逻辑应用。

(7)通信库:包含有大量的通信系统模块,是快速设计和仿真现代通信系统的力工具。这些模块从纠错编码、调制解调、到各种信道模型一应俱全。

(8)DSP库:能够在你将要运行DSP芯片上仿真DSP系统。该库支持大多DSP芯片的算法模式。例如乘法器、加法器、除法器和反相器的图标代表真正的DSP算法操作符。还包括高级处理工具:混合的Radix FFT、FIR和IIR滤波器以及块传输等。

(9)逻辑库:逻辑运算自然离不开逻辑库了,它包括象与非门这样的通用器件的图标、74系列器件功能图标及用户自己的图标等。

(10)射频/模拟库:支持用于射频设计的关键的电子组件,例如:混合器、放大器和功率分配器等。

3卷积码译码器仿真

3.1 卷积码译码器概述

本次课程设计利用SystemView软件进行了卷积码译码器的仿真,利用SystemView 软件提供的通信仿真平台,选择码元模块作为码元输入,经过采样变为数字信号,通过卷积码编码器模块进行卷积码编码,然后采样再送入卷积码译码器,将译码后的信号与码元输入进行比较从而观察系统能否正确的进行译码,从而知道设计是否正确。

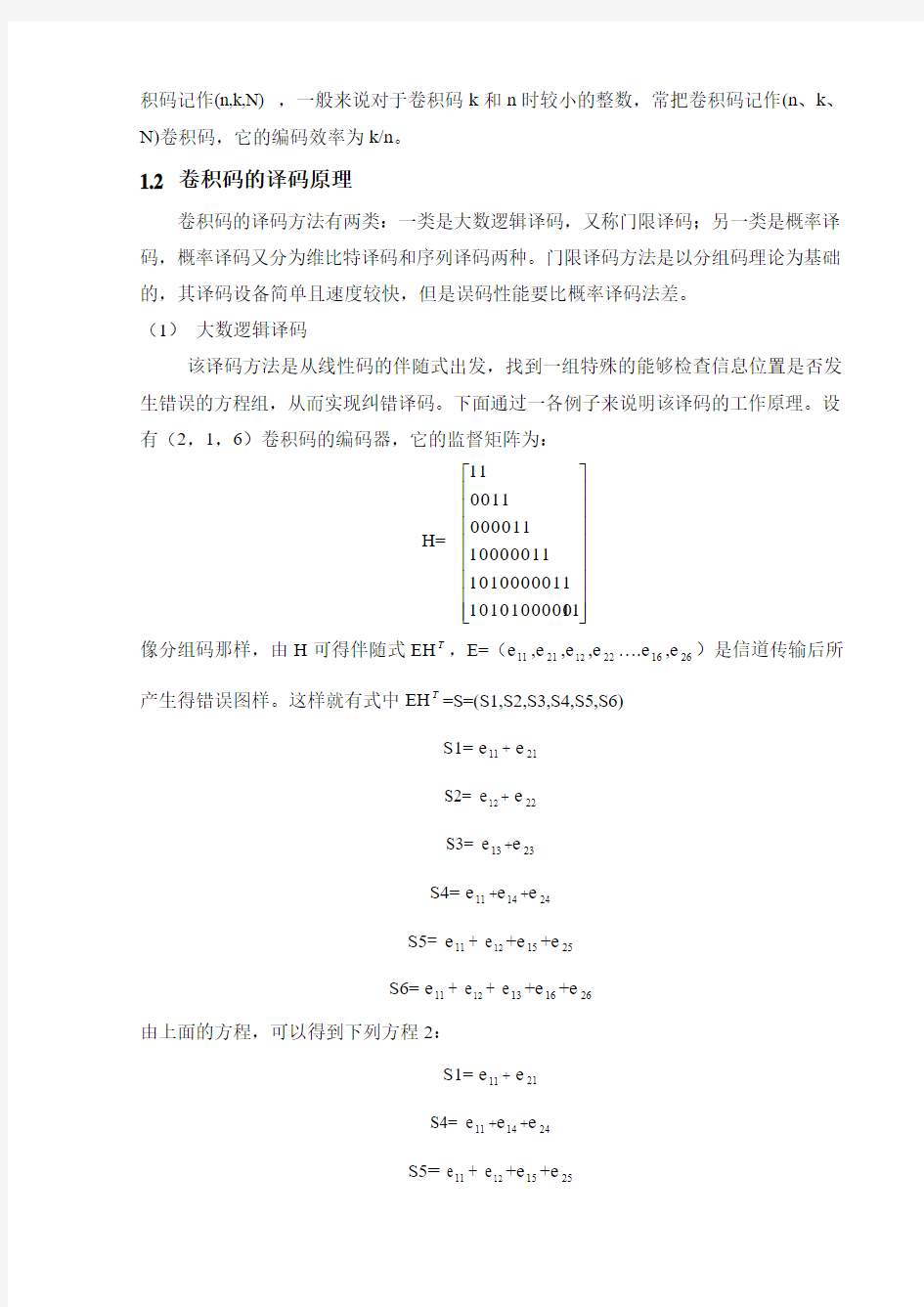

译码器设计框图如图3.1所示:

图3.1 译码器原理

3.2System View仿真图

根据译码原理设计的卷积码译码器如图3.2所示

图3.2 卷积码译码仿真图

其中各个模块的作用,如下:

①0模块:伪随机信号,可以设置幅度,频率、信号阶数、偏置和相位参数,可以按指

定的参数产生伪随机序列作为码元输入

②1模块:采样模块,可以设置采样速率、孔径偏差、时间,对采样信号进行采样,但

是不插入新的采样值,图种的4、16模块均位采样模块

③10模块:保持模块,可以设置增益选择保持最后一次采样还是保持0,放于采样图

符或压缩图符之后用于对采样值进行保持,20、19模块均为保持模块

④2模块:卷积码编码器,可以设置码长、信息位、约束位、门限、偏置,按指定的参

数对输入信号进行卷积编码

⑤11模块:多项式模块,22模块也为多项式模块

⑥24模块:采样延迟

⑦15模块:卷积码译码器,可以设置码长、信息位、约束位、门限、偏置,按制定设

置的卷积码进行译码

⑧18模块:图形显示模块,显示译码后得到的信号,5模块显示的示输入码元的图形,

图21显示的是编码后经过保持后得到的图形

3.3参数设置

伪随机信号的参数设置如图3.3所示:

图3.3 输入码元参数设置

采样器1中参数设置中采样频率和信号源的频率设置为一样,所以采样频率应设置为1Hz,其参数设置如图3.4所示:

图3.4 采样器参数设置

经过编码以后得到的波形有很多三角波,保持模块可以使图形中的三角波经过保持以后得到漂亮的矩形波,图3.5为保持模块的参数设置:

图3.5 保持模块参数设置

卷积码编码器,将经采样后的输入码进行卷积码的编码,在本次课程设计中,我们选取的是(2,1,3)卷积码,所以其参数设置中,n=2,k=1,l=3,生成多项式是自动生成的,下图3.6为卷积码编码器的参数设置:

图3.6 卷积码编码器参数设置

多项式模块完成码极性变换,将单极性码变成双极性码,它的原理是经一个多项式(-1+2x),0转化为-1,1仍为1,那么就将0到+1伏范围的单极性码转换为-1到+1伏范围的双极性码。其参数设置如图3.7所示:

图3.7 多项式模块参数设置

采样器4中参数设置要注意因为经过编码后,1个码元的输入对应有2个码元输出,所以码率增大一倍,所以此时其参数设置中,采样率应设为2Hz,其参数设置如下图3.8所示:

图3.8 采样器4参数设置

因为码元经过编码译码后,延迟很大,若没有经过延迟模块消除延迟则再图形显示器中显示的码元数很少,所以在译码器前加入译个延迟模块参数设置如图3.9所示:

图3.9 延迟器参数设置

卷积码译码器的参数设置,因为设计的是(2,1,3)的卷积码所以卷积码译码器中的n,k,L必须设置为2,1,3,还要输入“Path Length”(路径长度)参数,通常路径长度要设置为编码约束长度的5倍左右,除此之外还要选择硬件判决还是软件判决。通常软件判决比硬件判决可多得1-2dB的增益,在本次设计中选择了硬判决,参数设置如图3.10所示:

图3.10 卷积码译码器参数设置

采样器16中的采样速率应设置为1,因为经过卷积码译码器后2位码元对应一位,采样速率由译码前的2Hz变为1Hz,参数设置如图3.11所示:

图3.11 采样器16参数设置

在仿真中,要进行系统时间的设置,如开始时间、结束时间、采样数目、采样率、时间步长、频率分辨率和系统的循环次数等。其中采样频率=1/时间步长,频率分辨率=采样频率/采样点数,另外采样点数必须为整数。系统的循环次数则提供了用户系统自动重复运行的功能。要注意的是,系统采样率要大于图中码元的采样率。

其参数设置如下图3.12所示:

图3.12 系统时间参数设置

4运行结果及译码分析

图4.1 码元输入波形

4.2 卷积码编码后的波形

本课程设计选择随机码元输作为输入码元,码元输入频率为1Hz,(2,1,3)编码器将一个码元编码为2个码元,所以图4.1码元输入中的一个码元对应图4.2中编码波形的两个码元。

图4.3 卷积码译码后的波形

上图4.1为码元输入经过卷积码编码器后得到的波形,图4.2为码元输入波形,因为采样数目比较多,所以我们只取前面部分码元来进行分析。本课程设计选择随机码元输入作为输入码元,码元输入频率为1Hz,(2,1,3)编码器将一个码元编为2个码元,所以图4.1码元输入中的一个码元对应图4.2中编码波形的两个码元。

从图4.1可以读出前半部分输入的码元为(1010111),根据(2,1,3)译码器的原理,经过编码器后应该得到11010001001001,观察上图4.2编码后的图形可以得出编码是正确的,下图4.3为经过卷积码译码器以后的波形,由于经过编码译码以后的信号延迟很大,所以图形显示器显示的只有前面一部分的译码信号。从图中可以读出经过卷积码译码器得出的信号为(1010111),译码得到的信号有一定的时延,从图形显示器中只可以看到前面一部分信号的波形,但是译码得出的信号与原始的码元输入时一致的,所以可以得出系统可以将编码后的信号正确的译码为原始的码元输入信号。

4结束语

本课程设计首先介绍了卷积码得特点,将分组码得特点与卷积码特点进行了比较,分析了卷积码译码中的大数逻辑译码与维比特译码的译码原理,并且进行了性能的比较。以(2,1,3)卷积码为例,在在SystemView平台下,利用其丰富的图符库和强大的计算功能,对卷积码的译码过程进行了软件实现。根据仿真结果再一次论证了卷积码的译码过程,对译码以后得到的图形与原始的码元输入进行了比较,从而验证了设计的卷积码译码系统可以将编码后得到的信号正确的译码为原始的码元输入,卷积码具有很多分

组码所不具有的优点,因此在通信网络中广泛的得到应用。

参考文献

[1] 樊昌信.通信原理[M].北京:国防工业出版社,1994

[2] 孙屹,戴妍峰.SystemView通信仿真开发手册.北京: 国防工业大学,2004

[3] 曹志刚.现代通信原理[M].北京:清华大学出版社,1992

[4] 罗卫兵,孙桦,张捷.System View动态系统分析及通信系统仿真设计[M].西安:西安电子科技大学出版社,2001

课程设计成绩评定

学院专业

班级学号

学生姓名指导教师

课程成绩完成日期

指导教师对学生在课程设计中的评价

指导教师对课程设计的评定意见

长沙理工大学

《数字信号处理》课程设计报告

甘凌霞

学 院 计算机与通信工程 专 业 通信工程 班 级 通信03-01 学 号 200354080105 学生姓名 甘凌霞 指导教师 单树民 课程成绩

完成日期 2007年1月14日

基于Matlab的卷积码译码器的 设计与仿真 学生姓名:指导老师:** 摘要本课程设计主要解决对一个卷积码序列进行维特比(Viterbi)译码输出, 并通过Matlab软件进行设计与仿真,并进行误码率分析。在课程设计中,系统开发平台为Windows Vista Ultimate,程序设计与仿真均采用Matlab R2007a(7.4),最后仿真详单与理论分析一致。 关键词课程设计;卷积码译码器;Matlab;Simulink;设计与仿真 1引言 本课程设计主要解决对一个卷积码序列进行维特比(Viterbi)译码输出,并通 过Matlab软件进行设计与仿真。卷积码的译码有两种方法——软判决和硬判决,此课程设计采用硬判决的维特比译码。 1.1课程设计目的 卷积码是一种向前纠错控制编码。它将连续的信息比特序列映射为连续的编码器输出符号。这种映射是高度结构化的,使得卷积码的译码方法与分组码译码所采用的方法完全不同。可以验证的是在同样复杂度情况下,卷积码的编码增益要大于分组码的编码增益。对于某个特定的应用,采用分组编码还是采用卷积编码哪一种更好则取决于这一应用的具体情况和进行比较时可用的技术[1]。 本课程设计便是通过Matlab设计一个硬判决维特比译码输出的完整电路,并进行误码率分析。

1.2 课程设计的原理 卷积码,又称连环码,是由伊莱亚斯(P.elias)于1955年提出来的一种非分组码。 卷积编码的最佳译码准则为:在给定已知编码结构、信道特性和接收序列的情况下,译码器将把与已经发送的序列最相似的序列作为传送的码字序列的估值。对于二进制对称信道,最相似传送序列就是在汉明距离上与接收序列最近的序列。 卷积码的译码方法有两大类:一类是大数逻辑译码,又称门限译码(硬判决,编者注);另一种是概率译码(软判决,编者注),概率译码又分为维特比译码和序列译码两种。门限译码方法是以分组码理论为基础的,其译码设备简单,速度快,但其误码性能要比概率译码法差[2]。 当卷积码的约束长度不太大时,与序列译码相比,维特比译码器比较简单,计算速度快。维特比译码算法是1967年由Viterbi提出,近年来有大的发展。目前在数字通信的前向纠错系统中用的较多,而且在卫星深空通信中应用更多,该算法在卫星通信中已被采用作为标准技术。 2维特比译码原理 采用概率译码的基本思想是:把已接收序列与所有可能的发送序列做比较,选择其中码距最小的一个序列作为发送序列。如果发送L组信息比特,那么对于(n,k)卷积码来说,可能发送的序列有2kL个,计算机或译码器需存储这些序列并进行比较,以找到码距最小的那个序列。当传信率和信息组数L较大时,使得译码器难以实现。维特比算法则对上述概率译码做了简化,以至成为了一种实用化的概率算法。它并不是在网格图上一次比较所有可能的2kL条路径(序列),而是接收一段,计算和比较一段,选择一段最大似然可能的码段,从而达到整个码序列是一个最大似然值得序列。 下面以图2.1的(2,1,3)卷积码编码器所编出的码为例,来说明维特比解码的方法和运作过程。为了能说明解码过程,这里给出该码的状态图,如图2.2所

深圳市德普施科技有限公司 nRF24L01无线通信模块使用手册 一、模块简介 该射频模块集成了NORDIC公司生产的无线射频芯片nRF24L01: 1.支持2.4GHz的全球开放ISM频段,最大发射功率为0dBm 2.2Mbps,传输速率高 3.功耗低,等待模式时电流消耗仅22uA 4.多频点(125个),满足多点通信及跳频通信需求 5.在空旷场地,有效通信距离:25m(外置天线)、10m(PCB天线) 6.工作原理简介: 发射数据时,首先将nRF24L01配置为发射模式,接着把地址TX_ADDR和数据TX_PLD 按照时序由SPI口写入nRF24L01缓存区,TX_PLD必须在CSN为低时连续写入,而TX_ADDR在发射时写入一次即可,然后CE置为高电平并保持至少10μs,延迟130μs后发射数据;若自动应答开启,那么nRF24L01在发射数据后立即进入接收模式,接收应答信号。如果收到应答,则认为此次通信成功,TX_DS置高,同时TX_PLD从发送堆栈中清除;若未收到应答,则自动重新发射该数据(自动重发已开启),若重发次数(ARC_CNT)达到上限,MAX_RT置高,TX_PLD不会被清除;MAX_RT或TX_DS置高时,使IRQ变低,以便通知MCU。最后发射成功时,若CE为低,则nRF24L01进入待机模式1;若发送堆栈中有数据且CE为高,则进入下一次发射;若发送堆栈中无数据且CE为高,则进入待机模式2。 接收数据时,首先将nRF24L01配置为接收模式,接着延迟130μs进入接收状态等待数据的到来。当接收方检测到有效的地址和CRC时,就将数据包存储在接收堆栈中,同时中断标志位RX_DR置高,IRQ变低,以便通知MCU去取数据。若此时自动应答开启,接收方则同时进入发射状态回传应答信号。最后接收成功时,若CE变低,则nRF24L01进入空闲模式1。 三、模块引脚说明

湖南文理学院 课程设计报告 课程名称:通信系统课程设计 专业班级:通信工程11102班09 学生姓名:朱涛 指导教师:侯清莲 完成时间:2014-11-18 报告成绩:

目录 一、设计要求 (1) 二、设计作用与目的 (1) 三、所用设备及软件 (1) 四、卷积码编码的概念 (1) 4.1卷积码的编码描述方法 (1) 4.2 卷积编码 (2) 4.3 卷积码的树状图 (3) 4.4 卷积码的网格图 (3) 五、 EDA设计方法及工具软件QUARTUSⅡ (4) 六、改变卷积编码器的参数仿真以及结论 (4) 6.1 不同回溯长度对卷积编码器性能的影响 (4) 6.2 不同码率对卷积编码器误码性能的影响 (5) 6.3 不同约束长度对卷积编码器的误码性能影响 (6) 七、卷积码编码器的VHDL设计与仿真 (8) 7.1 VHDL设计的优点与设计方法 (8) 7.2 卷积码编码器的VHDL实现 (10) 八、心得体会 (10) 九、参考文献 (11)

卷积编码器的设计 一、设计要求 (1)画出卷积码的原理框图,说明系统中各主要组成部分的功能。 (2)使用EDA技术及VHDL语言对卷积编码器进行设计与仿真并对结果分析。 二、设计作用与目的 (1)巩固加深对通信基本知识分析以及卷积码的掌握,提高综合运用通信知识的能力。(2)掌握采用仿真软件对系统进行仿真分析。 (3)培养学生查阅参考文献,独立思考,设计,钻研电子技术相关问题的能力。 (4)掌握相关电子线路工程技术规范以及常规电子元器件的性能技术指标。 (5)培养严肃认真的工作作风与科学态度,建立严谨的工程技术观念。 (6)了解电气图国家标准,并利用电子CAD等正确绘制电路图。 (7)培养工程实践能力,创新能力与综合设计能力。 三、所用设备及软件 (1)QUARTUSⅡ (2)PC机 四、卷积码编码的概念 4.1卷积码的编码描述方法 编码描述方法有5种:冲激响应描述法、生成矩阵描述法、多项式乘积描述法、状态图描述法和网格图描述法。卷积码的纠错能力随着N的增加而增大,而差错率随着N的增加而指数下降。在编码器复杂性相同的情况下,卷积码的性能优于分组码。分组码有严格的代数结构,但卷积码至今尚未找到如此严密的数学手段。分组码的译码算法可以由其代数特性得到。卷积码虽然可以采用适用于分组码的门限译码(即大数逻辑译码),但性能不如维特比译码和序列译码[2]。 以二元码为例,输入信息序列为u=(u0,u1,…),其多项式表示为u(x)=u0+u1x+…+…。编码器的连接可用多项式表示为g (1,1) (x)=1+x+x2和g(1,2)(x)=1+x2,称为码的子生 成多项式。它们的系数矢量g (1,1)=(111)和g (1,2) =(101)称作码的子生成元。以子生成多项式 为阵元构成的多项式矩阵G(x)=[g (1,1)(x),g (1,2) (x)],称为码的生成多项式矩阵。由生成 元构成的半无限矩阵。

//下面是接收的NRF24L01的程序。 ////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////// #include

湖南文理学院课程设计报告 课程名称:通信系统课程设计 院部:电气与信息工程学院 专业班级: 学生姓名: 指导教师: 完成时间: 2011 年 12 月 29日 报告成绩:

目录 目录 (2) 摘要 (3) Abstract (4) 一、引言 (5) 1.1设计任务及基本要求 (5) 1.2设计目的 (6) 1.3 设计所用仪器设备.................................................................................. 错误!未定义书签。 二、基本概念 (6) 2.1 卷积码的编码原理 (6) 2.2 卷积码编码描述 (6) 2.3 卷积码译码描述 (6) 三、卷积码的编译码原理 (6) 3.1卷积码的图形描述 (6) 3.1.1 树状图 (8) 3.1.2 网格图 (8) 3.1.3 状态图 (9) 3.2 卷积积码的编码算法 (9) 3.3卷积码的Viterbi译码 (10) 四、卷积码的仿真及性能分析 (12) 4.1 SIMULINK仿真模块 (12) 4.2 卷积码的参数对误码率的影响 (13) 4.2.1 码率对误码性能的影响 (13) 4.2.2 约束长度对误码性能的影响 (15) 4.2.3 回溯长度对卷积码性能的影响 (16) 4.3 仿真分析 (17) 总结 (18) 参考文献: (19)

摘要 卷积码是深度空间通信系统和无线通信系统中常用的一种差错控制编码。在编码过程中,卷积码充分利用了各码字间的相关性。在与分组码同样的码率和设备复杂性的条件下,无论从理论上还是从实践上都证明,卷积码的性能都比分组码具有优势。而且卷积码在实现最佳译码方面也较分组码容易。因此卷积码广泛应用于卫星通信,CDMA数字移动通信等通信系统,是很有前途的一种编码方式。对其进行研究有很大的现实意义。为了解决传统的维特比译码器结构复杂、译码速度慢、消耗资源大的问题,提出一种新型的适用于FPGA 特点,路径存储于译码输出并行工作,同步存储路径矢量和状态矢量的译码器设计方案。该设计方案通过在ISE.2i中仿真验证,译码结果正确,得到编码前的原始码元,速度显著提高,译码器复杂程度明显降低。并在实际的软件无线电通信系统中信道编解码部分得到应用,性能优良。 关键词:卷积码;误码性能;原理

nRF24L01无线通信模块使用手册 一、模块简介 该射频模块集成了NORDIC公司生产的无线射频芯片nRF24L01: 1.支持2.4GHz的全球开放ISM频段,最大发射功率为0dBm 2.2Mbps,传输速率高 3.功耗低,等待模式时电流消耗仅22uA 4.多频点(125个),满足多点通信及跳频通信需求 5.在空旷场地,有效通信距离:25m(外置天线)、10m(PCB天线) 6.工作原理简介: 发射数据时,首先将nRF24L01配置为发射模式,接着把地址TX_ADDR和数据TX_PLD按照时序由SPI 口写入nRF24L01缓存区,TX_PLD必须在CSN为低时连续写入,而TX_ADDR在发射时写入一次即可,然后CE置为高电平并保持至少10μs,延迟130μs后发射数据;若自动应答开启,那么nRF24L01在发射数据后立即进入接收模式,接收应答信号。如果收到应答,则认为此次通信成功,TX_DS置高,同时TX_PLD 从发送堆栈中清除;若未收到应答,则自动重新发射该数据(自动重发已开启),若重发次数(ARC_CNT)达到上限,MAX_RT置高,TX_PLD不会被清除;MAX_RT或TX_DS置高时,使IRQ变低,以便通知MCU。最后发射成功时,若CE为低,则nRF24L01进入待机模式1;若发送堆栈中有数据且CE为高,则进入下一次发射;若发送堆栈中无数据且CE为高,则进入待机模式2。 接收数据时,首先将nRF24L01配置为接收模式,接着延迟130μs进入接收状态等待数据的到来。当接收方检测到有效的地址和CRC时,就将数据包存储在接收堆栈中,同时中断标志位RX_DR置高,IRQ 变低,以便通知MCU去取数据。若此时自动应答开启,接收方则同时进入发射状态回传应答信号。最后接收成功时,若CE变低,则nRF24L01进入空闲模式1。 二、模块电气特性 参数数值单位 供电电压5V 最大发射功率0dBm 最大数据传输率2Mbps 电流消耗(发射模式,0dBm)11.3mA 电流消耗(接收模式,2Mbps)12.3mA 电流消耗(掉电模式)900nA 温度范围-40~+85℃ 三、模块引脚说明 管脚符号功能方向 1GND电源地 2IRQ中断输出O 3MISO SPI输出O 4MOSI SPI输入I 5SCK SPI时钟I 6NC空 7NC空 8CSN芯片片选信号I 9CE工作模式选择I 10+5V电源

实验九 (2,1,5)卷积码编码译码技术 一、实验目的 1、掌握(2,1,5)卷积码编码译码技术 2、了解纠错编码原理。 二、实验内容 1、(2,1,5)卷积码编码。 2、(2,1,5)卷积码译码。 三、预备知识 1、纠错编码原理。 2、(2,1,5)卷积码的工作原理。 四、实验原理 卷积码是将发送的信息序列通过一个线性的,有限状态的移位寄存器而产生的编码。通常卷积码的编码器由K级(每级K比特)的移位寄存器和n个线性代数函数发生器(这里是模2加法器)组成。 若以(n,k,m)来描述卷积码,其中k为每次输入到卷积编码器的bit数,n 为每个k元组码字对应的卷积码输出n元组码字,m为编码存储度,也就是卷积编码器的k元组的级数,称m+1= K为编码约束度m称为约束长度。卷积码将k 元组输入码元编成n元组输出码元,但k和n通常很小,特别适合以串行形式进行传输,时延小。与分组码不同,卷积码编码生成的n元组元不仅与当前输入的k元组有关,还与前面m-1个输入的k元组有关,编码过程中互相关联的码元个数为n*m。卷积码的纠错性能随m的增加而增大,而差错率随N的增加而指数下降。在编码器复杂性相同的情况下,卷积码的性能优于分组码。 编码器 随着信息序列不断输入,编码器就不断从一个状态转移到另一个状态并同时输出相应的码序列,所以图3所示状态图可以简单直观的描述编码器的编码过程。因此通过状态图很容易给出输入信息序列的编码结果,假定输入序列为110100,首先从零状态开始即图示a状态,由于输入信息为“1”,所以下一状态为b并输出“11”,继续输入信息“1”,由图知下一状态为d、输出“01”……其它输入信息依次类推,按照状态转移路径a->b->d->c->b->c->a输出其对应的编码结果“110101001011”。 译码方法 ⒈代数 代数译码是将卷积码的一个编码约束长度的码段看作是[n0(m+1),k0(m+1)]线性分组码,每次根据(m+1)分支长接收数字,对相应的最早的那个分支上的信息数字进行估计,然后向前推进一个分支。上例中信息序列 =(10111),相应的码序列 c=(11100001100111)。若接收序列R=(10100001110111),先根据R 的前三个分支(101000)和码树中前三个分支长的所有可能的 8条路径(000000…)、(000011…)、(001110…)、(001101…)、(111011…)、(111000…)、(110101…)和(110110…)进行比较,可知(111001)与接收

西南科技大学 方向设计报告 课程名称:通信工程方向设计 设计名称:2/3卷积码编译码器仿真与性能分析 姓名: 学号: 班级: 指导教师: 起止日期:2011.12.12-2012.1.6 西南科技大学信息工程学院制

方向设计任务书 学生班级:学生姓名:学号: 设计名称:2/3卷积码编译码器仿真与性能分析 起止日期:2011.12.12-2012.1.6指导教师: 设计要求: (1)分析2/3卷积码编码器结构; (2)分析2/3卷积码译码的Viterbi算法; (3)基于SIMULINK进行2/3卷积码的纠错性能仿真; 方向设计学生日志 时间设计内容 12.15-12.17 查看题目及设计要求。 12.18-12.23 查阅相关资料,设计方案。 12.23-12.27 编写报告及调试程序。 12.28-12.29 完善修改课程设计报告。 12.30-12.31 答辩。

方向设计考勤表 周星期一星期二星期三星期四星期五 方向设计评语表 指导教师评语: 成绩:指导教师: 年月日

2/3卷积码编译码器仿真与性能分析 摘要: 卷积码是一种性能优越的信道编码。它的编码器和译码器都比较容易实现,同时它具有较强的纠错能力。随着纠错编码理论研究的不断深入,卷积码的实际应用越来越广泛。本文简明地介绍了卷积码的编码原理和Viterbi译码原理。并在SIMULINK模块设计中,完成了对卷积码的编码和译码以及误比特统计整个过程的模块仿真。最后,通过在仿真过程中分别改变卷积码的重要参数来加深理解卷积码的这些参数对卷积码的误码性能的影响。经过仿真和实测,并对测试结果作了分析。 关键词: 卷积码编码器、viterbi译码器、SIMULINK

基于System View的卷积码译码器的设计 摘要本课程设计在SystemView 平台上设计了卷积码译码器,SystemView系统中提供了专门的卷积码编码和译码图符,使用户能快速地建立基于卷积码的仿真系统,本课程设计对(2,1,6)的大数逻辑译码原理,以及维比特译码原理进行了解释,利用SystemView 进行了(2,1,3)卷积码译码器的仿真。系统运行以后将译码后得到的波形与原始的码元输入信号进行比较,系统参数经过修改以后能够正确地将编码后的信号译码为原始的码元。 关键字卷积码译码器,System View,(2,1,3)卷积码译码器 1 引言 卷积码的译码方法主要有两类,代数译码和概率译码。代数译码是根据卷积码的本身编码结构进行译码,译码时不考虑信道的统计特性。概率译码在计算时要考虑信道的统计特性。典型的算法如:最大似然译码、维比特译码、序列译码等。本课程设计利用SystemView 平台进行卷积码译码器的实现,SystemView系统中提供了专门的卷积码编码和译码图符,使用户能快速地建立基于卷积码的仿真系统,本课程设计对(2,1,6)的大数逻辑译码原理,以及维比特译码原理进行了解释,利用System View进行了(2,1,3)卷积码译码仿真,系统参数经过修改以后能够正确地将编码后的信号译码为原始的码元。 1.1 卷积码简介 卷积码也称为连环码是一种非分组码,分组码编码时,先将输入的信息序列分为长度为k的码元的字段,然后按照一定的编码规则,给含k个信息元的段附加上r长的监督元,于是生成n 长的码组。在编码时,各n长码组是分别编码的,各码组之间没有约束关系,因此译码时各码组之间是分别独立进行的。卷积码则不同于此,卷积编码属于信道编码,主要用来纠正码元的随机差错,它是以牺牲效率来换取可靠性的,利用增加监督位,进行检错和纠错。卷积码把k个信息位编成n位,k和n通常很小,特别适宜于串行形式传输,延时小,n个码元与当前段的k个信息位有关,而且与前N-1段的信息有关,编码过程相互关联的码元为Nn个,N或Nn称为卷积码的约束长度,常把卷

本科生毕业论文(设计) 题目:MATLAB实现卷积码编译码 专业代码: 作者姓名: 学号: 单位: 指导教师: 年月日

目录 前言----------------------------------------------------- 1 1. 纠错码基本理论---------------------------------------- 2 1.1纠错码基本理论 ----------------------------------------------- 2 1.1.1纠错码概念 ------------------------------------------------- 2 1.1.2基本原理和性能参数 ----------------------------------------- 2 1.2几种常用的纠错码 --------------------------------------------- 6 2. 卷积码的基本理论-------------------------------------- 8 2.1卷积码介绍 --------------------------------------------------- 8 2.1.1卷积码的差错控制原理----------------------------------- 8 2.2卷积码编码原理 ---------------------------------------------- 10 2.2.1卷积码解析表示法-------------------------------------- 10 2.2.2卷积码图形表示法-------------------------------------- 11 2.3卷积码译码原理---------------------------------------------- 15 2.3.1卷积码三种译码方式------------------------------------ 15 2.3.2V ITERBI译码原理---------------------------------------- 16 3. 卷积码编译码及MATLAB仿真---------------------------- 18 3.1M ATLAB概述-------------------------------------------------- 18 3.1.1M ATLAB的特点------------------------------------------ 19 3.1.2M ATLAB工具箱和内容------------------------------------ 19 3.2卷积码编码及仿真 -------------------------------------------- 20 3.2.1编码程序 ---------------------------------------------- 20 3.3信道传输过程仿真-------------------------------------------- 21 3.4维特比译码程序及仿真 ---------------------------------------- 22 3.4.1维特比译码算法解析------------------------------------ 23 3.4.2V ITERBI译码程序--------------------------------------- 25 3.4.3 VITERBI译码MATLAB仿真----------------------------------- 28 3.4.4信噪比对卷积码译码性能的影响 -------------------------- 28

NRF24L01无线模块C语言程序 24MHz晶振 #include #include #include #include #include #include #define U8 unsigned char #define U16 unsigned int #define TX_ADDR_WITDH 5 //发送地址宽度设置为5个字节 #define RX_ADDR_WITDH 5 //接收地址宽度设置为5个字节 #define TX_DATA_WITDH 1//发送数据宽度1个字节 #define RX_DATA_WITDH 1//接收数据宽度1个字节 #define R_REGISTER 0x00//读取配置寄存器 #define W_REGISTER 0x20//写配置寄存器 #define R_RX_PAYLOAD 0x61//读取RX有效数据 #define W_TX_PAYLOAD 0xa0//写TX有效数据 #define FLUSH_TX 0xe1//清除TXFIFO寄存器 #define FLUSH_RX 0xe2//清除RXFIFO寄存器 #define REUSE_TX_PL 0xe3//重新使用上一包有效数据 #define NOP 0xff//空操作 #define CONFIG 0x00//配置寄存器 #define EN_AA 0x01//使能自动应答 #define EN_RXADDR 0x02//接收通道使能0-5个通道 #define SETUP_AW 0x03//设置数据通道地址宽度3-5 #define SETUP_RETR 0x04//建立自动重发 #define RF_CH 0x05//射频通道设置 #define RF_SETUP 0x06//射频寄存器 #define STATUS 0x07//状态寄存器 #define OBSERVE_TX 0x08//发送检测寄存器 #define CD 0x09//载波 #define RX_ADDR_P0 0x0a//数据通道0接收地址 #define RX_ADDR_P1 0x0b//数据通道1接收地址 #define RX_ADDR_P2 0x0c//数据通道2接收地址 #define RX_ADDR_P3 0x0d//数据通道3接收地址 #define RX_ADDR_P4 0x0e//数据通道4接收地址 #define RX_ADDR_P5 0x0f//数据通道5接收地址

数字通信原理课程设计报告书

基于matlab的卷积码译码器的仿真设计 ) 1设计目的 卷积码是一种向前纠错控制编码。它将连续的信息比特序列映射为连续的编码器输出符号。这种映射是高度结构化的,使得卷积码的译码方法与分组码译码所采用的方法完全不同。可以验证的是在同样复杂度情况下,卷积码的编码增益要大于分组码的编码增益。对于某个特定的应用,采用分组编码还是采用卷积编码哪一种更好则取决于这一应用的具体情况和进行比较时可用的技术。 本课程设计便是通过Matlab设计一个硬判决维特比译码输出的完整电路,并进行误码率分析。 2设计的主要内容和要求 (1)要求能熟练地运用Matlab技术对卷积码译码器进行仿真。 (2)运用Matlab中Simulink单元来创建信源模块、信道模块、信宿模块、简易译码器模块等,并运用所有设计的模块来进行仿真。 3 设计原理 3.1卷积码 卷积码,又称连环码,是由伊莱亚斯(P.elias)于1955年提出来的一种非分组码。 卷积编码的最佳译码准则为:在给定已知编码结构、信道特性和接收序列的情况下,译码器将把与已经发送的序列最相似的序列作为传送的码字序列的估值。对于二进制对称信道,最相似传送序列就是在汉明距离上与接收序列最近的序列。 卷积码的译码方法有两大类:一类是大数逻辑译码,又称门限译码(硬判决,编者注);另一种是概率译码(软判决,编者注),概率译码又分为维特比译码和序列译码两种。门限译码方法是以分组码理论为基础的,其译码设备简单,速度快,但其误码性能要比概率译码法差。

当卷积码的约束长度不太大时,与序列译码相比,维特比译码器比较简单,计算速度快。维特比译码算法是1967年由Viterbi 提出,近年来有大的发展。目前在数字通信的前向纠错系统中用的较多,而且在卫星深空通信中应用更多,该算法在卫星通信中已被采用作为标准技术。 3.2 维特比译码原理 采用概率译码的基本思想是:把已接收序列与所有可能的发送序列做比较,选择其中码距最小的一个序列作为发送序列。如果发送L 组信息比特,那么对于(n,k )卷积码来说,可能发送的序列有2kL 个,计算机或译码器需存储这些序列并进行比较,以找到码距最小的那个序列。当传信率和信息组数L 较大时,使得译码器难以实现。维特比算法则对上述概率译码做了简化,以至成为了一种实用化的概率算法。它并不是在网格图上一次比较所有可能的2kL 条路径(序列),而是接收一段,计算和比较一段,选择一段最大似然可能的码段,从而达到整个码序列是一个最大似然值得序列。 下面以图3.2.1的(2,1,3)卷积码编码器所编出的码为例,来说明维特比解码的方法和运作过程。为了能说明解码过程,这里给出该码的状态图,如图3.2.2 示。维特比译码需要利用图来说明移码过程。根据卷积码画网格的方法,我们可以画出该码的网格图,如图3.2.3所示。该图设输入信息数目L=5,所以画L+N=8个时间单位,图中分别标以0至7。这里设编码器从a 状态开始运作。该网格图的每一条路径都对应着不同的输入信息序列。由于所有可能输入信息序列共有2kL 个,因而网格图中所有可能的路径也为2kL 条。这里节点a=00,b=01,c=10, b 图3.2.1 (2,1,3)卷积码编码器 图3.2.2 (2,1,3)卷积码状态图

NRF24L01使用文档 基于c8051f330单片机

目录 芯片简介 (3) 1 NRF24L01功能框图 (4) 2 NRF24L01状态机 (5) 3 Tx与Rx的配置过程 (7) 3.1 Tx 模式初始化过程 (7) 3.2 Rx模式初始化过程 (8) 4控制程序详解 (9) 4.1 函数介绍 (9) 4.1.1 uchar SPI_RW(uchar byte) (9) 4.1.2 uchar SPI_RW_Reg (uchar reg, uchar value) (10) 4.1.3 uchar SPI_Read (uchar reg); (10) 4.1.4 uchar SPI_Read_Buf (uchar reg, uchar *pBuf, uchar bytes); (11) 4.1.5 uchar SPI_Write_Buf (uchar reg, uchar *pBuf, uchar bytes); (11) 4.1.6 void RX_Mode(void) (12) 4.1.7 void TX_Mode(void) (13) 4.2 NRF24L01相关命令的宏定义 (13) 4.3 NRF24L01相关寄存器地址的宏定义 (14) 5 实际通信过程示波器图 (16) 1)发射节点CE与IRQ信号 (17) 2)SCK与IRQ信号(发送成功) (18) 3)SCK与IRQ信号(发送不成功) (19)

芯片简介 NRF24L01是NORDIC公司最近生产的一款无线通信通信芯片,采用FSK调制,内部集成NORDIC自己的Enhanced Short Burst 协议。可以实现点对点或是1对6的无线通信。无线通信速度可以达到2M(bps)。NORDIC公司提供通信模块的GERBER文件,可以直接加工生产。嵌入式工程师或是单片机爱好者只需要为单片机系统预留5个GPIO,1个中断输入引脚,就可以很容易实现无线通信的功能,非常适合用来为MCU系统构建无线通信功能。

湖南科技大学 信息与电气工程学院 课程设计报告 课程:通信原理 题目:卷积码的仿真 专业:电子信息工程 班级:电子二班 姓名:高二奎 学号: 1104030205

任务书

目录 一、任务与要求 (4) 1.1设计的目的 (4) 1.2 设计的基本内容 (4) 二、卷积码的介绍 (4) 2.1 卷积码的介绍 (4) 2.2 编码原理 (4) 2.3 译码原理 (7) 三、SystemView软件简介 (8) 3.1 SystemView基本特点 (8) 3.2 各单元模块功能介绍及电路设计 (8) 3.3 各模块的原理及介绍 (10) 3.4 图符库选择按钮 (10) 3.5 system view 的操作步骤 (11) 3.6 分析窗的接收计算器 (12) 四、系统仿真和调试 (12) 4.1 系统仿真 (12) 4.2 调试结果 (13) 五、总结 (15) 5.1 设计小结 (15) 5.2 心得体会 (15) 参考文献 (16)

一、任务与要求 1.1设计的目的 这次的课程设计就是基于SystemView软件的卷积码仿真设计,要学会运用SystemView,理解卷积码系统的原理,并用SystemView进行仿真设计。 1.2 设计的基本内容 SystemView是一种动态系统分析软件,也是一个非常好的仿真工具。它能按照物理概念直接建立分析和仿真,对通信技术的发展起到很大的作用。本次课程设计就是利用软件SystemView对卷积码进行可视化仿真,对信息数据的编码,传输及译码等功能的实现,充分展示了SystemView在通信仿真中灵活的应用实例。 二、卷积码的简介 2.1 卷积码介绍 非分组码的卷积码的编码器是在任一段规定时间内产生n个码元,但它不仅取决于这段时间中的k个信息位,还取决于前(K-1)段规定时间内的信息位,这K段时间内的码元数目为K·k,称参数K为卷积码的约束长度,每k 个比特输入,得到n比特输出,编码效率为k/n,约束长度为K。在k=1的条件下,移位寄存器级数m=K-1。 卷积码一般可用(n,k,K)来表示,其中k为输入码元数,n为输出码元数,而K则为编码器的约束长度。典型的卷积码一般选n和k ( k< n ) 值较小,但约束长度K可取较大值(K<10),以获得既简单又高性能的信道编码 [6]。 卷积码是1955年Elias最早提出,1957年Wozencraft提出了序列译码。 1963年Massey提出了一种性能稍差,但比较实用的门限译码方法。1967年维特比(Viterbi)提出了最大似然译码。它对存储器级数较小的卷积码的译码很容易实现,称为维特比算法或维特比译码。

删余卷积码的维特比译码器的设计与实现 在数字通信系统中,特别是面向IEEE802.11ac标准的无线通信系统中,删余卷积码与对应的维特比译码算法作为一种必选的提高信息传输可靠性的技术,具有严重的研究价值。随着人们对数据传输速率要求的不断提升,硬件设备的复杂度也在不断提高,而译码复杂度、硬件系统功耗与资源消耗问题制约了删余卷积码的维特比译码器在数字通信中的进一步发展与应用。本文基于IEEE802.11ac标准,以降低算法计算复杂度、减小硬件设计的系统功耗和硬件资源消耗为目标,对信道编译码算法(包括二进制卷积编译码、交织与扰码算法)进行设计并改进;在完成算法设计的基础上对信道编码各模块进行硬件设计,本文针对传统设计方法的高功耗和高硬件消耗问题提出优化方案。 本文的主要研究成果如下:1.针对删余卷积码的维特比译码算法在高码率下计算复杂度高的问题,提出改进的维特比译码算法。为了解决删余卷积码在码率高于的情况下,译码的计算复杂度较高,且随着码率的增大,译码复杂度也不断提高的问题,本文在传统的维特比译码算法中引入调整因子,可实现当码率大于时有用减少计算分支度量值的步骤,并且随着码率增大,改进算法对译码复杂度的优化更加明明,通过正交频分复用系统环路的搭建,可评估系统的误码率性能;2.针对删余卷积码的译码硬件设计复杂度随码率增高而提高的问题,提出在硬件设计过程中,增设存储删余位置指示信息的寄存器。该寄存器用来指示译码的输入数据是否为补零后的数据。 在计算分支度量值时,该寄存器中的数据与度量值计算结果进行相与,得到加比选模块的输入度量值,可有用减少删余卷积码的维特比译码器在计算分支度量值时的计算步骤。本文搭建FPGA验证平台,并运用QuartusⅡ软件和SignalTapⅡ在线逻辑分析仪可验证硬件设计结果;3.针对删余卷积码的维特比译码器效率低和系统延时较大的问题,提出在译码器内部对加比选模块的设计采用4个加比选子模块并行同步运算的基4方法,可有用提高系统译码效率,并降低译码延时;4.针对信道编码的硬件设计在硬件资源消耗、系统功耗和编译码性能三者之间不平均问题,本文提出串并结合的硬件设计方法。信道编码发送端采用全并行和组合逻辑进行硬件设计,可大幅降低系统功耗;信道编码接收端采用串并结合的处理方法,通过250KHz和20MHz双时钟折中处理硬件资源消耗与系统功耗问题。

北京邮电大学 ASIC原理课程实验 实验报告 设计要求:(3,1,8)卷积码编码器 学院:电子工程学院 专业:电子信息科学与技术 班级: 学号: 姓名: 2013年6月20日

一、设计要求 运用verilog语言编写一个(3,1,8)卷积码编码器,并对其进行仿真。 二、卷积码编码器原理 卷积码拥有良好的纠错性能,是一种被广泛应用于移动通信的信道编码系统。一个(n,k,m)卷积码编码器由k个输入,具有m阶存储的n个输出的线形时序电路实现。通常,n和k是较小的整数,且k<n,但m比较大。当k=1时,信息序列不再分成小块,以便可以连续处理。卷积码(n,k,m)表示码率R=k/n,编码器级数m=s-1,其中s是码约束长度。 反向CDMA信道使用(3,1,8)卷积码,码率R=1/3,约束长度为9,由于k=1,n=3,m=8,则该卷积编码器包含单个输入端,一个8级移位寄存器,三个模2加法器和一个3向编码器输出的连续转向器。编码器每输入一位信息比特将产生三位编码输出。这些编码符号中,第一个输出符号G0是生成序列g1⑴编码产生的符号,第二个输出符号G1是由生成序列g1⑵编码产生的符号,最后一个输出符号G2是由生成序列g1⑶编码产生的符号,如下图所示。 该电路由一个八位寄存器、三个码生成逻辑、一个时隙发生器和一个四选一复用器构成。mux的输入为G0、G1和G2,码选择信号C[1:0]和clk1由时隙发生器产生,输出信号即为整个电路的输出Yout。 卷积编码器的初始状态用rst异步清零信号置为0,rst=0时,电路清零。 卷积编码器的初始状态全为0,初始状态之后输出的第一个编码符号由生成序列g1⑴编码产生。这里,三个生成序列分别为g1⑴=(101101111),g1⑵=(110110011), g1⑶=(111001001)。

(相关人员如觉得本人水平低下,还请见谅) Nrf24L01的使用程序和使用方法和简单操作: 功能: 无线对发程序。两个模块a,b,实现按下一个按键,会在对方的数码管上显示3或4,在本机上显示1,2。 当一个模块,比如a模块。当两个按键按下其中一个,则会在另一个模块b上显示数字3,4(具体根据按下哪个按键)。以上功能描述,B模块按键按下,如同a模块一样的功能,不做系统性描述了。 下面给出程序中几个地方的解释: #define READ_REG 0x00 // 读寄存器指令 #define WRITE_REG 0x20 // 写寄存器指令 #define RD_RX_PLOAD 0x61 // 读取接收数据指令 #define WR_TX_PLOAD 0xA0 // 写待发数据指令 #define FLUSH_TX 0xE1 // 冲洗发送FIFO指令 #define FLUSH_RX 0xE2 // 冲洗接收FIFO指令 #define REUSE_TX_PL 0xE3 // 定义重复装载数据指令 #define NOP 0xFF // 保留 类似这种的描述,可以等同于READ_REG =0x00;这个是经过实际程序测试出来的,比如 以下程序: #include

MOSI = (uchar & 0x80); // output 'uchar', MSB to MOSI uchar = (uchar << 1); // shift next bit into MSB.. SCK = 1; // Set SCK high.. uchar |= MISO; // capture current MISO bit SCK = 0; 此处为spi的核心,是spi协议的编程,其中uchar |= MISO; 表示uchar |= MISO | uchar; MOSI = (uchar & 0x80);其中0x80是1000 0000,与上uchar,这种&,是按位与,故可以从uchar提取出一个电平给mosi。 MOSI = (uchar & 0x80); // output 'uchar', MSB to MOSI uchar = (uchar << 1); 这两句组合起来用,就实现了把uchar编程8位2进制数后的每一位都可以发送给mosi;Uchar的只待对象,就是上面的诸如#define FLUSH_TX 0xE1 这样的数,或者是相关的发送数据。 *pBuf这个并不是一个主要的问题,实际这个是涉及指针问题的,带*的跟地址有关系,但是我们其实不需要很关心编译的时候数据被具体存入哪个地址,即使是很重要的数据。 void init_NRF24L01(void) { inerDelay_us(100); CE=0; // chip enable CSN=1; // Spi disable SCK=0; // SPI_Write_Buf(WRITE_REG + TX_ADDR, TX_ADDRESS, TX_ADR_WIDTH); // 写本地地址 SPI_Write_Buf(WRITE_REG + RX_ADDR_P0, RX_ADDRESS, RX_ADR_WIDTH); // 写接收端地址 SPI_RW_Reg(WRITE_REG + EN_AA, 0x01); // 频道0自动ACK应答允许 SPI_RW_Reg(WRITE_REG + EN_RXADDR, 0x01); // 允许接收地址只有频道0,如果需要多频道可以参考Page21 SPI_RW_Reg(WRITE_REG + RF_CH, 0); // 设置信道工作为2.4GHZ,收发必须一致 SPI_RW_Reg(WRITE_REG + RX_PW_P0, RX_PLOAD_WIDTH); //设置接收数据长度,本次设置为32字节 SPI_RW_Reg(WRITE_REG + RF_SETUP, 0x07); //设置发射速率为1MHZ,发射功率为最大值0dB } 在整个初始化中我们看到: CE=0; // chip enable CSN=1; // Spi disable 这是设置整个的状态。如过状态设置成待机,则引脚可能变为高阻。(以上并非全部引脚)