硬件描述语言实验五

- 格式:doc

- 大小:315.00 KB

- 文档页数:10

eda技术及应用第三版课后答案谭会生【篇一:《eda技术》课程大纲】>一、课程概述1.课程描述《eda技术》是通信工程专业的一门重要的集中实践课,是通信工程专业学生所必须具备的现代电子设计技术技能知识。

eda是电子技术的发展方向,也是电子技术教学中必不可少的内容。

本课程主要介绍可编程逻辑器件在电子电路设计及实现上的应用,介绍电路原理图和pcb图的设计技术。

开设该课程,就是要让学生了解大规模专用集成电路fpga和cpld的结构,熟悉一种以上的硬件描述语言,掌握一种以上的开发工具的使用等,掌握电路原理图和pcb图的现代设计技术与方法,从而提高学生应用计算机对电子电路和高速智能化系统进行分析与设计的能力。

2.设计思路本课程坚持“以学生为中心”的原则,以项目任务驱动的方式,采取理论知识与案例相结合的方式授课,提高学生的学习主动性。

通过必要的理论知识讲授、大量的实践训练和案例分析,培养学生的动手设计和实践能力,掌握eda开发的整个流程和基本技巧。

课程采用演示讲授和实践相结合,边讲边练的方法,让学生切身体会并掌握eda开发产品的流程和方法。

本课程集中2周时间开设,注重实践性,边讲边练,让学生切身体会并掌握eda开发技术。

3.实践要求(1)纪律和安全要求①不得将食物带入实验室,每次实训后请将使用后的废弃物带走。

违反者每次扣罚平时分2分。

②实训期间不得做与实训无关的其他事情,不得大声喧哗或做其他影响实训正常进行的事宜。

违反者每次扣罚平时分2分。

③实训期间,若学生有事不能正常参加实训,须提前以书面形式请假,并按指导教师的安排补做实训。

未经指导教师许可,学生不得任意调换实训时间和实训地点。

违反者每次扣罚平时分4分。

④学生不得以任何理由替代他人进行实训,违者直接取消实训成绩。

⑤学生除操作自己所分配的计算机外,不得操作实验室内其他任何设备。

违者每次扣罚平时分2分。

(2)业务要求实训所使用的软件protel和quartus ii,所有数据均通过服务器中转以及储存在服务器上,所以重启自己所用的电脑不会造成数据丢失。

数电仿真实验报告数字电路仿真实验报告引言:数字电路仿真实验是电子信息类专业学生在学习数字电路原理与设计课程中的一项重要实践环节。

通过仿真实验,学生可以进一步加深对数字电路的理解,掌握数字电路的设计方法和仿真工具的使用。

本文将结合具体的实验案例,介绍数字电路仿真实验的目的、原理、实验步骤和实验结果。

一、实验目的本次实验的目的是通过使用仿真软件,设计并验证一个简单的数字电路电路原理图,了解数字电路仿真的基本流程,掌握仿真软件的使用方法,并通过仿真结果验证设计的正确性。

二、实验原理数字电路仿真实验是通过计算机软件模拟电路的运行过程,以验证电路设计的正确性。

仿真软件可以模拟电路的输入和输出波形,以及电路中各个元件的工作状态。

在数字电路仿真实验中,我们主要使用Verilog HDL(硬件描述语言)来描述电路结构和功能,并通过仿真软件进行仿真。

三、实验步骤1. 确定实验电路的功能和结构,绘制电路原理图;2. 使用Verilog HDL编写电路的结构描述和功能描述;3. 使用仿真软件加载Verilog HDL代码,并设置仿真参数;4. 运行仿真软件,观察并分析仿真结果;5. 根据仿真结果,对电路进行调试和优化,直至达到预期的功能和性能。

四、实验案例以设计一个4位二进制加法器为例,介绍数字电路仿真实验的具体步骤和过程。

1. 确定实验电路的功能和结构:4位二进制加法器是由4个全加器组成的,每个全加器有两个输入和两个输出。

输入包括两个4位二进制数和一个进位信号,输出为一个4位二进制数和一个进位信号。

2. 绘制电路原理图:根据功能和结构确定电路原理图,将4个全加器按照一定的连接方式组合在一起,形成4位二进制加法器的电路原理图。

3. 使用Verilog HDL编写电路的结构描述和功能描述:根据电路原理图,使用Verilog HDL编写电路的结构描述和功能描述。

结构描述包括各个元件的连接方式和引脚定义,功能描述包括各个元件的逻辑运算和信号传递。

第1篇一、实验目的1. 熟悉可编程逻辑器件(FPGA)的基本原理和操作方法。

2. 掌握使用FPGA进行数字电路设计的流程。

3. 学会使用FPGA进行简单数字电路的设计与实现。

二、实验器材1. FPGA开发板2. 编译器软件(如Xilinx ISE、Vivado等)3. 实验指导书4. 实验数据线三、实验原理可编程逻辑器件(FPGA)是一种基于半导体工艺的可编程数字电路,具有高集成度、高速度、可重构性强等特点。

FPGA通过内部逻辑单元(如查找表、触发器等)来实现各种数字电路功能。

本实验主要涉及以下原理:1. 数字电路基本原理2. 可编程逻辑器件(FPGA)的基本结构和工作原理3. 编译器软件的使用方法四、实验步骤1. 熟悉开发板(1)认识开发板上的各个模块,如时钟模块、输入输出模块、存储器模块等。

(2)了解开发板上各个模块的功能和作用。

2. 设计数字电路(1)根据实验要求,设计所需的数字电路。

(2)使用原理图或HDL语言进行电路描述。

3. 编译与下载(1)使用编译器软件对设计的数字电路进行编译。

(2)生成比特流文件。

(3)将比特流文件下载到FPGA中。

4. 测试与验证(1)观察FPGA上各个模块的输出信号,验证电路功能是否正确。

(2)使用示波器等仪器进行波形观察,进一步验证电路功能。

五、实验内容1. 设计一个4位全加器(1)原理图设计:使用原理图编辑器设计4位全加器电路。

(2)HDL语言设计:使用HDL语言描述4位全加器电路。

(3)编译与下载:将设计的电路编译成比特流文件,下载到FPGA中。

(4)测试与验证:观察FPGA上各个模块的输出信号,验证4位全加器电路功能是否正确。

2. 设计一个8位奇偶校验器(1)原理图设计:使用原理图编辑器设计8位奇偶校验器电路。

(2)HDL语言设计:使用HDL语言描述8位奇偶校验器电路。

(3)编译与下载:将设计的电路编译成比特流文件,下载到FPGA中。

(4)测试与验证:观察FPGA上各个模块的输出信号,验证8位奇偶校验器电路功能是否正确。

实验五 VGA图像显示控制一实验目的1.进一步掌握VGA显示控制的设计原理。

2.了解图像的存储和读取方法。

3.进一步掌握4×4键盘或PS/2键盘接口电路设计方法。

4.掌握状态机设计复杂控制电路的基本方法。

二硬件需求1.EDA/SOPC实验箱一台。

三实验原理VGA图像显示控制利用实验三中学习的《VGA显示控制模块》显示存储于ROM中的图像数据。

要显示的图像是四块64*64像素大小的彩色图片,通过键盘控制可以选择不同的图片显示。

图像可以在屏幕上移动(水平和垂直方向每帧分别移动“H_Step”点和“V_Step”点),通过键盘改变“H_Step”和“V_Step”的值即可改变其移动速度和方向。

图像碰到屏幕边沿会反弹回去。

如图5.1所示H_StepV_Step图5.1 VGA图像显示控制示意图实验中要用到4×4键盘、VGA显示控制、ROM等模块,在《实验三常用模块电路的设计》中已经讲述,可以直接使用已做好的模块(可能需要修改部分代码)。

键盘也可以使用PS/2接口键盘,这样可以输入更多的字符。

四实验内容1、图5.2是整个设计的顶层电路。

图5.2 VGA图像显示控制顶层电路图2、实验三中学习的几个模块①“Read_Keyboard”模块与实验三中的4×4键盘模块一致;②四个ROM模块使用宏功能模块实现,并设置其内存初始化文件分别为“FBB.mif”、“dog.mif”、“cat.mif”、“flower.mif”,如图5.3所示。

当然也可以用其他图片(大小为64*64)使用“BmpToMif”软件生成对应的“mif”文件,如图5.4所示。

图5.3 内存初始化文件设置图5.4 获取内存初始化文件(mif文件)③“VGA”模块与实验三中基本一致,只需要在端口中屏蔽“key”端口,并加入“imag_rgb: in std_logic_vector(2 downto 0);”用于从外部输入图像数据。

实验一 MAX+PLUSⅡ的基本应用一、实验目的1.掌握MAX+PLUSⅡ的安装及基本使用。

2.掌握MAX+PLUSⅡ基本输入法—图形输入工具按钮的使用。

二、实验设备与仪器1.计算机2 MAX+PLUSⅡ工具软件三、实验内容1.MAX+PLUSⅡ的安装。

2.在图形编辑软件中,进行调入元件符号、放置元件、连线、放置输入输出引脚及放置节点标号等练习。

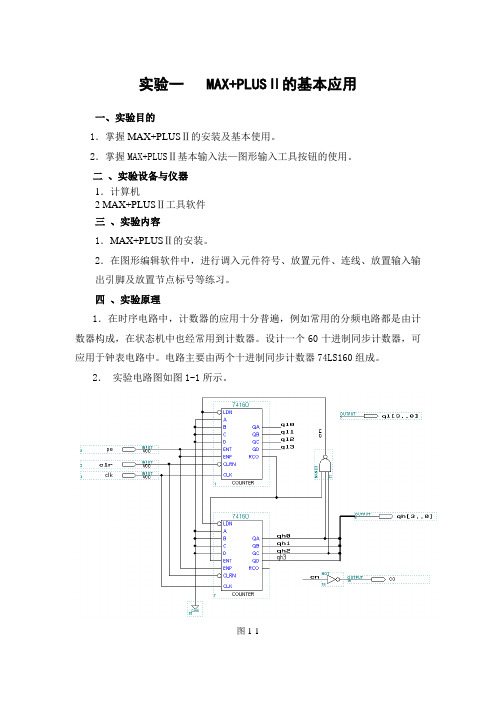

四、实验原理1.在时序电路中,计数器的应用十分普遍,例如常用的分频电路都是由计数器构成,在状态机中也经常用到计数器。

设计一个60十进制同步计数器,可应用于钟表电路中。

电路主要由两个十进制同步计数器74LS160组成。

2.实验电路图如图1-1所示。

图1-1五、实验步骤1. MAX+PLUSⅡ的安装,只要在安装向导的指引下,按步骤的顺序执行,即可完成。

2.AX+PLUSⅡ安装完毕后,在第一次运行时需要进行License设置,然后才可以使用。

3.启动MAX+PLUSⅡ软件,进入MAX+PLUSⅡ管理窗口。

进行设计项目的建立。

4.在MAX+PLUSⅡ管理窗口的File菜单下选择New选项或单击按钮,然后再选择Graphic Editor file后,单击OK按钮,可建立图形输入文件。

5.从库中调入元件符号。

在图形编辑区内双击鼠标左键或单击鼠标右键,在随后弹出的菜单中选择Enter Symbol即可直接键入元件名,调出元件,也可以选择元件库。

MAX+PLUSⅡ提供了4种库文件,其功能见表1-1所示。

表1-1 图形编辑器提供的库功能6.单击连线工具栏的按钮,光标变成,“+”形,单击连线起始端按住鼠标左键拖动至结束端松开,连线结束。

若要删除某连线,可单击连线使其变成高亮(红色),再按,Delete键,即可删除。

7.图形编辑时,在连线复杂的地方(总线),可用节点标号来连线。

用节点标号连线不区分大小写。

8.放置输入输出引脚。

在符号库中调入元件符号对话框中,键入,input”或,output”即可将输入或输出引脚添加到电路图中,新放置的输入输出引脚需要修改引脚名称。

实验一组合逻辑器件设计一、实验目的1、通过一个简单的3-8译码器的设计,掌握组合逻辑电路的设计方法。

2、掌握组合逻辑电路的静态测试方法。

3、初步了解QUARTUS II原理图输入设计的全过程。

二、实验主要仪器与设备1、输入:DIP拨码开关3位。

2、输出:LED灯。

3、主芯片:EP1K10TC100-3。

三、实验内容及原理三-八译码器即三输入,八输出。

输出与输入之间的对应关系如表1-1-1所示。

表1-1 三-八译码器真值表四、预习要求做实验前必须认真复习数字电路中组合逻辑电路设计的相关内容(编码器、译码器)。

五、实验步骤1、利用原理图设计输入法画图1-1-1。

2、选择芯片ACEX1K EP1K10TC100-3。

3、编译。

4、时序仿真。

5、管脚分配,并再次编译。

6、实验连线。

7、编程下载,观察实验结果。

图1-1 三-八译码器原理图六、实验连线用拨码开关的低三位代表译码器的输入(A,B,C),将之与EP1K10TC100-3的管脚相连;用LED灯来表示译码器的输出(D0~D7),将之与EP1K10TC100-3芯片的管脚相连。

拨动拨档开关,可以观察发光二极管与输入状态的对应关系同真值表中所描述的情况是一致的。

七、实验结果八、思考题在输入端加入使能端后应如何设计?附:用硬件描述语言完成译码器的设计::LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY T2 ISPORT(A: IN STD_LOGIC_VECTOR(2 DOWNTO 0);Y: OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END T2;ARCHITECTURE A OF T2 ISBEGINWITH A SELECTY <= "00000001" WHEN "000","00000010" WHEN "001","00000100" WHEN "010","00001000" WHEN "011","00010000" WHEN "100","00100000" WHEN "101","01000000" WHEN "110","10000000" WHEN OTHERS;END A;实验二组合电路设计一、实验目的1、掌握组合逻辑电路的设计方法。

一、实验名称1. 实验一QuartusⅡ原理图输入法设计与实现2. 实验二用VHDL设计与实现组合逻辑电路(一)3. 实验三用VHDL设计与实现时序逻辑电路(二)4.实验四用VHDL设计与实现时序逻辑电路(三)(数码管动态扫描控制器)二、实验任务要求1.实验一:○1用逻辑门设计实现一个半加器,仿真验证其功能,并生成新的半加器图形模块单元;○2用上面生成的半加器模块和逻辑门设计实现一个全加器,仿真验证其功能,并下载到实验板测试,要求用拨码开关设定输入信号,发光二极管显示输出信号;○3用3线-8线译码器(74LS138)和逻辑门设计实现函数F=CBA+CBA+CBA+CBA,仿真验证其功能,并下载到实验班测试。

要求用拨码开关设定输入信号,发光二极管显示输出信号;2.实验二:○1用VHDL语言设计实现一个4位二进制奇校验器,输入奇数个…1‟时,输出为…1‟,否则输出为…0‟,仿真验证其功能,并下载到实验板测试。

要求用拨码开关设定输入信号,发光二极管显示输出信号;○2用VHDL语言设计实现一个8421码转换为余3码的代码转换器,仿真验证其功能,并下载到实验板测试。

要求用拨码开关设定输入信号,发光二极管显示输出信号;○3用VHDL语言设计实现一个共阴极7段数码管译码器,仿真验证其功能,并下载到实验班测试。

要求用拨码开关设定输入信号,发光二极管显示输出信号;3.实验三:○1用VHDL语言设计实现一个分频系数为12,分频输出信号占空比为50%的分频器。

要求在Quartus Ⅱ平台上设计程序并仿真验证设计;○2用VHDL语言设计实现一个带异步复位的8421码十进制计数器,仿真验证其功能,并下载到实验板测试。

要求用拨码开关设定输入信号,发光二极管显示输出信号;○3将分频器、8421十进制计数器、数码管译码器3个电路进行连接并下载测试。

4.实验四:○1用VHDL语言设计并实现六个数码管串行扫描电路,要求同时显示0、1、2、3、4、5这6个不同的数字图形到6个数码管上,仿真验证其功能,并下载到实验板测试;(必做)○2用VHDL语言设计并实现六个数码管循环左滚动,时钟点亮6个数码管,坐出右进,状态为:012345→123450→234501→345012→450123→501234→012345;(选做)○3用VHDL语言设计并实现六个数码管向左滚动,用全灭的数码管填充右边,直至全部变灭,然后再一次从右边一个一个地点亮。

图像采集处理基础实验班级:14060242 学号:1406024248 姓名:张新雨一、实验目的1、了解摄像头OV9655的功能及其接口的设计方法;2、用硬件描述语言编程实现OV9655接口电路,能够实时采集图像数据;3、能够识别特定的黑白图像块,并通过LED的亮、灭进行表示。

二、实验器材1、台式计算机 1台;2、可编程逻辑器件实验软件1套;3、可编程逻辑器件开发套件1套;4、OV9655转接板1套。

三、实验说明1、台式计算机用于向可编程逻辑逻辑器件实验软件提供编程、仿真及下载平台;2、可编程逻辑器件实验软件硬件描述语言的编程、仿真及下载提供平台;3、可编程逻辑器件开发套件为本实验提供硬件平台;4、OV9655转接板用于OV9655与开发套件的连接。

四、实验原理1、OV9655作为一种高分辨率摄像头,具有如下特性:1)工作电压低,灵敏度高,轻便易携;2)支持标准的SCCB接口;3)支持输出RGB、YUV、YCbCr格式数据;4)支持多种分辨率,包括SXGA(1280×1024)、VGA(640×480)等;5)支持多种自动图像控制功能,包括自动曝光控制、自动增益控制,自动白平衡等;6)支持视频缩放等。

2、 OV9655主要引脚说明:1)PWDN:掉电模式选择引脚;2)RESETB:复位引脚;3)PCLK:像素时钟输出引脚;4)XVCLK1:系统时钟引脚;5)HREF:行同步信号;6)VSYNC:场同步信号;7)SIO_C:SCCB接口时钟信号;8)SIO_D:SCCB接口数据信号;9)D[7:0]:像素点数据信号。

3、OV9655操作说明:在摄像头正常工作之前,必须配置好相应的寄存器才能使摄像头完成指定的功能,如配置摄像头的像素输出时钟、自动控制功能等。

通过标准的SCCB时序就能配置,SCCB时序图如图1所示。

图1此次实验中,将摄像头的输出信号配置成RGB565格式信号,其数据输出时序图如图2所示,图中为一行像素数据的时序,再配合场同步信号就能读取摄像头的输出信号,场同步信号在数据有效时地变低,在一帧数据结束后变高。

第1页 / 共10页

硬件描述语言实验

题目: 四位加法器实验 学 院 计算机科学与技术 学科门类 xxxxxxxxxx 专 业 xxxxxxxxxx 学 号 xxxxxxxxxx 姓 名 宁剑 指导教师 xxxx

20xx年 x月 x 日 第2页 / 共10页

硬件描述语言 一、实验题目:四位加法器 二、实验目的和要求 实验目的:进一步练习VHDL语言设计工程的建立与仿真的步骤和方法、熟悉VHDL语言三种描述方法。 实验要求:设计一个四位加法器,实体名称为“adder4_3”,其引脚及其功能如下表。

端口模式 端口名 数据类型 说明 in (输入)

A std_logic_vector(3 downto 0) 加数

B 加数 Ci std_logic 低位进位 out (输出) S std_logic_vector(3 downto 0) 和

Co std_logic 高位进位

要求应用一位全加器(实验二中所实现的)按如下电路图通过结构描述方式构造四位加法器。 本实验用实验二“full_adder”的实体作为元件,用port map语句描述出来将下图的电路,实现四位加法器,并与实验三、实验四的加法器进行比较。

三、实验内容 第3页 / 共10页

1、打开altera软件,建立一个名为adder4_3的vhdl工程。 2、要求调用实验二中的一位加法器,按照如下电路图通过结构描述方式构造一个四位加法器。

3、编译及修改错误。 4、建立波形并仿真。 5、根据仿真结果分析设计是否正确。 附录:实验二中一位加法器的引脚及功能如下图: 设计一个一位加法器,实体名称为“full_adder”,其引脚与功能如下表。

端口模式 端口名 数据类型 功能逻辑表达式 说明

in(输入) a std_logic 加数 b 加数 ci 低位进位

out(输出) s s <= a xor b xor ci 和 co co <= (a and b) or (a and ci) or (b and ci) 高位进位

附录:实验三中四位加法器的引脚及功能如下图: 设计一个四位加法器,实体名称为“adder4”,其引脚与功能如下表。

端口模式 端口名 数据类型 功能逻辑表达式 说明

in 输入

a std_logic_vector (3 downto 0) 加数 b 加数

ci std_logic 来自低位进位 out s std_logic_vector s(0) <= a (0) xor b(0) xor ci 和 第4页 / 共10页

输出 (3 downto 0) c0<= (a(0) and b(0)) or (a(0) and ci) or (b(0) and ci) …

co std_logic co<= (a(3) and b(3)) or (a(3) and c2) or (b(3) and c2) 向高位的进位

附录:实验四中四位加法器的引脚及功能如下图: 设计一个四位加法器,实体名称为“adder4_2”,其引脚与功能如下表。

端口模式 端口名 数据类型 说明 in (输入)

a std_logic_vector(3 downto 0) 加数

b 加数 ci std_logic 自低位进位 out (输出) s std_logic_vector(3 downto 0) 和

co std_logic 向高位进位

四、实验结果 部分代码截图: 通过此图我们得知编写的代码全部通过编译。 第5页 / 共10页

实验的RTL结构图: 由编译器所绘出的RTL结构图与实验所示的结构图完全吻合,达到了实验要求。

波形图及仿真结果: 可以看到,在两个加数A、B不超过15的情况下,共测试了13组数据,四位加法器的计算正确,实验得以验证。

附录:实验三仿真图(波形仿真图略) 第6页 / 共10页

附录:实验四仿真图(波形仿真图略)

五、实验总结 通过此次实验,我们运用了COMPONENT语句和PORT MAP语句调用实验二中的full_adder逻辑描述模块,无需在本次实验的构造体中再次对其进行定义和描述,大大缩短了实验周期,提高了效率,同时保证了实验结果的准确性。 VHDL语言对硬件系统的描述可以用3种不同风格的描述方式进行描述,即行为描述方式、寄存器传输(RTL)描述方式和结构描述方式。这3种描述方式从不同的角度对硬件系统的行为和功能进行了描述。其中,RTL和结构描述下的程序可进行逻辑综合,而行为描述程序大多用于系统仿真。我们对这3种方式各自的特点总结如下: (1)行为描述方式: ①行为描述方式是对系统数学模型的描述,其抽象程度比其他两种描述方式都高。 ②在这种高层次抽象的行为描述中,不需要描述硬件电路的具体逻辑关系,而是采用算术运算、关系运算等类数学公式的语句来描述器件行为。但是这些语句大都难以进行逻辑综合,因此行为描述方式不能进行逻辑综合。 ③这种描述方式主要用于系统数学模型的仿真和系统工作原理的仿真。 (2)寄存器传输(RTL)描述方式: ①RTL描述方式是一种明确规定寄存器描述的方法。 ②RTL描述方式是真正可以进行逻辑综合的描述方式。 ③在采用该方式进行编程时,所使用的VHDL语句有一定的限制。 (3)结构体描述方式: 第7页 / 共10页

①结构体描述方式可较方便地进行多层次的结构设计,增加了代码的重用性。 ②这种描述方式能提高设计效率,并将已有的设计成果方便的用到新的设计中。

六、附录 本次实验(四)的代码部分: library ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all;

entity full_adder is port ( a,b,ci : in STD_LOGIC; s,co : out STD_LOGIC ); end entity;

architecture rtl of full_adder is begin s <= a xor b xor ci; co <= (a and b) or (a and ci) or (b and ci); end rtl;

library ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all;

entity adder4_3 is port ( A,B : in std_logic_vector(3 downto 0); Ci : in std_logic; S : out std_logic_vector(3 downto 0); Co : out std_logic ); end entity;

architecture rtl of adder4_3 is COMPONENT full_adder IS port ( a,b,ci : in STD_LOGIC; s,co : out STD_LOGIC ); END COMPONENT; 第8页 / 共10页

SIGNAL C0,C1,C2:STD_LOGIC; begin u0:full_adder port map(A(0),B(0),Ci,S(0),C0); u1:full_adder port map(A(1),B(1),C0,S(1),C1); u2:full_adder port map(A(2),B(2),C1,S(2),C2); u3:full_adder port map(A(3),B(3),C2,S(3),Co); end rtl;

实验二中一位加法器full_adder的代码如下: library ieee; use ieee.std_logic_1164.all;

entity full_adder is port ( a,b,ci : in STD_LOGIC; s,co : out STD_LOGIC ); end entity;

architecture rtl of full_adder is begin

s <= a xor b xor ci; co <= (a and b) or (a and ci) or (b and ci);

end rtl; 实验三中四位加法器adder4代码: library ieee;

use ieee.std_logic_1164.all; entity adder4 is port(a,b:in std_logic_vector(3 downto 0); ci:in std_logic; s:out std_logic_vector(3 downto 0); co:out std_logic); end entity; architecture rtl of adder4 is signal c0,c1,c2:std_logic; begin