组合逻辑电路

- 格式:doc

- 大小:912.50 KB

- 文档页数:31

第五章 组合逻辑电路

内容提要

【熟悉】组合逻辑电路的特点(功能、结构)

【掌握】组合逻辑电路的一般分析方法和设计方法

【熟悉】常见的五种组合逻辑电路

【掌握】中规模集成组合逻辑电路的应用(扩展与实现组合逻辑函数)

【了解】组合逻辑电路中的竞争和险象

一.一.网上导学

二.二.本章小结

三.三.典型例题

四.四.习题答案

网上导学

一. 一. 组合逻辑电路的特点:p123

功能:输出仅取决于该时刻的输入而与电路原状态无关(无记忆功能);

结构(无记忆元件,无反馈环路).

二. 二. 组合逻辑电路的一般分析方法(组合逻辑电路图→求解逻辑功能):

组合逻辑电路图→列出逻辑函数表达式(迭代法,由输入逐级向后推) →求

标准表达式或简化的表达式(转换或化简) →列出相应的真值表→判断电路功

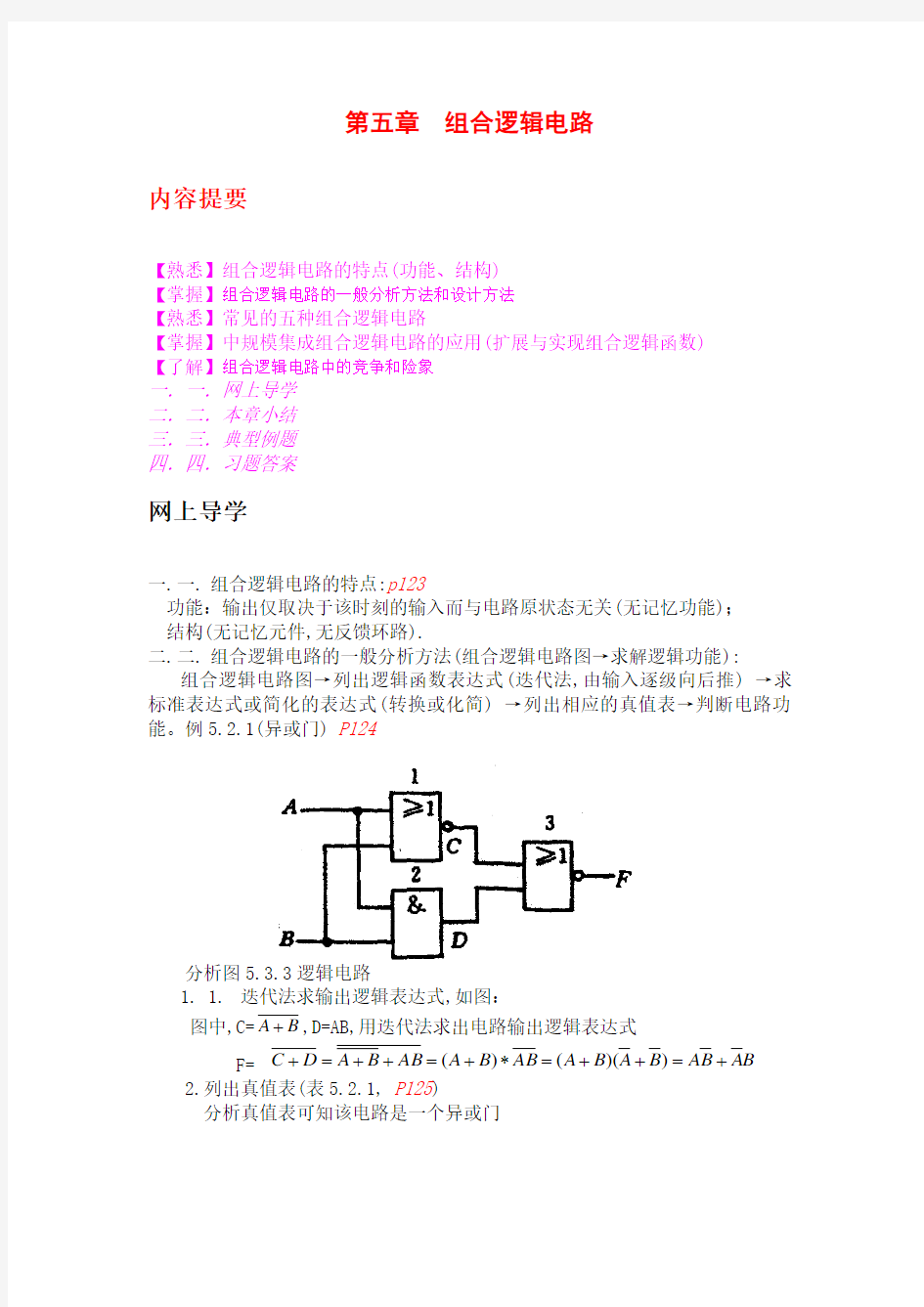

能。例5.2.1(异或门) P124

分析图5.3.3逻辑电路

1. 1. 迭代法求输出逻辑表达式,如图:

图中,C=B A +,D=AB,用迭代法求出电路输出逻辑表达式 F=B A B A B A B A AB B A AB B A D C +=++=*+=++=+))(()(

2.列出真值表(表5.2.1, P125)

分析真值表可知该电路是一个异或门

例2. 试分析下面电路

1.由上图可知E=AB,D=AC,G=BC,迭代法得F=E+D+G=AB+AC+BC

2. 列出相应的真值表

由真值表可以看出,该逻辑电路是一个三人多数表决电路。

三. 三.组合逻辑电路的一般设计方法:

根据设计要求(要实现的逻辑功能)→画出逻辑电路图.

设计要求→列出真值表(确定输入、输出变量及它们的逻辑关系) →化简写出简化的逻辑表达式(→或转换成逻辑器件所需的表达形式)→画出逻辑图。例5.3.1(多数表决器) P125。

举例:设计一个一位加法器(半加器)电路.

1. 1.该电路有两个输入An、Bn和二个输出Sn和Cn,

Sn=Bn An Bn An Bn An ⊕=+,Cn=An*Bn

3. 3. 画出逻辑图

四.组合逻辑电路中的竞争和险象:P126~P129 竞争:因门电路的传输时延而造成多路信号由于经过不同路径产生的时差现象;险象:由竞争产生的错误输出;检查(产生条件:输入存在互补变化;消除:

添加冗余项.

竞争(B=0)

*消除方法:参考例5.4.3(P128)

四. 四. 常见的五种组合逻辑电路:p129-p141

着重于其功能和输出与输入的对应逻辑关系.

1. 1. 编码:将输入信号转换成对应的数码信号;

编码器:互斥输入,方块图、逻辑图P130

功能表见表5.5.1(P129)

优先编码,方块图、逻辑图 、功能表P131;

2. 2.译码:将输入的码组翻译变换成对应的输出信号,是编码的逆过程;译码器:二进制译码器, 方块图、逻辑图;

功能表见表5.5.3(P133)

数字显示译码器:

功能表见表5.5.5(P133)

七段显示十进制数字

十进制数字显示p133;十进制数码显示

3.多路选择器:又叫数据选择器,在地址输入端的控制下从多路数据输入中选择

一个送到公共输出端.方块图,逻辑图,功能表P134;

由功能表可以写出其输出表达式:

Y=3

1

2

1

1

1

1

)

(

)

(

)

(

)

(D

A

A

D

A

A

D

A

A

D

A

A+

+

+

4选1多路选择器两种电路

4.数值比较器:比较两个二进制数的大小。P135-137

一位二进制数比较器

二位二进制数值比较器

4. 4.加法器:实现二进制数加法运算

全加器,逐位进位加法器,超前加法器。P137-141

半加器,

全加器逻辑图, (全加器真值表见表5.5.8P138)

逐位进位加法器 (电路简单,连接方便,但运算速度慢) ,超前进位形成电路 (运算速度快,但电路复杂)

五. 五.中规模集成组合逻辑电路及应用:应用着重于扩展(分级扩展和级联扩展)

1.1.中规模集成译码器74139:2线-4线译码器,功能表、逻辑图 P142

74154 :4线-16线译码器,功能表、逻辑图, P142-143

分级扩展:图5.6.3,利用允许端用一片74139和四片74154扩展为6线-64线译

级联扩展(补充):用二片74139实现3线-8线译码器,参考典型例题;

2. 2.中规模集成多路选择器74153:双4选1,功能表P144;

分级扩展:图5.6.5,用五片74153扩展为双16选1, P147;

级联扩展(补充):用74153实现8选1,参考典型例题;

实现组合逻辑函数:例5.6.1,用8选1和4选1实现三变量函数p145-147, 用8选1;用4选1〔注:本书利用对比真值表的方法欠简单明嘹,可用多路选择器的输出表达式和逻辑函数表达式对比的方法, 参考典型例题〕;

解:由表 5.6.4得 F’=∑m(2,3,5,6)=C AB C B A BC A C B A +++,与多路选择器比较:

F=76543210ABCD ABCD ABCD ABCD ABCD ABCD ABCD ABCD +++++++