奇数与半整数分频器

- 格式:doc

- 大小:43.50 KB

- 文档页数:6

分频器(已通过仿真)1.偶数(even )50%占空比偶分频比较简单,假设为N分频,只需计数到N/2-1,然后时钟翻转、计数清零,如此循环就可以得到N(偶)分频。

代码如下:module fp_even(clk_out,clk_in,rst);output clk_out;input clk_in, rst;reg [8:0] cnt;reg clk_out;parameter N=20;always @ (posedge clk_in or negedge rst)beginif(!rst)begincnt <= 0;clk_out <= 0;endelsebeginif(cnt==N/2-1)begin clk_out <= !clk_out;cnt<=0;endelsecnt <= cnt + 1;endendendmodule/*******test********/module fp_even_test;reg in,rst;wire out;initialbeginin=0;rst=0;#5 in=1;rst=1;#6000 rst=0;endalways #50 in=~in;fp_even f(.clk_out(out),.clk_in(in),.rst(rst));endmodule2 奇数(odd)50%占空比实现奇数(N)分频,分别用上升沿计数到(N-1)/2,再计数到N-1;用下降沿计数到(N-1)/2,再计数到N-1,得到两个波形,然后把它们相或即可得到N分频。

代码如下:module fp_odd(clk_out,clk_p,clk_n,clk_in,rst);output clk_out, clk_p,clk_n;input clk_in,rst;reg [8:0]cnt_p,cnt_n;reg clk_p,clk_n;parameter N=19;always @ (posedge clk_in or negedge rst) beginif(!rst)cnt_p <= 0;else if(cnt_p==N-1)cnt_p <=0;elsecnt_p <= cnt_p + 1;endalways @ (posedge clk_in or negedge rst) beginif(!rst)clk_p <= 0;else if(cnt_p==(N-1)/2) clk_p <= !clk_p;else if(cnt_p==N-1)clk_p <= !clk_p;endalways @ (negedge clk_in or negedge rst) beginif(!rst)cnt_n <= 0;else if(cnt_n==N-1)cnt_n <=0;elsecnt_n <= cnt_n + 1;endalways @ (negedge clk_in or negedge rst) beginif(!rst)clk_n <= 0;else if(cnt_n==(N-1)/2)clk_n <= !clk_n;else if(cnt_n==N-1)clk_n <= !clk_n;endassign clk_out = clk_p | clk_n;endmodule/******test*****************/module fp_odd_test;reg in,rst;wire out,clk_p,clk_n;initialbeginin=0;rst=0;#5 in=1;rst=1;#6000 rst=0;endalways #50 in=~in;fp_odd f(.clk_out(out),.clk_in(in),.rst(rst),.clk_p(clk_p),.clk_n(clk_n)); endmoduleendassign clk_out = clk_p | clk_n;endmodule同理,可以通过改变参量N的值和计数变量cnt_p和cnt_n的位宽实现任意奇分频。

用Verilog语言实现奇数倍分频电路3分频5分频7分频Verilog是一种硬件描述语言(HDL),用于描述数字电路的行为和结构。

使用Verilog语言实现奇数倍分频电路可以分为以下几个步骤:1.定义输入和输出端口通过module关键字定义一个模块,并指定输入和输出端口的信号。

```verilogmodule OddDividerinput clk,output reg out_3x,output reg out_5x,output reg out_7x```2.定义局部变量和计数器定义一个局部变量和一个计数器,用于跟踪时钟周期并确定何时输出。

```verilogreg [2:0] count;```3.实现分频逻辑使用always块,根据计数器的值判断何时输出,并在输出端口上更新信号。

```verilogif (count == 3'b000) beginout_3x <= !out_3x;endif (count == 3'b001) beginout_5x <= !out_5x;endif (count == 3'b010) beginout_7x <= !out_7x;endcount <= count + 1;end```4.结束模块使用endmodule关键字结束模块定义。

```verilogendmodule完整的Verilog代码如下:```verilogmodule OddDividerinput clk,output reg out_3x,output reg out_5x,output reg out_7xreg [2:0] count;if (count == 3'b000) begin out_3x <= !out_3x;endif (count == 3'b001) begin out_5x <= !out_5x;endif (count == 3'b010) begin out_7x <= !out_7x;endcount <= count + 1;endmodule```以上代码实现了一个奇数倍分频电路,其中输入时钟信号为`clk`,输出分别是3倍分频的信号`out_3x`,5倍分频的信号`out_5x`和7倍分频的信号`out_7x`。

分频器的设计一、课程设计目的1.学会使用电路设计与仿真软件工具Hspice,熟练地用网表文件来描述模拟电路,并熟悉应用Hspice内部元件库。

通过该实验,掌握Hspice的设计方法,加深对课程知识的感性认识,增强电路设计与综合分析能力。

2.分频器大多选用市售成品,但市场上出售的分频器良莠不齐,质量上乘者多在百元以上,非普通用户所能接受。

价格在几十元以下的分频器质量难以保证,实际使用表现平庸。

自制分频器可以较少的投入换取较大的收获。

二.内容分频器-概述分频器是指使输出信号频率为输入信号频率整数分之一的电子电路。

在许多电子设备中如电子钟、频率合成器等,需要各种不同频率的信号协同工作,常用的方法是以稳定度高的晶体振荡器为主振源,通过变换得到所需要的各种频率成分,分频器是一种主要变换手段。

早期的分频器多为正弦分频器,随着数字集成电路的发展,脉冲分频器(又称数字分频器)逐渐取代了正弦分频器,即使在输入输出信号均为正弦波时也往往采用模数转换-数字分频-数模转换的方法来实现分频。

正弦分频器除在输入信噪比低和频率极高的场合已很少使用。

分频器-作用分频器是音箱中的“大脑”,对音质的好坏至关重要。

功放输出的音乐讯号必须经过分频器中的各滤波元件处理,让各单元特定频率的讯号通过。

要科学、合理、严谨地设计好音箱之分频器,才能有效地修饰喇叭单元的不同特性,优化组合,使得各单元扬长避短,淋漓尽致地发挥出各自应有的潜能,使各频段的频响变得平滑、声像相位准确,才能使高、中、低音播放出来的音乐层次分明、合拍,明朗、舒适、宽广、自然的音质效果。

在一个扬声器系统里,人们把箱体、分频电路、扬声器单元称为扬声器系统的三大件,而分频电路对扬声器系统能否高质量地还原电声信号起着极其重要的作用。

尤其在中、高频部分,分频电路所起到的作用就更为明显。

其作用如下:合理地分割各单元的工作频段;合理地进行各单元功率分配;使各单元之间具有恰当的相位关系以减少各单元在工作中出现的声干涉失真;利用分频电路的特性以弥补单元在某频段里的声缺陷;将各频段圆滑平顺地对接起来。

以下考虑的分频都是占空比为50%的。

要是不要求占空比为50%将更加简单一些。

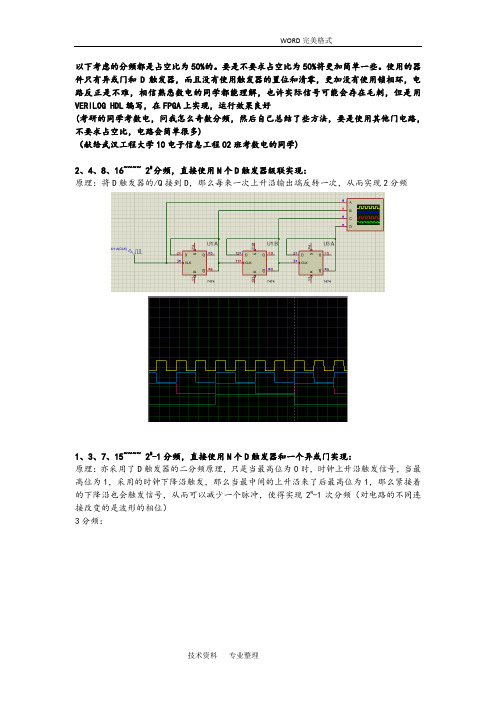

使用的器件只有异或门和D触发器,而且没有使用触发器的置位和清零,更加没有使用锁相环,电路反正是不难,相信熟悉数电的同学都能理解,也许实际信号可能会存在毛刺,但是用VERILOG HDL编写,在FPGA上实现,运行效果良好(考研的同学考数电,问我怎么奇数分频,然后自己总结了些方法,要是使用其他门电路,不要求占空比,电路会简单很多)(献给武汉工程大学10电子信息工程02班考数电的同学)2、4、8、16~~~~ 2N分频,直接使用N个D触发器级联实现:原理:将D触发器的/Q接到D,那么每来一次上升沿输出端反转一次,从而实现2分频1、3、7、15~~~~ 2N-1分频,直接使用N个D触发器和一个异或门实现:原理:亦采用了D触发器的二分频原理,只是当最高位为0时,时钟上升沿触发信号,当最高位为1,采用的时钟下降沿触发,那么当最中间的上升沿来了后最高位为1,那么紧接着的下降沿也会触发信号,从而可以减少一个脉冲,使得实现2N-1次分频(对电路的不同连接改变的是波形的相位)3分频:15分频:实质上该电路后面阶段都是二分频,可见前面都是输出信号的倍频成分,因此对该电路而言,第三个触发器输出为7.5分频,第二个输出为3.75分频,第一个为1.875分频,当然波形可能并不是一个规则的,只是说在单位时间内,脉冲数目有那么多任意偶数(N)分频,可以采用N/2个D触发器:原理:将第一个触发器的D接到最后一个触发器的反向输出端,其他的触发器的D接到前级的正向输出端,所有的时钟信号接到一起(以下对6分频为例说明)使用三个D触发器(当然也可以使用3分频后再二分频,只是多个异或门)三个触发器的输出端Q0 Q1 Q2在每个上升沿后的波形:Q0 Q1 Q2 /Q20 0 0 11 0 0 11 1 0 11 1 1 00 1 1 00 0 1 00 0 0 1可见总共六个状态,以Q作为输出可以满足六分频要求,而且占空比为50%任意奇数(2*N-1)分频可以使用采用N个D触发器和一个异或门:原理:同上,将任意Q或/Q(仅仅只是相位不同)接到异或门一端,时钟接到异或门另外一端,异或门输出作为总共的时钟(也是采用在中间时,同时采集了一个脉冲的上下边沿,从而减少了一个脉冲周期)5分频为例说明:对信号进行半整数n.5分频(n>=1, 1.5,2.5,3.5,·······)(因为这些信号倍频后是原信号的奇数分频,因此这些信号占空比不可能为50%)采用2组2n+1分频(相位不能相同)后将两个信号进行异或可能输出倍频信号(相位相差90度,占空比1:1,相位相差180,输出1,相位相差0,输出0,此处关键是相位的问题)1.5分频举例:也许以上方法会消耗过多的门电路:因此可以采用如下方法化简:1.5分频:或,1.5分频:2.5分频:3.5分频:3.5分频:(该电路最后输出为7分频,因此前级(第二个触发器)输出为3.5分频,理论第一个触发器的输出是3.5的倍频,即原信号1.75分频,但是波形明显不规则)(因为相位的选择上的原因,可能导致波形占空比有很大的差别,甚至无法倍频,因此需要选择合适的相位)需要VERILOG HDL代码的童鞋可以留言啦。

分频器设计实验报告一、实验目的本次实验的主要目的是设计并实现一个分频器,以深入理解数字电路中频率分频的原理和实现方法,掌握相关的电路设计和调试技能。

二、实验原理分频器是一种数字电路,用于将输入的时钟信号的频率降低为原来的 1/N,其中 N 为分频系数。

常见的分频器有偶数分频器和奇数分频器。

偶数分频器的实现相对简单,可以通过计数器来实现。

当计数器计数值达到分频系数的一半时,输出信号翻转,从而实现偶数分频。

奇数分频器的实现则较为复杂,通常需要使用多个触发器和组合逻辑电路来实现。

在本次实验中,我们将分别设计一个偶数分频器(以 4 分频为例)和一个奇数分频器(以 3 分频为例)。

三、实验器材1、数字电路实验箱2、示波器3、逻辑分析仪4、集成电路芯片(如 74LS 系列芯片)四、实验步骤(一)4 分频器的设计与实现1、原理图设计使用 74LS161 四位二进制同步计数器作为核心器件。

将计数器的时钟输入端连接到输入时钟信号。

将计数器的输出端 Q2 和 Q0 通过与门连接到一个 D 触发器的时钟输入端。

将 D 触发器的输出端作为 4 分频器的输出。

2、硬件连接按照原理图在数字电路实验箱上进行芯片的插装和连线。

3、调试与测试输入一个频率稳定的时钟信号。

使用示波器观察输入时钟信号和输出分频信号的波形,验证是否实现了 4 分频。

(二)3 分频器的设计与实现1、原理图设计使用两个 D 触发器和一些组合逻辑门(如与门、或门等)来实现 3 分频。

第一个 D 触发器的输出作为第二个 D 触发器的输入。

通过组合逻辑门对两个 D 触发器的输出进行处理,得到 3 分频的输出信号。

2、硬件连接按照原理图在数字电路实验箱上进行芯片的插装和连线。

3、调试与测试输入一个频率稳定的时钟信号。

使用示波器观察输入时钟信号和输出分频信号的波形,验证是否实现了 3 分频。

五、实验结果(一)4 分频器实验结果通过示波器观察输入时钟信号和输出分频信号的波形,发现输出信号的频率为输入信号频率的 1/4,成功实现了 4 分频功能。

标签:Verilog分频器N倍奇数分频器.(V erilog)N_odd_divider.v / Verilogmodule N_odd_divider (input i_clk,input rst_n,output o_clk);parameter N = N_odd; // 设置奇数(除1外)倍分频parameter M = ?; // M="N/2"// bit_of_N: N_odd的二进制位宽reg [(bit_of_N - 1):0] cnt_p; // 上升沿计数单位reg [(bit_of_N - 1):0] cnt_n; // 下降沿计数单位reg clk_p; // 上升沿时钟reg clk_n; // 下降沿时钟assign o_clk = clk_n & clk_p; // 按位与(作用:掩码)// 上升沿计数器: 0~(N-1)always @ (posedge i_clk or negedge rst_n)beginif (!rst_n)cnt_p <= 0;elsebeginif (cnt_p == N-1)cnt_p <= 0;elsecnt_p <= cnt_p + 1'b1;endend// 生成上升沿时钟// 0~(N>>1) ↑ -> 1;((N/2)+1)~(N-1) ↑ -> 0 always @ (posedge i_clk or negedge rst_n) beginif (!rst_n)clk_p <= 0;elsebeginif (cnt_p <= M) // 0 ~ (N/2)clk_p <= 1;elseendend// 下降沿计数器: 0~(N-1)always @ (negedge i_clk or negedge rst_n) beginif (!rst_n)cnt_n <= 0;elsebeginif (cnt_n == N-1)cnt_n <= 0;elsecnt_n <= cnt_n + 1'b1;endend// 生成下降沿时钟// 0~(N>>1) ↓ -> 1;((N/2)+1)~(N-1) ↓ -> 0 always @ (negedge i_clk or negedge rst_n) beginif (!rst_n)elsebeginif (cnt_n <= M) // 0 ~ (N/2) clk_n <= 1;elseclk_n <= 0;endendendmodule仿真波形图1. N_odd = 3图2. N_odd = 5另见N倍偶数分频器.(Verilog)参考资料1. 真OO 无双的(原創) 如何設計除頻器? (SOC) (Verilog) (MegaCore)2. 位运算.(C)奇数倍分频(Verilog)奇数倍分频的方法:(以5分频为例)(n=N-1),图中,COUNT0采用上沿计数,COUNT1采用下沿计数,DIV0和DIV1是分别是上沿触发器和下沿触发器的输出,计数为0~(n/2-1)时DIV0、DIV1<='1'此处为0~1,计数为n/2~(n-1)时DIV0、DIV1<='0'此处为2~4,DIV5_CLK是DIV0和DIV1的或门输出。

EDA技术与VHDL语言课程大作业设计题目:电子分频器姓名:李露班级:自动化10(2)学号: 41003010208目录1. 设计背景2. 设计方案2.1计数器模块2.2任意偶数分频模块2.3任意奇数分频模块2.4设计思路3. 数字分频器模块的VHDL源程序3.1 任意偶数分频的VHDL源程序(dvf.VHD)3.2 任意奇数分频的VHDL源程序(dvf.VHD)4. 源程序总体描述5. 波形仿真图6. 总结7. 参考文献1.设计背景EDA技术作为计算机硬件设计中的关键设计技术之一,是每一位将来希望从事涉及电子系统与集成电路设计研究领域工作的人所必须掌握的一门技术。

时序逻辑电路作为其主要设计与研究的电路类型之一,在EDA中占据着重要的位置,而时钟信号在时序逻辑电路有占据着重要的位置,它决定了时序逻辑单元中的状态何时更新。

时钟信号作为一种有固定周期并与运行状态无关的信号量,在边沿触发机制中,只有上升沿或下降沿才是有效信号,才能控制逻辑单元状态量的改变。

为满足不同的时序电路要求,对时钟信号进行分频也显得格外重要基于EDA技术的数控分频器设计,采用的是用软件的方法设计硬件的EDA (电子设计自动化)技术。

作为EDA技术重要组成部分的VHDL 硬件描述语言是一种符合IEEE工业标准的建模语言。

用它设计的数控分频器可作为一个模块,移植到很多数字电路系统中,且极易修改,只要修改程序中的某几条语句,就可使最大分频系数得到改变。

整个设计过程简单、快捷。

可从根本上减少硬件调试的时间,为总体设计完成争取宝贵的时间。

2. 设计方案2.1 计数器模块通过计数器来记录clk的信号个数,分别有以上升沿计数和以下降沿计数。

偶数计数器可采用以上升沿计数,即每当clk从0变为1时记一个数,下降沿计数是当clk从1变为0时记一个数2.2 任意偶数分频模块定义一个计数器对输入时钟进行计数,在计数的前一半时间里,输出高电平,在计数的后一半时间里,输出低电平,这样输出的信号就是占空比为50%的偶数分频信号。

【摘要】现代科技的发展对信号源提出了越来越高的要求,要求信号源的频带宽、频率分辨率高、频率稳定度高、相位噪声和杂散很低、能程控等。

频率合成技术是产生高精度频率信号的主要技术,是通讯、雷达、仪器仪表、高速计算机和导航设备中的一个重要组成部分。

可控分频器可完成分频的预置功能,基于FPGA的可控分频器由外部的晶体产生标准频率,利用外部的9位输入端口输入控制信号来实现对其分频系数的控制。

在可控分频器的设计中,采用9位输入数据代表其分频系数,其中高8位代表整数位,最后一位代表小数位,可以实现最大分频系数为28的整数分频和28-0.5的半整数分频。

且对任意分频都能实现等占空比或非等占空比其中之一可以实现50%的奇数分频。

利用VHDL语言编程,并用QUARTERS||8.0进行仿真,用FPGA 芯片实现。

关键词:半整数,可控分频器,VHDL, FPGA【Abstract】the development of modern science and technology of signal source put forward more and more high demands that the signal frequency resolution width frequently, high stability, high frequency and phase noise and stray very low, can program-controlled etc. Function. Frequency synthesis technology is the main frequency signal produced high-precision technology, is communication, radar, instrumentation, high-speed computer and navigation equipment an important component. Controllable points can be completed the frequency of an the preset functions, separate frequency controlled points based on FPGA frequency of an external crystals produce by using standard frequency, the nine input external input control signal to achieve its points of frequency coefficients control. In the design of controlled points in the frequency of an input data, using nine represents its points, including high frequency coefficients 8 bits represent the integer bit, finally a on behalf of small digital, can realize maximum points frequency coefficients of integer points for 28 frequency and the half integer 28-0.5 separate frequency. And forarbitrary points frequency can realize the 390v or 390v one can achieve 50% of the odd points frequency. Use VHDL language programming, and simulation | | 8.0 QUARTERS, using the FPGA chip realized.Keywords: half-integer, simulated, controllable frequency divider, VHDL目录第1章.引言................................................................................................................................ - 4 - 第2章.基于FPGA分频器的要求及特点................................................................................ - 5 - 2.1 技术要求.................................................................................................................... - 5 - 2.2 技术特点.................................................................................................................... - 5 - 2.3 基于FPGA的可控分频器介绍.................................................................................. - 5 - 第3章.方案设计......................................................................................................................... - 6 -3.1方案讨论....................................................................................................................... - 6 -3.2程序设计的思路........................................................................................................... - 7 -3.2.1 整数等占空比分频.......................................................................................... - 7 -3.2.2整数非等占空比分频.................................................................................... - 10 -3.2.3 半整数分频.................................................................................................... - 13 - 第4章小结................................................................................................................................ - 16 - 参考文献.................................................................................................................................... - 17 -第1章.引言在数字逻辑电路设计中,分频器是一种基本电路,通常用来对某个给定频率进行分频,得到所需的频率。

奇数与半整数分频器

1 / 6

奇数分频器

1 引言

分频器在CPLD/FPGA设计中使用频率非常高,尽管目前大部分设计

中采用芯片厂家集成的锁相环资源,但是对于要求奇数倍分频、小数倍分

频的应用场合却往往不能满足要求。硬件工程师希望有一种灵活的设计方

法,根据需要,在实验室就能设计分频器并马上投入使用,更改频率时无

需改动原器件或电路板,只需重新编程,在数分钟内即可完成。

对于偶数分频,使用一模N计数器模块即可实现,即每当模N计数器

从0开始计数至N时,输出时钟进行翻转,同时使计数器复位,使之从0

开始重新计数,以此循环即可实现。但对于奇数分频,实现50%的占空比

却是比较困难的。下面给出占空比50%的奇数分频器的设计源程序和仿真

结果。

2 VHDL程序

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL; --添加库

ENTITY fdiv IS --设计实体

PORT( clk,reset : IN STD_LOGIC; --端口说明

preset: IN INTEGER; --preset: 分频预置数

clkout : OUT STD_LOGIC); - -clkout : 分频后得到的时钟

END fdiv;

ARCHITECTURE behave OF fdiv IS --设计构造体

SIGNAL s1,s2 : STD_LOGIC; --内部信号s1,s2

SIGNAL cnt : INTEGER RANGE 0 TO preset-1; --模为preset的计数信号

BEGIN

P1: PROCESS(clk,reset) --计数器

BEGIN

IF reset='1' THEN

cnt<=0;

ELSIF clk'event AND clk='1' THEN

IF cnt=0 THEN

奇数与半整数分频器

2 / 6

cnt<=preset-1;

ELSE

cnt<=cnt-1;

END IF;

END IF;

END PROCESS;

P2: PROCESS(clk,reset) --信号1

BEGIN

IF reset='1' THEN

s1<='1';

ELSIF clk'event AND clk='1' THEN

IF cnt=0 THEN --计数信号为0时,S1翻转

s1<=NOT s1;

ELSE

s1<=s1;

END IF;

END IF;

END PROCESS;

P3: PROCESS(clk,reset) --信号2

BEGIN

IF reset='1' THEN

s2<='1';

ELSIF clk'event AND clk='0' THEN

IF cnt=(preset-1)/2 THEN --计数信号为N时,S2翻转

s2<=NOT s2;

ELSE

s2<=s2;

END IF;

END IF;

END PROCESS;

clkout<= s1 XOR s2; -- 异或输出

END BEHAVE;

程序说明:以上程序实现任意奇数为PRESET的50%占空比分频,计

数器CNT的模值为PRESET,计数器是为了控制信号S1和信号S2,使两

奇数与半整数分频器

3 / 6

信号保持恒定的时间差。信号S1为上升沿触发,在CNT=0时翻转,信

号S2为下降沿触发,在CNT=(PRESET-1)/2 时翻转。然后将S1和S2异

或输出,这样就实现了PRESET的50%占空比分频。

3 仿真波形

本设计选用的是FLEX10K系列器件,仿真波形如图所示。图中预置

值为7,即分频器分频值为7,由图中的波形可以看出,结果正确。

波形分析:计数器CNT的模值为7,信号S1是上升沿触发,CNT=0

时翻转,S2是下降沿触发,CNT=(7-1)/2=3时翻转,然后将S1和S2

异或输出,这样就实现了50%占空比的7分频。

奇数与半整数分频器

4 / 6

半整数分频器

1 引言

在数字系统设计中,分频器是一种基本电路。整数分频器的实现非常

简单,可采用标准的计数器来实现。但在某些场合下,时钟源所给频率与

所需频率不成整数倍关系,譬如把12MHZ的时钟频率分频为1.024MHZ

的时钟,分频系数为11.71875,此时可采用小数分频器进行分频。这类问

题在通信ASIC的设计中用的比较多。作为小数分频器的一个特例,本程

序完成的是半整数分频器的设计。

2 半整数分频器的基本原理

设有一个5MHZ的时钟源,但电路中需要产生一个2MHZ的时钟信号,

这时就需要设计一个分频比为2.5的分频器,可采用以下方法:设计一个

模3的计数器,再设计一个扣除脉冲电路,加在模3计数器输出之后,每

来两个脉冲就扣除一个脉冲,就可以得到分频系数为2.5的小数分频器。

实现扣除的电路是由二分频器和异或逻辑组成。采用类似的方法,可以设

计出分频系数为任意半整数的分频器。

3 电路组成

设需要设计一个分频系数为N-0.5的分频器,其电路可由一个模N计

数器、二分频器和一个异或门组成,如图(一)所示。

4 VHDL程序

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

异或逻辑 模N计

数器

二分频器

inclk outclk

图(一)通用半整数分频器电路组成

奇数与半整数分频器

5 / 6

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY decount IS

PORT(inclk: IN STD_LOGIC; --时钟源

preset: IN STD_LOGIC_VECTOR(3 DOWNTO 0); --预置分频值N

outclk: BUFFER STD_LOGIC); --输出时钟

END decount;

ARCHITECTURE decount_arch OF decount IS

SIGNAL clk,divide2: STD_LOGIC; --clk:异或门输出;

--divide2:二分频器输出

SIGNAL count: STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

clk<=inclk XOR divide2; --inclk与divide2异或后,

--作为模N计数器的时钟

PROCESS(clk)

BEGIN

IF(clk'event and clk='1') THEN

IF(count="0000") THEN

count<=preset-1; --置整数分频值N

outclk<='1';

ELSE

count<=count-1; --模N计数器减法计数

outclk<='0';

END IF;

END IF;

END PROCESS;

PROCESS(outclk)

BEGIN

IF(outclk'event and outclk='1') THEN

divide2<=not divide2; --输出时钟二分频

END IF;

END PROCESS;

END decount_arch;

说明:以上程序实现对时钟源inclk进行分频系数为N-0.5的分频,得

奇数与半整数分频器

6 / 6

到输出频率outclk。Preset输入端口是预置分频值N,本程序中preset设为

4位宽的位矢量,即分频系数为16以内的半整数值。若分频系数大于16,

需同时增大preset和count的位宽,两者的位宽应始终一致。

5 仿真波形

本设计选用的是MAX7000系列的EPM7032LC44-15器件实现,仿真

波形如图(二)所示。图中预置值设为3,即分频器分频值为2.5,由图中

outclk与inclk的波形可以看出,outclk会在inclk每隔2.5个周期处产生一

个上升沿,从而实现分频系数为2.5的分频器。

图(二) 仿真结果