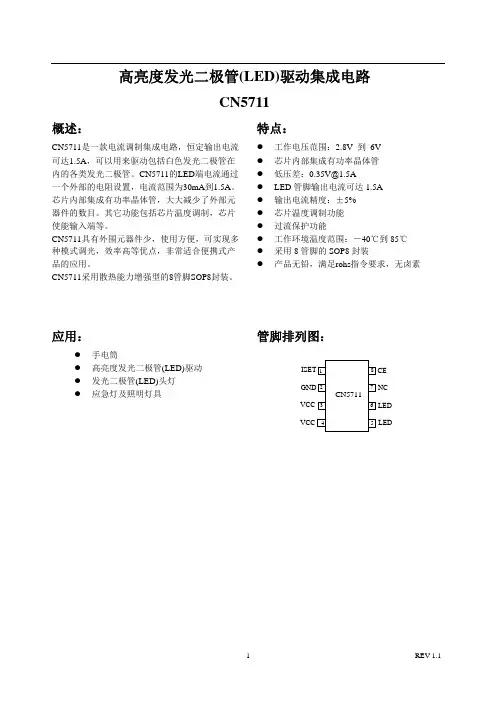

集成电路外引线图

- 格式:doc

- 大小:1.25 MB

- 文档页数:7

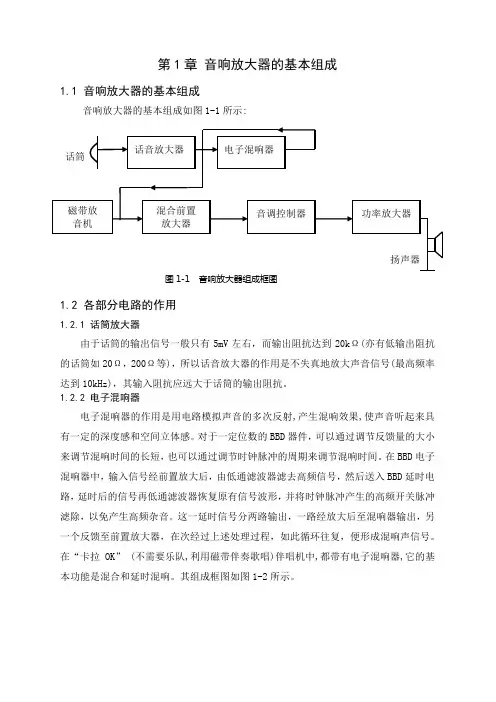

第1章音响放大器的基本组成1.1 音响放大器的基本组成音响放大器的基本组成如图1-1所示:1.2 各部分电路的作用1.2.1 话筒放大器由于话筒的输出信号一般只有5mV左右,而输出阻抗达到20kΩ(亦有低输出阻抗的话筒如20Ω,200Ω等),所以话音放大器的作用是不失真地放大声音信号(最高频率达到10kHz),其输入阻抗应远大于话筒的输出阻抗。

1.2.2 电子混响器电子混响器的作用是用电路模拟声音的多次反射,产生混响效果,使声音听起来具有一定的深度感和空间立体感。

对于一定位数的BBD器件,可以通过调节反馈量的大小来调节混响时间的长短,也可以通过调节时钟脉冲的周期来调节混响时间。

在BBD电子混响器中,输入信号经前置放大后,由低通滤波器滤去高频信号,然后送入BBD延时电路,延时后的信号再低通滤波器恢复原有信号波形,并将时钟脉冲产生的高频开关脉冲滤除,以免产生高频杂音。

这一延时信号分两路输出,一路经放大后至混响器输出,另一个反馈至前置放大器,在次经过上述处理过程,如此循环往复,便形成混响声信号。

在“卡拉OK” (不需要乐队,利用磁带伴奏歌唱)伴唱机中,都带有电子混响器,它的基本功能是混合和延时混响。

其组成框图如图1-2所示。

图1-2 电子混响器组成框图图中,集成电路BBD 称为模拟延时器,其内部有由场效应管构成的多级电子开关和高精度存储器。

在外加时钟脉冲作用下,这些电子开关不断地接通和断开,对输入信号进行取样。

保持并向后级传递,从而使BBD 的输出信号相对于输入信号延迟乐一段时间。

BBD 的级数越多,时钟脉冲的频率越高,延迟时间越长。

BBD 配有专用时钟电路,如MN3102时钟电路与MN3200系列的BBD 配套。

电子混响器的实验电路图所示(附录一),其中两级二阶低通滤波器(MFB)A 1、A 2滤去4kHz(语音)以上的高频成分,反相器A 3用于 隔离混响器的输出与输入级间的相互影响。

RP 1调节混响器的输入电压,RP 2调节 MN3207的平衡输出以减少失真,RP 3控制延时时间,RP 4控制混响器的输出电压。

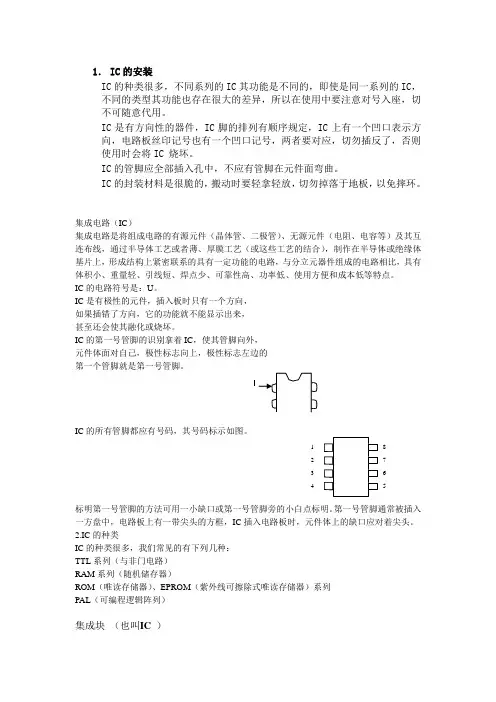

1. IC 的安装IC 的种类很多,不同系列的IC 其功能是不同的,即使是同一系列的IC ,不同的类型其功能也存在很大的差异,所以在使用中要注意对号入座,切不可随意代用。

IC 是有方向性的器件,IC 脚的排列有顺序规定,IC 上有一个凹口表示方向,电路板丝印记号也有一个凹口记号,两者要对应,切勿插反了,否则使用时会将IC 烧坏。

IC 的管脚应全部插入孔中,不应有管脚在元件面弯曲。

IC 的封装材料是很脆的,搬动时要轻拿轻放,切勿掉落于地板,以免摔环。

集成电路(IC )集成电路是将组成电路的有源元件(晶体管、二极管)、无源元件(电阻、电容等)及其互连布线,通过半导体工艺或者薄、厚膜工艺(或这些工艺的结合),制作在半导体或绝缘体基片上,形成结构上紧密联系的具有一定功能的电路,与分立元器件组成的电路相比,具有体积小、重量轻、引线短、焊点少、可靠性高、功率低、使用方便和成本低等特点。

IC 的电路符号是:U 。

IC 是有极性的元件,插入板时只有一个方向,如果插错了方向,它的功能就不能显示出来,甚至还会使其融化或烧坏。

IC 的第一号管脚的识别拿着IC ,使其管脚向外,元件体面对自己,极性标志向上,极性标志左边的第一个管脚就是第一号管脚。

IC 的所有管脚都应有号码,其号码标示如图。

标明第一号管脚的方法可用一小缺口或第一号管脚旁的小白点标明。

第一号管脚通常被插入一方盘中,电路板上有一带尖头的方框,IC 插入电路板时,元件体上的缺口应对着尖头。

2.IC 的种类IC 的种类很多,我们常见的有下列几种:TTL 系列(与非门电路)RAM 系列(随机储存器)ROM (唯读存储器)、EPROM (紫外线可擦除式唯读存储器)系列PAL (可编程逻辑阵列)集成块 (也叫IC )1 2 3 4 8 7 6 51、集成块的实物外形如下图:2.集成块在底板上用字母IC 表示,图形如下表示:从构造上分有:直插式引脚集成块和贴片引脚式集成块3、集成块的分类从用途上分有:模拟运算集成块和数字运算集成块4.集成块的标称方法:用字母和数字直接表示出来,不同型号代表不同用途。

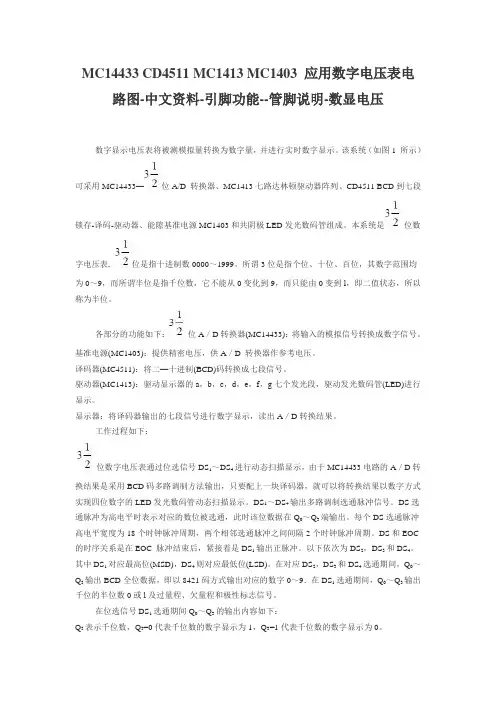

MC14433 CD4511 MC1413 MC1403 应用数字电压表电路图-中文资料-引脚功能--管脚说明-数显电压数字显示电压表将被测模拟量转换为数字量,并进行实时数字显示。

该系统(如图1 所示)可采用MC14433—位A/D 转换器、MC1413七路达林顿驱动器阵列、CD4511 BCD到七段锁存-译码-驱动器、能隙基准电源MC1403和共阴极LED发光数码管组成。

本系统是位数字电压表, 位是指十进制数0000~1999。

所谓3位是指个位、十位、百位,其数字范围均为0~9,而所谓半位是指千位数,它不能从0变化到9,而只能由0变到l,即二值状态,所以称为半位。

各部分的功能如下:位A/D转换器(MC14433):将输入的模拟信号转换成数字信号。

基准电源(MC1403):提供精密电压,供A/D 转换器作参考电压。

译码器(MC4511):将二—十进制(BCD)码转换成七段信号。

驱动器(MC1413):驱动显示器的a,b,c,d,e,f,g七个发光段,驱动发光数码管(LED)进行显示。

显示器:将译码器输出的七段信号进行数字显示,读出A/D转换结果。

工作过程如下:位数字电压表通过位选信号DS1~DS4进行动态扫描显示,由于MC14433电路的A/D转换结果是采用BCD码多路调制方法输出,只要配上一块译码器,就可以将转换结果以数字方式实现四位数字的LED发光数码管动态扫描显示。

DS1~DS4输出多路调制选通脉冲信号。

DS选通脉冲为高电平时表示对应的数位被选通,此时该位数据在Q0~Q3端输出。

每个DS选通脉冲高电平宽度为18个时钟脉冲周期,两个相邻选通脉冲之间间隔2个时钟脉冲周期。

DS和EOC 的时序关系是在EOC 脉冲结束后,紧接着是DS1输出正脉冲。

以下依次为DS2,DS3和DS4。

其中DS1对应最高位(MSD),DS4则对应最低位(LSD)。

在对应DS2,DS3和DS4选通期间,Q0~Q3输出BCD全位数据,即以8421码方式输出对应的数字0~9.在DS1选通期间,Q0~Q3输出千位的半位数0或l及过量程、欠量程和极性标志信号。

郑州电力职业技术学院毕业生论文题目:_基于单片机的数字电能表设计__系别___电力工程系______专业___建筑电气工程技术___班级__建筑电气班_____学号___ 09401060170___姓名____周莉_______论文成绩指导教师答辩成绩主答辩教师综合成绩答辩委员会主任目录摘要 (3)关键词 (3)一、工作原理 (4)1.1数字电流表的工作原理 (5)1.2电流采样电路的性能 (5)1.3显示电路与电流采样电路的逻辑关系 (5)1.4放大器 (5)1.5峰值保持电路 (10)A转换芯片 (13)1.6双积分型D1.7独立式非编码键盘的接口 (14)1.8 LED动态显示器接口及显示方式 (14)1.9 89C51单片机 (16)二、测量系统的总体结构设计 (20)2.1 系统框图 (20)2.2整机设计 (19)三、程序流程图 (23)四、实验结果 (26)参考文献 (2725)摘要本电流表各模块之间使用标准信号进行传输的,这些标准信号都符合国际标准。

国际电工委员会在1973年四月第65次技术委员会通过的标准规定了国际统一信号标准,过程控制系统的模拟直流信号为4到20MA,模拟直流电压信号为1到5伏,我国的DDZ-3型电动单元组合仪表采用了国际的信号标准。

关键词电流采样,A/D转换,放大器,单片机随着微电子技术的迅速发展和超大规模集成电路的出现,特别是单片机的出现,正在引起测量、控制仪表领域新的技术革命。

采用单片机作为测量仪器的主控制器,这种以单片机为主体的新型智能仪表将计算机技术与测量控制技术结合在一起,在测量过程自动化,测量结果数据处理以及功能的多样化方面都取得了巨大的进步。

基于单片机的智能综合仪表是基于智能化、数字化、网络化新一代智能仪表的设计理念,采用智能调理、灵巧总线、工业网络、液晶显示、电子储存技术,综合指示仪表、调节仪表、积算仪表与记录仪表功能.具有高测量控制精度、高可靠性稳定性的特点。

1.集成块好坏判断现在的电子产品往往由于一块集成电路损坏,导致一部分或几个部分不能正常工作,影响设备的正常使用。

那么如何检测集成电路的好坏呢?通常一台设备里面有许多个集成电路,当拿到一部有故障的集成电路的设备时,首先要根据故障现象,判断出故障的大体部位,然后通过测量,把故障的可能部位逐步缩小,最后找到故障所在。

要找到故障所在必须通过检测,通常修理人员都采用测引脚电压方法来判断,但这只能判断出故障的大致部位,而且有的引脚反应不灵敏,甚至有的没有什么反应。

就是在电压偏离的情况下,也包含外围元件损坏的因素,还必须将集成块内部故障与外围故障严格区别开来,因此单*某一种方法对集成电路是很难检测的,必须依赖综合的检测手段。

现以万用表检测为例,介绍其具体方法。

我们知道,集成块使用时,总有一个引脚与印制电路板上的“地”线是焊通的,在电路中称之为接地脚。

由于集成电路内部都采用直接耦合,因此,集成块的其它引脚与接地脚之间都存在着确定的直流电阻,这种确定的直流电阻称为该脚内部等效直流电阻,简称R内。

当我们拿到一块新的集成块时,可通过用万用表测量各引脚的内部等效直流电阻来判断其好坏,若各引脚的内部等效电阻R内与标准值相符,说明这块集成块是好的,反之若与标准值相差过大,说明集成块内部损坏。

测量时有一点必须注意,由于集成块内部有大量的三极管,二极管等非线性元件,在测量中单测得一个阻值还不能判断其好坏,必须互换表笔再测一次,获得正反向两个阻值。

只有当R内正反向阻值都符合标准,才能断定该集成块完好。

在实际修理中,通常采用在路测量。

先测量其引脚电压,如果电压异常,可断开引脚连线测接线端电压,以判断电压变化是外围元件引起,还是集成块内部引起。

也可以采用测外部电路到地之间的直流等效电阻(称R外)来判断,通常在电路中测得的集成块某引脚与接地脚之间的直流电阻(在路电阻),实际是R内与R外并联的总直流等效电阻。

在修理中常将在路电压与在路电阻的测量方法结合使用。

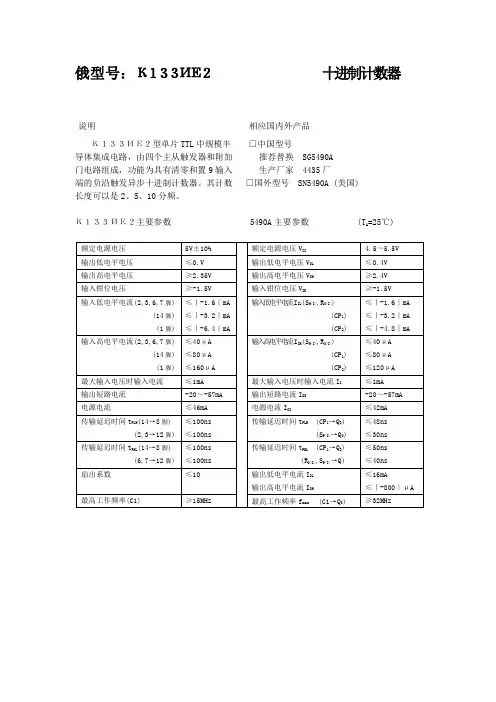

俄型号:К133ИЕ2十进制计数器说明相应国内外产品К133ИЕ2型单片TTL中规模半□中国型号导体集成电路,由四个主从触发器和附加推荐替换 SG5490A门电路组成,功能为具有清零和置9输入生产厂家 4435厂端的负沿触发异步十进制计数器。

其计数□国外型号 SN5490A (美国)长度可以是2、5、10分频。

К133ИЕ2主要参数 5490A主要参数 (T A=25℃)К133ИЕ2逻辑图和外引线排列 5490A功能表和外引线排列俄型号:К133ИЕ54位二进制计数器说明相应国内外产品К133ИЕ5型单片TTL中规模半□中国型号导体集成电路,由四个主从触发器和附加推荐替换 SG5493A门电路组成。

可组成二分频计数器和三级生产厂家 4435厂二进制计数器,具有清零输入端。

□国外型号 SN5493A (美国)AК133ИЕ5逻辑图和外引线排列 5493A功能表和外引线排列俄型号:К133ЛА28输入与非门说明相应国内外产品К133ЛА2型单片TTL小规模半□中国型号导体集成电路,功能为8输入端与非门。

推荐替换 JT5430生产厂家 4435厂□国外型号 SN5430 (美国)К133ЛА2逻辑图和外引线排列 5430逻辑图和外引线排列俄型号:К133ЛА3四2输入与非门说明相应国内外产品К133ЛА3型单片TTL小规模半□中国型号导体集成电路,由四个独立的而又完全相推荐替换 JT5400同的2输入端与非门组成。

生产厂家 4435厂□国外型号 SN5400 (美国)AК133ЛА3逻辑图和外引线排列 5400逻辑图和外引线排列说明相应国内外产品К133ЛА4型单片TTL小规模半□中国型号导体集成电路,由三个独立的而又完全相推荐替代 JT5410同的3输入端与非门组成。

生产厂家 4435厂□国外型号 SN5410 (美国)AК133ЛА4逻辑图和外引线排列* 5410逻辑图和外引线排列*注:俄产品输出脚顺序与5410不同,选用时应注意。

混合集成电路的外引线键合技术

李自学;金建东;席亚莉

【期刊名称】《电子元器件应用》

【年(卷),期】2003(5)3

【摘要】混合集成电路外引线键合的方式很多.与混合集成电路的内引线键合不同,外引线键合时,键合丝的1端在管壳的引线柱上.因此,管壳外引线金属镀层的结构、镀层材料、键合丝的性能和键合工艺等因素都将影响混合电路外引线键合的质量.本文主要对Au丝球焊、Au丝点焊、SiAl丝超声焊等不同的键合工艺及其对应的金属学系统进行研究,并对其结果进行比较.采用Au丝点焊工艺键合混合电路外引线的效果最佳.

【总页数】4页(P49-51,58)

【作者】李自学;金建东;席亚莉

【作者单位】航天科技集团西安微电子技术研究所,陕西,西安,710054;航天科技集团西安微电子技术研究所,陕西,西安,710054;航天科技集团西安微电子技术研究所,陕西,西安,710054

【正文语种】中文

【中图分类】TN405.96

【相关文献】

1.集成电路内引线键合工艺材料失效机制及可靠性 [J], 马鑫;何小琦

2.集成电路封装中的引线键合技术 [J], 黄玉财;程秀兰;蔡俊荣

3.四十五所:全自动集成电路引线键合机替代进口实现量产 [J], 四十五所

4.集成电路封装中的引线键合技术探究 [J], 孙千十

5.集成电路铜引线键合强度试验方法标准研究 [J], 李锟

因版权原因,仅展示原文概要,查看原文内容请购买。

集成电路封装形式介绍(图解)BGA BGFP132 CLCCCPGA DIP EBGA 680L FBGA FDIP FQFP 100L JLCC BGA160L LCCLDCC LGA LQFPLQFP100L Metal Qual100L PBGA217L PCDIP PLCC PPGAPQFP QFP SBA 192L TQFP100L TSBGA217L TSOPCSPSIP:单列直插式封装.该类型的引脚在芯片单侧排列,引脚节距等特征与DIP基本相同.ZIP:Z型引脚直插式封装.该类型的引脚也在芯片单侧排列,只是引脚比SIP粗短些,节距等特征也与DIP基本相同.S-DIP:收缩双列直插式封装.该类型的引脚在芯片两侧排列,引脚节距为1.778mm,芯片集成度高于DIP.SK-DIP:窄型双列直插式封装.除了芯片的宽度是DIP的1/2以外,其它特征与DIP相同.PGA:针栅阵列插入式封装.封装底面垂直阵列布置引脚插脚,如同针栅.插脚节距为2.54mm或1.27mm,插脚数可多达数百脚.用于高速的且大规模和超大规模集成电路.SOP:小外型封装.表面贴装型封装的一种,引脚端子从封装的两个侧面引出,字母L状.引脚节距为1.27mm.MSP:微方型封装.表面贴装型封装的一种,又叫QFI等,引脚端子从封装的四个侧面引出,呈I字形向下方延伸,没有向外突出的部分,实装占用面积小,引脚节距为1.27mm.QFP:四方扁平封装.表面贴装型封装的一种,引脚端子从封装的两个侧面引出,呈L字形,引脚节距为1.0mm,0.8mm,0.65mm,0.5mm,0.4mm,0.3mm,引脚可达300脚以上.SVP:表面安装型垂直封装.表面贴装型封装的一种,引脚端子从封装的一个侧面引出,引脚在中间部位弯成直角,弯曲引脚的端部与PCB键合,为垂直安装的封装.实装占有面积很小.引脚节距为0.65mm,0.5mm.LCCC:无引线陶瓷封装载体.在陶瓷基板的四个侧面都设有电极焊盘而无引脚的表面贴装型封装.用于高速,高频集成电路封装.PLCC:无引线塑料封装载体.一种塑料封装的LCC.也用于高速,高频集成电路封装.SOJ:小外形J引脚封装.表面贴装型封装的一种,引脚端子从封装的两个侧面引出,呈J字形,引脚节距为1.27mm.BGA:球栅阵列封装.表面贴装型封装的一种,在PCB的背面布置二维阵列的球形端子,而不采用针脚引脚.焊球的节距通常为1.5mm,1.0mm,0.8mm,与PGA相比,不会出现针脚变形问题.CSP:芯片级封装.一种超小型表面贴装型封装,其引脚也是球形端子,节距为0.8mm,0.65mm,0.5mm等.TCP:带载封装.在形成布线的绝缘带上搭载裸芯片,并与布线相连接的封装.与其他表面贴装型封装相比,芯片更薄,引脚节距更小,达0.25mm,而引脚数可达500针以上.介绍:1 基本元件类型Basic Component Type盒形片状元件(电阻和电容)Box Type Solder ComponentResistor and Capacitor小型晶体管三极管及二极管SOTSmall Outline TransistorTransistor and Diodeelf类元件Melf type Component [Cylinder]Sop元件Small outline package小外形封装TSop元件Thin Sop薄形封装SOJ元件Small Outline J-lead Package 具有丁形引线的小外形封装QFP元件Quad Flat Package方形扁平封装PLCC元件Plastic Leaded Chip Carrier 塑料有引线芯片载体BGABall Grid Array 球脚陈列封装球栅陈列封装CSPChip Size Package芯片尺寸封装2特殊元件类型Special Component Type钽电容( Tantalium Capacitor)铝电解电容(Aalminum Electrolytic Capacitor )可变电阻( Variable Resistor )针栅陈列封装BGABin Grid Array连接器ConnectorIC卡连接器IC Card Connector附BGA 封装的种类APBGAPlastic BGA塑料BGABCBGACeramic BGA陶瓷BGACCCGACeramic Column Grid Array陶瓷柱栅陈列DTBGATape Automated BGA载带自动键合BGAEMBGA微小BGA注芯片的封装技术已经历了好几代的变迁从DIPQFPPGABGA到CSP再到MCM技术指标一代比一代先进包括芯片面积与封装面积之比越来越接近于1适用频率越来越高耐温性能越来越好引脚数增多引脚间距减少重量减少可靠性提高使用更加方便等(MCMMulti Chip Model 多芯片组件)英汉缩语对照SMTSurface Mount Technology 表面贴装技术SMDSurface Mounting Devices 表面安装器件SMBSurface Mounting Printed Circuit Board 表面安装印刷板DIP Dual-In-Line Package 双列直插式组件THTThough Hole Mounting Technology插装技术PCB Printed Circuit Board 印刷电路板SMC Surface Mounting Components表面安装零件PQFP Plastic Quad Flat Package 塑料方形扁平封装SOIC Small Scale Integrated Circuit小外形集成电路LSI Large Scale Integration 大规模集成注意芯片封装图鉴封装大致经过了如下发展进程:结构方面:DIP封装(70年代)->SMT工艺(80年代 LCCC/PLCC/SOP/QFP)->BGA封装(90年代)->面向未来的工艺(CSP/MCM)材料方面:金属、陶瓷->陶瓷、塑料->塑料;引脚形状:长引线直插->短引线或无引线贴装->球状凸点;装配方式:通孔插装->表面组装->直接安装一.TO 晶体管外形封装TO(Transistor Out-line)的中文意思是“晶体管外形”。

集成电路好坏判断与拆卸方法集成电路块的好坏,可用万用表测量集成块各脚对地暄工作电压、对地电阻值和工作电流是否正常。

还可将集成块取下,测量集成块各脚与接地섚之间的阻值是否正常,在取下集成块的时候可测釯其外接电路各脚的对地电阻值是否正常。

需要特别说明的是,在更换集成电路块时,一定要注意焊接质量和焊接时间。

在更换集成电路块时一般要求用同型号、同规格的集成电路来进行替换。

实在找不到原型号、原规格的集成电路块时,可考虑用相近功能的集成电路块来代替,但需要注意的是,代替时要弄清供电电压、阻抗匹配、引脚位置以及外围控制电路等问题。

集成电路应用电路识图方法1.集成电路应用电路图功能集成电路应用电路图具有下列一些功能:①它表达了集成电路各引脚外电路结构、元器件参数等,从而表示了某一集成电路的完整工作情况。

②有些集成电路应用电路中,画出了集成电路的内电路方框图,这时对分析集成电路应用电路是相当方便的,但这种表示方式不多。

③集成电路应用电路有典型应用电路和实用电路两种,前者在集成电路手册中可以查到,后者出现在实用电路中,这两种应用电路相差不大,根据这一特点,在没有实际应用电路图时可以用典型应用电路图作参考,这一方法修理中常常采用。

④一般情况集成电路应用电路表达了一个完整的单元电路,或一个电路系统,但有些情况下一个完整的电路系统要用到两个或更多的集成电路。

2.集成电路应用电路特点集成电路应用电路图具有下列一些特点:①大部分应用电路不画出内电路方框图,这对识图不利,尤其对初学者进行电路工作分析时更为不利。

②对初学者而言,分析集成电路的应用电路比分析分立元器件的电路更为困难,这是对集成电路内部电路不了解的原缘,实际上识图也好、修理也好,集成电路比分立元器件电路更为方便。

③对集成电路应用电路而言,大致了解集成电路内部电路和详细了解各引脚作用的情况下,识图是比较方便的。

这是因为同类型集成电路具有规律性,在掌握了它们的共性后,可以方便地分析许多同功能不同型号的集成电路应用电路。

555定时器摘要:555定时器是一种多用途的数字——模拟混合集成电路,利用它能极方便地构成施密特触发器、单稳态触发器和多谐振荡器。

由于使用灵活、方便,所以555定时器在波形的产生与交换、测量与控制、家用电器、电子玩具等许多领域中都得到了广泛应用。

本文主要介绍了555定时器的工作原理及其在单稳态触发器、多谐振荡器方面的应用。

关键词:数字——模拟混合集成电路;施密特触发器;波形的产生与交换555芯片引脚图及引脚描述555的8脚是集成电路工作电压输入端,电压为5~18V,以UCC表示;从分压器上看出,上比较器A1的5脚接在R1和R2之间,所以5脚的电压固定在2UCC/3上;下比较器A2接在R2与R3之间,A2的同相输入端电位被固定在UCC/3上。

1脚为地。

2脚为触发输入端;3脚为输出端,输出的电平状态受触发器控制,而触发器受上比较器6脚和下比较器2脚的控制。

当触发器接受上比较器A1从R脚输入的高电平时,触发器被置于复位状态,3脚输出低电平;2脚和6脚是互补的,2脚只对低电平起作用,高电平对它不起作用,即电压小于1Ucc/3,此时3脚输出高电平。

6脚为阈值端,只对高电平起作用,低电平对它不起作用,即输入电压大于2 Ucc/3,称高触发端,3脚输出低电平,但有一个先决条件,即2脚电位必须大于1Ucc/3时才有效。

3脚在高电位接近电源电压Ucc,输出电流最大可打200mA。

4脚是复位端,当4脚电位小于0.4V时,不管2、6脚状态如何,输出端3脚都输出低电平。

5脚是控制端。

7脚称放电端,与3脚输出同步,输出电平一致,但7脚并不输出电流,所以3脚称为实高(或低)、7脚称为虚高。

1概述1.1 555定时器的简介555定时器是一种多用途的数字——模拟混合集成电路,利用它能极方便地构成施密特触发器、单稳态触发器和多谐振荡器。

由于使用灵活、方便,所以555定时器在波形的产生与交换、测量与控制、家用电器、电子玩具等许多领域中都得到了广泛应用。

fc1179引脚定义

FC1179是一种型号的集成电路,通常我们可以在相关的数据手册或者规格书中找到对于引脚定义的详细说明。

然而,由于我无法直接引用具体的数据手册,我会尽量从一般情况下集成电路的引脚定义来回答你的问题。

通常情况下,集成电路的引脚定义包括了每个引脚的功能、电气特性、以及引脚的物理排列。

在数据手册中,会有引脚图示以及对每个引脚的详细说明。

一般来说,引脚定义会包括输入输出信号的类型、电压范围、最大电流、引脚的物理位置等信息。

另外,对于特定型号的集成电路,引脚定义也会根据不同的封装类型而有所差异。

常见的封装类型包括DIP(双列直插封装)、SOIC(小轮廓集成电路封装)、QFN(无引线封装)等,每种封装类型的引脚定义都会有所不同。

在实际应用中,了解集成电路的引脚定义对于正确连接和使用集成电路至关重要。

工程师在设计电路板时需要准确理解每个引脚的功能和特性,以确保电路的正常工作。

总之,FC1179的引脚定义具体取决于该型号集成电路的数据手册或规格书中的说明,我建议你查阅相关的官方资料以获取准确的引脚定义信息。

附录1 集成电路外引线图

3四2输入异或门74LS86Y=A ⊕B

1A 1B 1Y 2A 2B 2Y GND

Vcc 4A 4B 4Y 3A 3B 3Y

4

六反向器74LS04

Y=A

1A 1Y 2A 2Y 3A 3Y GND

Vcc 6A 6Y 5A 5Y 4A

4Y

1四2输入与非门74LS00Y=A •B

1A 1B 1Y 2A 2B 2Y GND

Vcc 4A 4B 4Y 3A 3B 3Y

2

四2输入或门74LS32Y=A +

B

1A 1B 1Y 2A 2B 2Y GND

Vcc 4A 4B 4Y 3A 3B

3Y

7双4输入与非门74LS20Y=A •B •C •D

1A 1B NC 1C 1D 1Y GND

Vcc 2D 2C NC 2B 2A 2Y

8

2路3—3输入、2路2—2输入与或非门Y=(A •B •D)+(E •F •

G)1A 2A 2B 2C 2D 2Y GND

Vcc 1C 1B 1F 1E 1D

1Y

5四2输入与门74LS08Y=A •B

1A 1B 1Y 2A 2B 2Y GND

Vcc 4A 4B 4Y 3A 3B 3Y

6

三3输入与非门74LS10Y=A •B •

C

1A 1B 2A 2B 2C 2Y GND

Vcc 1C 1Y 3C 3B 3A 3Y

Y=(A •B)+(C •D)74LS51

11

四2输入与非门CD4011Y=A •B

1A 1B 1Y 2A 2B 2Y V SS

V DD 4A 4B 4Y 3A

3B 3Y 12

六反向器CD4069

Y=A

1A 1Y 2A 2Y 3A 3Y V SS

V DD 6A 6Y 5A 5Y 4A

4Y

9

四2输入或非门74LS02Y=A +B

1A 1B 1Y 2A 2B 2Y GND

Vcc 4A 4B 4Y 3A

3B 3Y 10

8输入与非门74LS30Y=A •B •C •D •E •F •G •

H A B C D E F GND

Vcc NC H G NC NC Y

15

16

13

14

1A 1B NC 1C 1D 1Y GND

V CC 2D 2C NC 2B 2A 2Y

双4输入与门

74LS211A 1B 2A 2B 2C 2Y GND

V CC 1C 1Y 3C 3B 3A 3Y

三3输入或非门74LS27Y=A+B+C Y=A •B •C •D

1A 1B 2A 2B 2C 2Y GND

V CC 1C 1Y 3C 3B 3A 3Y

三3输入与门74LS11

Y=A •B •

C 双上升沿

D 型触发器1CLR 1D 1CLK 1PR

E 1Q 1Q V SS

V DD CD40132CLR 2D 2CLK 2PRE

2Q 2Q

27

B C LT BI LE D

V SS

V DD 28

254线—七段译码器/驱动器(BCD B C LT BI/RBO

RBI D A V CC Y f Y g Ya Y b Y d Ye

26

GND

V CC 31

29

30

4线—16线译码器 74LS15445678910A B C D G215

G1A GND

输入,有限流电阻 ) 74LS48Yc Y f Y g Ya Y b Y d Ye

Yc 4线—七段译码器/驱动器(BCD 输入,无限流电阻 ) CD4511

4线—七段译码器/驱动器(OC)B C LT BI/RBO

RBI D A V CC Y f Y g Ya Y b Y d Ye

GND

74LS247Yc GND

V CC 3线—8线译码器 74LS138

A B C OE2A OE2B OE1Y7Y0Y1Y2Y3Y4Y6

Y5123141312011

双上升沿D 型触发器74LS74

1CLR 1D 1CLK 1PRE 1Q 1Q GND

Vcc 双下降沿JK 型触发器74LS112

GND Vcc 2CLR 2D 2CLK 2PRE 2Q 2Q

1CLR 1K 1CLK 1PRE 1Q 1Q 1J 2CLR 2K 2CLK 2PRE 2Q

2Q 2J

34

3532

33

38

四位十进制同步计数器(异步清零)CLR CLK A B C D GND

Vcc

RCO Q A Q B Q C Q D ET 39

十进制同步加/减计数器(双时钟)B Q B Q A DOWN

UP Q C Q D Vcc A CLR BO CO LOAD C 36

4位二进制全加器

37

2B2A2A1

B1GND

V CC C0LOAD

74LS160

EP 74LS192 CD40192GND

D

GND

V CC 10线—4线优先编码器 74LS14745678C B NC D 321A

9四位二进制同步计数器74LS161CLR CLK A B C D GND

V CC RCO Q A Q B Q C Q D ET LOAD

EP 74LS1484567E1A2GND

V CC E0GS 3210A1A0

8线—3线优先编码器GND

V CC 4线—10线译码器 74LS42

Y0Y1Y2Y3Y4Y5Y6A B C D Y9Y7

Y84位二进制同步加/减计数器(双时钟)B Q B Q A UP Q C Q D Vcc A CLR BO CO LOAD C 74LS193 CD40193GND

D

DOWN

74LS28313B3A3A4B4C4

4

42

456D 触发器(有清除端)

CLR 1Q 1D 2D 2Q 3D GND

V CC 6Q 6D 5D 5Q 4D 4Q 40

43

46

44

47

74LS174

3Q CLK

14位同步二进制计数/

分配,振荡器Q12Q13Q14Q6Q5Q7V SS

V DD Q10Q8Q9CLR CKI CKO CD4060

Q4CKO

4上升沿D

型触发器

CLR 1Q 1Q 1D 2D 2Q GND

V CC 74LS1752Q CLK

4Q 4Q 4D 3D 3Q 3Q 十进制计数/分频器

CD4017

Y5Y1Y0Y2Y6Y7V SS

V DD CLR CLK CLKEN CO Y9Y4Y3Y8

41

4

位双向通用移位寄存器SR SER

A CLR

B

C

D GND

V CC QA QB QC QD CLK S1SL SER S0

74LS194R9(1)NC R9(2)Q C Q B NC V CC GND

R0(2)CKB CKA Q D Q A 十进制计数器74LS290

R0(1)8

位移位寄存器Q A A CLR B Q C Q D GND

V CC Q H Q G Q F Q E CLK

Q B 74LS164四位二进制同步加/

减计数器B Q B Q A CTEN D/U Q C Q D Vcc A CLK RCO CO/BO LOAD C 74LS191GND

D

50

48

8段LED 数码显示器(共阴)

a b

c

d

e g 51

f

G N D

G N D

8段LED 数码显示器(共阳)

a b

c

d

e g

f V C C

V C C

555时基电路

GND TI OUT Vcc D TH VC

RD

49

E6E5E4E3E2E1GND

V CC E8E9E10E11E12E13D W E7G E0E14E15A B C

16选1数据选择器74LS1505253

4

双向模拟开关1IN/OUT V SS

V DD 1V C CD4066

8选1

数据选择器(原,反码输出)D3D2D1D0Y W GND

V CC D4D5D6D7A B 74LS151

G C

1IN/OUT 2IN/OUT 2IN/OUT

2V C 3V C 4V C

4IN/OUT 4IN/OUT 3IN/OUT 3IN/OUT

附录2 TTL集成电路分类、推荐工作条件

1.TTL集成电路分类

54系列:军用产品

74系列:民用产品

2.推荐工作条件。