总线接口芯片PCI9054及其在高速数据采集系统中的应用

- 格式:doc

- 大小:27.00 KB

- 文档页数:3

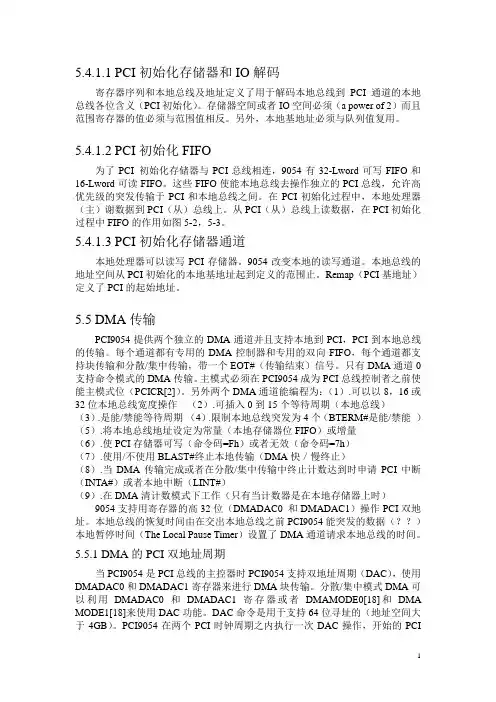

5.4.1.1 PCI初始化存储器和IO解码寄存器序列和本地总线及地址定义了用于解码本地总线到PCI通道的本地总线各位含义(PCI初始化)。

存储器空间或者IO空间必须(a power of 2)而且范围寄存器的值必须与范围值相反。

另外,本地基地址必须与队列值复用。

5.4.1.2 PCI初始化FIFO为了PCI 初始化存储器与PCI总线相连,9054有32-Lword可写FIFO和16-Lword可读FIFO。

这些FIFO使能本地总线去操作独立的PCI总线,允许高优先级的突发传输于PCI和本地总线之间。

在PCI初始化过程中,本地处理器(主)谢数据到PCI(从)总线上。

从PCI(从)总线上读数据,在PCI初始化过程中FIFO的作用如图5-2,5-3。

5.4.1.3 PCI初始化存储器通道本地处理器可以读写PCI存储器。

9054改变本地的读写通道。

本地总线的地址空间从PCI初始化的本地基地址起到定义的范围止。

Remap(PCI基地址)定义了PCI的起始地址。

5.5 DMA传输PCI9054提供两个独立的DMA通道并且支持本地到PCI,PCI到本地总线的传输。

每个通道都有专用的DMA控制器和专用的双向FIFO,每个通道都支持块传输和分散/集中传输,带一个EOT#(传输结束)信号。

只有DMA通道0支持命令模式的DMA传输。

主模式必须在PCI9054成为PCI总线控制者之前使能主模式位(PCICR[2])。

另外两个DMA通道能编程为:(1).可以以8,16或32位本地总线宽度操作(2).可插入0到15个等待周期(本地总线)(3).是能/禁能等待周期(4).限制本地总线突发为4个(BTERM#是能/禁能)(5).将本地总线地址设定为常量(本地存储器位FIFO)或增量(6).使PCI存储器可写(命令码=Fh)或者无效(命令码=7h)(7).使用/不使用BLAST#终止本地传输(DMA快/慢终止)(8).当DMA传输完成或者在分散/集中传输中终止计数达到时申请PCI中断(INTA#)或者本地中断(LINT#)(9).在DMA清计数模式下工作(只有当计数器是在本地存储器上时)9054支持用寄存器的高32位(DMADAC0 和DMADAC1)操作PCI双地址。

高速数据传输卡用PCI 9054总线控制器

谭博钊;陶然

【期刊名称】《电子产品世界》

【年(卷),期】2001(000)019

【摘要】介绍了一种基于PCI总线的数据传输卡的实现方案,应用PCI 9054总线控制器实现PCI总线接口,分析了PCI 9054的工作性能

【总页数】2页(P60,64)

【作者】谭博钊;陶然

【作者单位】北京理工大学电子工程系;北京理工大学电子工程系

【正文语种】中文

【中图分类】TP27

【相关文献】

1.基于PCI9054的LVDS高速数据通信卡设计 [J], 黄华;刘亚军

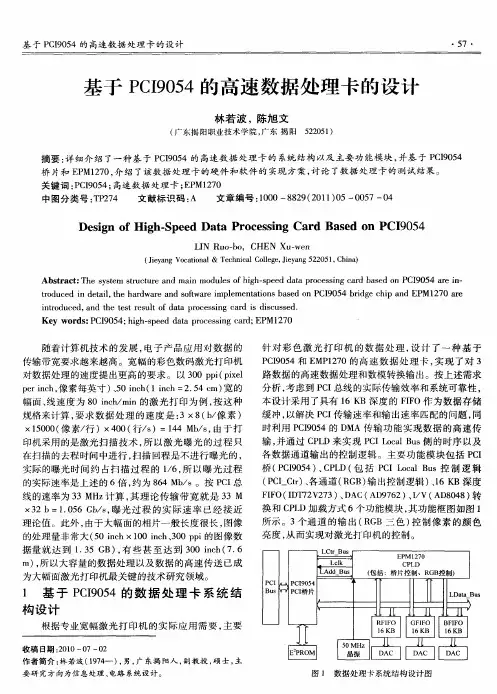

2.基于PCI9054的高速数据处理卡的设计 [J], 林若波;陈旭文

3.基于PCI-E总线高速数据传输卡的WDM驱动设计 [J], 景博利;孟李林;张亚运

4.基于NI PCI Express数字I/O卡的高速数据传输实现 [J], 王婧;王荣;周雪;易鸣

5.高速数据传输卡用PCI9054总线控制器 [J], 谭博钊; 陶然

因版权原因,仅展示原文概要,查看原文内容请购买。

第13卷,第3期 中国传媒大学学报自然科学版 Vol.13,No.3 2006年9月 JOURNAL OF C O M MUN I C ATI O N UN I V ERSI TY OF CH I N A S CI E NCE AND TECHNOLOGY Sept.2006基于PC I总线的高速数据采集板的设计熊伟信,杨隆鑫(中国传媒大学广播电视数字化工程中心,北京100024)摘 要:本文介绍了一种基于PC I总线的高速数据采集系统,该系统基于PC I总线技术,充分利用S DRAM的海量存储能力和FPG A的编程灵活性的特点,实现了数据的高速采集、S DRAM的海量存储和PC I的桥接传输三者的结合。

关键词:PC I;高速;FPG A;S DRAM;数据采集中图分类号:T N73 文献标识码:A 文章编号:1673-4793(2006)03-0077-05H i gh Speed Da t a Acqu isiti on Syste m Ba sed on PC I BusX I O NGW ei2xin,Y ANG Long2xin(ECDAV,Communicati on University of China,Beijing100024,China)Abstract:This paper intr oduces a high s peed data acquisiti on syste m based on PC I bus.It is based on the PC I bus;it takes the advantage of mass me mory of S DRAM and flexible p r ogra mm ing of FPG A.Achieve high s peed data acquisiti on,mass me mory of S DRAM and PC I bridge trans m issi on.Key words:PC I;high s peed;FPG A;S DRAM;data acquisiti on1 引言现代工业生产和科学研究对数据采集的要求日益提高,在瞬态信号测量、图像处理等一些高速、高精度的测量中,需要进行高速数据采集。

基于CPCI和光纤接口的数据采集卡设计与实现作者:李波张兴敢魏耀来源:《现代电子技术》2012年第05期摘要:设计了一套基于CPCI总线,PCI9054桥接芯片和可编程逻辑器件(FPGA)的高速数据采集卡。

FPGA作为本地主控芯片,根据工控机经PCI9054转发的采集命令,通过光纤接口实现与雷达接收机的通信。

采用高速RAM缓存数据,采集的接收机测试数据的分析结果可在工控机上显示,从而实现了对雷达接收机性能的快速测试。

该采集卡具有较强的通用性和可扩展性,详细介绍了高速数据采集卡的组成和工作原理、硬件设计。

关键词:光纤接口; CPCI总线; PCI9054; FPGA; 雷达接收机测试中图分类号:TN47-34文献标识码:A文章编号:1004-373X(2012)05-0095-04Design and implementation of data acquisition card based on CPCI bus and optical interfaceLI Bo, ZHANG Xing-(School of Electronic Science and Engineering, Nanjing University, Nanjing 210093, China)Abstract:To facilitate the testing of radar signal receiving system, a high-speed data acquisition card based on CPCI bus, PCI9054 bridge chip and programmable logic device (FPGA) was designed. Taking FPGA as a local master, and according to the acquisition command transmitted by the PCI9054 from computer, it can communicate with radar receiver through optical interface. SRAM is used to cache high-then the quick test of the radar receiver is implemented. The capture card has a strong versatility and scalability, the composition, working principle and hardware design of high-speed data acquisition card are described.Keywords: optical interface; CPCI bus; PCI9054; FPGA; radar receiver test收稿日期:2011-10-基金项目:2011年江苏省研究生创新计划项目(CXZZ11_0043)随着雷达技术的发展和雷达型号的增多,现代雷达接收机数据处理速度显著提高。

基于PCI9054总线控制器的数据接收和存储系统

王树志;周希德

【期刊名称】《电子设计应用》

【年(卷),期】2002(000)011

【摘要】本文介绍了基于PCI9054总线控制器的数据接收系统的构成及其应用,并给出了相关硬件接口电路和实现方案.

【总页数】3页(P16-17,28)

【作者】王树志;周希德

【作者单位】中国科学院空间中心;北方交通大学

【正文语种】中文

【相关文献】

1.高速率数据接收存储系统设计 [J], 徐洪信;申景诗;王凤阳

2.基于Windows NT的高速大容量数据接收与存储系统 [J], 石凌;孙政顺

3.卫星测试数据接收及存储系统的实现 [J], 杨猛; 吴超

4.卫星测试数据接收及存储系统的实现 [J], 杨猛; 吴超

5.高速数据传输卡用PCI9054总线控制器 [J], 谭博钊; 陶然

因版权原因,仅展示原文概要,查看原文内容请购买。

第30卷 第6期核电子学与探测技术Vo l.30 No.62010年 6月Nuclear Electronics &Detection T echno log yJune. 2010用于高速线阵CCD 的数据获取系统刘志艳1,陈香才1,江晓山2,章红宇2,向海生2,3,梁忠望2,胡 俊2,3(1.郑州大学,郑州450001;2.中国科学院高能物理研究所,北京100049;3.中国科学院研究生院,北京100049)摘要:介绍一种高速线阵CCD(Cha rge Coupled Device,光电耦合器件)的数据获取系统。

该系统采用了光纤传输,数据通过PCI 或U SB 接口送入计算机。

主要介绍了整个数据获取系统的搭建,P CI 接口端硬件、软件的设计和上位机数据获取程序的设计。

关键词:线阵CCD;光纤;PCI;L abVI EW ;数据获取中图分类号: T P 33 文献标识码: A 文章编号: 0258 0934(2010)06 0722 04收稿日期:2009 12 25作者简介:刘志艳(1984 ),女,河南新乡人,硕士研究生,主要研究方向为数据获取系统设计。

CCD 以其体积小、空间分辨率高、光敏单元的几何尺寸准确率高等优点及其高速发展的技术已经广泛应用在了众多的领域,如信号探测和数据获取方面[1]。

目前CCD 种类很多,包括线阵CCD 和面阵CCD 等。

通常情况下,面阵CCD 的读出像素远远超过线阵CCD,为了能及时读出数据,在同等要求下,选用线阵CCD 作为探测器件。

本文介绍了一个高速线阵CCD (IL C6 2048C)的数据获取系统,重点介绍了数据传输板的设计及上位机数据获取程序的设计。

1 系统介绍系统由高速线阵CCD 数据采集板、光纤以及PCI 光纤接收板组成。

CCD 数据采集板主要完成CCD 的控制及输出信号的处理与量化,采集得到的数据通过两种方式传输到计算机。

一种是通过U SB 直接送入计算机,另一种是通过光纤传输到基于PCI 总线接口的光纤接收板,并经PCI 总线传输到计算机中,系统框图如图1所示。

摘要:介绍了利用CPLD实现DSP芯片TMS320C6711b和PCI桥芯片PLX9054之间高速数据传输的系统设计方法,并给出了相应的系统设计原理图,同时对该系统的性能进行了分析。

关键词:PCI总线;TMS320C6711b;HPI(host port interface);局部总线;PLX9054CPLD是一种复杂的用户可编程逻辑器件。

它以操作灵活,开发迅速,投资风险低,可多次编程擦写和在系统可编程(InSystemprogrammability)等特点而成为一种可优化硬件电路设计且具竞争力的产品。

近年来,随着微电子集成工艺的不断发展,各种系列的CPLD可为简单PAL综合设计到先进实时硬件现场升级等全部范围内的任务设计提供全套的解决方法。

本文将给出如何使用Xilinx公司的CPLD器件XC9500LV实现PLX9054的局部总线(localbus)和DSP的HPI口之间的实时通信方法。

采用这种设计可以以单字或DMA方式完成主机与DSP之间的高速数据传输,传输速率可达到16Mb/s。

该方法可广泛应用于实时图形、图像及动画处理等场合。

图11设计需求1.1localbus接口要求PLX9054是PCI接口专用主从器件,包括通信、网络、磁盘控制、多媒体等高性能接口功能。

PLX9054可以以多种方式实现从pcibus端到localbus端(局部总线)的数据转移, 如直接传输,DMA控制传输等。

通过pcibus和localbus之间以六个可编程FIFO的不同连接可实现突发并发传输,同时也可通过串行EEPROM或PCI主控设备对PLX9054内部的配置寄存器进行设置,其简化框图如图1所示。

图中,通过配置EEPROM可设置PLX9054作为PCI总线的从设备工作在C模式下(数据、地址总线非复用),该模式下的localbus数据宽度为16bit,同时,通过使能外部设备就绪信号READY还可以禁止无限爆发操作(屏蔽BTERMbit)。

基于PCI总线的高速数据采集系统吴忠杰;林君;谢宣松【期刊名称】《吉林大学学报(信息科学版)》【年(卷),期】2005(023)002【摘要】在开发虚拟测试系统过程中,为解决高速数据采集中大容量数据传输和存储问题,以PCI(Peripheral Component Interconnect)总线控制器PLX9054为核心,设计了一种基于PCI总线的高速数据采集系统.给出了数据采集系统的基本结构及单元组成,重点阐述了PCI总线接口软硬件设计方法及注意事项,详细探讨了基于DriverWorks的设备驱动程序开发思想以及基于动态链接库和虚拟仪器软件开发平台的应用软件设计方法.该卡实现了PCI总线主控高速DMA(Direct Memory Access)传输,结合自主研发的虚拟仪器软件开发平台LabScene应用于虚拟仪器本科实验教学中,亦可作为标准通用高速数据采集卡使用.【总页数】5页(P167-171)【作者】吴忠杰;林君;谢宣松【作者单位】吉林大学,智能仪器与测控技术研究所,长春,130026;吉林大学,智能仪器与测控技术研究所,长春,130026;吉林大学,智能仪器与测控技术研究所,长春,130026【正文语种】中文【中图分类】TP274.2【相关文献】1.基于PCI总线的高速数据采集系统设计 [J], 张旭;陈昆明;李蕊;郑华耀2.基于PCI总线流水式高速数据采集系统设计 [J], 米根锁;王瑞峰3.基于PCI总线的高速数据采集系统的设计与实现 [J], 李国辉;杨宏;刘立新4.基于PCI-E总线的高速光纤数据采集系统设计 [J], 王慧英;曹志锋5.基于PCIe总线的高速数据采集系统设计与实现 [J], 尤焜因版权原因,仅展示原文概要,查看原文内容请购买。

基于PCI9054的数据采集卡

周育辉;蒋萍萍;吴兴林

【期刊名称】《电子测量技术》

【年(卷),期】2007(30)4

【摘要】为了解决数据采集系统中的大容量数据传输问题,本文介绍了一种基于PCI总线的数据采集卡的实现方案,详细分析了构成该系统数据采集卡的硬件结构以及主要功能模块,阐述了采集系统的工作原理。

并在此基础上引出了一种基于PCI9054专用芯片开发基于PCI总线的高速数据采集卡的软硬件实现方案,介绍了该采集卡的驱动程序的开发方法。

最后给出了实验测试数据。

实验数据表明,本地采集速率可达到160Mb/s,实时响应速度有了显著提高,能够满足系统要求。

【总页数】3页(P120-121)

【关键词】PCI总线;PCI;9054;PLXMON

【作者】周育辉;蒋萍萍;吴兴林

【作者单位】江西生物科技职业学院机电工程系

【正文语种】中文

【中图分类】TP274

【相关文献】

1.基于PCI9054的PCI接口数据通信系统 [J], 李垌楠;季彬彬

2.基于PCI9054的数据通信接口卡设计 [J], 张丹红;张孝勇;刘文

3.基于PCI9054的CameraLink图像采集卡设计 [J], 王雪松

4.基于PCI9054的数据采集卡的设计与实现 [J], 王松涛

5.基于PCI9054从模式的数据采集卡设计与应用 [J], 安冬冬;刘文怡;郅银周因版权原因,仅展示原文概要,查看原文内容请购买。

基于PCI总线的高速数据采集接口的设计与实现

韩雪峰;黄焱;杨涛

【期刊名称】《微计算机信息》

【年(卷),期】2005(000)022

【摘要】PCI总线接口控制器的设计是基于PCI总线的应用设计的关键所在.本文在介绍PCI9054接口控制器的基础上,给出了一种通用的高速数据采集接口的设计,并提出了一种新的包括PCI9054单周期读、写和DMA读操作的VHDL状态机设计.经测试证明,该接口的数据采集速率能稳定的达到200Mbit/s.

【总页数】3页(P71-73)

【作者】韩雪峰;黄焱;杨涛

【作者单位】450002,郑州解放军信息工程大学信息工程学院;450002,郑州解放军信息工程大学信息工程学院;450002,郑州解放军信息工程大学信息工程学院

【正文语种】中文

【中图分类】TP336

【相关文献】

1.基于PCI/CPCI接口的1553B总线模块设计与实现 [J], 杨春英

2.基于PCI软"核"的PCI总线接口设计与实现 [J], 李萍;夏斐斐

3.基于PCI总线的雷达视频高速数据采集接口设计 [J], 符联军

4.基于PCI总线的高速数据采集接口的设计与实现 [J], 韩雪峰;黄焱;杨涛

5.基于PCIe总线的高速数据采集系统设计与实现 [J], 尤焜

因版权原因,仅展示原文概要,查看原文内容请购买。

基于PCI总线多通道数据采集系统的设计作者:李润秋贺占庄来源:《现代电子技术》2008年第01期摘要:基于PCI总线的高速数据采集系统是近年来数据采集及其传输技术的一个发展方向。

文中围绕PCI总线接口控制器PCI9054,给出系统硬件设计方案,并阐明各个模块的具体实现。

设计出的采集卡具有体积小、速度快、支持突发性大数据量传输和抗干扰性强等特点,主要应用在图像数据采集领域。

关键词:数据采集中图分类号:TP274 文献标识码:B文章编号:Design of a Multi-channel Data Acquisition System Based on PCI(No.771 InstituteofChinaAerospace TimesElectronics Corp.,Xi′an,710065,C hina)Abstract:In recent years,based on PCI bus high speed data collecting system is a developing direction of data gather and transmission technology.This paper encircle with PCI bus interface controller PCI9054,presents the hardware system design scheme,and respectively discusses the modules.The card which we designed have the characteristic of less capacity,high speed,back up the burst transmission of a great number of data,and have strong performance of anti jamming,the mostly application domain of this card is image manipulation.Keywords:data acquisition;PCI9054;CPLD;DSP1 引言基于PCI总线的多通道数据采集卡的工作流程是:计算机应用程序根据命令通过驱动程序启动模数转换,模拟信号通过信号调理后进入A/D芯片,模数转换后的数据存入FIFO(先进先出)存储器缓存,在数据存储器中存满一帧时,硬件向主机发中断,主机响应中断后通过PCI9054芯片用DMA方式读出存放在数据存储器中的采样数据,然后进行后续处理(如计算、存储)并将结果显示于屏幕。

9054简介:PCI9054的主要功能就是实现PCI总线和本地总线(一般为哈佛结构)之间的数据通信,一共有三种数据传输方式:主模式、从模式、DMA方式。

PCI9054芯片内部主要由两路数据FIFO通道、内部寄存器、EEPROM和控制电路构成。

两个通道分别为DMA0和DMA1,他们的功能基本相同,其中DMA0还可以传输命令指令。

PCI9054有三种工作模式:M,J,CM模式,直接为Motorola公司的MPC850和MPC860准备的非复用接口;C模式,地址,数据线不复用;J模式,地址数据线复用。

由于M模式使用范围比较小,J模式使用起来控制比较复杂,一般使用C模式。

PIN定义:所有模式AD[31:0](Address and Data)地址和时钟复用,首先是一个地址段,后面跟着一个或多个数据段,支持突发模式的读写;C/BE[3:0]#(Bus Command and Byte Enables)总线命令和数据使能复用管脚,在AD为地址线的时候作为总线命令,在AD为数据线的时候作为数据使能;DEVSEL#(Device Select)有效的时候表示当前设备被选中,作为输入端口;FRAME#(Cyclone Frame)由主设备驱动,用来表示当前设备已经开始接入,总线开始传输数据。

有效:传输数据。

无效:完成最后一个数据的传输;GNT#(Grant)用来表示当前接入的设备已经被接受;IDSL(Initialization Device Select)在配置寄存器读写的时候用做片选信号;INTA#(Interrupt A)PCI中断请求;IRDY#(Initiator Ready)说明当前数据有效,可以并要完成传输;LOCK#(Lock)提示有自动操作,需要消耗若干个时钟来完成操作;PAR(Parity)作为AD和C/BE两部分总线的基偶校验,在传输地址的时候PAR要在地址传输完毕后一个时钟周期保持稳定。

对于数据段,PAR要在IRDY#或者TRDY#有效以后一个时钟周期保持稳定。

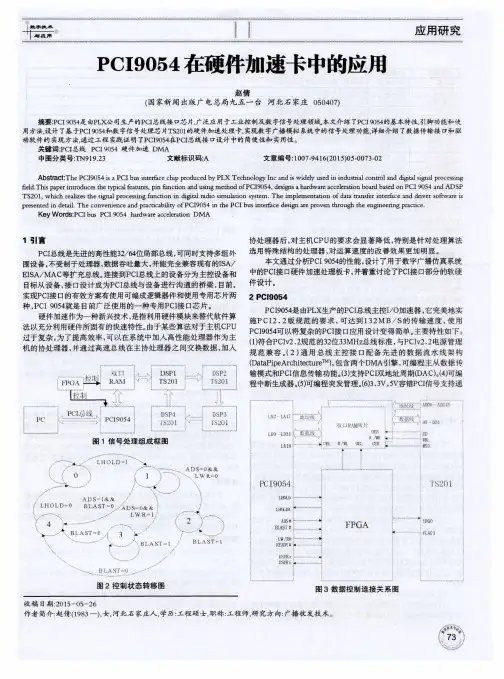

总线接口芯片PCI9054及其在高速数据采集系统中的应用装备指挥技术学院邵胜利侯孝民摘要:本文介绍了PCI总线接口芯片PCI9054的性能、总线操作及其DMA 数据传输方式,并且通过它在高速数据采集系统中的应用实例,阐述了PCI9054在PCI接口电路设计中的简便性和实用性。

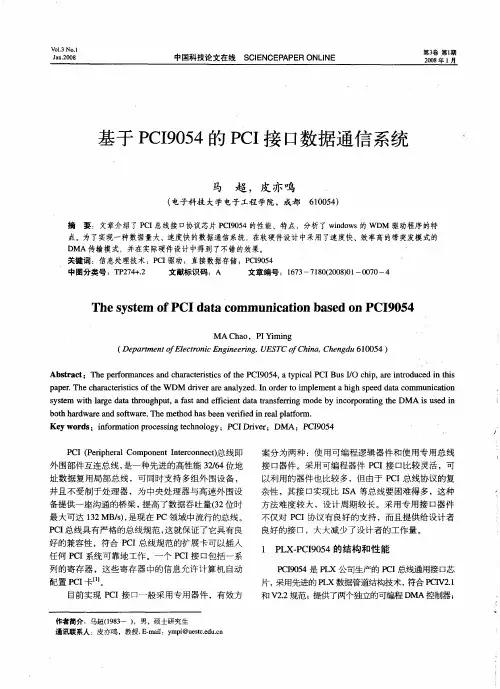

关键词:PCI总线接口PCI9054 DMA Windriver引言PCI(Peripheral Component Interconnect)总线即外围部件互连总线,是一种先进的高性能32/64位地址数据复用局部总线,可同时支持多组外围设备,并且不受制于处理器,为中央处理器与高速外围设备提供一座沟通的桥梁,提高了数据吞吐量(32位时最大可达132MB/s),是当今PC领域中流行的总线。

PCI总线具有严格的总线规范,这就保证了它具有良好的兼容性,符合PCI总线规范的扩展卡可以插入任何PCI系统可靠地工作。

一个PCI接口包括一系列的寄存器,这些寄存器中的信息允许计算机自动配置PCI卡。

目前实现PCI接口一般采用专用器件,有效方案分为两种:使用可编程逻辑器件和使用专用总线接口器件。

采用可编程逻辑器件实现PCI接口比较灵活,可以利用的器件也比较多,但由于PCI总线协议的复杂性,其接口的实现比ISA 等总线要困难得多,这种方法难度较大,设计周期较长。

采用专用接口器件不仅对PCI协议有良好的支持,而且提供给设计者良好的接口,这些都大大减少了设计者的工作量。

PCI9054的结构和性能PCI9054是美国PLX公司继PCI9052之后推出的又一低成本PCI总线接口芯片,低功耗,PQFP 172pins封装,它采用了先进的PLX数据管道结构技术,可以使局部总线快速转换到PCI总线上。

PCI9054主要特性PCI9054的主要特性如下:* 符合PCI V2.1,V2.2 规范,包含PCI电源管理特性。

* 支持VPD(Vital Product Data)的PCI扩展。

* 支持PCI双地址周期,地址空间高达4GB。

* 具备I2O准备报文单元,完全兼容I2O V1.5 规范。

* 提供了两个独立的可编程DMA控制器,每个通道均支持块和Scatter/Gather 的DMA方式,DMA通道0支持请求DMA方式。

* 在PCI启动模式,PCI 9054可插入类型1和类型2的配置周期。

* 在PCI和Local Bus的数据传送速率高达132MB/S。

* 支持本地总线(Local Bus)直接接口Motorola MPC850或MPC860系列,Intel i960系列,IBM PPC401系列及其它类似总线协议设备。

* 本地总线速率高达50MHz;支持复用/非复用的32位地址/数据;本地总线可为三种模式:M模式、C模式和J模式,可利用模式选择引脚加以选择。

* 具有可选的串行EEPROM接口。

* 本地总线时钟由外部提供,该时钟可和PCI时钟异步。

* 具有8个32位 Mailbox 寄存器和2个32位Doorbell寄存器。

PCI9054的内部结构组成PCI 9054内部有6种可编程的FIFO,以实现零等待突发传输及本地总线和PCI总线之间的异步操作。

PCI9054还提供了一个串行EEPROM配置接口,容量2K字节。

在配置存储器中存放了厂家标示、设备标示以及本地总线的基地址空间、I/O空间、中断控制信号等信息。

当初始化时,系统自动将串行EEPROM中的配置参数装入PCI配置寄存器,并根据本地总线对内存、I/O端口和中断的需求统一划分,自动配置。

PCI9054的总线操作.PCI9054的总线操作包括PCI总线操作和本地总线操作。

对于PCI总线操作,它完全遵守2.2版本PCI规范。

下面主要讨论一下本地总线操作。

PCI9054本地总线支持非多路复用32位地址/数据总线,多路复用32位和8位,16位或32位本地总线设备从属访问,运行速率高达50MHz,可以获得200MB/S的本地总线突发传输速率。

PCI9054有3种工作方式,分别为C、M和J模式。

M模式主要是针对Motorola 公司高性能MPC850/860的应用而设计的,主要应用在电信领域,J模式的接口设计相对比较麻烦,比较常用的是C模式。

C模式下PCI9054分为PCI Initiator操作和PCI Target操作。

在PIC Initiator操作过程中,本地处理器或本地总线主控设备能够直接通过PCI9054访问PCI总线,发起Local-to-PCI的数据传输。

而在PCI Target操作过程中,PCI总线主控设备可以以可编程的等待状态、总线宽度和突发传输功能访问PCI9054的三个本地空间(空间0,空间1和扩充ROM空间)。

PCI9054的DMA突发模式PCI9054集成了两个互相独立的DMA通道,每个通道都支持Block DMA和Scatter/Gather DMA,通道0还支持Demand DMA传输方式。

Block DMA要求PCI主机或Local主机提供PCI和Local的起始地址、传输字节数、传输方向。

主机设定DMA开始位启动数据传输,一旦传输完成,PCI9054设定DMA"传输结束位"结束DMA,如果中断允许位被使能,在传输结束时PCI9054将向主机申请中断。

在DMA传输中,PCI9054既是PCI总线的主控器又是Local 总线的主控器。

Scatter/Gather DMA要求主机在PCI空间或Local空间设定Descriptor模块,模块包括PCI和Local的起始地址、传输字节数、传输方向和下一个Descriptor模块的地址。

PCI9054载入第一个Descriptor模块并发起传输,连续加载下一个模块,直到它侦测到"链结束位"有效,PCI 9054设置"传输结束位",或者申请PCI或Local中断。

这种模式下,PCI9054也可以在每个模块加载时有效中断信号结束DMA传输。

若Descriptor模块在本地存储空间,可以编程使DMA控制器在每次DMA传输结束后清除传输字节数。

PCI9054的设计与应用PCI9054作为一种通用的PCI接口芯片,以其显著的功能和特性,得到了广泛的应用,下面就其在高速数据采集系统设计中的应用进行简单介绍。

硬件结构组成该高速数据采集系统利用PCI9054的PCI专用接口芯片的特性,设计了一个双路200M的高速数据采集卡,完成高速数据的采集和传输。

系统结构主要包括A/D转换、数据存储、逻辑控制,时钟分配和数据传输五大模块。

A/D转换电路采用AD(Analog Device)公司的AD9054芯片,分辨率为8位,最高采样率200MSPS。

数据存储电路采用IDT公司的产品72V36110,该芯片可以工作在133 MHz的频率下,零延迟传输,可以提供9位、18位、36位输入、输出接口,最大存储容量为128K 36Bit。

逻辑控制电路采用CPLD技术,利用Altera公司的可编程逻辑器件EPM7128S完成对数据存储电路、AD采集电路、PCI 桥电路的控制,对时钟电路的配置,以及各种触发控制。

时钟电路产生的采样脉冲的频率范围是25MHz~400MHz,步长为1MHz,采用SYNERGY公司的频率合成器SY89429V来完成。

第一步:模拟信号经过信号调理电路后送入ADC,ADC在逻辑控制电路和时钟控制电路的作用下,完成A/D转换,并将转换结果送入数据存储电路。

第二步:PCI桥电路在主机的控制下,将数据存储电路中的数据传输到微机内存中,以供应用程序进行后续的信号处理。

软件设计PCI数据传输卡的另一关键问题即驱动程序的开发。

设备驱动程序提供连接到PCI板卡的软件接口,在Windows 9x和Windows NT中,设备驱动程序必须根据Windows驱动程序模型(WDM)设计。

设备驱动程序的关键是如何完成硬件操作,基本功能是完成设备的初始化、对端口的读写操作、中断的设置和响应及中断的调用、以及对内存的直接读写。

该系统选用Windriver来编写设备驱动程序,Windriver是美国KRF-Tech 公司出品的用于编写驱动程序的另一种工具包。

它以通用设备驱动程序Windrvr.vxd和Windrvr.sys为核心,包含一个类似QuickVxD的代码生成器Windriver Wizard,一个Windriver发行包,两个公用程序pci_scan.exe和pci_dump.exe。

用它编写的程序主要针对ISA/PCI设备,可同时工作在Windows 9x/NT两种操作系统,其中Windrvr.vxd用于Windows 9x操作系统,Windrvr.sys 用于Windows NT操作系统,因此,它是设计PCI设备驱动程序的理想工具。

Windriver 针对PLX和AMCC的专用接口芯片特别编写了API函数包,这些函数能够方便地实现中断处理、DMA传输、I/O操作、内存映射以及即插即用等功能,为系统的驱动程序的编写提供了便利。

结论PCI 9054 以其强大的功能和简单的用户接口,为PCI总线接口的开发提供了一种简洁的方法,设计者只需设计出本地总线接口控制电路,即可实现与PCI 总线的高速数据传输。

本系统经过测试,高速数据能够正确采集和传输。

在高速数据传输系统中,利用PCI总线的高速特性实时传输和存储采集数据,有效解决了数据的传输和处理的实时性,可应用于高速数据采集卡、视频处理卡、网卡等高速设备中,随着PCI总线的普及应用,基于 PCI总线的传输系统设计有十分广阔的前景。