电子教案《数字电子技术(第5版_杨志忠)》教学资源第4章_组合逻辑电路

- 格式:doc

- 大小:5.28 MB

- 文档页数:26

第四章组合逻辑电路1. 解: (a)(b)是相同的电路,均为同或电路。

2. 解:分析结果表明图(a)、(b)是相同的电路,均为同或电路。

同或电路的功能:输入相同输出为“1”;输入相异输出为“0”。

因此,输出为“0”(低电平)时,输入状态为AB=01或103. 由真值表可看出,该电路是一位二进制数的全加电路,A为被加数,B为加数,C为低位向本位的进位,F1为本位向高位的进位,F2为本位的和位。

4. 解:函数关系如下:ABSF+⊕=++ABSSSABB将具体的S值代入,求得F 312值,填入表中。

A A FB A B A B A A F B A B A A F A A F AB AB F B B A AB F AB B A B A B A AB F B A A AB F B A B A B A F B A AB AB B A B A F B B A B A B A B A B A B A F AB BA A A B A A B A F F B A B A F B A B A F A A F S S S S =⊕==+==+⊕===+⊕===⊕===⊕===+⊕===+=+⊕===⊕==+==⊕==Θ=+=+⊕===+++=+⊕===+=⊕===⊕==+=+⊕==+=+⊕===⊕==01111111011010110001011101010011000001110110)(01010100101001110010100011000001235. (1)用异或门实现,电路图如图(a)所示。

(2) 用与或门实现,电路图如图(b)所示。

6. 解因为一天24小时,所以需要5个变量。

P变量表示上午或下午,P=0为上午,P=1为下午;ABCD表示时间数值。

真值表如表所示。

利用卡诺图化简如图(a)所示。

化简后的函数表达式为D C A P D B A P C B A P A P DC A PD B A P C B A P A P F =+++=用与非门实现的逻辑图如图(b)所示。

数字电子技术(第5版)第4章组合逻辑电路1.(261)要用n 位二进制数为N 个对象编码,必须满足()。

A. N = 2nB. N ≥ 2nC. N ≤ 2nD. N = n答案.C2.(268)串行加法器的进位信号采用()传递,并行加法器的进位信号采用()传递。

A. 超前,逐位B. 逐位,超前C.逐位,逐位D.超前,超前答案.B3.(258)组合逻辑电路()。

A. 可以用逻辑门构成B. 不可以用集成逻辑门构成C. 可以用集成逻辑门构成D. A与C均可答案.D4.(260)优先编码器的编码()。

A.是唯一的B.不是唯一的C. 有时唯一,有时不唯一D. A、B、C都不对答案.A5.(262)用输出低电平有效的三线—八线译码器(74LS138)和逻辑门实现某一逻辑函数()。

A. 一定用与非门B. 不一定用与非门C. 一定用非门D.一定用或门答案.B6.(263)要使三线—八线译码器74LS138能正常工作时,其使能端ST A,ST B,ST C的电平信号应是()。

A. 100B. 111C. 000D. 011答案.A7.(264)一个有n位地址码的数据选择器,它的数据输入端有()。

A. 2n 个B. 2n- 1个C. 2n – 1个D. n个答案.A8.(270)要消除竞争—冒险,下列说法中错误的是()。

A. 修改逻辑设计B.引入封锁脉冲C. 加滤波电容D. 以上都不对答案.D9.(266)四位比较器(74LS85)的三个输出信号A>B,A=B,A<B中,只有一个是有效信号时,它呈现()。

A. 高电平B. 低电平C. 高阻D.任意电平答案.A10.(269)已知CAB+A+,左式和右式的两个逻辑图分别是X和Y,产生+=AABBCC竞争—冒险的是()。

A. XB. YC. X和YD.都不是答案.B11.(267)采用四位比较器(74LS85)对两个四位数比较时,最后比较的是()。

A. 最高位B. 最低位C. 次高位D. 次低位答案.B12.(271)在下列逻辑电路中,不是组合逻辑电路的有()。

A. 译码器B. 编码器C.全加器D. 寄存器答案.D13.(265)要实现多输入、单输出逻辑函数,最好选用()。

A. 数据选择器B.数据分配器C. 译码器D. 编码器答案.A14.(259)组合逻辑电路()。

A. 有记忆功能B. 无记忆功能C. 有时有,有时没有D. 要根据电路确定答案.B15.(251)如果想实现并串转换可以选择数据分配器。

()答案.错误16.(252)没有专门的数据分配器,一般是用译码器来实现数据分配的答案.正确17.(253)半加器与全加器的主要区别是是否考虑来自低位的进位。

()答案.正确18.(254)四个全加器可以组成一个串行进位的四位数加法器。

()答案.正确19.(255)一个四位数比较器进行数值比较时,只有四位数全部比较完才能产生比较结果。

()答案.错误20.(257)竞争冒险现象是可以消除的。

()答案.正确21.(249)只用两片4选1数据选择器可以构成一个8选1数据选择器。

( )答案.正确22.(248)四线—十线译码器的地址输入代码一定有六组伪码。

( )答案.正确23.(239)分析组合逻辑电路一般要列出真值表。

( )答案.正确24.(256)只要是组合逻辑电路就可能存在竞争。

()答案.正确25.(241)表示逻辑函数的逻辑表达式与真值表是等价的。

( )答案.正确26.(250)一片8选1数据选择器可以实现二输入逻辑函数。

( )答案.正确27.(240)设计组合逻辑电路时,一般要化简。

( )答案.正确28.(242)两个逻辑电路的逻辑函数表达式不一样,这两个电路的逻辑功能就不一样。

( )答案.错误29.(243)四线—十线优先编码器的输入请求必须是低电平有效。

( )答案.错误30.(244)非优先编码器的输入请求编码的信号之间是互相排斥的。

()答案.正确31.(245)优先编码器的输入请求编码的信号级别一般是下标号大的优先级别高。

()答案.正确32.(246)译码是编码的逆过程,编码是唯一的,译码也一定是唯一的。

( )答案.正确33.(247)七段显示译码器数据输入是自然二进制数。

( )答案.错误34.(305)在优先编码器中,是优先级别()的编码信号排斥优先级别()的。

答案.高低35.(310) 2n选1数据选择器,它有( )位地址码,有( )个输出端。

答案. n 136.(315)串行进位加法器的缺点是(),要想速度较高时应采用()加法器。

答案.速度较慢超前进位37.(314)一个多位的串行进位加法器,最低位的进位输入端应()。

答案.接地38.(313)只考虑两个一位二进制数的相加而不考虑来自低位进位数的运算电路称为()。

答案.半加器39.(312)四路数据分配器有()个数据输入端, ()个地址端, ()个输出端。

答案. 1 2 440.(311)要把并行数据转换成串行数据,应选用( )。

答案.数据选择器41.(316)由于信号的()不同而产生干扰脉冲(毛刺)的现象称为()。

答案.延时竞争-冒险42.(309)驱动共阳极七段数码管的译码器的输出电平为()有效,驱动共阴极七段数码管的译码器的输出电平为()有效。

答案.低电平高电平43.(308)驱动七段数码管的译码器CC14547有()个数据输出端。

答案.七44.(307)一个三线—八线译码器,它的译码输入端有()个,输出端信号有()个。

答案. 3 845.(306)编码器按进制分一般有()()。

答案.二进制编码器二—十进制编码器46.(304)十线—四线编码器常用的输出代码为()码。

答案. 8421BCD47.(303)描述组合逻辑电路逻辑功能的方法有()、()、()、()、()。

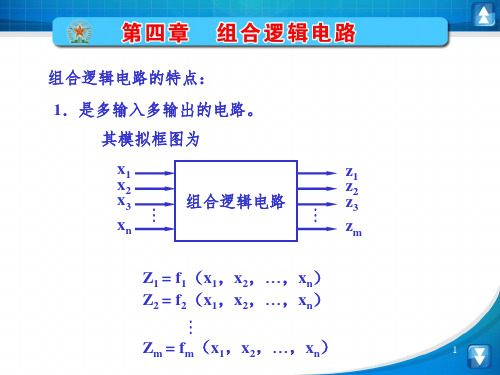

答案.逻辑表达式真值表卡诺图逻辑图波形图48.(302)数字电路中,任意时刻的输出信号只与该时刻的输入有关,而与该信号作用之前的原来状态无关的电路是()。

答案.组合逻辑电路49.(317)消除竞争冒险现象的方法通常有()、()、()、()。

答案. 加封锁脉冲 加选通脉冲 修改逻辑设计 接入滤波电容50.(279) 在一个射击游戏中,射手可打三枪,一枪打鸟,一枪打鸡,一枪打兔子,规则是命中不少于两枪者获奖。

试用与非门设计一个判别得奖电路。

答案. (1)设鸟、鸡、兔分别用变量A 、B 、C 表示,1表示命中,0表示没有命中;用Y表示结果,1表示得奖,0表示不得奖。

(2)列真值表:(3)卡诺图化简并写出最简表达式:A BC 01000111101111得:BC AC AB BC AC AB Y =++= (4)与非门设计的逻辑电路如下图:BAC51.(287) 试用74LS138和逻辑门设计一个组合电路,该电路输入X 和输出Y 均为三位二进制数。

二者之间的关系为:2≤X ≤5时,Y=X+2 X <2时, Y=1 X >5时, Y=0答案. (1)由题得出X 、Y 的关系表:X 2 X 1 X 0 Y 2 Y 1 Y 0 0 0 0 0 0 1 0 0 1 0 0 1 0 1 0 1 0 0 0 1 1 1 0 1 1 0 0 1 1 0 1 0 1 1 1 1 1 1 0 0 0 0 1 1 10 0 0由表得:2 Y ABC ABC AB C ABC =+++1 Y AB C ABC =+0 Y A B C A BC ABC ABC =+++(2) 置A ST =1,0==C B ST ST 。

与74LS138输出表达式进行比较,令X 2=A 2,X 1=A 1,X 0=A 0得:54322 Y Y Y Y Y =, 541 Y Y Y =, 53100 Y Y Y Y Y = (3)作逻辑图如下:52.(301) 只知道某一电路为组合电路,但不知道其电路结构,如何确定其逻辑功能? 答案. 通过实验测量的方法来确定电路的逻辑功能。

具体方法如下:把所有的输入端口接逻辑开关,按自然二进制数组合,依次输入逻辑高低电平,记录对应的输出逻辑电平,再列出真值表,根据真值表分析其逻辑功能。

53.(300) 已知BC D C D B A Y ++=,问是否存在竞争冒险现象,并说明原因。

答案. 不存在竞争冒险现象。

因为无论A 、B 、C 、D 取值如何组合,都不会出现他们的互非量。

54.(299) 已知D A C A B C A Y +++=,问是否存在竞争冒险现象,若有,指出冒险情况。

答案. 存在竞争冒险现象。

当C=1,B=0,D=0的时候,A A Y +=,出现竞争冒险现象。

当A=0,B=1的时候,Y C C =+,出现竞争冒险现象。

55.(298) 试用一个74LS138译码器和适当的门电路实现一位全减器。

答案. (1)在全减器中,A i 表示本位的被减数,B i 表示本位的减数,V i-1 表示低位的借位,D i 表示本位的差,V i 表示向高位的借位。

得真值表:由真值表得输出表达式:∑∑==)7,3,2,1( ),7,4,2,1(m Vi m Di(2)取ST A =1,0==C B ST ST 时,74LS138工作,与74LS138输出表达式进行比较(输出低电平有效),令2110,,i i i A A B A V A -=== 得:7421 Y Y Y Y D i =, 7321Y Y Y Y V i = (3)画逻辑图如下:56.(297) 利用74LS138译码器和门电路实现一位全加器电路。

答案. (1)在全加器中,A i 表示本位的被加数,B i 表示本位的加数,C i-1 表示低位的进位,S i 表示本位的和,C i 表示向高位的进位,得真值表:A iB iC i-1 S i C i 0 0 0 0 0 0 0 1 1 0 0 1 0 1 0 0 1 1 0 1 1 0 0 1 0 1 0 1 0 1 1 1 0 0 1 1 1 11 1由真值表得输出表达式:(1,2,4,7), (3,5,6,7)i i S m C m ==∑∑。

(2)取ST A =1,0==C B ST ST 时,74LS128工作,与74LS138输出表达式进行比较,令2A A i =, 1A B i =, 01A C i =-得:7421 Y Y Y Y S i =, 7653 Y Y Y Y C i = (输出低电平有效) (3)画逻辑图如下:57.(296) 试用两个半加器和一个或门设计一个全加器。

(1)写出半加输出表达式; (2)写出全加输出表达式; (3)画出逻辑图。

A iB iC iS i答案. (1)半加表达式:, i i i i i i S A B C A B =⊕=(2)全加表达式:1-⊕⊕=i i i i C B A S , ()i i i i i i B A C B A C +⊕=-1 (3)画逻辑图如下:58.(295) 已知74LS151的A 2脚断了,但内部结构完整,试用该芯片实现逻辑函数Y=C B A ⊕⊕。