数字电子技术基础 第四章.

- 格式:ppt

- 大小:3.67 MB

- 文档页数:50

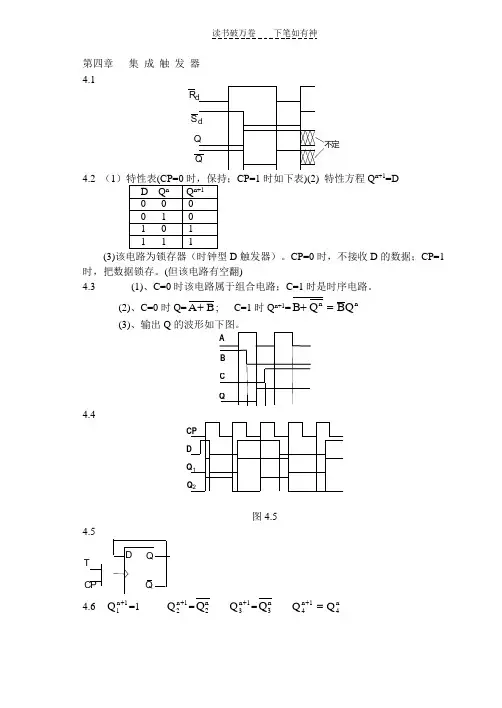

第四章 集 成 触 发 器 4.1R d S d Q Q不定4.2 (1CP=1时如下表)(2) 特性方程Q n+1=D(3)该电路为锁存器(时钟型D 触发器)。

CP=0时,不接收D 的数据;CP=1时,把数据锁存。

(但该电路有空翻)4.3 (1)、C=0时该电路属于组合电路;C=1时是时序电路。

(2)、C=0时Q=A B +; C=1时Q n+1=B Q BQ nn+= (3)、输出Q 的波形如下图。

A B C Q4.4CP D Q 1Q 2图4.54.5 DQ QCPT4.6 Q 1n 1+=1 Q 2n 1+=Q 2n Q n 13+=Q n 3 Q Q 4n 14n+=Q1CP Q2Q3Q44.7 1、CP 作用下的输出Q 1 Q 2和Z 的波形如下图; 2、Z 对CP 三分频。

DQ QCPQ1DQ QQ2ZRd CP Q1Q2Z14.8由Q D J Q KQ J Q KQ n 1n n n n +==+=⋅得D 触发器转换为J-K 触发器的逻辑图如下面的左图;而将J-K 触发器转换为D 触发器的逻辑图如下面的右图CPD Q QJKQ QDQ QJ KCP4.9CP B CA4.10CP X Q1Q2Z4.11 1、555定时器构成多谐振荡器 2、u c, u o 1, u o 2的波形u c u o 1u o 2t t t 1.67V3.33V3、u o 1的频率f 1=1074501316..H z ⨯⨯≈ u o 2的频率f 2=158H z4、如果在555定时器的第5脚接入4V 的电压源,则u o 1的频率变为1113001071501232....H z ⨯⨯+⨯⨯≈4.12 图(a)是由555定时器构成的单稳态触发电路。

1、工作原理(略);2、暂稳态维持时间t w =1.1RC=10ms(C 改为1μF);3、u c 和u o 的波形如下图:u ou ct t tu i (ms)(ms)(ms)5 10 25 30 45 503.33V4、若u i 的低电平维持时间为15m s ,要求暂稳态维持时间t w 不变,可加入微分电路4.13由555定时器构成的施密特触发器如图(a)所示 1、电路的电压传输特性曲线如左下图; 2、u o 的波形如右下图;3、为使电路能识别出u i 中的第二个尖峰,应降低555定时器5脚的电压至3V 左右。

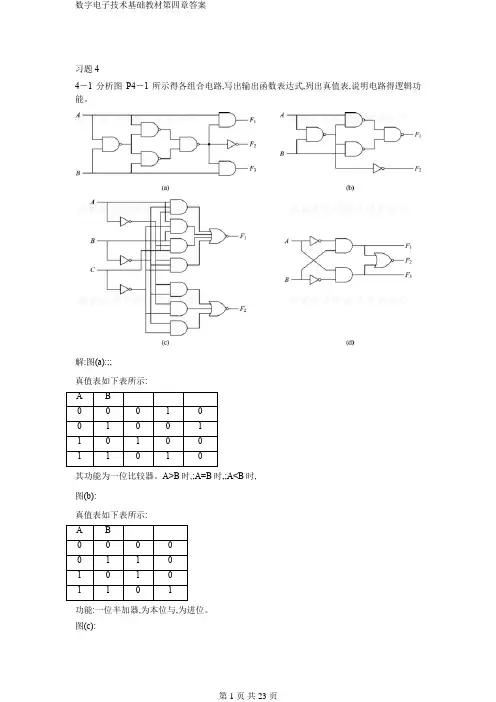

习题44-1 分析图P4-1所示得各组合电路,写出输出函数表达式,列出真值表,说明电路得逻辑功能。

解:图(a):;;真值表如下表所示:其功能为一位比较器。

A>B时,;A=B时,;A<B时,图(b):真值表如下表所示:功能:一位半加器,为本位与,为进位。

图(c):真值表如下表所示:功能:一位全加器,为本位与,为本位向高位得进位。

图(d):;;功能:为一位比较器,A<B时,=1;A=B时,=1;A>B时,=14-2 分析图P4-2所示得组合电路,写出输出函数表达式,列出真值表,指出该电路完成得逻辑功能。

解:该电路得输出逻辑函数表达式为:因此该电路就是一个四选一数据选择器,其真值表如下表所示:,当M=1时,完成4为二进制码至格雷码得转换;当M=0时,完成4为格雷码至二进制得转换。

试分别写出,,,得逻辑函数得表达式,并列出真值表,说明该电路得工作原理。

解:该电路得输入为,输出为。

真值表如下:由此可得:完成二进制至格雷码得转换。

完成格雷码至二进制得转换。

4-4 图P4-4就是一个多功能逻辑运算电路,图中,,,为控制输入端。

试列表说明电路在,,,得各种取值组合下F与A,B得逻辑关系。

解:,功能如下表所示,两个变量有四个最小项,最多可构造种不同得组合,因此该电路就是一个能产生十六种函数得多功能逻辑运算器电路。

4-5 已知某组合电路得输出波形如图P4-5所示,试用最少得或非门实现之。

解:电路图如下:4-6 用逻辑门设计一个受光,声与触摸控制得电灯开关逻辑电路,分别用A,B,C表示光,声与触摸信号,用F表示电灯。

灯亮得条件就是:无论有无光,声信号,只要有人触摸开关,灯就亮;当无人触摸开关时,只有当无关,有声音时灯才亮。

试列出真值表,写出输出函数表达式,并画出最简逻辑电路图。

解:根据题意,列出真值表如下:由真值表可以作出卡诺图,如下图:C AB 00 10 11 100 1由卡诺图得到它得逻辑表达式为: 由此得到逻辑电路为:4-7 用逻辑门设计一个多输出逻辑电路,输入为8421BCD 码,输出为3个检测信号。

第四章组合逻辑电路一、本章知识点(一)概念1.组合电路:电路在任一时刻输出仅取决于该时刻的输入,而与电路原来的状态无关。

电路结构特点:只有门电路,不含存储(记忆)单元。

2.编码器的逻辑功能:把输入的每一个高、低电平信号编成一个对应的二进制代码。

优先编码器:几个输入信号同时出现时,只对其中优先权最高的一个进行编码。

3.译码器的逻辑功能:输入二进制代码,输出高、低电平信号。

显示译码器:半导体数码管(LED数码管)、液晶显示器(LCD)4.数据选择器:从一组输入数据中选出某一个输出的电路,也称为多路开关。

5.加法器半加器:不考虑来自低位的进位的两个1位二进制数相加的电路。

全加器:带低位进位的两个 1 位二进制数相加的电路。

超前进位加法器与串行进位加法器相比虽然电路比较复杂,但其速度快。

6.数值比较器:比较两个数字大小的各种逻辑电路。

7.组合逻辑电路中的竞争一冒险现象竞争:门电路两个输入信号同时向相反跳变(一个从1变0,另一个从0变1)的现象。

竞争-冒险:由于竞争而在电路输出端可能产生尖峰脉冲的现象。

消除竞争一冒险现象的方法:接入滤波电容、引入选通脉冲、修改逻辑设计(二)组合逻辑电路的分析方法分析步骤:1.由图写出逻辑函数式,并作适当化简;注意:写逻辑函数式时从输入到输出逐级写出。

2.由函数式列出真值表;3.根据真值表说明电路功能。

(三)组合逻辑电路的设计方法设计步骤:1.逻辑抽象:设计要求----文字描述的具有一定因果关系的事件。

逻辑要求---真值表(1) 设定变量--根据因果关系确定输入、输出变量;(2)状态赋值:定义逻辑状态的含意输入、输出变量的两种不同状态分别用0、1代表。

(3)列出真值表2.由真值表写出逻辑函数式真值表→函数式,有时可省略。

3.选定器件的类型可选用小规模门电路,中规模常用组合逻辑器件或可编程逻辑器件。

4.函数化简或变换式(1)用门电路进行设计:从真值表----卡诺图/公式法化简。