第三章_组合逻辑电路

- 格式:ppt

- 大小:6.71 MB

- 文档页数:146

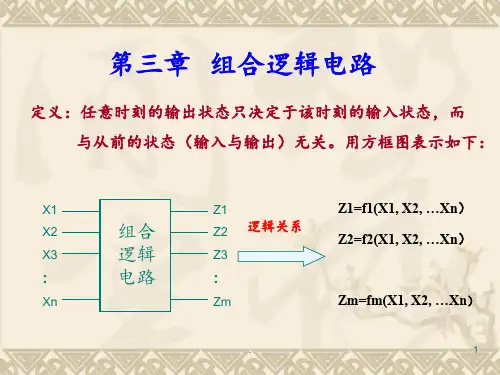

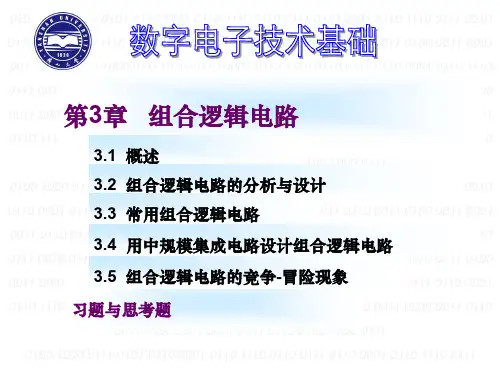

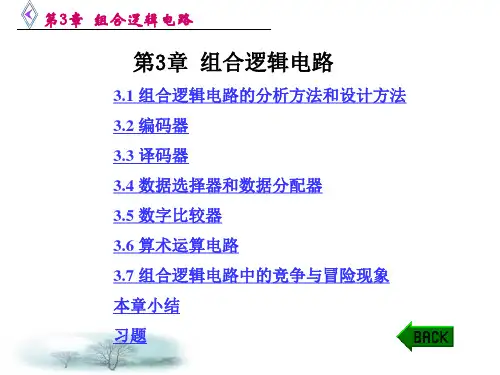

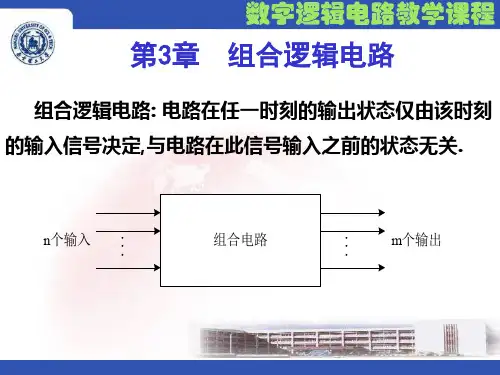

第三章组合逻辑电路•3.1概述•3.2组合逻辑电路的分析方法和设计方法•3.3若干常用的组合逻辑电路•3.4组合逻辑电路中的竞争-冒险现象返回3.1 概述•图3.1.1组合逻辑电路举例•图3.1.2组合逻辑电路的框图返回图3.1.1 组合逻辑电路举例返回图3.1.2 组合逻辑电路的框图返回3.2 组合逻辑电路的分析方法和设计方法•图3.2.1 例3.2.1的电路•图3.2.2 组合逻辑电路的设计过程•图3.2.3 交通信号灯的正常工作状态与故障状态•图3.2.4 例3.2.2的逻辑图之一•图3.2.5 例3.2.2的逻辑图之二•图3.2.6 例3.2.2的卡诺图•图3.2.7 例3.2.2的逻辑图之三返回图3.2.1 例3.2.1的电路返回图3.2.2 组合逻辑电路的设计过程返回返回图3.2.3 交通信号灯的正常工作状态与故障状态返回返回返回图3.2.6 例3.2.2的卡诺图返回图3.2.7 例3.2.2的逻辑图之三返回3.3 若干常用的组合逻辑电路(一)•图3.3.1 3位二进制(8线-3线)编码器的框图•图3.3.2 3位二进制编码器•图3.3.3 8线-3线优先编码器74LS148的逻辑图•图3.3.4 用两片74LS148接成的16线-4线优先编码器•图3.3.5 二-十进制优先编码器74LS147的逻辑图•图3.3.6 3位二进制(3线-8线)译码器的框图•图3.3.7 用二极管与门阵列组成的3线-8线译码器•图3.3.8 用与非门组成的3线-8线译码器74LS138•图3.3.9 用两片74LS138接成的4线-16线译码器•图3.3.10 二-十进制译码器74LS42•图3.3.11 半导体数码管BS201A(a)外形图(b)等效电路下页返回3.3 若干常用的组合逻辑电路(二)•图3.3.12 液晶显示器的结构及符号•(a )未加电场时(b )加电场以后(c )符号•图3.3.13 用异或门驱动液晶显示器•(a )电路(b )电压波形•图3.3.14 BCD -七段显示译码器的卡诺图•图3.3.15 BCD -七段显示译码器7448的逻辑图•图3.3.16 7448的输入、输出电路•(a )端(b )输入端(c )输出端•图3.3.17 用7448驱动BS201的连接方法•图3.3.18 有灭零控制的8位数码显示系统•图3.3.19 例3.3.3的电路•图3.3.20 双4选1数据选择器74LS153•图3.3.21 采用CMOS 传输门结构的数据选择器CC14539•图3.3.22 用两个4选1数据选择器接成的8选1数据选择器返回下页上页RBO BI /3.3 若干常用的组合逻辑电路(三)•图3.3.23 例3.3.5的电路•图3.3.24 例3.3.6的电路•图3.3.25 半加器(a)逻辑图(b)符号•图3.3.26 全加器的卡诺图•图3.3.27 双全加器74LS183 (a)1/2逻辑图(b)图形符号•图3.3.28 4位串行进位加法器•图3.3.29 4位超前进位加法器74LS283 的逻辑图•图3.3. 30 例3.3.7的代码转换电路•图3.3. 31 1位数值比较器•图3.3. 32 4位数值比较器CC14585的逻辑图•图3.3. 33 将两片CC14585 接成8位数值比较器上页返回图3.3.1 3位二进制(8线-3线)编码器的框图返回图3.3.2 3位二进制编码器返回图3.3.3 8线-3线优先编码器74LS148的逻辑图返回图3.3.4 用两片74LS148接成的16线-4线优先编码器返回图3.3.5 二-十进制优先编码器74LS147的逻辑图返回返回返回图3.3.8 用与非门组成的3线-8线译码器74LS138返回图3.3.9 用两片74LS138接成的4线-16线译码器返回图3.3.10 二-十进制译码器74LS42返回图3.3.11 半导体数码管BS201A(a)外形图(b)等效电路返回图3.3.12液晶显示器的结构及符号(a)未加电场时(b)加电场以后(c)符号返回图3.3.13 用异或门驱动液晶显示器(a)电路(b)电压波形返回图3.3.14 BCD-七段显示译码器的卡诺图返回图3.3.15 BCD-七段显示译码器7448的逻辑图返回图3.3.16 7448的输入、输出电路(a )端(b )输入端(c)输出端返回RBO BI /图3.3.17 用7448驱动BS201的连接方法返回图3.3.18 有灭零控制的8位数码显示系统返回图3.3.19 例3.3.3的电路返回图3.3.20 双4选1数据选择器74LS153返回图3.3.21 采用CMOS传输门结构的数据选择器CC14539返回图3.3.22 用两个4选1数据选择器接成的8选1数据选择器返回图3.3.23 例3.3.5的电路返回图3.3.24 例3.3.6的电路返回图3.3.25 半加器(a)逻辑图(b)符号返回图3.3.26 全加器的卡诺图返回图3.3.27 双全加器74LS183(a)1/2逻辑图(b)图形符号返回图3.3.28 4位串行进位加法器返回图3.3.29 4位超前进位加法器74LS283 的逻辑图返回图3.3.30 例3.3.7的代码转换电路返回图3.3.31 1位数值比较器返回图3.3.32 4位数值比较器CC14585的逻辑图返回图3.3.33 将两片CC14585 接成8位数值比较器返回3.4 组合逻辑电路中的竞争-冒险现象•图3.4.1 由于竞争而产生的尖峰脉冲•图3.4.2 2线-4线译码器中的竞争-冒险现象(a)电路图(b)电压波形图•图3.4.3 同一输入变量经不同途径到达输出门的情况(m、n均为正整数)•图3.4.4 例3.4.1 的电路•图3.4.5 消除竞争-冒险现象的几种方法(a)电路接法(b)电压波形•图3.4.6 用增加冗余项消除竞争-冒险返回图3.4.1 由于竞争而产生的尖峰脉冲返回。