基于FPGA的音乐灯光系统

- 格式:pdf

- 大小:1.39 MB

- 文档页数:2

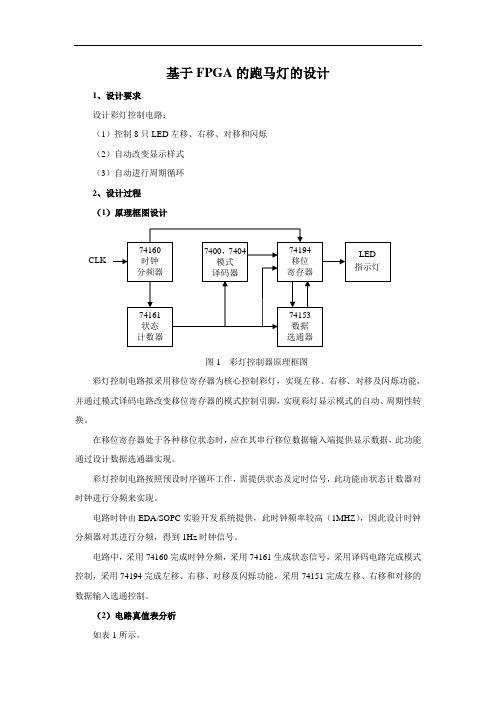

基于FPGA的跑马灯的设计1、设计要求设计彩灯控制电路:(1)控制8只LED左移、右移、对移和闪烁(2)自动改变显示样式(3)自动进行周期循环2、设计过程(1)原理框图设计图1 彩灯控制器原理框图彩灯控制电路拟采用移位寄存器为核心控制彩灯,实现左移、右移、对移及闪烁功能,并通过模式译码电路改变移位寄存器的模式控制引脚,实现彩灯显示模式的自动、周期性转换。

在移位寄存器处于各种移位状态时,应在其串行移位数据输入端提供显示数据,此功能通过设计数据选通器实现。

彩灯控制电路按照预设时序循环工作,需提供状态及定时信号,此功能由状态计数器对时钟进行分频来实现。

电路时钟由EDA/SOPC实验开发系统提供,此时钟频率较高(1MHZ),因此设计时钟分频器对其进行分频,得到1Hz时钟信号。

电路中,采用74160完成时钟分频,采用74161生成状态信号,采用译码电路完成模式控制,采用74194完成左移、右移、对移及闪烁功能,采用74151完成左移、右移和对移的数据输入选通控制。

(2)电路真值表分析如表1所示。

表1 电路真值表其中:QC1和QC0为状态计数器输出的控制信号;CLK/8为对时钟进行8分频的状态计数器输出信号,CLK/32为对时钟进行32分频的状态计数器输出信号;LED4为左侧74LS194的高位输出信号,LED5为右侧74LS194的低位输出信号;为简化设计,彩灯控制器的状态计数器输出(右移、左移、闪烁)与数据选通器控制端、移位寄存器工作模式(右移、左移、置数)的控制端采用相同逻辑值编码,状态计数器的对移输出与剩余的逻辑值编码(00)相同。

(3)时钟分频器设计107分频(4)状态计数器设计采用二进制计数器74LS161设计,提供时钟的2分频作为闪烁模式的数据信号,8分频作为移位的数据信号,32分频和64分频作为移位数据信号和模式控制信号。

(5)模式译码器设计根据真值表1,经逻辑化简可得:AS=11QCAS⋅QC=+QC=1QC10QCBS⋅QC==QC+QC111QCBS=0QC(6)数据选通器设计(7)移位寄存器设计使用了两片74LS194的左移、右移和置数模式分别实现了LED灯的左移、右移、对移和闪烁。

一种基于FPGA的LED室内照明系统设计与实现柴万东;张立萍【期刊名称】《内蒙古民族大学学报(自然科学版)》【年(卷),期】2016(031)002【摘要】针对LED光源在室内照明中的应用,设计了一种LED室内照明控制系统,该系统包括室内控制盒和模组控制器两部分.采用FPGA芯片Spartan-3E设计了室内控制盒硬件电路,并将模组控制器全部集成到XILINX公司的CoolRunner-II CPLD芯片中,用来接收DMX512协议上的调光数据,并将调光数据转化为PWM信号.LED驱动器接收PWM信号以便控制和调节LED光源亮度;利用SOPC开发工具EDK,搭建了基于32位嵌入式软核处理器的嵌入式系统,设计了室内控制盒的软件,最终实现了八种室内LED照明模式.%A set of indoor LED lighting control system for LED applications in indoor lighting is presented. The in-door LED lighting system include indoor control box and module controllers. A FPGA chip Spartan-3E is adapted to design the hardware circuit of indoor control box. The module controller is realized in a CoolRunner-II CPLD chip of Xilinx Company, which receives the brightness information from DMX512 protocol and output PWM signals. The LED driving chips receive PWM signals to control and adjust the LED lighting level. The SOPC Embedded Develop-ment Kit(EKD)is used to build the whole software system that is based on a 32-bit Microblaze soft processor. Final, 8 LED lighting patterns have been finished.【总页数】5页(P104-108)【作者】柴万东;张立萍【作者单位】赤峰学院物理与电子信息工程系,内蒙古赤峰 024000;赤峰学院物理与电子信息工程系,内蒙古赤峰 024000【正文语种】中文【中图分类】TM923【相关文献】1.基于Zigbee的室内LED智能照明系统 [J], 陈越2.基于物联网的LED室内照明系统设计趋势探讨 [J], 刘芳娇;王琦;胡海华3.基于物联网的LED室内照明系统设计趋势探讨 [J], 刘芳娇;王琦;胡海华4.基于WIFI的室内LED智能照明系统设计 [J], 周青山; 李建英; 郭晓华; 梁志鹏; 姜慧彬5.一种基于WiFi环境下的简易LED照明系统设计与实现 [J], 熊强强;李丽英;齐志艺;梁华;徐文磊;曾炜因版权原因,仅展示原文概要,查看原文内容请购买。

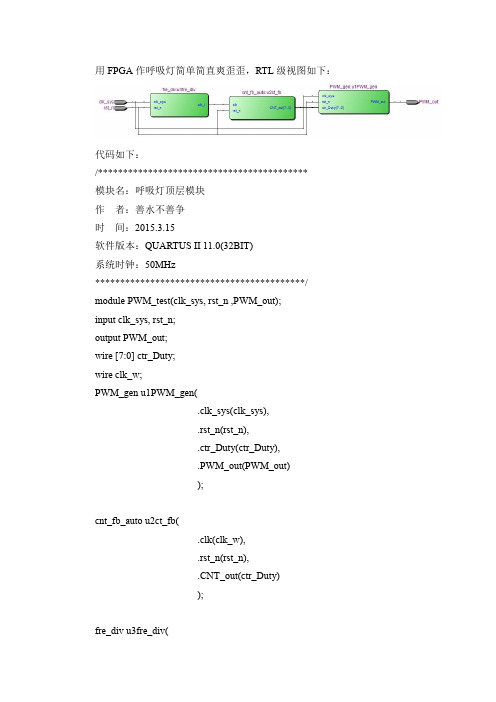

用FPGA作呼吸灯简单简直爽歪歪,RTL级视图如下:代码如下:/******************************************模块名:呼吸灯顶层模块作者:善水不善争时间:2015.3.15软件版本:QUARTUS II 11.0(32BIT)系统时钟:50MHz******************************************/ module PWM_test(clk_sys, rst_n ,PWM_out);input clk_sys, rst_n;output PWM_out;wire [7:0] ctr_Duty;wire clk_w;PWM_gen u1PWM_gen(.clk_sys(clk_sys),.rst_n(rst_n),.ctr_Duty(ctr_Duty),.PWM_out(PWM_out));cnt_fb_auto u2ct_fb(.clk(clk_w),.rst_n(rst_n),.CNT_out(ctr_Duty));fre_div u3fre_div(.clk_sys(clk_sys),.rst_n(rst_n),.clk_l(clk_w));endmodule/************************************模块名:分频计数器作者:善水不善争时间:2015.3.15软件版本:QUATUS II 11.0(32BIT)时钟频率:50MHz************************************/module fre_div(clk_sys, rst_n, clk_l);input clk_sys, rst_n;output clk_l;reg [19:0] cnt_clk;reg clk_w;/******************************************************PWM模块中最大值为FF,需要其在0~FF(即占空比0~100%)之间循环,循环时间为3秒(一呼吸的时间),所以其所需时钟频率为:255/1.5=170Hz系统时钟为50MHz,所以分频模块的计数最大值为:50000000/170=294118********************************************************/ parameter maxcnt = 20'd294118;always @(posedge clk_sys, negedge rst_n) beginif(!rst_n) begincnt_clk <= 20'd0;clk_w <= 1'b0;endelse if(cnt_clk == maxcnt) beginclk_w <= 1'b1;cnt_clk <= 20'd0;endelse beginclk_w <= 1'b0;cnt_clk <= cnt_clk + 1'b1;endendassign clk_l = clk_w;endmodule/*******************************模块名:自动可逆加减计数器作者:善水不善争时间:2015.3.15软件版本:QUARTUS II 11.0(32BIT)*********************************/module cnt_fb_auto(clk, rst_n, CNT_out);input clk, rst_n;output [7:0] CNT_out;//输出计数范围00~ffreg [7:0] cnt;reg ud_f;//ud_f=1,加法计数;ud_f=0,减法计数//计数单元,ud_f=1时,计数器cnt加1,否则减1 always @(posedge clk, negedge rst_n) beginif(!rst_n) begincnt <= 8'b00;endelse if(ud_f) begincnt <= cnt + 1'b1;endelse begincnt <= cnt - 1'b1;endend//cnt加到最大值时,ud_f赋1;cnt减到最小时,ud_f赋0 always @(posedge clk, negedge rst_n) beginif(!rst_n) ud_f <= 1'b1;else if(cnt == 8'hfe) ud_f <= 1'b0;else if(cnt == 8'h01) ud_f <= 1;endassign CNT_out = cnt;endmodule/**************************************************模块名:PWM波产生模块作者:善水不善争时间:2015.3.15软件版本:QUARTUS II 11.0(32BIT)**************************************************/ module PWM_gen(clk_sys, rst_n, ctr_Duty, PWM_out); input clk_sys,rst_n;input [7:0] ctr_Duty;//输入高电平持续时间output PWM_out;reg PWM_w;reg [7:0] cnt;//cnt从0到FF计数always @(posedge clk_sys, negedge rst_n) begin if(!rst_n) cnt <= 8'h00;else if(cnt == 8'hff) cnt <= 8'h00;else cnt <= cnt + 1'b1;end//当cnt<=ctr_Duty时输出高电平,否则输出低电平always @(posedge clk_sys, negedge rst_n) begin if(!rst_n) PWM_w <= 1'b0;else if(cnt <= ctr_Duty) PWM_w <= 1'b1;else PWM_w <= 1'b0;endassign PWM_out = PWM_w;endmodule。

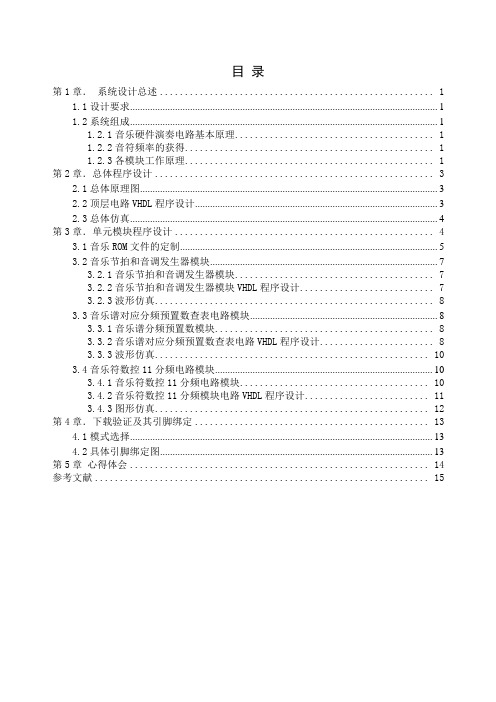

目录第1章.系统设计总述 (1)1.1设计要求 (1)1.2系统组成 (1)1.2.1音乐硬件演奏电路基本原理 (1)1.2.2音符频率的获得 (1)1.2.3各模块工作原理 (1)第2章.总体程序设计 (3)2.1总体原理图 (3)2.2顶层电路VHDL程序设计 (3)2.3总体仿真 (4)第3章.单元模块程序设计 (4)3.1音乐ROM文件的定制 (5)3.2音乐节拍和音调发生器模块 (7)3.2.1音乐节拍和音调发生器模块 (7)3.2.2音乐节拍和音调发生器模块VHDL程序设计 (7)3.2.3波形仿真 (8)3.3音乐谱对应分频预置数查表电路模块 (8)3.3.1音乐谱分频预置数模块 (8)3.3.2音乐谱对应分频预置数查表电路VHDL程序设计 (8)3.3.3波形仿真 (10)3.4音乐符数控11分频电路模块 (10)3.4.1音乐符数控11分频电路模块 (10)3.4.2音乐符数控11分频模块电路VHDL程序设计 (11)3.4.3图形仿真 (12)第4章.下载验证及其引脚绑定 (13)4.1模式选择 (13)4.2具体引脚绑定图 (13)第5章心得体会 (14)参考文献 (15)第1章.系统设计总述1.1设计要求(1)顺序播放乐曲功能(2)具有通过按键切换及其复位乐曲的功能1.2系统组成1.2.1音乐硬件演奏电路基本原理硬件电路的发声原理,声音的频谱范围约在几十到几千赫兹,若能利用程序来控制FPGA 芯片某个引脚输出一定频率的矩形波,接上扬声器就能发出相应频率的声音。

乐曲中的每一音符对应着一个确定的频率,要想FPGA发出不同音符的音调,实际上只要控制它输出相应音符的频率即可。

模块U1类似于弹琴人的手指;U2类似于琴键;U3类似于琴弦或音调发生器。

1.2.2音符频率的获得多个不同频率的信号可通过对某个基准频率进行分频器获得。

对照各个音频的频率计算该音频的分频系数。

音频的频率可以四舍五入计算。

基于FPGA的音乐合成器设计第一章:绪论随着数字信号处理技术的发展,音乐合成器越来越受到人们的关注。

音乐合成器可以帮助音乐人创造更加丰富、多样化的音乐作品。

FPGA作为一种高性能可编程逻辑器件,正逐渐成为音乐合成器设计的优选芯片。

本文结合FPGA,探讨音乐合成器的设计。

第二章:音乐合成器的工作原理音乐合成器是一种电子乐器,可以通过软件或硬件合成多种音色。

数字合成技术是音乐合成的主要手段之一,它基于取样理论,把音乐信号的模拟信号通过采样量化转换成由数字信号的二进制编码组成的序列,再通过数字信号处理技术实现音乐合成。

第三章:基于FPGA的音乐合成器设计FPGA作为一种可编程逻辑器件,具有高性能、低延迟、低功耗、高可靠性等特点,适合用于音乐合成器设计。

基于FPGA的音乐合成器设计需要解决三个主要问题:音频数据的输入输出、音乐合成算法的实现、音频信号的合成输出。

(一)音频数据的输入输出音频数据的输入输出可以通过集成外部Codec芯片实现。

Codec芯片是一种将模拟信号转换成数字信号或将数字信号转换成模拟信号的器件,同时包含ADC和DAC两个部分,可以直接将模拟信号转换成数字信号,或将数字信号转换成模拟信号输出。

(二)音乐合成算法的实现音乐合成基于数字合成技术,常见的数字合成技术有加法合成、减法合成、频率合成、波表合成等。

其中,波表合成是一种常用的数字合成技术,它通过预先生成一些波表音色,然后根据需要自由选择波表音色的组合,从而实现更加丰富、多样化的音色合成。

(三)音频信号的合成输出音频信号的合成输出需要借助FPGA芯片的PWM输出功能。

PWM是一种宽度可调的方波信号,通过控制占空比可以控制输出信号的幅值大小,进而实现音频信号的合成输出。

第四章:实验结果与分析本文采用基于FPGA的音乐合成器设计方案,设计实现了一款多音色合成器。

实验结果表明,在FPGA芯片的控制下,合成器能够自由切换多种不同音乐风格和音色特征的声音。

基于FPGA的音频信号处理系统设计与实现随着科技的发展和音频技术的不断进步,音频信号处理系统被广泛应用于各个领域。

本文将介绍基于FPGA的音频信号处理系统的设计与实现,并探讨其中的原理和关键技术。

一、引言随着数字音频技术的快速发展,音频信号处理系统的需求日益增长。

传统的音频信号处理方法往往通过软件实现,但其实时性和处理能力受到了限制。

而基于FPGA的音频信号处理系统具有高速运算、低延迟和灵活性强等优势,逐渐成为热门研究方向。

二、FPGA的基本原理FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,其内部由大量可编程的逻辑资源和存储器单元组成。

通过在FPGA上配置电路,可以实现各种不同的功能,包括音频信号处理。

三、音频信号处理系统的设计1. 模拟信号输入音频信号一般以模拟信号的形式输入到系统中,需要进行采样和模数转换。

采样率的选择应根据音频信号的特点和需求进行合理确定。

2. 数字信号处理在FPGA上设计并实现各种数字信号处理算法,如滤波、均衡、降噪等。

选择适合的算法和优化算法实现的技术,以提高系统的处理能力和性能。

3. 实时性要求由于音频信号的特性需保证处理系统的实时性。

FPGA的高并行性和硬件级别的实时性特点,使得其能够满足音频信号处理系统的实时性要求。

4. 数据存储与输出经过数字信号处理后的音频信号可以存储在FPGA内部的存储器中或外部的存储器中,也可以通过数字转模拟的方式输出到外部设备中。

四、关键技术与应用1. 快速算法优化为提高音频信号处理系统的处理速度,可以采用快速算法进行优化,如FFT(Fast Fourier Transform)等。

这些优化算法能够在保证处理结果准确性的前提下有效提高系统的运算速度。

2. 并行计算FPGA的并行计算能力是其强大的优势之一,可以将音频信号的处理任务进行拆分,同时进行多路处理,从而提高整个系统的处理能力。

3. 运算精度的选择在音频信号处理系统中,需要根据处理需求选择合适的运算精度。

摘要随着科技和经济的快速发展,人们对生活质量和生活环境的要求不断的提高,多彩多样的彩灯成了现今装饰和美化的时尚和潮流。

千姿万态的流水灯能给人一种视觉冲击。

拟采用单片机AT89C51去实现这种千变万化的流水灯。

单片机技术是一种传统和典型的技术,具有智能化、体积小、集成度高和价格低廉等许多独特的优点。

而且单片机明显优越于其他电子电路,其硬件电路和软件方面都不是特别复杂。

本设计将所学的单片机的理论和动手实践结合起来,主要利用AT89C51单片机设计并制作一个音乐流水灯。

首先设计一个稳定的直流电源电路,然后设计一个复位电路,为单片机的正常工作提供条件,然后再设计时钟电路和声音驱动电路,可以使单片机能够更好的控制与编译音乐部分,另外还设计一个通信电路以方便单片机和PC机的连接与通信,最后还需要设计按键电路用来控制音乐流水灯。

为了使蜂鸣器能够正常的发生还需设计一个音频电路。

硬件电路设计后要将各模块连接起来进行仿真和调试。

软件设计部分则需要将各电路模块进行编译,并设计音乐频率程序、流水灯程序和按键程序,同时将其进行仿真调试和组合调试。

以实现在播放音乐时LED灯有千变万化的效果,以满足对视觉上的享受。

关键词:单片机;音乐;流水灯;仿真;ABSTRACTWith the science and technology and the economy the rapid development, people pairs quality of life and living environment the requirements of continuously improve, colorful and diverse of the lantern became a nowadays decorative and beautify's fashion and trend. Zi million-state of flowing water lamp can give a person one kinds visual impact. Intends to adopt AT89C51 microcontroller to go achieve such kaleidoscopic of flowing water lights. MCU technology is a kind of tradition and typical technical, with intelligent, the volume is small, high integration and price inexpensive and so on many unique advantages. Moreover single-chip obviously superior to other electronic circuit, its hardware circuits and software aspects of are not particularly complicated.The single-chip design will combine theory and practice, the main use AT89C51 single-chip design of a musical water lights. First, design a stable DC power supply circuit, and then design a reset circuit for the microcontroller to provide normal working conditions, and then design a clock circuit and sound driver circuit, will enable MCU to better control and compile music part, in addition to design a to facilitate communication circuit chip and PC connectivity and communication, and finally also need to design the circuit to control the music keys light water. In order to make the buzzer to normal design an audio circuit needs to happen. After the hardware circuit design to connect the modules for simulation and debugging. Software design will need to be compiled each circuit module, and the design frequency of the music program, water lights and key procedures, and its combination of simulation debugging and debugging. When playing music in order to achieve a kaleidoscopic effect LED lights to meet the visual enjoyment.Key words:MCU; Music; Light water;Simulation目录摘要 (I)ABSTRACT (II)目录 (1)1. 绪论 (1)1.1 单片机的概念 (1)1.2 单片的历史、发展和应用 (4)2. 总体设计 (6)2.1 设计要求 (6)2.2 设计方案选择 (6)2.3 整体设计思路 (6)3. 系统硬件设计与部分电路说明 (8)3.1 硬件设计框图 (8)3.2 部分电路说明 (8)3.2.1 电源及启动电路 (8)3.2.2 复位电路 (9)3.2.3 时钟电路 (10)3.2.4 通信电路 (10)3.2.5 键盘电路 (11)3.2.6 流水灯电路 (11)3.2.7 音频电路 (12)3.3 电路原理图及说明 (12)4. 系统软件电路设计与分析 (13)4.1 音乐程序设计 (13)4.1.1 音乐程序流程图 (14)4.2 流水灯设计 (16)4.2.1 流水灯程序流程图 (16)4.2.2 流水灯程序 (16)4.3 音乐流水灯程序 (16)4.3.1 音乐流水灯程序流程图 (16)4.3.2 音乐流水灯程序 (17)5. 系统调试与仿真 (19)5.1 硬件调试 (19)5.2 软件调试 (19)5.3 软件仿真 (19)总结 (22)致谢 .................................................................................................... 错误!未定义书签。

基于FPGA的音乐播放器的设计作者:陈嘉来源:《中国新通信》 2018年第19期【摘要】本文主要从FPGA 概述角度出发,阐述了基于FPGA 音乐播放器电路设计原理,论述了基于FPGA 音乐播放器算法模块设计,最后对音乐播放器系统实现进行叙述,并从不同角度进行详细分析,从而为基于FPGA 的音乐音乐播放器设计研究提供参考。

【关键词】电路原理电子产品系统设计引言随着科学技术不断创新与发展,电子产品生命周期逐渐被缩短,大部分电子产品在半年内便会被新产品所替代,因此要进一步对电子产品开发周期实施缩短,由此便应用到可编程逻辑器件,不仅能够有效缩短产品开发周期,同时随着集成电路制作技术水平不断提升,可编程逻辑器件整体设计技术水平得到有效提升,从而应用到各类电子产品开发当中。

一、FPGA 概述分析FPGA 主要指一种现场可编程门阵列,其主要以CPLD、GAL、PLA 等编程器为基础,通过不断发展和创新产生,属于半定制电路之一,属于专用集成电路领域中的一种,其优势在于填补定制电路存在的缺陷,并且可以解决可编程器件门电路数有限问题。

在实际应用过程中,其主要利用逻辑单元陈列,其中包括内部连线、输入输出模块以及可配置逻辑模块CLB,通过小型查找表来实施组合逻辑,每一个D 触发器输入端都连接着查找表,然后利用触发器来实现I/O 和逻辑电路驱动,同时利用向内部静态储存单元在实现编程数据加载,从而最终实现整个FPGA 功能。

二、基于FPGA 音乐播放器电路设计原理作为一种基本逻辑器件,计数器应用比较广泛,尤其是在数字系统当中应用比较频繁,其主要应用功能是通过计算操作来发挥自身效果,其在应用过程中可以和定时、分频产生脉冲序列和节拍脉冲,分频器能够将频段不同的声音信号进行划分,同时单独将不同声音信号方法,然后将其输送到一定频段扬声器当中,并通过重放方式来实现播放目的,由此可见,播放电路基本原理主要是将声音信号进行单独方法,并通过放大方式来达到一定播放效果。

基于FPGA/CPLD的脉冲信号型乐曲播放器的设计摘要用纯硬件来完成乐曲演奏电路的逻辑非常复杂,仅凭传统的数字逻辑技术,即使最简单的电路也难以实现。

但是借助于功能强大的EDA工具和硬件描述语言,就可以轻松的实现设计。

本设计利用可编程逻辑器件设计一个控制器让不同频率的脉冲信号有序的输出并驱动扬声器发声,最终完成一首乐曲的演奏。

设计以《世上只有妈妈好》为例,分析了硬件电路发声的基本原理,探讨了可以实现设计的方案,利用VHDL语言在QuartusⅡ上编程设计了节拍发生器、分频器、顺序控制、音高控制等模块的功能。

最后,运用原理图编辑器调出已经设计好的各个模块,根据设计的要求进行连线、加输入输出脚,得到了总体设计的仿真实体。

并对总体设计进行了功能仿真和下载。

本设计完成了乐曲《世上只有妈妈好》的32个音符64个节拍的播放,每个节拍0.5秒,整曲播放时长为32秒。

基于FPGA,利用Quartus Ⅱ和VHDL语言完成的脉冲型乐曲播放器,其特点是设计简单、灵活、设计周期短;缺陷是实现播放的乐曲种类单一,播放时间长度较短,若想要实现较长的乐曲播放,则需要很长的源程序。

关键词:FPGA,EDA,VHDL,QuartusⅡ,乐曲播放器The design of the pulse-type music player based on FPGA / CPLDAbstractIt is very complex to complete the music playing logic circuit using pure hardware. Only depend on the traditional digital logic technology, it is difficult to achieve even the simple circuit. However, it is very ease to achieve by using the EDA tools and hardware description language. The design finished a controller that output a series of orderly pulse signal with different frequencies and driven speaker with, by using the programmable logic device ,and finally complete the concert of a music.The music <shi shang zhi you ma ma hao> was used as an example. The basic principal of the hardware circuit sing was analyzed. How could achieve the player’s faction was also discussed. Following functional module was designed in Quartus II by using VHDL language: pulse generator, frequencies divider, sequence control, pitch control and so on. Finally, simulate entity was build in the Block Editor of the Quartus II , using all of the module which has been designed and according to the design’s requirements to connect, and plus input and output pin. Following these, the player’s entity was simulated and downloaded. The <shi shang zhi you ma ma hao>’s note 32 of the 64 players beat was completed in this design. One beat was sat as 0.5 seconds long, and the whole song was played within 32 seconds。

目录1 引言........................................................................................ 错误!未定义书签。

2 课程简介................................................................................ 错误!未定义书签。

2.1EDA介绍....................................................................... 错误!未定义书签。

2.2VHDL介绍 .................................................................... 错误!未定义书签。

2.3QUARTUSII介绍........................................................... 错误!未定义书签。

3 FPGA简介 ............................................................................. 错误!未定义书签。

4 设计原理与分析.................................................................... 错误!未定义书签。

4.1设计题目........................................................................ 错误!未定义书签。

4.2设计分析........................................................................ 错误!未定义书签。

科学技术创新2019.181概述近些年,中小型公园、大型广场、酒吧以及室内大型表演场地相继出现了音乐灯光的身影。

音乐灯光系统成为模拟自然、渲染气氛的重要手段,音乐灯光系统已成为大众生活娱乐以及追求高雅艺术和高质量生活中不可或缺部分。

现有的高音效功放和多彩的舞台灯光的确能够渲染氛围,但灯光的控制需要一个总控制台,其体积庞大并且昂贵,因此家庭推广受到限制。

为了能够实现家庭有限空间不带总控制台的舞台灯应用,本文提出采用FPGA作为主控制器,将音乐信息转换成舞台灯光所需的DMX512协议,控制其跟随音乐的节奏、高音,低音幅度的变化而产生对应的颜色,频闪和亮度,达到音乐与灯光一体化实现舞台灯光的效果。

2系统硬件设计2.1系统结构原理。

本设计采用FPGA控制系统,其有着功耗低、设计周期短、并行操作的特点。

音乐灯光系统主要编写主控芯片FPGA主程序,来对系统进行操控;运用电源模块给设备输入稳定可靠的电源;经过蓝牙模块将手机音频传输入FPGA主控板。

通过FPGA将数据通过傅立叶时频谱分析后提取音乐数据的特征,将数据特征作为特殊标志位。

再编写FPGA程序定义协议灯通道功能的几种模式,用特殊标志位作为开关控制协议灯功能模式。

最后,通过解码器解码输出给功放与协议灯共同播放音乐与灯光,实现音乐与灯光相结合的功能。

系统结构框图如图1所示。

图1系统结构框图2.2蓝牙模块。

蓝牙功率低、经济、实时性、安全的特点,已经在日常生活中广泛普及。

蓝牙技术为使减小干扰特别设计了跳频方案与快速确认。

采用蓝牙模块传输音频数据,能使得音频信号更准确稳定的传输。

使用串口uart协议发送和接收数据,将手机作为设备的客户端实时发送数据,FPGA连接的蓝牙模块作为数据接收端。

FPGA通过编写时序逻辑电路模拟蓝牙技术的数据包的数据格式进行数据处理。

其数据以1bit的起始位数据、8bit的数据位数据和1bit的停止位数据的方式传输,通过时序逻辑电路能准确提取出蓝牙传输数据中的数据位信号,再对信号进行分析处理。

2.3RS485接口。

本设计采用RS485接口的差分输出电压能与DMX512输入信号电平兼容。

RS485接口采用MAX485芯片,其具有采用半双工通讯方式。

如图2,RE与DE脚分别为芯片接收器与驱动器输出使能,将两脚短接后由FPGA的一个I/O进行控制。

RO为接收器输出端,DI为驱动器输入端。

RO、DI两端与FPGA的CMOS电平进行通信通过芯片转化为差分信号输出,通过与DMX512协议灯的XLR通信接口相接进行通讯。

XLR有3个脚其中1脚为GND;2脚为反向端;3脚为同向端将输出的差分信号A 接入协议灯同向端,信号B接入协议灯的反向端端,1脚接地。

图2MAX485接口电路2.4功放模块。

音频功率放大首先需要将前置放大电路放大的信号经过电压放大级来对输入信号进行电压放大,使得输入到推动级的电压信号达到一定的幅值即预放大。

推动级的作用是将进过电压放大的信号进一步进行电压、电流放大,输出级仅对电流进行放大。

3系统的软件设计3.1DMX512协议。

DMX512协议是一种多通道信号传输协议。

DMX512协议传输的信号由许多的DMX512数据包组合而成。

数据包时序图如图3中序号为1的部分所示。

其中每个数据包中又包含复位序列和字段,复位序列包含了复位标志信号和字段。

有效复位标志信号为88us的低电平Break和4us的高电平信号MAB。

复位信号之后连续的第一个字段信号的功能是选通DMX512的通道,在下一个复位信号来之前的后续字段都表示在该通道下的数据。

例如有一台协议灯的第一通道功能为0°~360°的旋转。

当第一个字段的数据位00000000时即选择通道1为功能通道,当后续字段在00000000~11111111之间按时间均匀变化则协议灯的效果为0°~180°匀速旋转。

当程序快速运行在多通道之间快速复位实现连续变化时,由于人眼的暂留效应多通道功能就能同时呈现出来。

图5中序号为2的部分为每一个字段的时序图。

每一个指令帧都包含了1个开始位、8个数据位和2个结束位。

因为DMX512的传输速率是250Kbps,每一个位宽的时间为4us。

所以每个字段的数据有11位,宽度为44us。

3.2系统主流程图(图4)。

4结论本设计采用FPGA作为系统设计的主控板,用户可以通过手机蓝牙传输音乐信号,FPGA控制模块接收手机端传输的音乐信号,将接收音频信号通过功放放大播出。

通过硬件描述语言使FPGA 对数据分析处理,并将其转换成舞台灯识别的DMX512协议信号,实现舞台灯的控制。

通过提取接收的音频数据特征控基于FPGA的音乐灯光系统徐志博王浩覃昌鹏(桂林电子科技大学信息科技学院,广西桂林541004)摘要:文章围绕FPGA灵活多变的特点设计一款可以随音乐变化而变化的灯光系统。

为了实现音乐与灯光的变换,系统采用了FPGA作为主控芯片,研究了DMX512标准协议的控制原理。

选用蓝牙作为通信方式传输音乐,通过功放播放音乐。

关键词:FPGA;DMX512标准协议;音频ADC;音乐;灯光系统;蓝牙;功放中图分类号:TN79+1,TM923.5文献标识码:A文章编号:2096-4390(2019)18-0086-02(转下页)86--2019.18科学技术创新图4系统主流程图制DMX512协议模块输出,将系统将音乐与灯光联系起来。

采用FPGA 能使多个模块并行计算,提高了数据的实时性准确性。

FPGA 还具有重构性,面对仿真错误能及时有效的返回模块设计步骤,减少了设计的开发成本。

参考文献[1]姚远,李辰.FPGA 应用开发与典型实例[M].北京:人民邮电出版社,2010,66-100.[2]李晓巍.舞台灯光控制技术及其发展[J].中国新技术新产品,2015(13):35.[3]苏欣,智能多通道电功率分配的硬件设计[J].科技创新与应用,2014(6):32.[4]姚晖.基于DMX+的LED 舞台灯光控制系统的设计[D].杭州:浙江理工大学,2011.[5]黄诗涌.基于DMX512协议的8通道舞台电脑灯控制系统设计[D].广州:广东工业大学,20006.[6]崔岩,吴国兴,顾媛媛,等.基于FPGA 的红外遥控密码锁的设计[J].电子技术应用,2013,39(11):44-46.[7]钟洪声,汪玲,王明珍等.《电路分析基础》中的课程设计[J].实验科学与技术,2013,11(4):206-208.作者简介:徐志博(1996-),男,汉,浙江温州人,本科在读,研究方向:电子信息科学与技术。

通讯作者:欧少敏(1988-),女,汉,湖南永州人,讲师,研究方向:嵌入式应用以及太阳能光伏技术。

1多功能铁路轨道测试平台的需求分析目前在国内轨道检修作业工段,通常每25KM~50KM 划分一个工区,目前检测方式主要为,人工推动的单轨无动力超声探伤仪,检测速度约为3KM/小时,双轨检测速度为1.5km/小时,每公里需8至15名技工维护,完成25KM 检测需要近14小时,轨道检修作业量与所需作业时间都非常巨大,同时根据铁路部门的统计,高铁的非通车时间≤6小时/天,普铁≤2小时/天,所有路网检测工作需在此“天窗”时间内完成,对检修人员与设备的机动性提出了非常高的要求。

目前超声波检测设备生产企业也有在试验研发探伤车,但由于整车质量过重,测试前安装调试时间需2小时,设计操作未结合探伤实际操作要求,无系统设计支撑,目前均未通过检测认证要求。

为了解决目前轨道检修作业面临的巨大压力,着眼于解决轨道探伤及路网检测工作量大,劳动强度高的痛点,本文设计并制造了一种多功能铁路轨道综合测试平台,本平台基于物联网技术为控制核心,综合轨道超声波检测探伤功能、机器视觉轨道检测功能、轨道电力线巡检功能、检测数据云端上传处理分析功能等四大功能模块,在硬件部分上选用四轮电动轮毂动力平台,集成特殊定制的高速高距超声波探头的无损检测设备,高速工业线阵相机,可实现高速运行状态下的安全检测,并实时记录传输图像与传感器数据。

同时平台机械结构采用模块化与轻量化的设计理念,经实际测试,本平台可在10分钟内进行快速安装调试,极大地节约了时间与人力成本,降低检修的运维成本,大大提高检测速度及检测精度,提升轨道检测的智能化水平。

2轨道测试平台结构设计为便于设计产品的普及推广,在设计平台时,需要综合考虑在不同场景下,平台的快速运输与便捷安装调试需要,划分检测平台的需求,分安装模块进行设计制造,本功能检测多功能铁路轨道综合测试平台的设计赵国栋1单文举2(1、珠海平川智达科技有限公司,广东珠海5190002、吉林大学珠海学院,广东珠海519000)摘要:随着铁路网建设的不断进行,维护铁路轨道运行状态变得至关重要,同时,因为发车密度的不断上升,可用于维护作业的天窗时间不断缩短,运营与维修的矛盾日益尖锐。

本文为提高轨道检修效率,提出了一种多功能铁路轨道综合测试平台,能够有效地整合现有轨道检修设备,提高单位时间内检修作业公里数,并提出了一套匹配的物联网数据管理系统,对提高轨道作业的现代化具有重要的实用价值。

关键词:轨道检修;结构设计;物联网中图分类号:U213.2文献标识码:A 文章编号:2096-4390(2019)18-0087-02(转下页)图3数据包序图和字段时序图87--。