西工大数字集成电路实验报告 数集实验1

- 格式:docx

- 大小:274.89 KB

- 文档页数:6

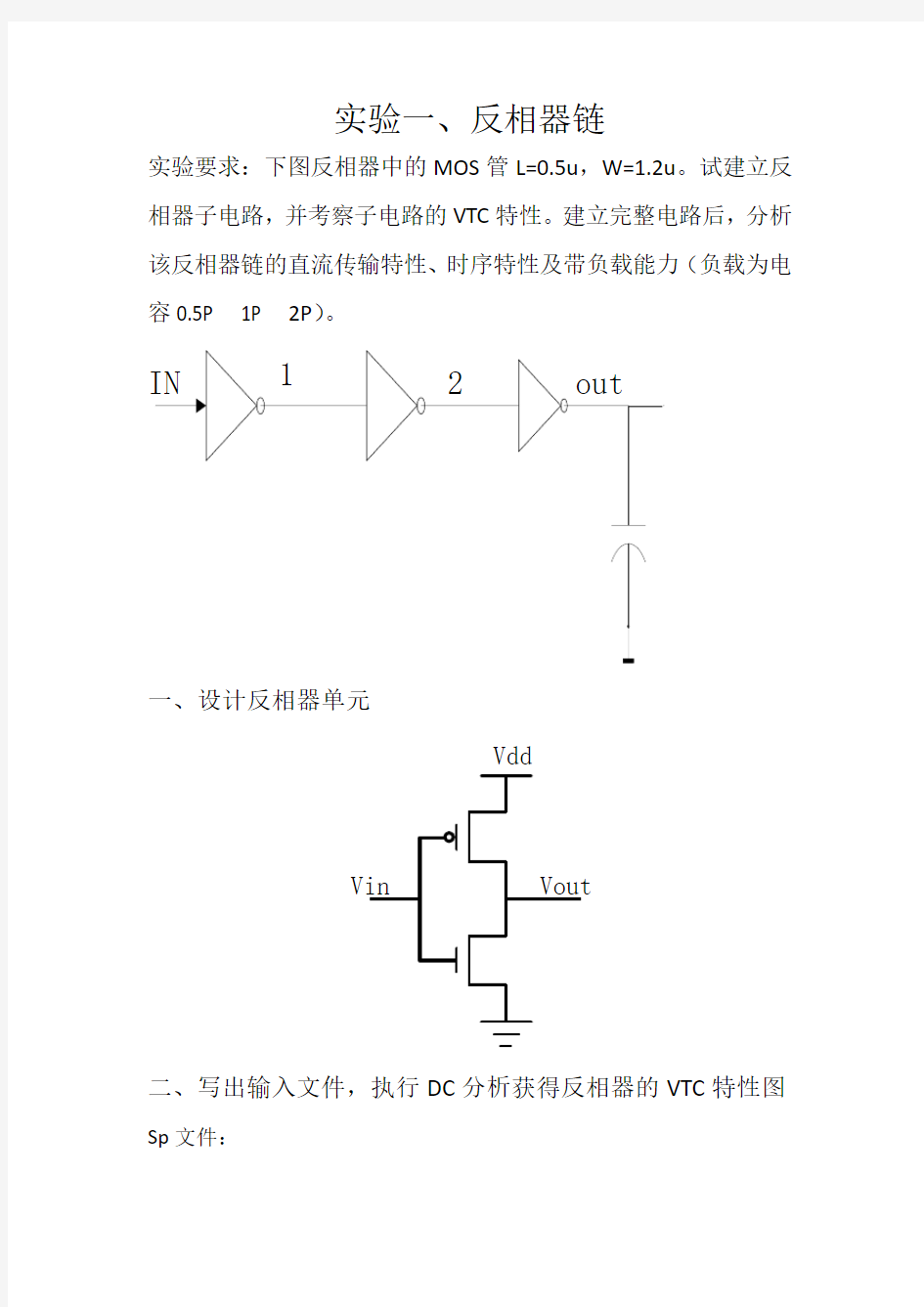

实验一、反相器链

实验要求:下图反相器中的MOS 管L=0.5u ,W=1.2u 。试建立反相器子电路,并考察子电路的VTC 特性。建立完整电路后,分析该反相器链的直流传输特性、时序特性及带负载能力(负载为电容0.5P 1P 2P )。

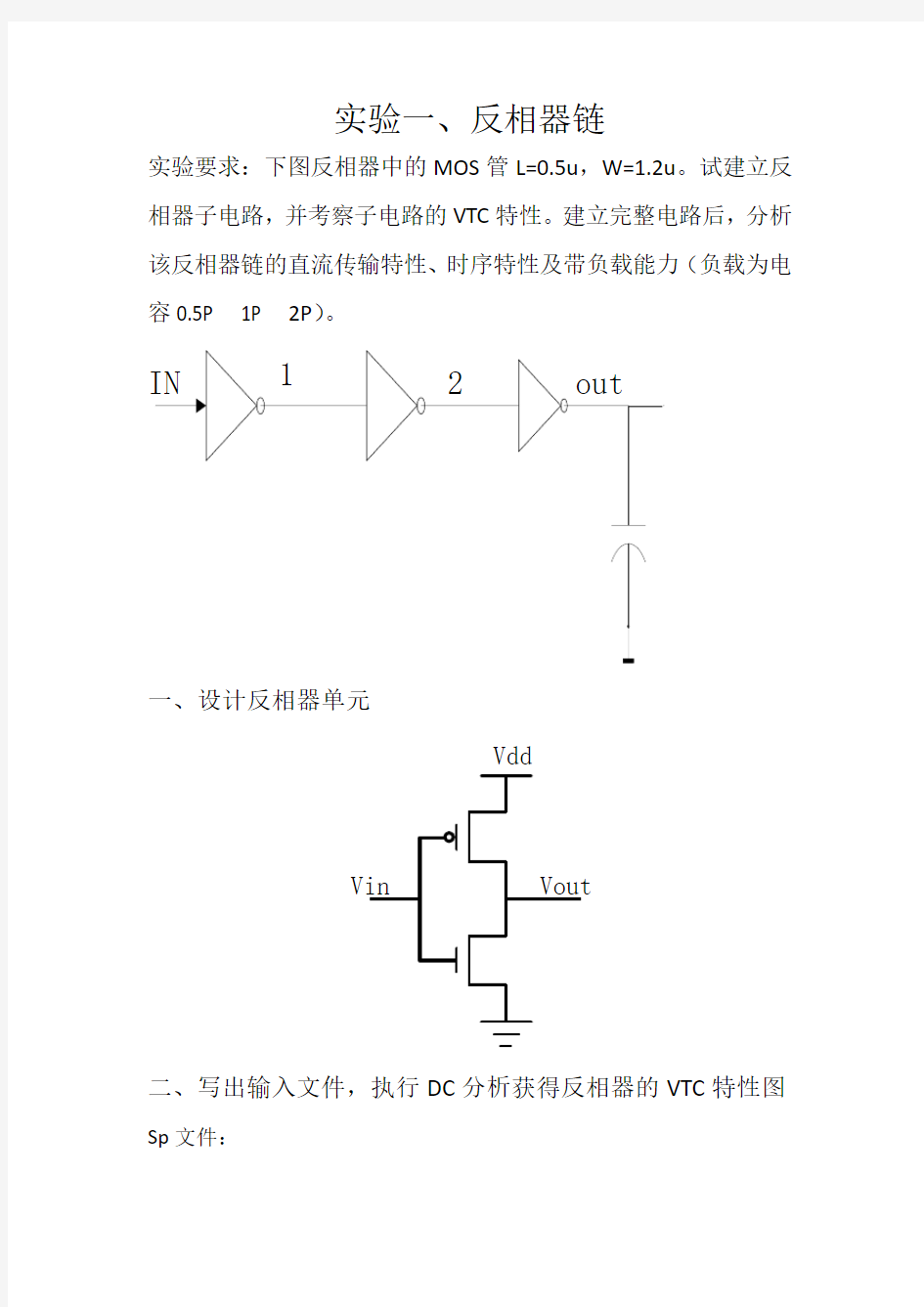

一、设计反相器单元

Vout

Vdd

二、写出输入文件,执行DC 分析获得反相器的VTC 特性图 Sp 文件:

.TITLE 1.2UM CMOS INVERTER

.options probe

.options tnom=25

.options ingold=2 limpts=30000 method=gear

.options lvltim=2 imax=20 gmindc=1.0e-12

.protect

.lib'C:\synopsys\cmos25_level49.lib' TT

.unprotect

.global vdd

Mn out in 0 0 NMOS W=1.2u L=0.5u *(工艺中要求尺寸最大0.5u)

Mp out in vdd vdd PMOS W=2.4u L=0.5u * 此处W需做更改)

CL OUT 0 0.5PF

VDD VDD 0 5V

VIN IN 0 PULSE(0 5V 10NS 1N 1N 50N 100N)

.DC VIN 0 5V 0.1V

.op

.probe dc v(out)

.end

仿真结果:

三、写出SUBCKT并实例化三个,来实现反相器链对反相器链执行DC扫描。

Sp文件:

.TITLE 1.2UM CMOS INVERTER CHAIN

.options probe

.options tnom=25

.options ingold=2 limpts=30000 method=gear

.options lvltim=2 imax=20 gmindc=1.0e-12

.protect

.lib'C:\synopsys\cmos25_level49.lib' TT

.unprotect

.global vdd

.SUBCKT INV IN OUT

Mn out in 0 0 NMOS W=1.2u L=0.5u

Mp out in vdd vdd PMOS W=2.4u L=0.5u

.ENDS

X1 IN 1 INV

X2 1 2 INV

X3 2 OUT INV

CL OUT 0 1PF

VDD VDD 0 5V

VIN IN 0 0

.DC VIN 0 5V 0.1V

.measure DC V1 when v(out)=2.5v

.PROBE dc v(out)

.END

仿真结果:

V(out)=2.5时,V1的值:

四、执行measure 命令测量延迟时间。

Sp文件:

.TITLE 1.2UM CMOS INVERTER CHAIN

.options probe

.options tnom=25

.options ingold=2 limpts=30000 method=gear

.options lvltim=2 imax=20 gmindc=1.0e-12

.protect

.lib'C:\synopsys\cmos25_level49.lib' TT

.unprotect

.global vdd

.SUBCKT INV IN OUT

Mn out in 0 0 NMOS W=1.2u L=0.5u

Mp out in vdd vdd PMOS W=2.4u L=0.5u

.ENDS

X1 IN 1 INV

X2 1 2 INV

X3 2 OUT INV

CL OUT 0 1PF

VDD VDD 0 5V

VIN IN 0 PULSE(0 5V 10NS 1N 1N 50N 100N)

.TRAN 1N 200N

.measure tran tdelay trig v(in) val=2.5 td=8ns rise=1

+ targ v(out) val=2.5 td=9n fall=1

.PRINT V(OUT)

.end

仿真结果:

五、考察电路带容性负载的能力(建立DATA包含三个容值,

瞬态分析时执行SWEEP DATA=DATANM)Sp文件:

.TITLE 1.2UM CMOS INVERTER CHAIN

.options probe

.options tnom=25

.options ingold=2 limpts=30000 method=gear

.options lvltim=2 imax=20 gmindc=1.0e-12

.protect

.lib'C:\synopsys\cmos25_level49.lib' TT

.unprotect

.global vdd

.SUBCKT INV IN OUT

Mn out in 0 0 NMOS W=1.2u L=0.5u

Mp out in vdd vdd PMOS W=2.4u L=0.5u

.ENDS

X1 IN 1 INV

X2 1 2 INV

X3 2 OUT INV

VDD VDD 0 5V

VIN IN 0 PULSE(0 5V 10NS 1N 1N 50N 100N)

.TRAN 1N 200N

.Param C1=0

CL OUT 0 C1

.TRAN 1N 200N sweep data=d1

.data d1 C1

+ 0.5p

+ 1P

+ 2P

.enddata

.PRINT V(OUT)

.end

仿真结果: