第9章 高速串行总线

- 格式:ppt

- 大小:653.00 KB

- 文档页数:47

高速串行总线知多少…纵观整个电子行业,制造商和其他公司推出的串行总线标准以满足市场和客户提出的多样化的需求。

这些标准的关键性目标是在某一个体系框架内,由不同制造商生产的设备能够相互通用。

每个标准是由一个管理机构、委员会和工作组,建立设计和测试要求。

表1 列出一些关键串行标准。

表1:重要的串行总线标准每个规范定义了产品必须符合标准的要求,包括电气、光学、机械、互连等等。

管理机构发起标准化测试,来检验产品是否能通过标准要求。

这些测试可能会详细到了指定具体的测试设备。

标准不断发展,因此参数规格不断的修改。

必须保持目前对产品的测试和规范的要求一致。

我参与许多标准组织并在不同的工作组中和其他公司一道,帮助管理机构制定有效的测试过程和符合性测试流程。

在这份文档中,我们会提到以下三个标准。

泰克公司作为工作组的一员,参与到这些标准的制定中。

SATASATA 接口是一个标准的串行存储接口,广泛应用于在今天的台式机和其他计算平台。

最初的速率只用1.5Gbps,但最近更新到 3.0Gbps 的第二代规范,已经进入市场。

下一代标准规定速率是6Gbps,部分规范正在业内制定中。

图1.SATA 总线的机械结构像许多串行标准,S A T A 接口采用低电压差分信号(LVDS)和8b/10b 编码。

数据在发射端和接收端之间采用全双工的数据通道,分别由一条发送通道(Tx)和一条接收通道(Rx)组成。

SATA 接口采用了扩频时钟(SSC)嵌入式时钟方法,不提供单独的参考时钟传送给接收端。

PCI ExpressPCI Express 已经取代PCI 成为大多数芯片到芯片级的应用或电路板传输和电缆连接中系统中使用。

PCIe 是一个高度可扩展的架构,提供从1 到16 条全双工的PCIe 连接。

在多通道应用,数据流根据现有可用通道的情况而拆分,同时在多个通道上传输。

最快的PCIe 应用通常是图像处理应用,通过16 条高速通道,在系统芯片组和图形处理器之间传输高分辨率的图形数据。

串行总线原理

串行总线是计算机系统中用来传输数据的一种传输方式。

它通过将数据位按照顺序一个接一个地发送,而不是同时发送多个数据位。

这种方式需要较少的电子线路和物理连接,因此可以节省空间和成本。

在串行总线中,发送方将数据位按照一定的顺序发送到接收方。

发送方将每个数据位转换为电信号,并通过物理线路将信号发送给接收方。

接收方将接收到的信号转换为数字信号,并恢复原始的数据位。

串行总线使用起来较为简单,因为数据位是依次发送的,所以在传输过程中不会发生数据冲突。

这意味着可以减少许多数据传输时需要解决的问题。

然而,串行总线的传输速度相对较慢。

由于数据是按顺序一个一个地发送的,所以整个数据包的发送时间较长。

这在需要高速传输大量数据的应用中可能成为一个限制因素。

因此,在实际应用中,通常会采用并行总线来提高传输速度。

并行总线可以同时发送多个数据位,从而加快数据传输的速度。

但是,并行总线需要更多的物理连接和电子线路,因此成本较高。

总的来说,串行总线是一种简单而经济的数据传输方式,适用于对传输速度要求不高的应用场景。

而在需要高速传输大量数据的情况下,则需要采用并行总线。

高速串行总线的常用测试码型本文讨论了高速串行链路中常用的测试码型伪随机码流的原理,以及不同的测试码型对物理层测试结果的影响。

高速串行总线的常用测试码型在当今的电信和计算机产品上,相比传统的并行总线,电路中的串行总线越来越多,速率越来越快。

比如通信产品中的10GBase-KR、CPRI2代,计算机中的PCIeGen2、SATA6G,存储产品中的SAS6G、FC8.5G,这些串行总线都陆续的跨过了5Gbps。

由于速率比较高,使得串行总线上的相关的收发器芯片(SERDES)、连接器、单板、背板的设计面临着越来越多的挑战。

对于这些高速串行总线的物理层测试,测试码型的选用至关重要,在很多串行总线的规范中对测试码型有严格的要求。

本文将对此进行探讨。

首先,串行总线的物理层测试通常分为发射机测试和接收机测试,又称为TX测试和RX测试。

发射机测试通常包括眼图、抖动、信号波形、幅度、上升下降时间等测试项目,接收机测试通常包括误码率、抖动容限、接收机灵敏度等测试项目。

对于眼图测试、误码率和抖动容限测试,最常用的测试码是伪随机码(PseudoRandomBinarySequence,简称PRBS),主要有PRBS7、PRBS15、PRBS23和PRBS31。

除了PRBS以外,K28.5、1010、CJPAT等码型在很多串行总线的物理层测试中都很常用,特别是计算机上的串行标准(比如SATA、USB3.0、SAS)的测试码型有所不同,在本文中主要讨论最常用的测试码型——PRBS。

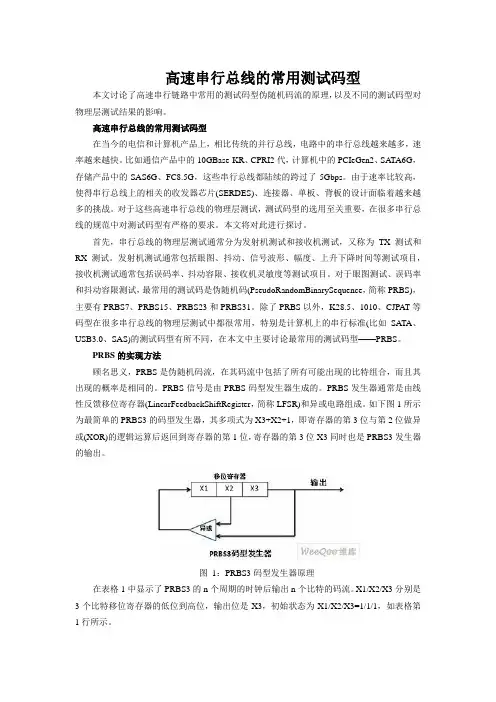

PRBS的实现方法顾名思义,PRBS是伪随机码流,在其码流中包括了所有可能出现的比特组合,而且其出现的概率是相同的。

PRBS信号是由PRBS码型发生器生成的。

PRBS发生器通常是由线性反馈移位寄存器(LinearFeedbackShiftRegister,简称LFSR)和异或电路组成。

如下图1所示为最简单的PRBS3的码型发生器,其多项式为X3+X2+1,即寄存器的第3位与第2位做异或(XOR)的逻辑运算后返回到寄存器的第1位,寄存器的第3位X3同时也是PRBS3发生器的输出。

串行总线是什么?(优点和作用)串行总线是什么?(优点和作用)任何一个微处理器都要与一定数量的部件和外围设备连接,但如果将各部件和每一种外围设备都分别用一组线路与CPU直接连接,那么连线将会错综复杂,甚至难以实现。

为了简化硬件电路设计、简化系统结构,常用一组线路,配置以适当的接口电路,与各部件和外围设备连接,这组共用的连接线路被称为总线。

采用总线结构便于部件和设备的扩充,尤其制定了统一的总线标准则容易使不同设备间实现互连。

微机中总线一般有内部总线、系统总线和外部总线。

内部总线是微机内部各外围芯片与处理器之间的总线,用于芯片一级的互连;而系统总线是微机中各插件板与系统板之间的总线,用于插件板一级的互连;外部总线则是微机和外部设备之间的总线,微机作为一种设备,通过该总线和其他设备进行信息与数据交换,它用于设备一级的互连。

图串行通信另外,从广义上说,计算机通信方式可以分为并行通信和串行通信,相应的通信总线被称为并行总线和串行总线。

并行通信速度快、实时性好,但由于占用的口线多,不适于小型化产品;而串行通信速率虽低,但在数据通信吞吐量不是很大的微处理电路中则显得更加简易、方便、灵活。

串行通信一般可分为异步模式和同步模式。

-随着微电子技术和计算机技术的发展,总线技术也在不断地发展和完善,而使计算机总线技术种类繁多,各具特色。

下面仅对微机各类总线中目前比较流行的总线技术分别加以介绍。

一、内部总线1.I2C总线I2C(Inter-IC)总线10多年前由Philips公司推出,是近年来在微电子通信控制领域广泛采用的一种新型总线标准。

它是同步通信的一种特殊形式,具有接口线少,控制方式简化,器件封装形式小,通信速率较高等优点。

在主从通信中,可以有多个I2C总线器件同时接到I2C总线上,通过地址来识别通信对象。

2.SPI总线串行外围设备接口SPI(serial peripheral interface)总线技术是Motorola公司推出的一种同。

第九章并⾏处理技术 本章讲述的重点内容就是阵列处理机和多处理机,对阵列机的基本结构、主要特点、以及阵列机的互连络和并⾏存储器的⽆冲突访问等内容要加强理解。

本章应掌握的概念有:阵列处理机、络拓扑结构、单级⽴⽅体络、多级⽴⽅体等。

⼀、并⾏处理技术(识记): 并⾏性主要是指同时性或并发性,并⾏处理是指对⼀种相对于串⾏处理的处理⽅式,它着重开发计算过程中存在的并发事件。

并⾏性通常划分为作业级、任务级、例⾏程序或⼦程序级、循环和迭代级以及语句和指令级。

作业级的层次⾼,并⾏处理粒度粗。

粗粒度开并⾏性开发主要采⽤MIMD⽅式,⽽细粒度并⾏性开发则主要采⽤SIMD⽅式。

开发计算机并⾏性的⽅法主要有:资源重复、时间重叠和资源共享三种⽅法。

⼆、SIMD并⾏计算机(阵列处理机) 阵列机也称并⾏处理机。

它将⼤量重复设置的处理单元按⼀定⽅式互连成阵列,在单⼀控制部件CU(Contrul Unit)控制下对各⾃所分配的不同数据并⾏执⾏同⼀指令规定的操作,是操作并⾏的SIMD计算机。

它采⽤资源重复的措施开发并⾏性。

是以SIMD(单指令流多数据流)⽅式⼯作的。

1、阵列机的基本结构(识记) 阵列机通常由⼀个控制器CU、N个处理器单元PE(Processing Element)、M个存储模块以及⼀个互连络部件(IN)组成。

根据其中存储器模块的分布⽅式,阵列机可分为两种基本结构:分布式存储器的阵列机和共享存储器的阵列机(理解⼆者不同之处)。

阵列机的主要特点: 它采⽤资源重复的⽅法引⼊空间因素,这与利⽤时间重叠的流⽔线处理机是不⼀样的。

它是利⽤并⾏性中的同时性⽽不是并发性,所有的处理单元必须同时进⾏相同操作(资源重复同时性)(我们想象⼀下亚运会的开幕式⼤型团体操表演,每个⼈就是⼀个PE,他们听从⼀个总指挥的指令,同时进⾏⾃⼰的操作,很快地就能"计算"出⼀个结果(队形)来。

) 它是以某类算法为背景的专⽤计算机,基本上是专⽤于向量处理的计算机(某类算法专⽤机)。

高速串行总线设计基础概述及解释说明1. 引言1.1 概述在当前信息技术飞速发展的背景下,高速串行总线作为一种重要的数据传输方式,在各个领域都得到了广泛的应用。

它已经取代了传统的并行总线,并带来了更快、更稳定的数据传输速度。

本文将对高速串行总线的设计基础进行详细阐述,包括其概念、优势以及应用领域。

1.2 文章结构为了使读者能够系统地了解高速串行总线的设计基础,本文将分为五个主要部分来讲解相关内容。

首先,在引言部分将介绍本文的概述和结构,然后进入正文部分。

第二部分将详细讨论什么是高速串行总线以及它所具备的优势。

接着,第三部分将深入探讨高速串行总线的工作原理,包括数据传输模式、时钟和同步机制以及数据编码和解码方法等内容。

第四部分将对目前较为常见的几种高速串行总线协议标准进行比较与分析,主要涉及PCI Express(PCIe)协议标准、USB协议标准和Thunderbolt协议标准。

最后,第五部分将讨论高速串行总线设计中的关键要点与挑战,包括时钟和信号完整性管理、噪声抑制与电磁兼容(EMC)设计技术以及延迟和功耗优化方法等。

1.3 目的本文的主要目的是为读者提供高速串行总线设计的基础知识,以便更好地理解其原理和应用。

通过对高速串行总线概念、工作原理和协议标准的讲解,读者可以更加全面地了解这一领域。

同时,本文也旨在帮助读者认识到高速串行总线设计中可能遇到的关键问题和挑战,并为其提供相应的解决方法和技巧。

希望通过阅读本文,读者能够深入研究和探索高速串行总线设计,并能够在实际应用中取得更好的效果。

2. 高速串行总线设计基础:2.1 什么是高速串行总线:高速串行总线是一种数据传输技术,用于在计算机系统中连接各种设备和组件。

与传统的并行总线相比,高速串行总线使用较少的物理引脚,并通过将数据位逐位地传输来提供更高的传输速度。

它可以有效地支持更快的数据传输率,并能同时处理多个信号。

2.2 高速串行总线的优势:高速串行总线具有以下优势:- 传输速度快:由于采用逐位传输方式,高速串行总线能够实现更快的数据传输速度。

⾼速串⾏简史(⼀):信号、接⼝、协议及总线在这个系列开篇的时候⼤家提到了希望了解⼀下,其实基本的概念⼤家应该都知道⼀点,但真正要把它写出来,我觉得⼜不是很好下笔,这也是为什么隔了这么久才推出这篇⽂章,我们也是为了对⼤家负责的态度,不能误导了各位忠实的读者,有什么说得不对或者没有说得很清楚的希望⼤家⼀起来探讨。

突然有个问题,我们通常说的PCIE,既可以是PCIE信号,也可以是PCIE接⼝、PCIE总线,还可以是PCIE协议。

之所以难写,其实中间就是涉及到了太多的概念和认知的差异,因为串⾏和并⾏的概念太⼴了。

只要百度⼀下串⾏和并⾏,就会出来很多类似“串⾏通信与并⾏通信”、“串⾏接⼝与并⾏接⼝”、“串⾏总线与并⾏总线”、“串⾏协议与并⾏协议”以及“串⾏传输与并⾏传输”等概念介绍,⽽我们现在要说的串⾏信号应该包括了上⾯所有的这些概念,既有传输(通信)⽅式,⼜有接⼝类型,同时还有数据本⾝的协议特点,信号、协议、总线和接⼝,有时候看起来是⼀样的,但细细思量却还是有差别的,总之不是⼀两句话就能说清楚的(如PCIE信号、PCIE协议、PCIE接⼝以及PCIE总线之间的相互⽠葛就是剪不断理还乱啊)。

举个简单的例⼦,PCI总线说的是⼀组传输通道,⽽PCI接⼝是⼀种连接标准,两者之间的关系就是PCI接⼝的设备都要通过PCI总线来进⾏通信,⽽PCI总线上⾛的设备并不全是PCI接⼝的,像集成声卡,⾛的就是PCI总线。

在这⾥PCI总线提供了⼀种通道,这个通道上可以有不同的符合这种通道要求的接⼝设备或信号(PCI信号或Audio信号)。

打个更进⼀步的⽐⽅:两者关系就像马车(接⼝设备)和马路(总线)⼀样,马车必须在马路上⾛,⽽马路上不⼀定⾛马车(⽜车等)。

如下图所⽰。

车(接⼝、信号)有车(接⼝、信号)的标准(协议),如马车、汽车、⽕车、货车、⾃⾏车等(PCIE、SATA、SAS、USB等信号标准);路(通道、总线)有路的标准,如马路、⼈⾏道、⾼速公路等(PCIE、SATA、SAS、USB等通道标准),所以协议⾥⾯⼜包含通道(总线)协议和信号(接⼝)协议。