高速串行总线RapidIO与PCI Express协议分析比较

- 格式:pdf

- 大小:285.08 KB

- 文档页数:4

Rapid-IO 、PCI-E 和10GBase-T R id IO PCI E10GB T测试方案Rapid-IO简介目录Rapid-IO 的物理层信号质量测试Rapid-IO 的协议层测试分析PCIE PCIE简介PCIE 的物理层信号质量测试PCIE 的协议层测试分析10GBase-T 简介及物理层信号质量测试NAFO 09Rapid-IO简介Rapid IO什么是RapidIO嵌入式系统中用于替代PCI协议的一种高速总线协议的种高速总线主要的应用领域在于:通讯系统,图像处理系统以及国防军工装备高速传输,使用低压差分信号由Motorola公司发起的协议组成,(安捷伦公司是该协议组织的会员)公司发起的协议组成(安捷伦公司是该协议组织的会员)与HyperTransport (AMD), PCI Express (Intel)进行竞争NAFO 09RapidIORapidIO 芯片和集成系统提供商Bus Bridges &gSwitch FabricsMicroprocessorsBoards/platformsProgrammable LogicRapidIO 的总线开发公司RapidIOWirelessWirelessbase stations 还有其他大量使用PowerPC 处理器的单位(8260, etc)ControlRapidIO Links Switched fabric means more ports t b !RapidIO 互连互通的例子ProcessorR idIO S it h Data Path LinksDebug Portto probe!RapidIO SwitchData Switch Fabric Control PacketForwarding PacketForwarding Fabric ControlControlControl Data Switch FabricPacket Packet PHY Packet ProcessorPHYPacket ProcessorRapiodIO协议规范特点RapidIO采用三层分级的体系结构,分级结构图如下图所示:RapiodIO物理层测试表述Level I 的输出信号已经具备如下特性:• 支持三种不同的波特率:1.25G, 2.5G, 以及3.125G支持种的波特率• 支持×1 ×2 ×4 ×8 ×16 等多个Lane结构• 接收段采用AC耦合• 支持热插拔• 发射端口支持:short run (SR) 和long run (LR) 两种类型的传输信号发射端支持• short run 传输信号至少可以传输20 cm 通过1个连接器• long run 传输信号至少可以传输50 cm 通过2个连接器• 发射系统• 每一个Lane的误码率要求低于10-12每个12• 不需要使用均衡来功能** 参考协议第9章什么是Short Run 和Long Run Short Run指的是发射端口和接收端口在同一个PCB上面直接进行芯片到芯片的接仅仅个接接连接或者是中间仅仅通过一个连接器进行连接Long Run指的是发射端口和接收端口使用更大摆动幅度的信号进行传输,传输指的是发射端口和接收端口使用更大摆动幅度的信号进行传输传输过程中通过了两个或者两个以上的连接以及背板进行连接* 参考协议第8章ShortRun和LongRun输出信号的要求信号抖动和眼图的要求Short RunLong RunReceiver接收抖动和眼图的要求Receiver抖动容限要求Aerospace and Defense Symposium 2008 2009 AD On-Site Seminarg pAgilent Rapid-IO物理层的信号质量分析方案帮助您发现问题的根源70 ps8 GHzp80 ps8 GHz 90 ps 6 GHz90000 X-Series系列示波器能提供的真正的32GHz模拟带宽能提供的真的9最高的实时示波器的测试精度9完善的30GHz示波器探头系统9业界最全面丰富的测试应用软件带宽可升级可以保护用户的投资10款新的示波器型号DSO/DSA91604A DSO/DSA92004A DSO/DSA92504A DSO/DSA92804A DSO/DSA93204A 模拟带宽(2 ch)16 GHz20 GHz 25 GHz28 GHz 32 GHz最大采样率(2 ch/4 ch)80/40 GSA/s80/40 GSA/s80/40 GSA/s80/40 GSA/s80/40 GSA/s 标配存储深度10M10M10M10M10M最大存储深度 2 Gpts 2 Gpts 2 Gpts 2 Gpts 2 Gpts噪声@ 50mV/div 1.34 mV 1.53 mV 1.77 mV 1.89 mV 2.08 mV 抖动测量噪底150 fs rms150 fs rms150 fs rms150 fs rms150 fs rms90000X的关键技术:MCBGA封装的前端前端芯片正面:蔽盖扣上屏蔽盖以后前端芯片正面:Oak Module 去掉屏蔽盖以后90000X的采集板90000X示波器前端的内部结构4、类同轴设计确保信号屏蔽。

SRIO协议分析协议名称:SRIO协议分析一、引言SRIO(Serial RapidIO)协议是一种高速串行总线协议,用于在芯片之间传输数据和控制信息。

本协议分析旨在深入了解SRIO协议的特性、工作原理和应用场景,以便更好地理解和应用该协议。

二、协议概述SRIO协议是一种点对点的高速串行总线协议,支持数据传输和控制信息的交换。

它提供了可靠的、低延迟的数据传输,适用于各种应用领域,如通信、网络、嵌入式系统等。

三、协议特性1. 高速传输:SRIO协议支持多个速率选项,包括1.25Gbps、2.5Gbps、3.125Gbps等,可根据实际需求选择适当的速率。

2. 可靠性:SRIO协议采用差错检测和纠正机制,确保数据传输的可靠性和完整性。

3. 低延迟:SRIO协议具有较低的传输延迟,适用于对实时性要求较高的应用场景。

4. 灵活性:SRIO协议支持多种拓扑结构,包括点对点、多点对点、多点对多点等,可根据系统需求选择合适的拓扑结构。

5. 扩展性:SRIO协议支持多种数据传输方式,如流模式、消息模式等,可根据应用需求选择合适的传输方式。

四、协议工作原理1. 初始化阶段:在SRIO协议的初始化阶段,各个节点通过发送和接收初始化消息来建立通信连接。

2. 数据传输阶段:在建立通信连接后,节点之间可以通过SRIO协议进行数据传输。

数据可以以流模式或消息模式进行传输,发送节点将数据打包成数据包并发送给接收节点,接收节点则解析数据包并进行相应的处理。

3. 控制信息交换:除了数据传输外,SRIO协议还支持控制信息的交换。

节点可以通过发送控制消息来进行配置、管理和监控等操作。

五、协议应用场景1. 通信系统:SRIO协议广泛应用于通信系统中,用于高速数据传输和控制信息交换,提高系统的性能和可靠性。

2. 网络设备:SRIO协议可用于网络设备中,实现高速数据传输和设备之间的通信。

3. 嵌入式系统:SRIO协议适用于嵌入式系统中,用于连接各个芯片和模块,实现数据传输和控制信息交换。

图1 SRIO协议层级PCI Express协议有物理层、数据链路层、处理层等共三层。

如图2所示。

嵇康(1981-),男,江苏涟水人,本科,工程师。

研究方向:机载座舱显示技术。

林茂宽(1988-),男,湖北大冶人,本科,助理工程师。

研究方向:机载座舱显示技术。

李兵强(1981-),男,河北邢台人,硕士,工程师。

研究方向:机载座舱显示技术。

张杰(1984-),男,江苏淮安人,本科,高级工程师。

研究方向:机载座舱显示技术。

夏建平(1988-),男,江苏常州人,本科,助理工程师。

研究方向:机载座舱显示技术。

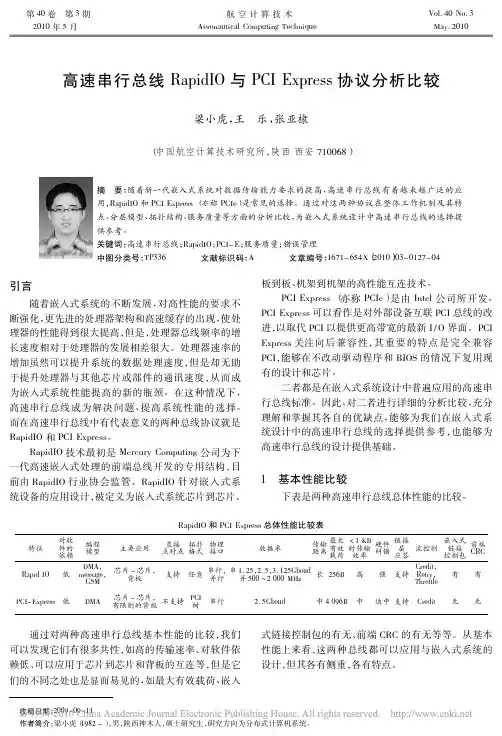

图2 PCI Express网络分层两者的第一层都为物理层,但其实质内容略有不同,SRIO串行物理层电器接口使用差分电流量控制基于802.3XAUI规范的驱动器,而PCI Express协议的电器接口采用高速的低压差分信号(LVDS)的驱动器和接收器。

两者的第二层名称不同,实质内容更是不一样,SRIO的传输层支持8bit或16bit器件ID,一个网络最多可容纳256或65 536个终端器件。

PCI Express的数据链路层,其功能设置图3 SRIO网络结构图从以上对比来看,注重网络结构多样性时,尽量选择,考虑到设备升级换代影响时,尽量选择PCI Express。

SRIO和PCI Express这两种最常用的总线形式的工作机制、特点、分层模型、拓扑结构等。

协议具有传输效率更高、允许更灵活的拓扑结构和多样的处理部件的特点,当考虑到高实时性、高可靠性时应优先选择。

PCI Express协议具有前后兼容性的特点,当考虑到大块数据传输、低成本设计、实时性较低以及系统网络简单时应优先选择。

参考文献[1]孟会,刘雪峰.PCI Express工程,2006(23):253-255.[2]Sam Fuller.SRIO嵌入式系统互联电子工业出版社,2004.图4 PCI Express网络结构图,B A r e z o o,A A b d u l l a h. Positional,Geometrical,and Thermal Errors Compensation by Tool Path Modification Using Three Methods of Regression,N euralNetworks,andFuzzy Logic[J].The International Journal of Advanced ManufacturingTechnology,2013:1635-1649.童恒超,等.数控机床热误差实时上海交通大学学报,2005,39(9):1389-1392.范嘉桢,等.基于FANUC oi系统外部坐标原点偏移功能的数控机床误差补偿研究造,2009,47(7):73-76.[12]W Wang,Y Zhang,JG Yang.Modeling of Compound Errors for CNC Machine Tools[J].Advanced Materials Research,2012:1796-1799.[13]G Cui,Y Lu,D Gao,etal.ANovel Error Compensation Implementing Strategy and Realizing on Siemens 840D CNC Systems[J].The International Journal of AdvancedManufacturing Technology,2012:595-608.。

以太网、PCIe和R apidI O的比较虽然在嵌入式系统中有许多连接元件的方法,但最主要的还是以太网、PCI Expres s和Rap idIO这三种高速串行标准。

所有这三种标准都使用相似的串行解串器(SerDes)技术,它们提供的吞吐量和时延性能都要超过宽的并行总线技术。

随着这些标准的不断发展,今后的趋势将是采用通用SerDe s 技术。

这意味着这些协议提供的原始带宽不会有明显的差异。

相反,每种协议的用途将取决于如何使用带宽。

大多数设计人员都很熟悉基本的以太网协议特征。

以太网是一种'尽力而为'的数据包传送方式。

在以太网物理层上建立的软件协议,如TCP/IP,需要提供信息的可靠传输,因为基于以太网的系统一般在网络层执行流量控制,而不是在物理层。

一般基于以太网的系统带宽都要超配20%到70%。

因此以太网最适合高时延的设备间应用,或带宽要求较低的板上/板间应用。

相反,PCI Expres s(PCIe)针对板上互连的数据包可靠传送作了优化,这种场合的典型时延在毫秒数量级。

PCIe协议交换的是事务处理层数据包(TLP),如读和写,以及被称为数据链路层数据包(DLLP)的少量特殊链路信息。

DLLP用于链路管理功能,包括物理层的流量控制。

PCIe后向兼容传统的PCI和P CI-X器件,这些器件认为处理器位于总线层的顶部,因此PCIe具有能够充分利用与P CI 相关的软件和硬件知识产权的优势。

正如后文要讨论的那样,传统PCI总线对交换式PCIe协议有很大的约束。

RapidI O技术则针对嵌入式系统作了优化,尤其是那些要求多处理单元合作的嵌入式系统。

与PCIe一样,RapidI O协议交换的是数据包和被称为控制符的少量特殊链路信息。

随着高性能嵌入式系统的不断发展,芯片间及板间互连对带宽、成本、灵活性及可靠性的要求越来越高,传统的互连方式,如处理器总线、PCI总线和以太网,都难以满足新的需求。

处理器总线主要用作外部存储器接口,如德州仪器(TI) C6000系列DSP的外部存储器接口,可支持外接同步SDRAM、SBSRAM及FIFO,也可支持异步SRAM、FLASH等。

外部存储器接口也可用作与板内FPGA或ASIC芯片互连,这种情况下,FPGA或ASIC模拟一个DSP支持的存储器接口,DSP则把FPGA或ASIC当作存储器来访问。

这类同步接口带宽可达10Gbps,如德州仪器TMS320C6455 DSP的DDR2接口最大带宽为17.066Gbps,SBSRAM接口最大带宽为8.533Gbps。

然而,这种接口也存在一些局限性:1. 接口管脚多,硬件设计困难。

常见的DDR2接口有70~80个管脚;2. 只能用于板内互连,无法用于板间互连;3. 不是点对点的对等互连,DSP始终是主设备,其它器件只能做从设备。

PCI是广泛用于计算机内器件互连的技术。

传统PCI技术也采样类似于上述存储器接口的并行总线方式,如TMS320C6455 DSP的PCI接口,有32bits数据总线,最高时钟速度为66MHz,共有42个管脚。

最新的串行PCI Express技术采用与串行RapidIO(SRIO,Serial RapidIO)类似的物理层传输技术,使得带宽达到10Gbps左右。

但由于其主要的应用仍是计算机,而且为了兼容传统PCI技术,使得它在嵌入式设备方面的应用具有一定的局限性,如不支持点对点对等通信等。

众所周知,以太网是使用最广泛的局域网互连技术,它也被扩展应用到嵌入式设备互连,但它的局限性也是显而易见的:1. 不支持硬件纠错,软件协议栈开销较大;2. 打包效率低,有效传输带宽因此而减小;3. 只支持消息传输模式,不支持对对端设备的直接存储器访问(DMA, Direct Memory Access)。

rapidio协议RapidIO协议。

RapidIO是一种面向高性能计算和通信系统的互连技术,它提供了一种高速、低延迟的数据传输方式,被广泛应用于网络设备、嵌入式系统、通信基站等领域。

本文将对RapidIO协议进行详细介绍,包括其特点、应用、优势等方面的内容。

RapidIO协议是一种面向数据包交换的互连技术,它采用了分组交换的方式进行数据传输,能够实现高速、低延迟的数据通信。

RapidIO协议的特点之一是支持多种拓扑结构,包括点对点、多播、环形等结构,可以灵活地适应不同的系统架构需求。

此外,RapidIO还支持多种数据传输模式,包括可靠性传输、流控传输等,能够满足不同应用场景下的数据传输需求。

在实际应用中,RapidIO协议被广泛应用于网络设备、嵌入式系统、通信基站等领域。

在网络设备中,RapidIO可以实现高速数据交换,提高网络传输效率,降低数据传输延迟,提升系统性能。

在嵌入式系统中,RapidIO可以实现多个处理器之间的高速数据传输,支持多种外设设备的连接,满足复杂系统的数据通信需求。

在通信基站中,RapidIO可以实现基站内部各个模块之间的高速数据交换,提高通信系统的性能和稳定性。

与其他互连技术相比,RapidIO协议具有许多优势。

首先,RapidIO具有高速、低延迟的特点,能够满足高性能计算和通信系统对数据传输速度的需求。

其次,RapidIO支持多种拓扑结构和数据传输模式,具有较高的灵活性和可扩展性,能够适应不同系统架构和应用场景的需求。

此外,RapidIO还具有较高的可靠性和稳定性,能够保证数据传输的安全和稳定。

总的来说,RapidIO协议是一种高性能、灵活、可靠的互连技术,被广泛应用于网络设备、嵌入式系统、通信基站等领域。

随着信息技术的不断发展,RapidIO协议将在更多的领域得到应用,为高性能计算和通信系统的发展提供强大的支持。

显卡的物理接口标准PCIExpressvs AGP在当前科技发展的大背景下,电子设备不断更新换代,新的标准和接口也在不断出现。

对于计算机硬件而言,显卡作为重要组成部分,其物理接口的标准选择对性能和兼容性有着重要的影响。

在本文中,我们将重点讨论显卡的物理接口标准PCI Express与AGP之间的区别与优劣。

一、PCI Express(简称PCIe)PCI Express是一种高速串行总线技术,它被广泛应用于现代计算机的外部设备连接。

相较于传统的PCI总线,PCIe具有更高的带宽和更强的扩展性能,能够更好地满足多媒体、图形和数据处理等高性能应用的需求。

PCIe接口分为不同的版本,如PCIe 1.0、PCIe 2.0、PCIe3.0等,每个版本都有不同的带宽和技术参数。

PCIe的优势主要体现在以下几个方面:1.带宽升级:PCIe接口的带宽远远超过传统的PCI和AGP接口,具有更高的传输速率和更大的数据吞吐量。

这使得显卡能够更好地处理高分辨率的图像和复杂的三维模型,提供更流畅的游戏和视频体验。

2.热插拔支持:PCIe接口支持热插拔技术,用户可以在运行时随时插拔显卡,无需关闭计算机。

这在一定程度上方便了显卡的更换和升级,提高了计算机系统的灵活性。

3.扩展性强:PCIe接口采用了点对点连接的方式,每个设备都有独立的数据通道,不会受到其他设备的影响。

这种设计使得系统支持更多的设备,并且能够更好地利用系统资源,提高整体性能。

尽管PCIe接口在诸多方面具有优势,但也存在一些不足之处。

首先,由于PCIe接口需要更高的带宽和更复杂的传输协议,相较于传统接口而言,其成本更高。

其次,对于老旧的计算机系统,可能无法支持PCIe接口,需要进行相应的硬件升级。

二、AGP(加速图形端口)AGP是过去用于连接显卡和主板的一种标准接口,它在1996年问世并迅速流行起来。

与PCI接口相比,AGP接口专为图形处理而优化,具有更高的带宽和更低的延迟,能够更好地满足3D游戏和图形应用的需求。

串行RapidIO技术介绍串行RapidIO(RapidIO)是一种高性能、低延迟、可靠的互联技术,它被广泛应用于通信和计算领域。

RapidIO技术最初由RapidIO Trade Association(RSTA)开发,并于2002年首次发布。

它目前已成为通信和计算系统中最重要的互联技术之一RapidIO技术采用串行通信的方式进行数据传输。

相较于并行通信,串行通信具有更高的带宽和更低的功耗。

RapidIO技术的主要特点包括以下几个方面:1. 高带宽:RapidIO技术提供高达10Gbps的带宽,可以满足各种通信和计算应用的需求。

它支持点对点和多对一的拓扑结构,可以满足不同系统的互连需求。

2. 低延迟:RapidIO技术的延迟非常低,可以在纳秒级别内完成数据传输。

这使得它非常适合实时应用,如无线通信、视频处理和数据中心应用等。

3. 可靠性:RapidIO技术提供了一系列的错误检测和纠正机制,包括CRC(循环冗余检测)、重传机制和流量控制等。

这些机制可以确保数据在传输过程中的完整性和可靠性。

4. 灵活性:RapidIO技术支持多种拓扑结构,如星型、树型和多级互连等。

它还支持多种传输模式,包括消息传输、数据传输和共享内存等。

这使得它可以适应不同系统的需求,提供灵活的扩展性和性能。

5. 兼容性:RapidIO技术具有良好的兼容性,可以与其他互联技术进行集成。

它可以与PCI Express、Ethernet和InfiniBand等技术进行互操作,实现多种设备的互连。

除了以上特点,RapidIO技术还具有一些独特的优势。

首先,它提供了一种可编程的硬件和软件结构,可以简化系统的开发和维护。

其次,它采用了精简的协议,使得系统设计更加简单和高效。

第三,RapidIO技术具有低功耗的特点,可以降低整个系统的能耗。

RapidIO技术在通信和计算领域有着广泛的应用。

在通信领域,它被用于构建高性能数据传输和处理系统,如基站、网络路由器和交换机等。

以太网、PCIe和RapidIO的比较虽然在嵌入式系统中有许多连接元件的方法,但最主要的还是以太网、PCI Express和RapidIO 这三种高速串行标准。

所有这三种标准都使用相似的串行解串器(SerDes)技术,它们提供的吞吐量和时延性能都要超过宽的并行总线技术。

随着这些标准的不断发展,今后的趋势将是采用通用SerDes 技术。

这意味着这些协议提供的原始带宽不会有明显的差异。

相反,每种协议的用途将取决于如何使用带宽。

大多数设计人员都很熟悉基本的以太网协议特征。

以太网是一种'尽力而为'的数据包传送方式。

在以太网物理层上建立的软件协议,如TCP/IP,需要提供信息的可靠传输,因为基于以太网的系统一般在网络层执行流量控制,而不是在物理层。

一般基于以太网的系统带宽都要超配20%到70%。

因此以太网最适合高时延的设备间应用,或带宽要求较低的板上/板间应用。

相反,PCI Express(PCIe)针对板上互连的数据包可靠传送作了优化,这种场合的典型时延在毫秒数量级。

PCIe协议交换的是事务处理层数据包(TLP),如读和写,以及被称为数据链路层数据包(DLLP)的少量特殊链路信息。

DLLP用于链路管理功能,包括物理层的流量控制。

PCIe后向兼容传统的PCI和PCI-X器件,这些器件认为处理器位于总线层的顶部,因此PCIe具有能够充分利用与PCI相关的软件和硬件知识产权的优势。

正如后文要讨论的那样,传统PCI总线对交换式PCIe协议有很大的约束。

RapidIO技术则针对嵌入式系统作了优化,尤其是那些要求多处理单元合作的嵌入式系统。

与PCIe一样,RapidIO协议交换的是数据包和被称为控制符的少量特殊链路信息。

RapidIO兼具PCIe 和以太网的特性。

例如,RapidIO可以提供可靠和非可靠的数据包传送机制。

RapidIO也具有许多独特的功能,因此最适合板上、板间以及短距离(小于100米)的设备间应用。

高速串行总线RapidIO与PCI Express协议分析比较

梁小虎;王乐;张亚棣

【期刊名称】《航空计算技术》

【年(卷),期】2010(040)003

【摘要】随着新一代嵌入式系统对数据传输能力要求的提高,高速串行总线有着越来越广泛的应用,RapidIO和PCI Express(亦称PCIe)是常见的选择.通过对这两种

协议在整体工作机制及其特点、分层模型、拓扑结构、服务质量等方面的分析比较,为嵌入式系统设计中高速串行总线的选择提供参考.

【总页数】4页(P127-130)

【作者】梁小虎;王乐;张亚棣

【作者单位】中国航空计算技术研究所,陕西,西安,710068;中国航空计算技术研究所,陕西,西安,710068;中国航空计算技术研究所,陕西,西安,710068

【正文语种】中文

【中图分类】TP336

【相关文献】

1.RapidIO高速串行总线的信号完整性测试 [J], 侯红英

2.RapidIO高速串行总线的信号完整性仿真 [J], 侯红英

3.IDT推出业界首款用于RapidIOGen2协议转换网桥的PCI Express Gen2产品,用于x86处理器 [J],

4.关于总线接口PCI Express数据传输的协议分析 [J], 刘雨佳;张静;袁梦鑫

5.关于总线接口PCI Express数据传输的协议分析 [J], 刘雨佳;张静;袁梦鑫;

因版权原因,仅展示原文概要,查看原文内容请购买。

描述srio总线的特点Srio总线是一种高速串行总线,它的全称为Serial RapidIO。

Srio总线是用于连接多个处理器、FPGA、DSP等组件的高速互联技术。

下面将从以下几个方面来详细介绍Srio总线的特点。

一、高速性能Srio总线是一种高速串行通信总线,其数据传输速率可达到10Gbps 以上,比PCIe和HyperTransport等其他常见的互联技术更快。

这使得Srio在需要大量数据传输和处理的应用中表现出色。

例如,在视频处理和高性能计算等领域中,Srio可以提供卓越的性能。

二、低延迟另一个重要特点是低延迟。

由于Srio总线采用了流水线架构,因此它可以实现非常低的延迟。

这使得它在需要实时响应和快速数据传输的应用中表现出色。

例如,在无人驾驶汽车、医疗设备和军事应用等领域中,低延迟是至关重要的。

三、可靠性在工业控制和汽车电子等领域中,可靠性是至关重要的因素之一。

Srio总线通过采用差分信号传输技术来提高抗干扰能力,从而保证了数据传输的可靠性。

此外,Srio总线还支持多种错误检测和纠正机制,例如CRC校验和重传机制等。

四、灵活性Srio总线是一种非常灵活的互联技术。

它支持点对点、多播和广播通信模式,并且可以在不同的拓扑结构下工作。

此外,Srio总线还支持多种映射模式,例如内存映射、消息映射和I/O映射等。

这些特性使得Srio总线非常适合于复杂的系统集成应用。

五、可扩展性最后一个重要特点是可扩展性。

Srio总线可以通过添加更多的链路来扩展系统带宽和连接数量。

此外,Srio还支持端口聚合技术,从而可以将多个物理端口聚合为一个逻辑端口来增加系统带宽。

综上所述,Srio总线具有高速性能、低延迟、可靠性、灵活性和可扩展性等优秀特点,在许多应用中都表现出色。

PCI总线和PCIE总线的差异由于公司产品一直以X86架构为基础发展,在前几年中一直受到ASIC、NP 架构等厂商的攻击,但是随着技术的发展,在PCI-E架构出现后,效率的瓶颈得以突破。

最初PCI总线是32bit,33Mhz,这样带宽为133Mbps。

接着因为在服务器领域传输要求Intel把总线位数提高到64,这样又出现了2种PCI总线,分别为64bit/33Mhz和64bit/66Mhz,当然带宽分别翻倍了,为266Mbps和533Mbps,这个比较通常的名称应该是pci-64,但这好像是intel 自己做的,没有行业标准。

稍后一段时间,在民用领域,单独开发出了AGP,32bit,66Mhz,这样带宽为266Mbps,再加上后来AGP2.0的2X和4X标准,最高4X的带宽高达1Gbps,但是这个只是为显卡设计的。

同时服务器领域也没闲着,几家厂商联合制定了PCI-X,这个就是真正PCI 下一代的工业标准了,其实也没什么新意,就是64bit,133Mhz版本的PCI,那这样带宽就为1Gbps,后来PCI-X 2.0,3.0又分别提升频率,经历过266Mhz,533Mhz,甚至1GMhz,各位自己算带宽吧,我乘法学的不好,这个带宽可以说是非常足够的了,不过这个时候PCI也面临一些问题:一方面是频率提高造成的并行信号串扰,另一方面是共享式总线造成的资源争用,总之也就是说虽然规格上去了,但实际效果可能跑不了这些指标。

然后就是我们目前的明星pci-E了,这个标准应该是和pci-X同时出现的,但是由于当时用不到这么高带宽,并且不像pci-X一样兼容老pci板卡,所以一直没什么发展,直到最近民用领域显卡带宽又不够了,服务器领域对pci-X也觉得不爽了,pci-E才真正显出优势来,目前这个标准应该会替代agp和pci-X,成为民用和服务器两大领域的统一标准。

PCI-E标准的最大特点就是串行总线,和普通pci的区别类似于ide和sata 的区别,具体说起来就比较麻烦了,简单来看指标的话,频率为2.5Ghz(这个恐怖,串行的好处,同样因为串行,位宽就没意义了,但是据说是什么8bit/10bit 的传输),带宽 pci-E 1X单向传输250MBps,双向也就500了,同时pci-e的倍速最高可达16X,多少就自己乘吧,要注意的是pci-e不存在共享问题,也就是说挂在总线上的任何一个设备都会达到这个速度而不是所有设备带宽的总合。

PCIe总线基本概念,高速串行总线取代传统并行总线是一个大的趋势PCIe总线- - -PCIe总线的提出可以算是代表着传统并行总线向高速串行总线发展的时代的到来。

实际上,不仅是PCI总线到PCIe总线,高速串行总线取代传统并行总线是一个大的趋势。

如ATA到SATA,SCSI到USB等……不过,为了兼容之前的PCI总线设备,虽然PCIe是一种串行总线,无法再物理层上兼容PCI总线,但是在软件层上面却是兼容PCI总线的。

和很多的串行总线一样,PCIe采用了全双工的传输设计,即允许在同一时刻,同时进行发送和接收数据。

如下图所示,设备A和设备B之间通过双向的Link相连接,每个Link 支持1到32个通道(Lane)。

由于是串行总线,因此所有的数据(包括配置信息等)都是以数据包为单位进行发送的。

与绝大部分的高速连接一样,PCIe采用了差分对进行收发,以提高总线的性能。

一个PCIe Lane的例子如下图所示:除了差分总线,PCIe还引入了嵌入式时钟的技术(Embedded Clock),即发送端不再向接收端发送时钟,但是接收端可以通过8b/10b的编码从数据Lane中恢复出时钟。

一个简单的时钟恢复电路模型如下图所示:注:PCie Gen3以及之后的版本采用了128b/130b的编码方式。

PCIe相对于PCI总线的另一个大的优势是其的Scalable Performance,即可以根据应用的需要来调整PCIe设备的带宽。

如需要很高的带宽,则采用多个Lane(比如显卡);如果并不需要特别高的带宽,则只需要一个Lane就可以了(比如说网卡等)。

和PCI-X总线一样,由于非常高的传输速度,PCIe是一种点对点连接的总线,而不像PCI 那样的共享总线。

但是PCIe总线系统可以通过Switch连接多个PCIe设备,也可以通过PCIe桥连接传统的PCI和PCI-X设备。

一个简单的PCIe总线系统的拓扑结构图如下所示:注:这里的Switch实际上包含了多个类似于PCI总线中桥的概念。