封装库的命名规则

- 格式:pdf

- 大小:135.29 KB

- 文档页数:9

BGA封装命名规则1. 引言BGA封装是电子元器件的一种封装形式,用于将电子元器件与电路板相连接,并提供保护和支持。

为了有效管理和识别不同类型的BGA封装,制定了一套BGA封装命名规则。

本文将详细介绍BGA封装命名规则的内容和要求。

2. BGA封装命名规则的目的BGA封装命名规则的主要目的是提供一个统一的命名标准,方便工程师和制造商在设计、生产和组装过程中准确识别和选择不同类型的BGA封装。

通过符合统一的命名规则,可以减少误解和错误,并提高工作效率和产品质量。

3. BGA封装命名规则的要求BGA封装命名规则需要满足以下要求:•唯一性:每种BGA封装都应有一个唯一的名称,以避免混淆和歧义。

•简洁性:命名应简洁明了,便于记忆和使用。

•规范性:命名规则应符合通用的命名规范,遵循一定的语法和规则。

•可拓展性:命名规则应具有一定的可拓展性,以适应新的封装类型的出现。

•易读性:命名应具有良好的可读性,避免使用过于复杂和晦涩的命名方式。

4. BGA封装命名规则的具体内容BGA封装命名规则的具体内容如下:4.1 前缀BGA封装的命名通常以一个前缀开始,用于表示封装的类型或特性。

常见的前缀包括:•FBGA:表示普通的BGA封装。

•LBGA:表示低温BGA封装,适用于高温敏感的元器件。

•CBGA:表示高温BGA封装,适用于高温环境下的元器件。

•PBGA:表示可塑性BGA封装,适用于需要更好的抗冲击性能的元器件。

•TBGA:表示薄型BGA封装,适用于对高度有限制的应用场景。

4.2 封装尺寸BGA封装的尺寸通常以数字表示,表示封装的外部尺寸或球阵列的尺寸。

常见的尺寸表示方式包括:•Xmm x Ymm:表示封装的外部尺寸,其中X表示封装的宽度,Y表示封装的长度。

•X x Y:表示球阵列的尺寸,其中X表示球阵列的行数,Y表示球阵列的列数。

4.3 球阵列间距BGA封装的球阵列间距通常以数字表示,表示球阵列之间的间距或间隔。

常见的间距表示方式包括:•Xmil:表示球阵列之间的间距,其中X表示间距的大小,单位为mil。

PCB封装库命名规则资料PCB封装库命名1、集成电路(直插):用DIP-引脚数量+尾缀来表示双列直插封装尾缀有N和W两种,用来表示器件的体宽N为体窄的封装,体宽300mil,引脚间距2.54mm W为体宽的封装, 体宽600mil,引脚间距2.54mm如:DIP-16N表示的是体宽300mil,引脚间距2.54mm的16引脚窄体双列直插封装2 、集成电路(贴片)用SO-引脚数量+尾缀表示小外形贴片封装尾缀有N、M和W三种,用来表示器件的体宽N为体窄的封装,体宽150mil,引脚间距1.27mmM为介于N和W之间的封装,体宽208mil,引脚间距1.27mm W为体宽的封装, 体宽300mil,引脚间距1.27mm如:SO-16N表示的是体宽150mil,引脚间距1.27mm的16引脚的小外形贴片封装若SO前面跟M则表示为微形封装,体宽118mil,引脚间距0.65mm 3、电阻3.1 SMD贴片电阻命名方法为:封装+R如:1812R表示封装大小为1812的电阻封装 3.2 碳膜电阻命名方法为:R-封装如:R-AXIAL0.6表示焊盘间距为0.6英寸的电阻封装 3.3 水泥电阻命名方法为:R-型号如:R-SQP5W表示功率为5W的水泥电阻封装4、电容4.1 无极性电容和钽电容命名方法为:封装+C 如:6032C表示封装为6032的电容封装 4.2 SMT独石电容命名方法为:RAD+引脚间距如:RAD0.2表示的是引脚间距为200mil的SMT独石电容封装4.3 电解电容命名方法为:RB+引脚间距/外径如:RB.2/.4表示引脚间距为200mil, 外径为400mil的电解电容封装5、二极管整流器件命名方法按照元件实际封装,其中BAT54和1N4148封装为1N4148 6 、晶体管命名方法按照元件实际封装,其中SOT-23Q封装的加了Q以区别集成电路的SOT-23封装,另外几个场效应管为了调用元件不致出错用元件名作为封装名7、晶振HC-49S,HC-49U为表贴封装,AT26,AT38为圆柱封装,数字表规格尺寸如:AT26表示外径为2mm,长度为8mm的圆柱封装8、电感、变压器件电感封封装采用TDK公司封装9、光电器件9.1 贴片发光二极管命名方法为封装+D来表示如:0805D表示封装为0805的发光二极管9.2 直插发光二极管表示为LED-外径如LED-5表示外径为5mm的直插发光二极管9.3 数码管使用器件自有名称命名10、接插10.1 SIP+针脚数目+针脚间距来表示单排插针,引脚间距为两种:2mm,2.54mm如:SIP7-2.54表示针脚间距为2.54mm的7针脚单排插针10.2DIP+针脚数目+针脚间距来表示双排插针,引脚间距为两种:2mm,2.54mm10.3如:DIP10-2.54表示针脚间距为2.54mm的10针脚双排插针10.4 封装库元件命名一、多引脚集成电路芯片封装SOIC、SOP、TSOP在AD7.1元器件封装库中的命名含义。

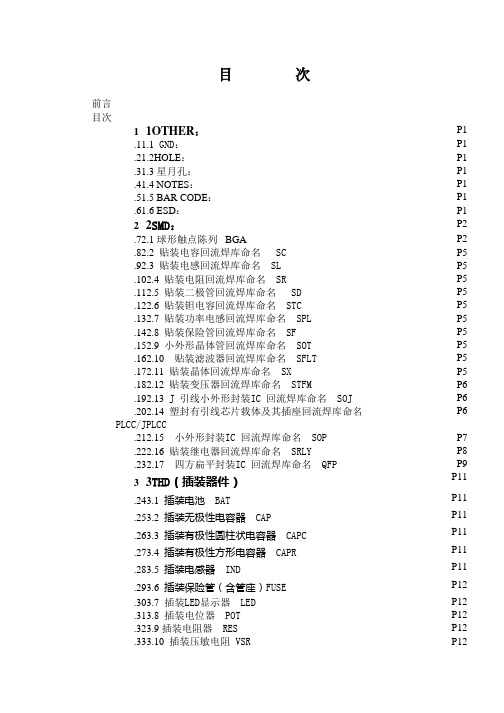

目次前言目次11OTHER:P1.11.1 GND:P1.21.2HOLE:P1.31.3 星月孔:P1.41.4 NOTES:P1.51.5 BAR CODE:P1.61.6 ESD:P122SMD:P2.72.1 球形触点陈列 BGA P2.82.2贴装电容回流焊库命名 SC P5.92.3贴装电感回流焊库命名 SL P5.102.4贴装电阻回流焊库命名 SR P5.112.5贴装二极管回流焊库命名 SD P5.122.6贴装钽电容回流焊库命名 STC P5.132.7贴装功率电感回流焊库命名 SPL P5.142.8贴装保险管回流焊库命名 SF P5.152.9小外形晶体管回流焊库命名 SOT P5.162.10贴装滤波器回流焊库命名 SFLT P5.172.11贴装晶体回流焊库命名 SX P5.182.12贴装变压器回流焊库命名 STFM P6.192.13 J 引线小外形封装IC 回流焊库命名 SOJ P6P6 .202.14塑封有引线芯片载体及其插座回流焊库命名PLCC/JPLCC.212.15小外形封装IC 回流焊库命名 SOP P7.222.16贴装继电器回流焊库命名 SRLY P8.232.17四方扁平封装IC 回流焊库命名 QFP P933THD(插装器件)P11.243.1插装电池 BAT P11.253.2插装无极性电容器 CAP P11.263.3插装有极性圆柱状电容器 CAPC P11.273.4插装有极性方形电容器 CAPR P11.283.5插装电感器 IND P11.293.6插装保险管(含管座)FUSE P12.303.7插装LED显示器 LED P12.313.8插装电位器 POT P12.323.9 插装电阻器 RES P12.333.10插装压敏电阻 VSR P12.343.11插装继电器 RLY P12 .353.12插装整流桥 RTF P12 .363.13插装传感器 SEN P12 .373.14插装散热器 HSK P13 .383.15插装滤波器 FLT P13 .393.16插装晶体 XTAL P13 .403.17插装振荡器 OSC P13 .413.18 插装变压器 TFM P14 .423.19双列直插封装(不含厚膜) DIP P14 .433.20屏蔽盒 SHIELD P15 .443.21风扇 FAN P15 .453.22插装光模块 LASER P16 .463.23插装电源模块 PW P20 .473.24单列直插封装(不含厚膜) SIP P29 44CONNECT P30 .484.1D型电缆连接器 DB P30 .494.2插针 HEAD P32 .504.3开关 DSW P32 .514.4扁平电缆连接器 IDC P33 .524.5数据通信口 MJ P34 .534.6压接型欧式连接器 PDIN P36 .544.7SIMM/DIMM插座 SIM/DIM P38 .554.8压接型 2mmFB连接器 PFB P39 .564.9压接型2mmHM连接器 PHM P40 .574.10压接型HS3连接器 PHS P42 .584.11压接型 HM-ZD连接器 PZD P42 .594.12电源连接器 PWC P42 .604.13贴装双边缘连接器 SED P43封装库图例PCB封装库图例按插件(THD)/贴片(SMD)/连接器(CONNECT)及其它杂类(OTHER)来分类1OTHER:包括各种安装孔、接地孔、定位光标、条码,以及PCB设计时使用的各类图框、 NOTE表格、各种规范的PCB加工文字说明(如阻抗控制、BGA塞孔说明等)、生产工艺提示(如ESD标记,波峰焊过板方向)1.1GND:1.1HOLE:HOLE*为非金属化孔,用于安装孔、定位孔。

Allegro PCB封装建库规则焊盘表贴焊盘方形焊盘命名规则:SPD焊盘长度X焊盘宽度∙钢网:钢网尺寸与焊盘尺寸相同∙阻焊:阻焊尺寸比焊盘尺寸大6mil圆形焊盘命名规则: SPD焊盘直径∙钢网:钢网尺寸与焊盘尺寸相同∙阻焊:阻焊尺寸比焊盘尺寸大6mil通孔金属化孔命名规则:PAD焊盘直径CIR钻孔直径(圆形焊盘)/PAD焊盘边长SQ钻孔直径(方形焊盘)参数计算:∙焊盘:分为表层焊盘和内层焊盘,表层焊盘尺寸参考各器件封装参数计算;内层焊盘比钻孔大尺寸10~20mil∙Antipad:各层Antipad至少比焊盘大10mil,具体尺寸大小应该考虑电气安全、传输阻抗、生产可行性等实际情况而定∙Thermal Relief :与Antipad取相同尺寸∙阻焊:阻焊尺寸比焊盘尺寸大6mil非金属化孔命名规则:MaDOTb(钻孔直径为a.bmm)/Tooling-Hole,(2004-4-15以前PAD为按照 FIaDOTb 命名),如果为整数直径,则为Ma即可。

参数计算:∙焊盘:设置焊盘比钻孔大1mil∙Antipad:各层Antipad至少比焊盘大10mil,具体尺寸大小应该考虑电气安全、生产可行性等实际情况而定∙Thermal Relief :与Antipad取相同尺寸∙阻焊:阻焊尺寸比钻孔尺寸大6mil过孔命名规则:VIA钻孔大小,比如VIA10 ,如果为堵孔,命名为VIA钻孔大小-F。

比如VIA12-F。

参数计算:封装库封装库的组成封装库主要由Package Symbol, Mechanical Symbol, Format Symbol, Shape Symbol ,Flash symbol五种.他们又可以分为可编辑(*.dra)与不可编辑(Package Symbol→ .psm , MechanicalSymbol→ .bsm , Format Symbol→ .osm , Shape Symbol→ .ssm,flash symbol →*.fsm)其中目前和我们联系比较大的是Package Symbol, Mechanical Symbol, Format Symbol,1.焊盘形状是指圆形、方形或者其他形状,尺寸是指长宽与半径等参数,类型指焊盘属于表贴或者通孔、盲孔等。

嘉立创封装命名规则

嘉立创封装命名规则是指嘉立创PCB封装库中用于描述元器件包装尺寸、引

脚布局和特性的命名规则。

这些规则旨在标准化封装命名,以便工程师能够快速而准确地选择和使用合适的封装。

根据嘉立创的命名规则,每个封装都有一个特定的编号。

这个编号由字母、数

字和其他特定字符组成。

其中,字母代表该封装类型的首字母缩写,数字代表封装的总引脚数,其他字符用于区分不同的封装变种。

例如,QFN-32表示一个具有32

个引脚的无引线封装。

除了封装编号外,嘉立创还规定了其他重要的命名规则。

其中之一是引脚布局

的描述。

嘉立创使用数字和字母来表示引脚的排列顺序和布局方式。

例如,DIP-8

表示一个具有8个引脚的双列直插式封装,其中引脚按照正常顺序编号。

此外,嘉立创还提供了一些特殊封装的命名规则。

例如,SOT-23是一种具有3个引脚的小型表面贴装封装,而BGA-256是一种具有256个引脚的球格阵列封装。

嘉立创封装命名规则的标准化有助于工程师在设计过程中准确选择合适的元器

件封装。

通过这些规则,工程师可以更轻松地识别和理解不同封装之间的区别,以便正确应用到电路设计中。

这样,嘉立创封装命名规则不仅提高了设计的准确性和效率,还促进了工程师之间的交流和合作。

PCB元件封装库命名规则简介1、集成电路(直插)用DIP-引脚数量+尾缀来表示双列直插封装尾缀有N和W两种,用来表示器件的体宽N为体窄的封装,体宽300mil,引脚间距2.54mmW为体宽的封装, 体宽600mil,引脚间距2.54mm如:DIP-16N表示的是体宽300mil,引脚间距2.54mm的16引脚窄体双列直插封装2 、集成电路(贴片)用SO-引脚数量+尾缀表示小外形贴片封装尾缀有N、M和W三种,用来表示器件的体宽N为体窄的封装,体宽150mil,引脚间距1.27mmM为介于N和W之间的封装,体宽208mil,引脚间距1.27mmW为体宽的封装, 体宽300mil,引脚间距1.27mm如:SO-16N表示的是体宽150mil,引脚间距1.27mm的16引脚的小外形贴片封装若SO前面跟M则表示为微形封装,体宽118mil,引脚间距0.65mm3、电阻SMD贴片电阻命名方法为:封装+R如:1812R表示封装大小为1812的电阻封装碳膜电阻命名方法为:R-封装如:表示焊盘间距为英寸的电阻封装水泥电阻命名方法为:R-型号如:R-SQP5W表示功率为5W的水泥电阻封装4、电容无极性电容和钽电容命名方法为:封装+C如:6032C表示封装为6032的电容封装SMT独石电容命名方法为:RAD+引脚间距如:表示的是引脚间距为200mil的SMT独石电容封装电解电容命名方法为:RB+引脚间距/外径如:.4表示引脚间距为200mil, 外径为400mil的电解电容封装5、二极管整流器件命名方法按照元件实际封装,其中BAT54和1N4148封装为1N41486 、晶体管命名方法按照元件实际封装,其中SOT-23Q封装的加了Q以区别集成电路的SOT-23封装,另外几个场效应管为了调用元件不致出错用元件名作为封装名7、晶振HC-49S,HC-49U为表贴封装,AT26,AT38为圆柱封装,数字表规格尺寸如:AT26表示外径为2mm,长度为8mm的圆柱封装8、电感、变压器件电感封封装采用TDK公司封装9、光电器件贴片发光二极管命名方法为封装+D来表示如:0805D表示封装为0805的发光二极管直插发光二极管表示为LED-外径如LED-5表示外径为5mm的直插发光二极管数码管使用器件自有名称命名10、接插SIP+针脚数目+针脚间距来表示单排插针,引脚间距为两种:2mm,2.54mm如:表示针脚间距为2.54mm的7针脚单排插针DIP+针脚数目+针脚间距来表示双排插针,引脚间距为两种:2mm,2.54mm如:表示针脚间距为2.54mm的10针脚双排插针其他接插件均按E3命名封装库元件命名一、多引脚集成电路芯片封装SOIC、SOP、TSOP在元器件封装库中的命名含义。

PCB元件封装库命名规则简介1、集成电路(直插)用DIP-引脚数量+尾缀来表示双列直插封装尾缀有N和W两种,用来表示器件的体宽N为体窄的封装,体宽300mil,引脚间距2.54mmW为体宽的封装, 体宽600mil,引脚间距2.54mm如:DIP-16N表示的是体宽300mil,引脚间距2.54mm的16引脚窄体双列直插封装2 、集成电路(贴片)用SO-引脚数量+尾缀表示小外形贴片封装尾缀有N、M和W三种,用来表示器件的体宽N为体窄的封装,体宽150mil,引脚间距1.27mmM为介于N和W之间的封装,体宽208mil,引脚间距1.27mmW为体宽的封装, 体宽300mil,引脚间距1.27mm如:SO-16N表示的是体宽150mil,引脚间距1.27mm的16引脚的小外形贴片封装若SO前面跟M则表示为微形封装,体宽118mil,引脚间距0.65mm3、电阻3.1 SMD贴片电阻命名方法为:封装+R如:1812R表示封装大小为1812的电阻封装3.2 碳膜电阻命名方法为:R-封装如:R-AXIAL0.6表示焊盘间距为0.6英寸的电阻封装3.3 水泥电阻命名方法为:R-型号如:R-SQP5W表示功率为5W的水泥电阻封装4、电容4.1 无极性电容和钽电容命名方法为:封装+C如:6032C表示封装为6032的电容封装4.2 SMT独石电容命名方法为:RAD+引脚间距如:RAD0.2表示的是引脚间距为200mil的SMT独石电容封装4.3 电解电容命名方法为:RB+引脚间距/外径如:RB.2/.4表示引脚间距为200mil, 外径为400mil的电解电容封装5、二极管整流器件命名方法按照元件实际封装,其中BAT54和1N4148封装为1N41486 、晶体管命名方法按照元件实际封装,其中SOT-23Q封装的加了Q以区别集成电路的SOT-23封装,另外几个场效应管为了调用元件不致出错用元件名作为封装名7、晶振HC-49S,HC-49U为表贴封装,AT26,AT38为圆柱封装,数字表规格尺寸如:AT26表示外径为2mm,长度为8mm的圆柱封装8、电感、变压器件电感封封装采用TDK公司封装9、光电器件9.1 贴片发光二极管命名方法为封装+D来表示如:0805D表示封装为0805的发光二极管9.2 直插发光二极管表示为LED-外径如LED-5表示外径为5mm的直插发光二极管9.3 数码管使用器件自有名称命名10、接插10.1 SIP+针脚数目+针脚间距来表示单排插针,引脚间距为两种:2mm,2.54mm如:SIP7-2.54表示针脚间距为2.54mm的7针脚单排插针10.2 DIP+针脚数目+针脚间距来表示双排插针,引脚间距为两种:2mm,2.54mm如:DIP10-2.54表示针脚间距为2.54mm的10针脚双排插针10.3 其他接插件均按E3命名封装库元件命名一、多引脚集成电路芯片封装SOIC、SOP、TSOP在AD7.1元器件封装库中的命名含义。

Allegro PCB 封装建库规则焊盘表贴焊盘方形焊盘命名规则:SP D旱盘长度X焊盘宽度钢网:钢网尺寸与焊盘尺寸相同阻焊:阻焊尺寸比焊盘尺寸大6mil 圆形焊盘命名规则:SPD焊盘直径钢网:钢网尺寸与焊盘尺寸相同阻焊:阻焊尺寸比焊盘尺寸大6mil通孔金属化孔命名规则:PAD旱盘直径CIR钻孔直径(圆形焊盘)/PAD焊盘边长SQ钻孔直径(方形焊盘)参数计算:焊盘:分为表层焊盘和内层焊盘,表层焊盘尺寸参考各器件封装参数计算;内层焊盘比钻孔大尺寸10〜20milAntipad :各层Antipad至少比焊盘大10mil,具体尺寸大小应该考虑电气安全、传输阻抗、生产可行性等实际情况而定Thermal Relief :与Antipad 取相同尺寸阻焊:阻焊尺寸比焊盘尺寸大6mil非金属化孔命名规则:MaDOT(钻孔直径为a.bmm /Tooling-Hole, (2004-4-15以前PAD为按照FlaDOTb命名),如果为整数直径,则为Ma即可。

参数计算:焊盘:设置焊盘比钻孔大1milAntipad :各层Antipad至少比焊盘大10mil,具体尺寸大小应该考虑电气安全、生产可行性等实际情况而定Thermal Relief :与Antipad 取相同尺寸阻焊:阻焊尺寸比钻孔尺寸大6mil过孔命名规则:VIA钻孔大小,比如VIA10 ,如果为堵孔,命名为VIA钻孔大小-F。

比如VIA12-F。

参数计算:封装库封装库的组成圭寸装库主要由Package Symbol, Mechanical Symbol, Format Symbol, Shape Symbol , Flash symbol五种.他们又可以分为可编辑(*dra)与不可编辑(Package Symbol —.psm , MechanicalSymbol —.bsm , Format Symbol —.osm , Shape Symbol —.ssm , flash symbol—*.fsm)其中目前和我们联系比较大的是Package Symbol, Mecha nical Symbol, Format Symbol Flash symbol 0下表为他们的简单介绍与比较。

sot封装命名规则SOT封装命名规则SOT(System-on-a-Chip Test)是一种用于集成电路测试的封装技术,它将测试模块集成到芯片封装中,可以在封装级别上对集成电路进行测试。

SOT封装命名规则是为了统一命名SOT封装中的测试模块,使其易于识别和管理。

本文将介绍SOT封装命名规则的几个重要方面。

一、命名规则的基本原则在制定SOT封装命名规则时,需要遵循以下几个基本原则:1. 清晰易懂:命名应简洁明了,能够准确表达测试模块的功能和作用。

2. 规范统一:命名规则应统一,以便于不同工程师之间的交流和协作。

3. 精炼简洁:命名应尽量简短,避免出现冗长的命名,提高命名的可读性和易理解性。

二、命名规则的要素在SOT封装的命名中,可以包含以下几个要素:1. 功能描述:对测试模块的功能进行简要描述,例如ADC (Analog-to-Digital Converter,模数转换器)。

2. 类型标识:标识测试模块的类型,例如DA(Digital Analyzer,数字分析仪)。

3. 版本号:标识测试模块的版本,以便于追踪和管理,例如V1.0。

4. 序号:标识同一类型的不同测试模块,以便于区分和管理,例如01、02等。

三、命名规则的示例根据上述要素,可以得到以下几个示例:1. ADC模块命名:ADC_DA_V1.0_01,表示版本为V1.0的ADC 模块,序号为01。

2. DA模块命名:DA_DA_V1.0_01,表示版本为V1.0的DA模块,序号为01。

3. GPIO模块命名:GPIO_DA_V1.0_01,表示版本为V1.0的GPIO 模块,序号为01。

四、命名规则的应用在实际应用中,SOT封装命名规则可以应用于以下几个方面:1. 设计和开发:在SOT封装的设计和开发过程中,可以根据命名规则对测试模块进行命名,以方便标识和管理。

2. 文档编写:在编写相关文档时,可以使用SOT封装命名规则对测试模块进行命名,以便于读者理解和查找相关信息。

PCB元件封装库命名规则简介1、集成电路(直插)用DIP-引脚数量+尾缀来表示双列直插封装尾缀有N和W两种,用来表示器件的体宽N为体窄的封装,体宽300mil,引脚间距2.54mmW为体宽的封装,体宽600mil,引脚间距2.54mm如:DIP-16N表示的是体宽300mil,引脚间距2.54mm的16引脚窄体双列直插封装2、集成电路(贴片)用SO-引脚数量+尾缀表示小外形贴片封装尾缀有N、M和W三种,用来表示器件的体宽N为体窄的封装,体宽150mil,引脚间距1.27mmM为介于N和W之间的封装,体宽208mil,引脚间距1.27mm W为体宽的封装,体宽300mil,引脚间距1.27mm如:SO-16N表示的是体宽150mil,引脚间距1.27mm的16引脚的小外形贴片封装若SO前面跟M则表示为微形封装,体宽118mil,引脚间距0.65mm 3、电阻3.1SMD贴片电阻命名方法为:封装+R如:1812R表示封装大小为1812的电阻封装 3.2碳膜电阻命名方法为:R-封装如:R-AXIAL0.6表示焊盘间距为0.6英寸的电阻封装 3.3水泥电阻命名方法为:R-型号如:R-SQP5W表示功率为5W的水泥电阻封装4、电容4.1无极性电容和钽电容命名方法为:封装+C如:6032C表示封装为6032的电容封装 4.2SMT独石电容命名方法为:RAD+引脚间距如:RAD0.2表示的是引脚间距为200mil的SMT独石电容封装 4.3电解电容命名方法为:RB+引脚间距/外径如:RB.2/.4表示引脚间距为200mil,外径为400mil的电解电容封装5、二极管整流器件命名方法按照元件实际封装,其中BAT54和1N4148封装为1N41486、晶体管命名方法按照元件实际封装,其中SOT-23Q封装的加了Q以区别集成电路的SOT-23封装,另外几个场效应管为了调用元件不致出错用元件名作为封装名7、晶振HC-49S,HC-49U为表贴封装,AT26,AT38为圆柱封装,数字表规格尺寸如:AT26表示外径为2mm,长度为8mm的圆柱封装8、电感、变压器件电感封封装采用TDK公司封装9、光电器件9.1贴片发光二极管命名方法为封装+D来表示如:0805D表示封装为0805的发光二极管9.2直插发光二极管表示为LED-外径如LED-5表示外径为5mm的直插发光二极管9.3数码管使用器件自有名称命名10、接插10.1SIP+针脚数目+针脚间距来表示单排插针,引脚间距为两种:2mm,2.54mm如:SIP7-2.54表示针脚间距为2.54mm的7针脚单排插针10.2DIP+针脚数目+针脚间距来表示双排插针,引脚间距为两种:2mm,2.54mm如:DIP10-2.54表示针脚间距为2.54mm的10针脚双排插针10.3其他接插件均按E3命名封装库元件命名一、多引脚集成电路芯片封装SOIC、SOP、TSOP在AD7.1元器件封装库中的命名含义。

例如:SOIC库分为L、M、N三种。

L、M、N--代表芯片去除引脚后的片身宽度,即芯片两相对引脚焊盘的最小宽度。

其中L 宽度最大,N次之,M最小。

--这里选择名称为SOIC_127_M的一组封装为例,选择改组中名为SOIC127P600-8M 的封装。

其中,127P--代表同一排相邻引脚间距为1.27mm;600--代表芯片两相对引脚焊盘的最大宽度为6.00mm;-8--代表芯片共有8只引脚。

二、封装库中,名为DPDT的封装含义为(Double Pole Double Throw),同理就有了封装名称SPST、DPST、SPDT;三、让软件中作为背景的电路板外形与实际机械1层定义的尺寸(无论方圆)等大的办法。

首先,在PCB Board Wizard中按照实际尺寸初步Custom一块板子(一定要合理设置keepout间距,一般为2mm)。

然后在Edit->Origin中为电路板设置坐标原点,将生成的电路板尺寸设置在机械1层,如果不喜欢板子四周的直角怕伤手,可以将四脚重新定义为弧形并标注尺寸。

选定所有机械1层上电路的尺寸约束对象,然后选择Design->Board Shape->Define from select,即可完成背景电路板外形的设置。

四、关于Design->Rules的一些设置技巧。

1、如果设计中要求敷铜层(及内电层)与焊盘(无论表贴还是通孔)的连接方式采用热缓冲方式连接,而敷铜层(及内电层)与过孔则采用直接连接方式的规则设置方法:敷铜层设置方法:在规则中的Plane项目中找到Polygon Connect style项目,新建子项名为:PolygonConnect_Pads,设置where the first object matches为:(InPADClass('All Pads')),where the second object matches为:All;并选择连接类型为45度4瓣连接。

又新建子项名为:PolygonConnect_Vias,设置where the first object matches为:All,where the second object matches为:All;并选择连接类型为直接连接方式。

在侧边栏中选中其中任何一个子项,点击坐下方Priorities按钮,将PolygonConnect_Pads子项的优先级设置为最高级别然后关闭。

内电层设置方法:同样,在Power Plane Connect Style项目中,新建子项名为:PlaneConnect_Pads,设置where the first object matches为:(InPadClass('All Pads'));连接类型为4瓣连接。

又新建子项名为:PlaneConnect_Vias,设置where the first object matches 为:All;连接类型为直接连接方式。

在侧边栏中选中其中任何一个子项,点击坐下方Priorities按钮,将PolygonConnect_Pads子项的优先级设置为最高级别然后关闭。

2、敷铜层(敷铜层为铜皮)与走线过孔以及焊盘的间距设置方法:在Electrical项目中新建子项名为:Clearance_Polygon,设置where the first object matches为:(IsRegion),where the second object matches 为:All;并设置间距一般为20mil以上,30mil合适。

3、敷铜层(敷铜层为网格敷铜方式)与走线过孔以及焊盘的间距设置方法:需要将走线间距由原来的9、10mil设置为需要敷铜的间距30mil,然后敷网格铜。

待敷铜结束后,将走线间距改回为原来的间距,系统就不会报错了。

五、带有敷铜层和内电层的四层以上板,为了显示电路板层数,需要加入层标,在每一层上用数字标识,将层标处对准明亮处可以看到每一层的标识。

由于层标处需要透光,所以该区域不能有任何敷铜以及内电层通过。

所以,首先在keepout 层画出一个矩形框,阻隔上下两个敷铜层通过;然后用Place->Polygon Pour Cutout命令分别在每一个内电层上切除一个矩形框区域,这些区域要完全重叠,用于透光;最后在每一层上放置相应的层标字符。

六、在发热量较大的芯片下敷网格铜,而其他区域敷铜皮方法:还是利用keepout线在发热芯片对应区域的禁止布线层(keepout层)圈出芯片的外形来;然后开始整板敷铜皮,看到的结果是,所有发热芯片位置的敷铜没有了。

注意:还要将芯片底部的所有接地过孔设置为NoNet,不让它接地!(以免敷铜皮时,芯片内部没有靠近keepout线的区域也被敷上了铜皮。

)接下来是删除先前在keepout层的画线;下面就好办了,同样还是敷铜,这回是在发热芯片区域敷网格铜,不必担心,可以圈出一个较大的敷铜区域以免芯片区域敷铜不完整,即便是占用了被敷了铜皮的位置,敷铜结果还是铜皮。

PCB封装焊盘大小与引脚关系在PCB中画元器件封装时,经常遇到焊盘的大小尺寸不好把握的问题,因为我们查阅的资料给出的是元器件本身的大小,如引脚宽度,间距等,但是在PCB板上相应的焊盘大小应该比引脚的尺寸要稍大,否则焊接的可靠性将不能保证。

下面将主要讲述焊盘尺寸的规范问题。

为了确保贴片元件(SMT)焊接质量,在设计SMT印制板时,除印制板应留出3mm-8mm 的工艺边外,应按有关规范设计好各种元器件的焊盘图形和尺寸,布排好元器件的位向和相邻元器件之间的间距等以外,我们认为还应特别注意以下几点:(1)印制板上,凡位于阻焊膜下面的导电图形(如互连线、接地线、互导孔盘等)和所需留用的铜箔之处,均应为裸铜箔。

即绝不允许涂镀熔点低于焊接温度的金属涂层,如锡铅合金等,以避免引发位于涂镀层处的阻焊膜破裂或起皱,以保证PCB板的焊接以及外观质量。

(2)查选或调用焊盘图形尺寸资料时,应与自己所选用的元器件的封装外形、焊端、引脚等与焊接有关的尺寸相匹配。

必须克服不加分析或对照就随意抄用或调用所见到的资料J或软件库中焊盘图形尺寸的不良习惯。

设计、查选或调用焊盘图形尺寸时,还应分清自己所选的元器件,其代码(如片状电阻、电容)和与焊接有关的尺寸(如SOIC,QFP等)。

(3)表面贴装元器件的焊接可靠性,主要取决于焊盘的长度而不是宽度。

(a)如图1所示,焊盘的长度B等于焊端(或引脚)的长度T,加上焊端(或引脚)内侧(焊盘)的延伸长度b1,再加上焊端(或引脚)外侧(焊盘)的延伸长度b2,即B=T b1b2。

其中b1的长度(约为0.05mm—0.6mm),不仅应有利于焊料熔融时能形成良好的弯月形轮廓的焊点,还得避免焊料产生桥接现象及兼顾元器件的贴装偏差为宜;b2的长度(约为0.25mm—1.5mm),主要以保证能形成最佳的弯月形轮廓的焊点为宜(对于SOIC、QFP等器件还应兼顾其焊盘抗剥离的能力)。

(b)焊盘的宽度应等于或稍大(或稍小)于焊端(或引脚)的宽度。

常见贴装元器件焊盘设计图解,如图2所示。

焊盘长度B=T b1b2焊盘内侧间距G=L-2T-2b1焊盘宽度A=W K焊盘外侧间距D=G2B。

式中:L–元件长度(或器件引脚外侧之间的距离);W–元件宽度(或器件引脚宽度);H–元件厚度(或器件引脚厚度);b1–焊端(或引脚)内侧(焊盘)延伸长度;b2–焊端(或引脚)外侧(焊盘)延伸长度;K–焊盘宽度修正量。

常用元器件焊盘延伸长度的典型值:对于矩形片状电阻、电容:b1=0.05mm,0.10mm,0.15mm,0.20mm,0.30mm其中之一,元件长度越短者,所取的值应越小。