基于FPGA的串行通信接口设计

- 格式:ppt

- 大小:454.50 KB

- 文档页数:11

基于FPGA的SDIO通信接口的设计实现刘雨沁;郭元兴;刘继平【摘要】In order to meet the requirements of SDIO security module batch testing, it is necessary to make generalized and modularized design of SDIO interface. The SDIO interface, for its fast transmission speed, good compatibility and other advantages, is widely used in mobile handheld devices. The common SDIO interface is implemented by the special interface chip, but there are few chips with special protocol and multi-channel parallel processing. Therefore, the SDIO interface is realized by using VerilogHDL language and in combination of finite state machine with top-down modular design. Specifically, the main function is implemented in FPGA, and this makes the whole design flexible, rich and transplantable. The experimental results indicate that the designed SDIO interface is stable and reliable, and provides a solution to multi-channel parallel detection of SDIO security module.%为满足SDIO安全模块的批量检测需求,需对SDIO接口进行通用化、模块化设计.SDIO接口以其传输速度快、兼容性好等优点被广泛应用于移动手持设备中.常用的SDIO接口由专用接口芯片实现,但具备专用协议和多通道并行处理的芯片较少.因此,采用VerilogHDL语言,结合有限状态机和自顶向下的模块化设计方法来实现SDIO接口.具体地,将主体功能在FPGA中实现,整体设计灵活丰富、移植性强.经实验验证,设计实现的SDIO接口功能稳定、可靠,可为SDIO安全模块多通道并行检测提供解决方案.【期刊名称】《通信技术》【年(卷),期】2017(050)011【总页数】5页(P2632-2636)【关键词】SDIO;FPGA;VerilogHDL;状态机;多通道【作者】刘雨沁;郭元兴;刘继平【作者单位】中国电子科技集团公司第三十研究所,四川成都 610041;中国电子科技集团公司第三十研究所,四川成都 610041;中国电子科技集团公司第三十研究所,四川成都 610041【正文语种】中文【中图分类】TP336SDIO安全模块内部集成安全SOC芯片,具备高性能、低功耗、高安全性等特点。

fpga常用接口协议FPGA常用接口协议随着科技的不断发展,FPGA(现场可编程门阵列)在数字电路设计中的应用越来越广泛。

FPGA常用接口协议是指在FPGA与其他设备之间进行数据交换时所使用的通信协议。

本文将介绍几种常见的FPGA接口协议,包括SPI、I2C、UART和PCIe。

一、SPI(串行外设接口)协议SPI是一种串行通信协议,可以实现FPGA与外设之间的数据传输。

SPI接口由四条线组成,分别是时钟信号(SCLK)、主设备输出从设备输入(MOSI)、主设备输入从设备输出(MISO)和片选信号(CS)。

SPI协议采用主从模式,主设备通过控制时钟信号和片选信号来与从设备进行通信。

SPI接口的优点是通信速度快,但只能实现点对点的通信。

二、I2C(串行总线接口)协议I2C是一种串行通信协议,可以实现FPGA与多个外设之间的数据传输。

I2C接口由两条线组成,分别是时钟信号(SCL)和数据信号(SDA)。

I2C协议采用主从模式,主设备通过控制时钟信号和数据信号来与从设备进行通信。

I2C接口的优点是可以同时连接多个从设备,但通信速度相对较慢。

三、UART(通用异步收发传输)协议UART是一种异步串行通信协议,可以实现FPGA与其他设备之间的数据传输。

UART接口由两条线组成,分别是发送线(TX)和接收线(RX)。

UART协议采用点对点通信,通过发送和接收线来进行数据传输。

UART接口的优点是通信简单易用,但通信速度相对较慢。

四、PCIe(外部总线接口)协议PCIe是一种高速串行总线接口协议,可以实现FPGA与计算机之间的数据传输。

PCIe接口由多条差分信号线组成,包括数据传输线(TX和RX)和控制信号线(CLK、RESET等)。

PCIe协议采用主从模式,通过数据传输线和控制信号线来实现高速数据传输。

PCIe接口的优点是通信速度快,但连接和配置相对复杂。

总结:本文介绍了几种常见的FPGA常用接口协议,包括SPI、I2C、UART 和PCIe。

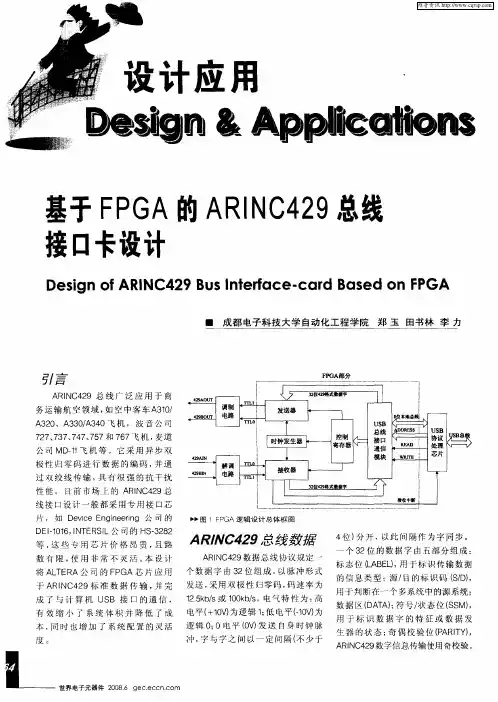

基于国产FPGA的ARINC429总线接口的设计

尹嘉乐;彭良福

【期刊名称】《电脑与信息技术》

【年(卷),期】2024(32)1

【摘要】依据ARINC429总线的传输规范,提出了ARINC429总线接口的一种设

计方案。

设计采用国产FPGA芯片SL2-25E,详细描述了结构设计与软件开发,以及集成在FPGA内部的发送、接收等模块的功能。

仿真测试结果表明,基于国产FPGA的ARINC429总线接口能够完成数据无误收发,并且符合总线规范的要求,结构简单,易于扩展,对其他串行总线数据通信以及航空电子系统的发展具有借鉴意义。

【总页数】4页(P82-85)

【作者】尹嘉乐;彭良福

【作者单位】西南民族大学

【正文语种】中文

【中图分类】TP334.7;V243.1

【相关文献】

1.基于DSP与FPGA的ARINC429总线接口卡设计

2.基于CPU和FPGA的ARINC429总线接口板设计

3.基于FPGA的ARINC429总线接口卡设计

4.基于FPGA IP核的AFDX与ARINC429总线转换接口设计

5.基于FPGA的ARINC429总线嵌入式接口板的设计与实现

因版权原因,仅展示原文概要,查看原文内容请购买。

fpga片间gth通信

FPGA片间GTH通信是指在FPGA芯片之间使用GTH(Gigabit Transceiver)进行通信的过程。

GTH是Xilinx FPGA系列中的一种高速串行通信接口,可以用于实现高速数据传输和通信。

在FPGA片间通信中,GTH通常被用于实现高速串行通信接口,以便在不同FPGA芯片之间传输大量数据和实现高速通信。

从硬件角度来看,FPGA片间GTH通信涉及到了GTH接口的配置和连接。

在配置方面,需要对GTH接口进行正确的初始化和设置,包括设置传输速率、协议、时序等参数,以确保通信的稳定和可靠性。

在连接方面,需要设计合适的物理连接方式和布线方案,以确保GTH通信能够在FPGA芯片之间进行正常的数据传输。

从软件角度来看,FPGA片间GTH通信涉及到了通信协议的设计和实现。

在设计方面,需要确定通信协议的格式、数据帧结构、校验机制等,以确保数据能够在FPGA芯片之间正确地传输和解析。

在实现方面,需要编写相应的驱动程序或者使用现有的通信协议栈,以便在FPGA芯片之间实现数据的发送和接收。

此外,还需要考虑时序同步、时钟分配、数据完整性等问题,

以确保FPGA片间GTH通信的稳定性和可靠性。

在实际应用中,还需要考虑功耗、布局布线、信号完整性等方面的问题,以确保FPGA片间GTH通信能够在实际的系统中正常工作。

总的来说,FPGA片间GTH通信涉及到硬件配置、连接设计、通信协议设计和实现等多个方面,需要综合考虑硬件和软件的因素,以确保通信的稳定和可靠。

这需要工程师具备扎实的硬件设计和通信协议设计能力,以及丰富的实践经验。

基于FPGA的以太网MII接口扩展设计与实现电脑知识2009-01-10 11:09:49 阅读80 评论0 字号:大中小引言传统以PC为中心的互联网应用现已开始转向以嵌入式设备为中心。

据网络专家预测,将来在互联网上传输的信息中,有70%来自小型嵌入式系统,因此,对嵌入式系统接入因特网的研究是有必要的。

目前有两种方法可以实现单片机系统接入因特网:一种方法是利用NIC (网络控制/网卡)实现网络接口,由单片机来提供所需的网络协议;另外一种方法是利用具有网络协议栈结构的芯片和PHY(物理层的接收器)来实现网络接口,主控制器只负责往协议栈结构芯片的某个寄存器里放上适当的数据。

与此同时,用FPGA实现单片机系统接入因特网的方法也日益受到人们的重视。

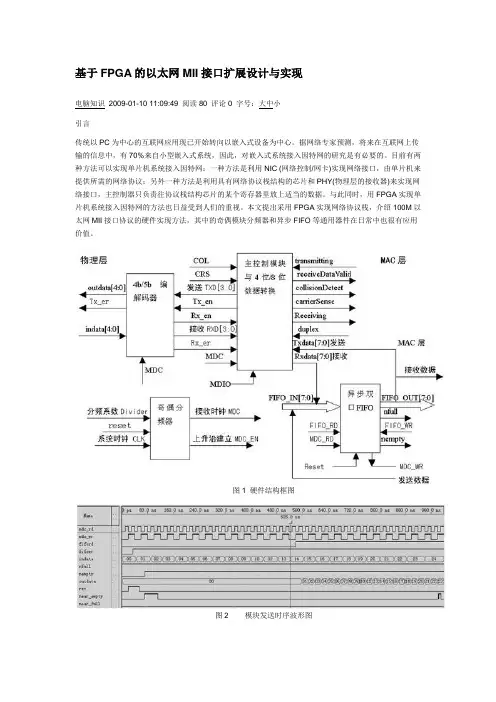

本文提出采用FPGA实现网络协议栈,介绍100M以太网MII接口协议的硬件实现方法,其中的奇偶模块分频器和异步FIFO等通用器件在日常中也很有应用价值。

图1 硬件结构框图图2 模块发送时序波形图以太网MII接口协议IEEE802协议标准系列中,数据链路层包括LLC (逻辑链路控制)子层和MAC (媒体访问控制)子层。

其中MAC单独作为一个子层,完成数据帧的封装、解封、发送和接收功能。

物理层PHY的结构随着传输速率的不同而有一定差异,在100M和1000M以太网中,依次为PCS子层、PMA子层和PMD子层。

MII接口是连接数据链路层和物理层的接口,因为本设计中以太网速率采用100Mb/s,所以MII接口实际连接的是MAC子层和PCS子层。

根据协议,要求MII接口具有的功能有:数据和帧分隔符的读写时钟同步,提供独立的读写数据通道,为MAC层和PCS层提供相应的管理信号,以及支持全双工模式。

扩展MII接口功能及其FPGA实现由于100M以太网的物理层采用4b/5b编码,为了扩展MII接口的功能,要求其能够实现直接物理层5位数据和MAC层8位数据的发送接收传输转换。

即把从MAC子层用于发送的数据和从PHY用于接收的数据存入数据缓冲FIFO,同时要求MII接口将从PHY传来的信号COL、CRS转为信号Carrier和Collision,并提供给MAC子层用于载波监听和冲突检测,以及发送和接收时的时钟、使能、错误位信号的传送。

基于FPGA的SPI总线接口的实现作者:王珏文,金伟信,蔡一兵,颜莉萍来源:《现代电子技术》2010年第14期摘要:在现代EDA外围电子器件的接口中存在多种标准,已知的一些接口协议存在速度慢、协议复杂等问题。

SPI总线是能够克服上述缺点的一种外围串行总线,其能很好地满足要求。

通过使用Lattice公司的FPGA芯片以及工程开发软件,特别是在线逻辑分析仪这一先进的EDA工具,实现了基于FPGA的SPI接口的连接。

将FPGA编程的灵活性和SPI总线的易用性结合,实现了FLASH的存取功能。

同时也为同类型接口的芯片应用提供了一个原型,为进一步的工程设计提供了支持。

关键词: FPGA; FLASH; SPI; 在线逻辑分析中图分类号:TN710; TP336 文献标识码:A文章编号:1004-373X(2010)14-0102-03Implementation of SPI Bus Interface Based on FPGAWANG Jue-- Yi--(1. PLA University of Science and Technology, Nanjing 210007, China; 2. CEDSEC, Beijing 100141, China)Abstract: There are many standards in the scope of interfaces for peripheral electronic devices in the field of modern EDA. Some known interface protocols perform an unsatisfactory role with their low speed or complexity. SPI bus is a popular peripheral serial bus which can satisfy the practical demand. By using Lattice FPGA and its EDA software, especially the on-line logic analyzer which is an advanced EDA tool, the connection of SPI bus interface based on FPGA was implemented. Theand the adaptability of SPI bus. At the same time, it can be taken as a prototype, which can be used in a further profound exploitation in EDA projection.Keywords: FPGA; FLASH; SPI; on-line logic analysis0 引言串行接口已成为当前传输接口的发展趋势,原因在于串行的高速率传输性能和较简单的线路连接。

2022年5月第20期May 2022No.20教育教学论坛EDUCATION AND TEACHING FORUM基于FPGA的通信技术综合实验课程教学模式设计张延彬,高向川(郑州大学 信息工程学院,河南 郑州 450001)[摘 要] 通信技术综合实验是通信工程专业必修的一门综合性实验课程,对提升学生的工程实践能力和解决复杂工程问题能力具有重要意义。

以通信技术综合实验课程的培养目标为依据,设计了由学生团队半自主命题并完成实验任务的教学模式,采用软件无线电硬件实验平台,设计并验证基于FPGA的编码、调制、解调、解码和同步等通信收发电路。

整个课程教学贯彻以学生为中心的教育理念,注重过程管理,全方位多角度进行考核,对学生和老师均提出了较高要求,确保了课程的含金量。

[关键词] FPGA;以学生为中心;过程管理;教学模式[基金项目] 2019年度河南省高等教育教学改革研究与实践项目“新工科牵引下信息类专业‘一体多维’式工程教育模式研究与实践”(2019SJGLX034)[作者简介] 张延彬(1980—),男,河南南阳人,博士,郑州大学信息工程学院讲师,主要从事高速实时信号处理、嵌入式系统等研究;高向川(1981—),男,河南南阳人,博士,郑州大学信息工程学院教授,主要从事无线通信与信号处理等研究。

[中图分类号] G642.41 [文献标识码] A [文章编号] 1674-9324(2022)20-0137-04 [收稿日期] 2021-07-19引言在通信工程专业的培养方案中,通信技术综合实验是一门必修的综合性实验课程,该课程要求学生综合运用数字电路、信号处理、通信原理、电磁场、计算机和系统建模仿真等工程基础知识和专业理论知识,根据特定的功能和技术指标要求,设计一个完整的通信收发电路。

该课程的目标是通过较为系统的工程实践训练,理论与实践相结合,培养学生解决复杂工程问题的能力,提高学生进行工程设计、开发和测试验证的能力,增强学生发现问题、分析问题和解决问题的能力,为毕业后从事专业工作打下坚实基础[1]。

毕业设计(论文)题目名称:基于FPGA的双口RAM在双CPU通信中的应用及设计学院:电气信息工程学院专业/班级:电子信息工程摘要基于现代通信系统的要求,本次设计详细研究了利用双端口RAM实现高速并行双CPU之间的数据通信,指出了设计中需要解决的几个关键性问题,并给出了相应的解决方案。

随着电子技术的迅速发展,大量的高速数据采集和现代工业测控系统和在线测试仪器的功能和性能提出了更高的要求,双CPU并行工作双单片机系统广泛应用。

为了使两个单片机可以快捷有效地交换信息,充分利用系统资源,共享内存实现通过使用双端口RAM现在更受欢迎的方法。

大容量高速FPGA器件具有较高的集成,体积小,灵活配置和实验风险小的优势。

在复杂数字系统越来越广泛的应用,数字电路设计采用1块FPGA设备存储设备和一些电气接口匹配电路解决方案已经成为一个主流的选择。

使用FPGA实现函数的双端口RAM是一个很好的方法来解决这个问题的并行性和速度,以及其灵活的可配置特性使基于FPGA双端口RAM容易修改测试和系统升级可以降低设计成本,缩短开发周期。

在嵌入式多CPU系统中,CPU之间的通信可以使用串行、并行和系统总线方式的双端口RAM,等等。

在三种沟通方式存在的共同传输速度慢的特点,在大量数据的情况下可能会导致数据处理时间的延长,实时性能,甚至出现数据拥堵现象。

所以与方法之间的双端口RAM数据交换系统是一个简单而有效的方法。

关键词: FPGA;双端口RAM;双CPU;并行数据通信AbstractBased on the demand of modern communication system, the design was studied by using dual port RAM to implement the parallel data communication between the double CPU, pointed out the need to be solved in the design of several key problems, and gives the corresponding solutions.With the rapid development of electronic technology, a large number of high-speed data acquisition and modern industry measurement and control system and the function of the online test instrument and performance put forward higher request, double CPU parallel work double single chip microcomputer system is widely used. Is becoming more and more widely used in complex number system, the digital circuit design of one piece of FPGA device storage equipment and some of the electrical interface matching circuit solution has become a mainstream choice. Using FPGA to realize function of dual port RAM is a very good method to solve the problem of parallelism and speed, and its flexible configurable properties based on FPGA dual port RAM is easier to modify test and system upgrade can reduce the design cost, shorten the development cycle.Key words: FPGA; Dual port RAM; Double CPU; The parallel data communication目录摘要 (I)Abstract (II)1绪论 (1)1.1研究发展趋势 (1)1.2研究现状 (1)1.3研究重点方向 (2)2 RAM与CPU之间通信的基本原理 (3)2.1 双口RAM 结构及工作原理 (3)2.1.1双口RAM的结构 (3)图2,1双口RAM存储结构图 (3)2.1.2双口RAM工作原理 (4)2.2 双CPU工作原理及应用 (5)2.2.1双CPU的结构 (5)2.2.2双CPU的工作原理 (6)2.2.3基于双CPU通信的设计及应用 (6)2.3 FPGA的基本结构及工作原理 (7)2.4本章小结 (8)3 双口RAM在双CPU通信中的设计及仿真 (9)3.1双端口RAM并行通信设计 (9)3.2系统关键性问题的解决 (10)3.2.1 系统故障冗余设计 (10)3.2.2 交叉事物处理设计 (10)3.3双CPU系统设计及关键技术问题 (11)3.3.1确保双CPU的协同可靠 (11)3.3.2合理设计交叉事物的实时处理软硬件 (11)3.3.3 双口RAM存储空间的组成及访问 (11)3.3.4可靠性的保障 (12)3.4仿真结果及性能分析 (13)3.5本章小结 (14)4总结及展望 (15)4.1课题研究所面临的问题 (15)4.2未来研究方向 (15)参考文献 (16)致谢 (17)附录 (18)1绪论1.1研究发展趋势随着现代智能系统的升级和更新,在双向通信和信息传输过程中,对信息量的增加和实时性的要求更加精准高效。

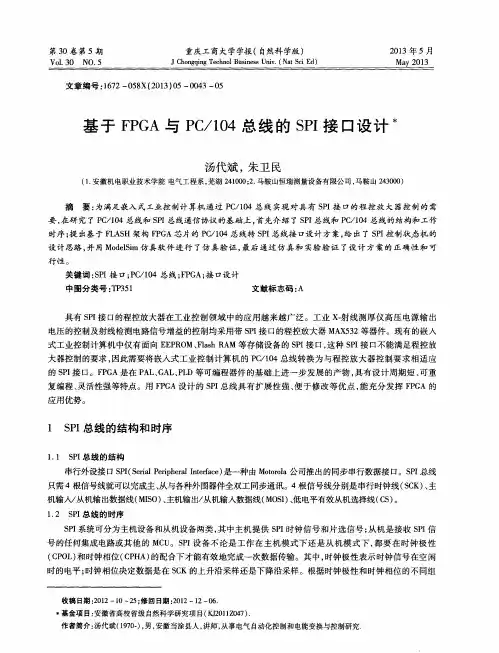

摘要控制器局域网CAN(ControllerAreaNetwork)是80年代初BOSCH公司为解决现代汽车中众多控制单元、测试仪器之间的实时数据交换而开发的一种串行通信协议。

CAN总线仅详细定义了物理层和数据链路层,更多复杂的应用需要应用层协议来解决。

因此,更多关于CAN的高层协议应运而生,CANopen是由CiA(cANinAutomation)组织开发的,它主要采用对象字典结构,将CAN网络中通讯数据的组建和传输进行标准化。

CANopen作为一种开放的CAN高层协议,在工业控制和自动化领域获得了广泛的应用。

本文的研究目的是实现一个可配置、高时效性的基于FPGA技术的CANopen从站。

本文提出了一种通用CANopen从站的设计方法。

CANopen从站的硬件设计以EPlS40F780C5FPGA器件为核心,利用本文设计的CAN控制器模块连接CTMl051A通用CAN隔离收发器构成了CAN总线通信接口电路。

CAN控制器的设计通过对CAN总线协议的分析,以及根据目前市场上主流CAN控制器芯片的功能,确定了本文的CAN控制器模块的结构,将其分为三个大模块,包括寄存器控制模块、位时序逻辑模块、位数据流处理模块,对设计的CAN控制器模块进行了时序仿真。

同时利用芯片的外设资源,设计了时钟电路、电源电路、SRAM电路、Flash电路、复位电路、JTAG接口电路、CAN总线接口电路等,这些电路共同组成了CANopen从站的硬件架构。

软件设计方面,对CANopen从站进行了协议栈的移植。

整个系统的代码遵循模块化的设计原则,包括对象字典的读/写模块、NMT控制模块、SDO报文处理模块和PDO报文处理模块。

采用分层结构实现CANopen协议的功能,分别对硬件驱动层、CANopen协议,以及设备规范应用层进行了设计。

最后提出了CANopen从站的测试方案,采用CANoe软件设计了CANopen主站的上位机软件,上位机通过CANCardXL接口卡与CANopen从站通信,在125Kbps的波特率下,测试了NMT、SDO、PDO报文通信及CAN总线负载,并采用力科示波器WaveRunner44MXi.A进行了实时报文观测。

基于国产FPGA的高速SRIO接口设计与实现摘要:随着技术发展水平的提升,接口芯片国产化要求越来越高,研究人员在国产PFGA基础上设计SRIO接口,能够有效提高国产芯片的使用效果。

因此研究人员应该继续加大对SRIO接口的研究力度,基于FRGA开展内部功能模块设计工作,还需对SRIO接口展开设计,从而提高接口验证的准确性。

本文首先分析SRIO接口的基本情况,其次探讨SRIO接口逻辑设计实现情况,以期对相关研究产生一定的参考价值。

关键词:国产FPGA;高速SRIO接口设计;实现引言:在国产FRGA技术发展水平不断提高的背景下,一些研究人员在FPGA基础上研发设计了高速SRIO接口,推动了我国国产芯片的高速发展。

以往在应用芯片时,主要依赖于进口,但是进口芯片价格高昂,在推动国产发展的背景下,基于国产FPGA的SRIO接口应运而生,使得我国很多企业不再需要使用进口芯片,可以使用价格更为低廉的国产化芯片,能够在促进国产芯片发展的同时,避免企业在芯片接口处花费过多的资金。

1国产FPGA平台本文研究的国产FPGA平台出自紫光同创电子有限公司,性能比较好,属于具备完全自主产权体系、自主开发的套件,这种芯片构成部分主要包括逻辑单元CLM、18KB存储单元DRM、算数处理单元APM、高速串行接口模块HSST、IO模块以及丰富的时钟资源。

这种国产FPGA芯片一般需要直接内置在高速串行模块HSST中,数据传输速率能够达到每秒钟6.375 Gb/s,可以灵活使用各类串行协议标准,FPGA内置的HSST接口可以被视为SRIO接口的硬件基础。

2SRIO接口的基本情况SRIO接口属于开放式比较强的互联网体系结构,这种接口类型属于能够进行交换的新一代高速互联技术,可靠性比较高、延时性比较低,管脚数比较少,接口频率比较高,端口宽度能够进行升级管理,运用这种接口可以顺利解决嵌入式系统串行数据出现的平面连接问题、高速串行数据传输安全稳定性问题、时效性问题。

serdes项目实例SerDes(Serializer/Deserializer)是一种高速串行接口技术,用于将数据从并行格式转换为串行格式,或者将数据从串行格式转换为并行格式。

SerDes广泛应用于高速通信、数据中心、云计算等领域。

下面是一个简单的SerDes项目实例,使用FPGA实现一个4Gbps的SerDes接口。

1. 项目目标本项目旨在设计并实现一个基于FPGA的4Gbps SerDes接口,用于高速数据传输和通信。

SerDes接口需要能够将FPGA内部的并行数据转换为高速串行数据,并能够在远距离传输后恢复原始数据。

2. 项目设计本项目采用Xilinx Virtex-7系列FPGA,使用其内建的SERDES模块实现SerDes接口。

具体设计如下:并行数据输入:SerDes接口接收FPGA内部的32位并行数据,数据速率为1000MHz。

串行数据输出:SerDes接口将接收到的并行数据转换为高速串行数据,数据速率为4Gbps,通过一对差分线传输。

线路编码:采用8B/10B编码方案,以提高信号的眼图质量和降低误码率。

均衡与去加重:在发送端,使用预加重和去加重技术,以提高信号的传输质量和降低误码率。

时钟管理:SerDes接口内部采用时钟管理单元(CMT),以确保时钟的准确性和稳定性。

3. 项目实现在FPGA上实现SerDes接口需要编写相应的硬件描述语言(HDL)代码,如VHDL或Verilog。

具体实现步骤如下:设计并行数据接收模块,将FPGA内部的并行数据接收并缓存到FIFO中。

设计串行数据发送模块,将FIFO中的数据转换为高速串行数据并发送出去。

设计时钟管理模块,为SerDes接口提供稳定的时钟信号。

设计均衡与去加重模块,在发送端对数据进行预加重和去加重处理,在接收端进行均衡处理。

综合和布局布线:使用Xilinx Vivado工具对设计进行综合和布局布线,生成可下载到FPGA的bit文件。

基于FPGA实现JESD204B高速接口设计作者:曹鹏飞来源:《无线互联科技》2018年第23期摘要:JESD204B接口是高速ADC和DAC芯片采用的数据通信接口之一,具有传输速率高,抗干扰能力强,芯片间同步方便等优点。

目前国内JESD204B 接口应用多由国外集成芯片提供,缺乏自主性和灵活性。

为了加强JESD204B 接口自主设计,文章阐述了基于FPGA GTX 高速收发器实现JESD204B接口通信的方法,详细说明了JESD204B接口的FPGA设计实现方案、同步化处理机制等内容。

利用多通道JESD204B接口实现高速串行数据的传输,有效解决了传统并行数据采集存在的问题,满足实际工程的应用需求。

关键词:JESD204B;FPGA;高速串行传输;数据采集模数转换器(Analog-to-Digital Converter,ADC)和数模转换器(Digital to Analog Converter,DAC)在众多领域中应用非常广泛,随着工艺的发展和实际应用的需要,采样速率和采样精度越来越高,采用传统的CMOS接口和LVDS接口已经无法满足设计的要求,而采用基于CML的JESD204B接口可以很好地解决这一问题,接口单通道速率可达12.5 Gb/s。

在ADC/DAC与FPGA处理芯片之间实现JESD204B接口,可以有效完成芯片间的高速数据传输,并且具有减少器件管脚和封装尺寸,减少占用布局空间,降低功耗等优点。

1 JESD204B概述JESD204B接口包括3个子类,分别为子类0、子类1和子类2。

JESD204B接口包括3个子类,分别为子类0、子类1和子类2。

3个子类的区别主要体现在同步方式各不相同。

子类0不支持确定性延迟,而子类1和子类2能够支持确定性延迟,可实现片间的数据同步。

子类1通过SYSREF信号在芯片内部产生帧时钟和本地多帧时钟(Local Multiframe Clock,LMFC),同步传输数据并在数字信道上实现已知和确定性延迟。