2440的裸跑程序说明

- 格式:doc

- 大小:20.50 KB

- 文档页数:2

裸跑程序之LED灯TQ2440+JLINK+keilu4(mdk)连调这个是我用JLINK+keilv4(mdk)在TQ2440跑的第一个裸奔程序。

希望对大家有帮助,如果有什么困难可以联系我,我的qq:644933989.希望大家多多交流,共同进步。

1、打开keil uvision4 新建工程,打开keil u4,点project->new2、我起名时ex1.如下,按保存。

3、在出现的下面的界面中选择samsung->S3C2440->S3C2440A芯片,点OK4、弹出对话中选是(拷贝S3C2440.S初始化文件)5、使用快捷工具栏上的方法2:点file->new6、如图,按右键加入S3C2440.h头文件。

7、写入使小灯一次点亮的代码#include <S3C2440.H>/**********************************被注释掉的是跑马灯程序。

如果想开跑马灯效果,只需把我注释掉的程序前面的//去掉,把下面一行注释掉就好***********************************/void delay(){int i, j;for(i = 0; i < 10000; i ++)for(j = 0; j < 50; j ++);}int main(){GPBCON = 0x155555;//配置protB的所有引脚为输出while(1){GPBDAT |= 0x1E0; //0001 1110 0000 第5~8位对应的是开发板上的四个小灯,为1为灭0为亮GPBDAT &= 0x1C0; //点亮第一个小灯delay();GPBDAT |= 0x1E0;//GPBDAT &= 0x1A0; //点亮第二个小灯GPBDAT &= 0x180; //点亮第一个、二个小灯delay();GPBDAT |= 0x1E0;//GPBDAT &= 0x160; //点亮第三个小灯GPBDAT &= 0x100; //点亮第一二三个小灯delay();GPBDAT |= 0x1E0;//GPBDAT &= 0x0E0; //点亮第四个小灯GPBDAT &= 0x0; //四个小灯全亮delay();}}8、然后按保存键。

//===================================================================== ========// File Name : 2440addr.h// Function : S3C2440 Define Address Register// History// 0.0 : Programming start (February 15,2002) -> SOP// Revision : 03.11.2003 ver 0.0 Attatched for 2440//===================================================================== ========#ifndef __2440ADDR_H__#define __2440ADDR_H__#ifdef __cplusplusextern "C" {#endif#include "option.h"// Memory control#define rBWSCON (*(volatile unsigned *)0x48000000) //Bus width & wait status#define rBANKCON0 (*(volatile unsigned *)0x48000004) //Boot ROM control#define rBANKCON1 (*(volatile unsigned *)0x48000008) //BANK1 control#define rBANKCON2 (*(volatile unsigned *)0x4800000c) //BANK2 cControl#define rBANKCON3 (*(volatile unsigned *)0x48000010) //BANK3 control#define rBANKCON4 (*(volatile unsigned *)0x48000014) //BANK4 control#define rBANKCON5 (*(volatile unsigned *)0x48000018) //BANK5 control#define rBANKCON6 (*(volatile unsigned *)0x4800001c) //BANK6 control#define rBANKCON7 (*(volatile unsigned *)0x48000020) //BANK7 control#define rREFRESH (*(volatile unsigned *)0x48000024) //DRAM/SDRAM refresh#define rBANKSIZE (*(volatile unsigned *)0x48000028) //Flexible Bank Size#define rMRSRB6 (*(volatile unsigned *)0x4800002c) //Mode register set for SDRAM#define rMRSRB7 (*(volatile unsigned *)0x48000030) //Mode register set for SDRAM// USB Host// INTERRUPT#define rSRCPND (*(volatile unsigned *)0x4a000000) //Interrupt request status#define rINTMOD (*(volatile unsigned *)0x4a000004) //Interrupt mode control#define rINTMSK (*(volatile unsigned *)0x4a000008) //Interrupt mask control#define rPRIORITY (*(volatile unsigned *)0x4a00000c) //IRQ priority control#define rINTPND (*(volatile unsigned *)0x4a000010) //Interrupt request status#define rINTOFFSET (*(volatile unsigned *)0x4a000014) //Interruot request source offset #define rSUBSRCPND (*(volatile unsigned *)0x4a000018) //Sub source pending#define rINTSUBMSK (*(volatile unsigned *)0x4a00001c) //Interrupt sub mask// DMA#define rDISRC0 (*(volatile unsigned *)0x4b000000) //DMA 0 Initial source#define rDISRCC0 (*(volatile unsigned *)0x4b000004) //DMA 0 Initial source control#define rDIDST0 (*(volatile unsigned *)0x4b000008) //DMA 0 Initial Destination#define rDIDSTC0 (*(volatile unsigned *)0x4b00000c) //DMA 0 Initial Destination control#define rDCON0 (*(volatile unsigned *)0x4b000010) //DMA 0 Control#define rDSTAT0 (*(volatile unsigned *)0x4b000014) //DMA 0 Status#define rDCSRC0 (*(volatile unsigned *)0x4b000018) //DMA 0 Current source#define rDCDST0 (*(volatile unsigned *)0x4b00001c) //DMA 0 Current destination#define rDMASKTRIG0 (*(volatile unsigned *)0x4b000020) //DMA 0 Mask trigger#define rDISRC1 (*(volatile unsigned *)0x4b000040) //DMA 1 Initial source#define rDISRCC1 (*(volatile unsigned *)0x4b000044) //DMA 1 Initial source control#define rDIDST1 (*(volatile unsigned *)0x4b000048) //DMA 1 Initial Destination#define rDIDSTC1 (*(volatile unsigned *)0x4b00004c) //DMA 1 Initial Destination control#define rDCON1 (*(volatile unsigned *)0x4b000050) //DMA 1 Control#define rDSTAT1 (*(volatile unsigned *)0x4b000054) //DMA 1 Status#define rDCSRC1 (*(volatile unsigned *)0x4b000058) //DMA 1 Current source#define rDCDST1 (*(volatile unsigned *)0x4b00005c) //DMA 1 Current destination#define rDMASKTRIG1 (*(volatile unsigned *)0x4b000060) //DMA 1 Mask trigger#define rDISRC2 (*(volatile unsigned *)0x4b000080) //DMA 2 Initial source#define rDISRCC2 (*(volatile unsigned *)0x4b000084) //DMA 2 Initial source control#define rDIDST2 (*(volatile unsigned *)0x4b000088) //DMA 2 Initial Destination#define rDIDSTC2 (*(volatile unsigned *)0x4b00008c) //DMA 2 Initial Destination control#define rDCON2 (*(volatile unsigned *)0x4b000090) //DMA 2 Control#define rDSTAT2 (*(volatile unsigned *)0x4b000094) //DMA 2 Status#define rDCSRC2 (*(volatile unsigned *)0x4b000098) //DMA 2 Current source#define rDCDST2 (*(volatile unsigned *)0x4b00009c) //DMA 2 Current destination#define rDMASKTRIG2 (*(volatile unsigned *)0x4b0000a0) //DMA 2 Mask trigger#define rDISRC3 (*(volatile unsigned *)0x4b0000c0) //DMA 3 Initial source#define rDISRCC3 (*(volatile unsigned *)0x4b0000c4) //DMA 3 Initial source control#define rDIDST3 (*(volatile unsigned *)0x4b0000c8) //DMA 3 Initial Destination#define rDIDSTC3 (*(volatile unsigned *)0x4b0000cc) //DMA 3 Initial Destinationcontrol#define rDCON3 (*(volatile unsigned *)0x4b0000d0) //DMA 3 Control#define rDSTAT3 (*(volatile unsigned *)0x4b0000d4) //DMA 3 Status#define rDCSRC3 (*(volatile unsigned *)0x4b0000d8) //DMA 3 Current source#define rDCDST3 (*(volatile unsigned *)0x4b0000dc) //DMA 3 Current destination#define rDMASKTRIG3 (*(volatile unsigned *)0x4b0000e0) //DMA 3 Mask trigger// CLOCK & POWER MANAGEMENT#define rLOCKTIME (*(volatile unsigned *)0x4c000000) //PLL lock time counter#define rMPLLCON (*(volatile unsigned *)0x4c000004) //MPLL Control#define rUPLLCON (*(volatile unsigned *)0x4c000008) //UPLL Control#define rCLKCON (*(volatile unsigned *)0x4c00000c) //Clock generator control#define rCLKSLOW (*(volatile unsigned *)0x4c000010) //Slow clock control#define rCLKDIVN (*(volatile unsigned *)0x4c000014) //Clock divider control#define rCAMDIVN (*(volatile unsigned *)0x4c000018) //USB, CAM Clock divider control// LCD CONTROLLER#define rLCDCON1 (*(volatile unsigned *)0x4d000000) //LCD control 1#define rLCDCON2 (*(volatile unsigned *)0x4d000004) //LCD control 2#define rLCDCON3 (*(volatile unsigned *)0x4d000008) //LCD control 3#define rLCDCON4 (*(volatile unsigned *)0x4d00000c) //LCD control 4#define rLCDCON5 (*(volatile unsigned *)0x4d000010) //LCD control 5#define rLCDSADDR1 (*(volatile unsigned *)0x4d000014) //STN/TFT Frame buffer start address 1#define rLCDSADDR2 (*(volatile unsigned *)0x4d000018) //STN/TFT Frame buffer start address 2#define rLCDSADDR3 (*(volatile unsigned *)0x4d00001c) //STN/TFT Virtual screen address set#define rREDLUT (*(volatile unsigned *)0x4d000020) //STN Red lookup table#define rGREENLUT (*(volatile unsigned *)0x4d000024) //STN Green lookup table#define rBLUELUT (*(volatile unsigned *)0x4d000028) //STN Blue lookup table#define rDITHMODE (*(volatile unsigned *)0x4d00004c) //STN Dithering mode#define rTPAL (*(volatile unsigned *)0x4d000050) //TFT Temporary palette#define rLCDINTPND (*(volatile unsigned *)0x4d000054) //LCD Interrupt pending#define rLCDSRCPND (*(volatile unsigned *)0x4d000058) //LCD Interrupt source#define rLCDINTMSK (*(volatile unsigned *)0x4d00005c) //LCD Interrupt mask#define rTCONSEL (*(volatile unsigned *)0x4d000060) //LPC3600 Control --- edited by junon#define PALETTE 0x4d000400 //Palette start address//Nand Flash#define rNFCONF (*(volatile unsigned *)0x4E000000) //NAND Flash configuration #define rNFCONT (*(volatile unsigned *)0x4E000004) //NAND Flash control#define rNFCMD (*(volatile unsigned *)0x4E000008) //NAND Flash command#define rNFADDR (*(volatile unsigned *)0x4E00000C) //NAND Flash address#define rNFDATA (*(volatile unsigned *)0x4E000010) //NAND Flash data#define rNFDATA8 (*(volatile unsigned char *)0x4E000010) //NAND Flash data#define NFDATA (0x4E000010) //NAND Flash data address#define rNFMECCD0 (*(volatile unsigned *)0x4E000014) //NAND Flash ECC for Main Area#define rNFMECCD1 (*(volatile unsigned *)0x4E000018)#define rNFSECCD (*(volatile unsigned *)0x4E00001C) //NAND Flash ECC for Spare Area#define rNFSTAT (*(volatile unsigned *)0x4E000020) //NAND Flash operation status#define rNFESTAT0 (*(volatile unsigned *)0x4E000024)#define rNFESTAT1 (*(volatile unsigned *)0x4E000028)#define rNFMECC0 (*(volatile unsigned *)0x4E00002C)#define rNFMECC1 (*(volatile unsigned *)0x4E000030)#define rNFSECC (*(volatile unsigned *)0x4E000034)#define rNFSBLK (*(volatile unsigned *)0x4E000038) //NAND Flash Start block address#define rNFEBLK (*(volatile unsigned *)0x4E00003C) //NAND Flash End block address//Camera Interface. Edited for 2440A#define rCISRCFMT (*(volatile unsigned *)0x4F000000)#define rCIWDOFST (*(volatile unsigned *)0x4F000004)#define rCIGCTRL (*(volatile unsigned *)0x4F000008)#define rCICOYSA1 (*(volatile unsigned *)0x4F000018)#define rCICOYSA2 (*(volatile unsigned *)0x4F00001C)#define rCICOYSA3 (*(volatile unsigned *)0x4F000020)#define rCICOYSA4 (*(volatile unsigned *)0x4F000024)#define rCICOCBSA1 (*(volatile unsigned *)0x4F000028)#define rCICOCBSA2 (*(volatile unsigned *)0x4F00002C)#define rCICOCBSA3 (*(volatile unsigned *)0x4F000030)#define rCICOCBSA4 (*(volatile unsigned *)0x4F000034)#define rCICOCRSA1 (*(volatile unsigned *)0x4F000038)#define rCICOCRSA2 (*(volatile unsigned *)0x4F00003C)#define rCICOCRSA3 (*(volatile unsigned *)0x4F000040)#define rCICOCRSA4 (*(volatile unsigned *)0x4F000044)#define rCICOTRGFMT (*(volatile unsigned *)0x4F000048)#define rCICOCTRL (*(volatile unsigned *)0x4F00004C)#define rCICOSCPRERA TIO (*(volatile unsigned *)0x4F000050)#define rCICOSCPREDST (*(volatile unsigned *)0x4F000054)#define rCICOSCCTRL (*(volatile unsigned *)0x4F000058)#define rCICOTAREA (*(volatile unsigned *)0x4F00005C)#define rCICOSTATUS (*(volatile unsigned *)0x4F000064)#define rCIPRCLRSA1 (*(volatile unsigned *)0x4F00006C)#define rCIPRCLRSA2 (*(volatile unsigned *)0x4F000070)#define rCIPRCLRSA3 (*(volatile unsigned *)0x4F000074)#define rCIPRCLRSA4 (*(volatile unsigned *)0x4F000078)#define rCIPRTRGFMT (*(volatile unsigned *)0x4F00007C)#define rCIPRCTRL (*(volatile unsigned *)0x4F000080)#define rCIPRSCPRERATIO (*(volatile unsigned *)0x4F000084)#define rCIPRSCPREDST (*(volatile unsigned *)0x4F000088)#define rCIPRSCCTRL (*(volatile unsigned *)0x4F00008C)#define rCIPRTAREA (*(volatile unsigned *)0x4F000090)#define rCIPRSTATUS (*(volatile unsigned *)0x4F000098)#define rCIIMGCPT (*(volatile unsigned *)0x4F0000A0)// UART#define rULCON0 (*(volatile unsigned *)0x50000000) //UART 0 Line control#define rUCON0 (*(volatile unsigned *)0x50000004) //UART 0 Control#define rUFCON0 (*(volatile unsigned *)0x50000008) //UART 0 FIFO control#define rUMCON0 (*(volatile unsigned *)0x5000000c) //UART 0 Modem control #define rUTRSTAT0 (*(volatile unsigned *)0x50000010) //UART 0 Tx/Rx status#define rUERSTAT0 (*(volatile unsigned *)0x50000014) //UART 0 Rx error status #define rUFSTAT0 (*(volatile unsigned *)0x50000018) //UART 0 FIFO status#define rUMSTAT0 (*(volatile unsigned *)0x5000001c) //UART 0 Modem status#define rUBRDIV0 (*(volatile unsigned *)0x50000028) //UART 0 Baud rate divisor#define rULCON1 (*(volatile unsigned *)0x50004000) //UART 1 Line control#define rUCON1 (*(volatile unsigned *)0x50004004) //UART 1 Control#define rUFCON1 (*(volatile unsigned *)0x50004008) //UART 1 FIFO control#define rUMCON1 (*(volatile unsigned *)0x5000400c) //UART 1 Modem control #define rUTRSTAT1 (*(volatile unsigned *)0x50004010) //UART 1 Tx/Rx status#define rUERSTAT1 (*(volatile unsigned *)0x50004014) //UART 1 Rx error status #define rUFSTAT1 (*(volatile unsigned *)0x50004018) //UART 1 FIFO status#define rUMSTAT1 (*(volatile unsigned *)0x5000401c) //UART 1 Modem status#define rUBRDIV1 (*(volatile unsigned *)0x50004028) //UART 1 Baud rate divisor #define rULCON2 (*(volatile unsigned *)0x50008000) //UART 2 Line control#define rUCON2 (*(volatile unsigned *)0x50008004) //UART 2 Control#define rUFCON2 (*(volatile unsigned *)0x50008008) //UART 2 FIFO control#define rUMCON2 (*(volatile unsigned *)0x5000800c) //UART 2 Modem control #define rUTRSTAT2 (*(volatile unsigned *)0x50008010) //UART 2 Tx/Rx status#define rUERSTAT2 (*(volatile unsigned *)0x50008014) //UART 2 Rx error status#define rUFSTAT2 (*(volatile unsigned *)0x50008018) //UART 2 FIFO status#define rUMSTAT2 (*(volatile unsigned *)0x5000801c) //UART 2 Modem status#define rUBRDIV2 (*(volatile unsigned *)0x50008028) //UART 2 Baud rate divisor#ifdef __BIG_ENDIAN#define rUTXH0 (*(volatile unsigned char *)0x50000023) //UART 0 Transmission Hold#define rURXH0 (*(volatile unsigned char *)0x50000027) //UART 0 Receive buffer#define rUTXH1 (*(volatile unsigned char *)0x50004023) //UART 1 Transmission Hold#define rURXH1 (*(volatile unsigned char *)0x50004027) //UART 1 Receive buffer#define rUTXH2 (*(volatile unsigned char *)0x50008023) //UART 2 Transmission Hold#define rURXH2 (*(volatile unsigned char *)0x50008027) //UART 2 Receive buffer#define WrUTXH0(ch) (*(volatile unsigned char *)0x50000023)=(unsigned char)(ch)#define RdURXH0() (*(volatile unsigned char *)0x50000027)#define WrUTXH1(ch) (*(volatile unsigned char *)0x50004023)=(unsigned char)(ch)#define RdURXH1() (*(volatile unsigned char *)0x50004027)#define WrUTXH2(ch) (*(volatile unsigned char *)0x50008023)=(unsigned char)(ch)#define RdURXH2() (*(volatile unsigned char *)0x50008027)#define UTXH0 (0x50000020+3) //Byte_access address by DMA#define URXH0 (0x50000024+3)#define UTXH1 (0x50004020+3)#define URXH1 (0x50004024+3)#define UTXH2 (0x50008020+3)#define URXH2 (0x50008024+3)#else //Little Endian#define rUTXH0 (*(volatile unsigned char *)0x50000020) //UART 0 Transmission Hold#define rURXH0 (*(volatile unsigned char *)0x50000024) //UART 0 Receive buffer#define rUTXH1 (*(volatile unsigned char *)0x50004020) //UART 1 Transmission Hold#define rURXH1 (*(volatile unsigned char *)0x50004024) //UART 1 Receive buffer#define rUTXH2 (*(volatile unsigned char *)0x50008020) //UART 2 Transmission Hold#define rURXH2 (*(volatile unsigned char *)0x50008024) //UART 2 Receive buffer#define WrUTXH0(ch) (*(volatile unsigned char *)0x50000020)=(unsigned char)(ch)#define RdURXH0() (*(volatile unsigned char *)0x50000024)#define WrUTXH1(ch) (*(volatile unsigned char *)0x50004020)=(unsigned char)(ch)#define RdURXH1() (*(volatile unsigned char *)0x50004024)#define WrUTXH2(ch) (*(volatile unsigned char *)0x50008020)=(unsigned char)(ch)#define RdURXH2() (*(volatile unsigned char *)0x50008024)#define UTXH0 (0x50000020) //Byte_access address by DMA#define URXH0 (0x50000024)#define UTXH1 (0x50004020)#define URXH1 (0x50004024)#define UTXH2 (0x50008020)#define URXH2 (0x50008024)#endif// PWM TIMER#define rTCFG0 (*(volatile unsigned *)0x51000000) //Timer 0 configuration#define rTCFG1 (*(volatile unsigned *)0x51000004) //Timer 1 configuration#define rTCON (*(volatile unsigned *)0x51000008) //Timer control#define rTCNTB0 (*(volatile unsigned *)0x5100000c)//Timer count buffer 0#define rTCMPB0 (*(volatile unsigned *)0x51000010) //Timer compare buffer 0#define rTCNTO0 (*(volatile unsigned *)0x51000014) //Timer count observation 0#define rTCNTB1 (*(volatile unsigned *)0x51000018) //Timer count buffer 1#define rTCMPB1 (*(volatile unsigned *)0x5100001c) //Timer compare buffer 1#define rTCNTO1 (*(volatile unsigned *)0x51000020) //Timer count observation 1#define rTCNTB2 (*(volatile unsigned *)0x51000024) //Timer count buffer 2#define rTCMPB2 (*(volatile unsigned *)0x51000028) //Timer compare buffer 2#define rTCNTO2 (*(volatile unsigned *)0x5100002c) //Timer count observation 2#define rTCNTB3 (*(volatile unsigned *)0x51000030) //Timer count buffer 3#define rTCMPB3 (*(volatile unsigned *)0x51000034) //Timer compare buffer 3#define rTCNTO3 (*(volatile unsigned *)0x51000038) //Timer count observation 3#define rTCNTB4 (*(volatile unsigned *)0x5100003c)//Timer count buffer 4#define rTCNTO4 (*(volatile unsigned *)0x51000040) //Timer count observation 4// USB DEVICE#ifdef __BIG_ENDIAN<ERROR IF BIG_ENDIAN>#define rFUNC_ADDR_REG (*(volatile unsigned char *)0x52000143) //Function address #define rPWR_REG (*(volatile unsigned char *)0x52000147) //Power management#define rEP_INT_REG (*(volatile unsigned char *)0x5200014b) //EP Interrupt pending and clear#define rUSB_INT_REG (*(volatile unsigned char *)0x5200015b) //USB Interrupt pending and clear#define rEP_INT_EN_REG (*(volatile unsigned char *)0x5200015f)//Interrupt enable#define rUSB_INT_EN_REG (*(volatile unsigned char *)0x5200016f)#define rFRAME_NUM1_REG (*(volatile unsigned char *)0x52000173) //Frame number lower byte#define rFRAME_NUM2_REG (*(volatile unsigned char *)0x52000177) //Frame number higher byte#define rINDEX_REG (*(volatile unsigned char *)0x5200017b) //Register index #define rMAXP_REG (*(volatile unsigned char *)0x52000183) //Endpoint max packet#define rEP0_CSR (*(volatile unsigned char *)0x52000187) //Endpoint 0 status#define rIN_CSR1_REG (*(volatile unsigned char *)0x52000187) //In endpoint control status#define rIN_CSR2_REG (*(volatile unsigned char *)0x5200018b)#define rOUT_CSR1_REG (*(volatile unsigned char *)0x52000193) //Out endpoint control status#define rOUT_CSR2_REG (*(volatile unsigned char *)0x52000197)#define rOUT_FIFO_CNT1_REG (*(volatile unsigned char *)0x5200019b) //Endpoint out write count#define rOUT_FIFO_CNT2_REG (*(volatile unsigned char *)0x5200019f)#define rEP0_FIFO (*(volatile unsigned char *)0x520001c3) //Endpoint 0 FIFO#define rEP1_FIFO (*(volatile unsigned char *)0x520001c7) //Endpoint 1 FIFO#define rEP2_FIFO (*(volatile unsigned char *)0x520001cb) //Endpoint 2 FIFO#define rEP3_FIFO (*(volatile unsigned char *)0x520001cf) //Endpoint 3 FIFO#define rEP4_FIFO (*(volatile unsigned char *)0x520001d3) //Endpoint 4 FIFO#define rEP1_DMA_CON (*(volatile unsigned char *)0x52000203) //EP1 DMA interface control#define rEP1_DMA_UNIT (*(volatile unsigned char *)0x52000207) //EP1 DMA Tx unit counter#define rEP1_DMA_FIFO (*(volatile unsigned char *)0x5200020b) //EP1 DMA Tx FIFO counter#define rEP1_DMA_TTC_L (*(volatile unsigned char *)0x5200020f) //EP1 DMA total Tx counter#define rEP1_DMA_TTC_M (*(volatile unsigned char *)0x52000213)#define rEP1_DMA_TTC_H (*(volatile unsigned char *)0x52000217)#define rEP2_DMA_CON (*(volatile unsigned char *)0x5200021b) //EP2 DMA interface control#define rEP2_DMA_UNIT (*(volatile unsigned char *)0x5200021f) //EP2 DMA Tx unit counter#define rEP2_DMA_FIFO (*(volatile unsigned char *)0x52000223) //EP2 DMA Tx FIFO counter#define rEP2_DMA_TTC_L (*(volatile unsigned char *)0x52000227) //EP2 DMA total Tx counter#define rEP2_DMA_TTC_M (*(volatile unsigned char *)0x5200022b)#define rEP2_DMA_TTC_H (*(volatile unsigned char *)0x5200022f)#define rEP3_DMA_CON (*(volatile unsigned char *)0x52000243) //EP3 DMA interface control#define rEP3_DMA_UNIT (*(volatile unsigned char *)0x52000247) //EP3 DMA Tx unit counter#define rEP3_DMA_FIFO (*(volatile unsigned char *)0x5200024b) //EP3 DMA Tx FIFO counter#define rEP3_DMA_TTC_L (*(volatile unsigned char *)0x5200024f) //EP3 DMA total Tx counter#define rEP3_DMA_TTC_M (*(volatile unsigned char *)0x52000253)#define rEP3_DMA_TTC_H (*(volatile unsigned char *)0x52000257)#define rEP4_DMA_CON (*(volatile unsigned char *)0x5200025b) //EP4 DMA interface control#define rEP4_DMA_UNIT (*(volatile unsigned char *)0x5200025f) //EP4 DMA Tx unit counter#define rEP4_DMA_FIFO (*(volatile unsigned char *)0x52000263) //EP4 DMA Tx FIFO counter#define rEP4_DMA_TTC_L (*(volatile unsigned char *)0x52000267) //EP4 DMA total Tx counter#define rEP4_DMA_TTC_M (*(volatile unsigned char *)0x5200026b)#define rEP4_DMA_TTC_H (*(volatile unsigned char *)0x5200026f)#else // Little Endian#define rFUNC_ADDR_REG (*(volatile unsigned char *)0x52000140) //Function address #define rPWR_REG (*(volatile unsigned char *)0x52000144) //Power management#define rEP_INT_REG (*(volatile unsigned char *)0x52000148) //EP Interrupt pending and clear#define rUSB_INT_REG (*(volatile unsigned char *)0x52000158) //USB Interrupt pending and clear#define rEP_INT_EN_REG (*(volatile unsigned char *)0x5200015c) //Interrupt enable #define rUSB_INT_EN_REG (*(volatile unsigned char *)0x5200016c)#define rFRAME_NUM1_REG (*(volatile unsigned char *)0x52000170) //Frame number lower byte#define rFRAME_NUM2_REG (*(volatile unsigned char *)0x52000174) //Frame number higher byte#define rINDEX_REG (*(volatile unsigned char *)0x52000178) //Register index #define rMAXP_REG (*(volatile unsigned char *)0x52000180) //Endpoint max packet#define rEP0_CSR (*(volatile unsigned char *)0x52000184) //Endpoint 0 status#define rIN_CSR1_REG (*(volatile unsigned char *)0x52000184) //In endpoint control status#define rIN_CSR2_REG (*(volatile unsigned char *)0x52000188)#define rOUT_CSR1_REG (*(volatile unsigned char *)0x52000190) //Out endpoint control status#define rOUT_CSR2_REG (*(volatile unsigned char *)0x52000194)#define rOUT_FIFO_CNT1_REG (*(volatile unsigned char *)0x52000198) //Endpoint out write count#define rOUT_FIFO_CNT2_REG (*(volatile unsigned char *)0x5200019c)#define rEP0_FIFO (*(volatile unsigned char *)0x520001c0) //Endpoint 0 FIFO#define rEP1_FIFO (*(volatile unsigned char *)0x520001c4) //Endpoint 1 FIFO#define rEP2_FIFO (*(volatile unsigned char *)0x520001c8) //Endpoint 2 FIFO#define rEP3_FIFO (*(volatile unsigned char *)0x520001cc) //Endpoint 3 FIFO#define rEP4_FIFO (*(volatile unsigned char *)0x520001d0) //Endpoint 4 FIFO#define rEP1_DMA_CON (*(volatile unsigned char *)0x52000200) //EP1 DMA interface control#define rEP1_DMA_UNIT (*(volatile unsigned char *)0x52000204) //EP1 DMA Tx unit counter#define rEP1_DMA_FIFO (*(volatile unsigned char *)0x52000208) //EP1 DMA Tx FIFO counter#define rEP1_DMA_TTC_L (*(volatile unsigned char *)0x5200020c) //EP1 DMA total Tx counter#define rEP1_DMA_TTC_M (*(volatile unsigned char *)0x52000210)#define rEP1_DMA_TTC_H (*(volatile unsigned char *)0x52000214)#define rEP2_DMA_CON (*(volatile unsigned char *)0x52000218) //EP2 DMA interface control#define rEP2_DMA_UNIT (*(volatile unsigned char *)0x5200021c) //EP2 DMA Tx unit counter#define rEP2_DMA_FIFO (*(volatile unsigned char *)0x52000220) //EP2 DMA Tx FIFO counter#define rEP2_DMA_TTC_L (*(volatile unsigned char *)0x52000224) //EP2 DMA total Tx counter#define rEP2_DMA_TTC_M (*(volatile unsigned char *)0x52000228)#define rEP2_DMA_TTC_H (*(volatile unsigned char *)0x5200022c)#define rEP3_DMA_CON (*(volatile unsigned char *)0x52000240) //EP3 DMA interface control#define rEP3_DMA_UNIT (*(volatile unsigned char *)0x52000244) //EP3 DMA Tx unit counter#define rEP3_DMA_FIFO (*(volatile unsigned char *)0x52000248) //EP3 DMA Tx FIFO counter#define rEP3_DMA_TTC_L (*(volatile unsigned char *)0x5200024c) //EP3 DMA total Tx counter#define rEP3_DMA_TTC_M (*(volatile unsigned char *)0x52000250)#define rEP3_DMA_TTC_H (*(volatile unsigned char *)0x52000254)#define rEP4_DMA_CON (*(volatile unsigned char *)0x52000258) //EP4 DMA interface control#define rEP4_DMA_UNIT (*(volatile unsigned char *)0x5200025c) //EP4 DMA Tx unit counter#define rEP4_DMA_FIFO (*(volatile unsigned char *)0x52000260) //EP4 DMA Tx FIFO counter#define rEP4_DMA_TTC_L (*(volatile unsigned char *)0x52000264) //EP4 DMA total Tx counter#define rEP4_DMA_TTC_M (*(volatile unsigned char *)0x52000268)#define rEP4_DMA_TTC_H (*(volatile unsigned char *)0x5200026c)#endif // __BIG_ENDIAN// WATCH DOG TIMER#define rWTCON (*(volatile unsigned *)0x53000000) //Watch-dog timer mode#define rWTDAT (*(volatile unsigned *)0x53000004) //Watch-dog timer data#define rWTCNT (*(volatile unsigned *)0x53000008) //Eatch-dog timer count// IIC#define rIICCON (*(volatile unsigned *)0x54000000) //IIC control#define rIICSTAT (*(volatile unsigned *)0x54000004) //IIC status#define rIICADD (*(volatile unsigned *)0x54000008) //IIC address#define rIICDS (*(volatile unsigned *)0x5400000c) //IIC data shift#define rIICLC (*(volatile unsigned *)0x54000010) //IIC multi-master line control// IIS#define rIISCON (*(volatile unsigned *)0x55000000) //IIS Control#define rIISMOD (*(volatile unsigned *)0x55000004) //IIS Mode#define rIISPSR (*(volatile unsigned *)0x55000008) //IIS Prescaler#define rIISFCON (*(volatile unsigned *)0x5500000c) //IIS FIFO control#ifdef __BIG_ENDIAN#define IISFIFO ((volatile unsigned short *)0x55000012) //IIS FIFO entry#else //Little Endian#define IISFIFO ((volatile unsigned short *)0x55000010) //IIS FIFO entry#endif//AC97, Added for S3C2440A#define rAC_GLBCTRL *(volatile unsigned *)0x5b000000#define rAC_GLBSTAT *(volatile unsigned *)0x5b000004#define rAC_CODEC_CMD *(volatile unsigned *)0x5b000008#define rAC_CODEC_STA T *(volatile unsigned *)0x5b00000C#define rAC_PCMADDR *(volatile unsigned *)0x5b000010#define rAC_MICADDR *(volatile unsigned *)0x5b000014#define rAC_PCMDATA *(volatile unsigned *)0x5b000018#define rAC_MICDA TA *(volatile unsigned *)0x5b00001C#define AC_PCMDATA 0x5b000018#define AC_MICDA TA 0x5b00001C// I/O PORT#define rGPACON (*(volatile unsigned *)0x56000000) //Port A control#define rGPADAT (*(volatile unsigned *)0x56000004) //Port A data#define rGPBCON (*(volatile unsigned *)0x56000010) //Port B control#define rGPBDAT (*(volatile unsigned *)0x56000014) //Port B data#define rGPBUP (*(volatile unsigned *)0x56000018) //Pull-up control B#define rGPCCON (*(volatile unsigned *)0x56000020) //Port C control#define rGPCDAT (*(volatile unsigned *)0x56000024) //Port C data#define rGPCUP (*(volatile unsigned *)0x56000028) //Pull-up control C#define rGPDCON (*(volatile unsigned *)0x56000030) //Port D control#define rGPDDAT (*(volatile unsigned *)0x56000034) //Port D data#define rGPDUP (*(volatile unsigned *)0x56000038) //Pull-up control D#define rGPECON (*(volatile unsigned *)0x56000040) //Port E control#define rGPEDAT (*(volatile unsigned *)0x56000044) //Port E data#define rGPEUP (*(volatile unsigned *)0x56000048) //Pull-up control E#define rGPFCON (*(volatile unsigned *)0x56000050) //Port F control#define rGPFDAT (*(volatile unsigned *)0x56000054) //Port F data#define rGPFUP (*(volatile unsigned *)0x56000058) //Pull-up control F#define rGPGCON (*(volatile unsigned *)0x56000060) //Port G control#define rGPGDAT (*(volatile unsigned *)0x56000064) //Port G data#define rGPGUP (*(volatile unsigned *)0x56000068) //Pull-up control G#define rGPHCON (*(volatile unsigned *)0x56000070) //Port H control#define rGPHDAT (*(volatile unsigned *)0x56000074) //Port H data#define rGPHUP (*(volatile unsigned *)0x56000078) //Pull-up control H#define rGPJCON (*(volatile unsigned *)0x560000d0) //Port J control#define rGPJDAT (*(volatile unsigned *)0x560000d4) //Port J data#define rGPJUP (*(volatile unsigned *)0x560000d8) //Pull-up control J#define rMISCCR (*(volatile unsigned *)0x56000080) //Miscellaneous control#define rDCLKCON (*(volatile unsigned *)0x56000084) //DCLK0/1 control#define rEXTINT0 (*(volatile unsigned *)0x56000088) //External interrupt control register 0 #define rEXTINT1 (*(volatile unsigned *)0x5600008c) //External interrupt control register 1 #define rEXTINT2 (*(volatile unsigned *)0x56000090) //External interrupt control register 2 #define rEINTFLT0 (*(volatile unsigned *)0x56000094) //Reserved#define rEINTFLT1 (*(volatile unsigned *)0x56000098) //Reserved#define rEINTFLT2 (*(volatile unsigned *)0x5600009c) //External interrupt filter control register 2。

2440裸机学习心得(上)哎,以前总想裸机加系统一齐学,学着学着发现好混乱,D驱动~~然后又重新斋跑2440的裸机。

以下系少少心得,记录下学习过程。

里面有三个地方还没弄好:1、硬盘的文件系统 FAT部分(后面有空补补)2、 NORFLASH中的读写有点问题3、 USB主机中对U盘的UFI命令有什么问题欢迎一起交流。

以下是部分心得:LEDGPXCON中每两位控制一个引脚:00输入,01输出,10特殊功能初始化rGPBCON , rGPBUP , rGPBDAT三个寄存器关于ADS配置的解释:在Target Settings中的Post-linker中选择ARM fromELF,因为我们需要把ELF文件格式转化为下载到flash中所必须的二进制文件。

在Language Settings中的所有语言的Target下的Architecture or Processor,选择ARM920T,因为s3c2440是ARM920T内核。

在ARM Linker中的Output中的RO Base填写0x30000000,因为在开发板上SDRAM是从0x30000000地址开始。

在Layout中的Object/Symbol中填写2440init.o,它是启动文件的目标文件,在Section中填写Init,它是在启动文件中我们所定义的入口代码段的名称。

外部中断我们要打开某一中断的屏蔽,这样才能响应该中断,相对应的寄存器为INTMSK;还要设置外部中断的触发方式,如低电平、高电平、上升沿、下降沿等,相对应的寄存器为EXTINTn。

另外由于EINT4到EINT7共用一个中断向量,EINT8到EINT23也共用一个中断向量,而INTMSK只负责总的中断向量的屏蔽,要具体打开某一具体的中断屏蔽,还需要设置EINTMASK。

有一些中断是共用一个中断向量的,而一个中断向量只能有一个中断执行函数,因此具体是哪个外部中断,还需要EINTPEND或rINTOFFSET来判断使用__irq这个关键词来定义中断处理函数,这样系统会为我们自动保存一些必要的变量,并能够在中断处理函数执行完后正确地返回这种形式:void __irq key();pISR_EINT0=(int)key;定时器使用主要配置:外部时钟源→通过寄存器MPLLCON得到FCLK→再通过寄存器CLKDIVN得到HCLK和PCLK->;再得到定时器的工作频率PWM定时器使用:蜂鸣器=GPB0=TOUT0=定时器0蜂鸣器高电平响,低电平不响关键是设置寄存器TCNTBn和TCMPBn,前者可以确定一个计数周期的时间长度,而后者可以确定方波的占空比定时器中断使用:不需要配置TCMPBn,只需TCNTBn,TCNTBn*1/定时器的工作频率=定时的时间但要记住中断要:void __irq timer0_sever();pISR_TIMER0=(int)timer0_sever;rINTMSK =~BIT_TIMER0;Uart主要配置以下寄存器:UBRDIVn,UCONn,UTRSTATn收发寄存器:UTXHn,URXHn注意几点:1.对于s3c2440来说,接收数据是被动的,发送数据是主动的,因此一般来说,接收数据用中断方式,发送数据用查询方式较好;2.在中断方式下,当接收到数据时,尽管可能该数据无用,但也一定要读取它,否则下次再接收数据时,不会再引起中断,因为接收数据缓存器被上次接收到的数据所霸占,只要没有读取它,它就永远在那里;3.由于UART中断涉及到SUBSRCPND寄存器,因此在中断处理程序中不仅要清SRCPND寄存器,还要清SUBSRCPND 寄存器,它们的顺序一定是先清SUBSRCPND寄存器,再清SRCPND寄存器,否则就会引起一个中断两次响应的问题。

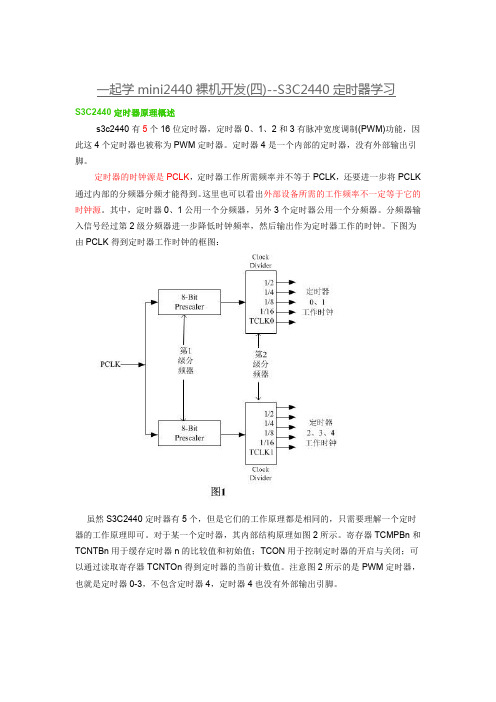

一起学mini2440裸机开发(四)--S3C2440定时器学习S3C2440定时器原理概述s3c2440有5个16位定时器,定时器0、1、2和3有脉冲宽度调制(PWM)功能,因此这4个定时器也被称为PWM定时器。

定时器4是一个内部的定时器,没有外部输出引脚。

定时器的时钟源是PCLK,定时器工作所需频率并不等于PCLK,还要进一步将PCLK 通过内部的分频器分频才能得到。

这里也可以看出外部设备所需的工作频率不一定等于它的时钟源。

其中,定时器0、1公用一个分频器,另外3个定时器公用一个分频器。

分频器输入信号经过第2级分频器进一步降低时钟频率,然后输出作为定时器工作的时钟。

下图为由PCLK得到定时器工作时钟的框图:虽然S3C2440定时器有5个,但是它们的工作原理都是相同的,只需要理解一个定时器的工作原理即可。

对于某一个定时器,其内部结构原理如图2所示。

寄存器TCMPBn和TCNTBn用于缓存定时器n的比较值和初始值;TCON用于控制定时器的开启与关闭;可以通过读取寄存器TCNTOn得到定时器的当前计数值。

注意图2所示的是PWM定时器,也就是定时器0-3,不包含定时器4,定时器4也没有外部输出引脚。

定时器工作原理概述:●首先,将定时器的比较值和初始值装入寄存器TCMPBn和TCNTBn中●然后,设置定时器控制寄存器TCON,启动定时器。

此时,TCMPBn和TCNTBn 中的值会加载到寄存器TCMPn和TCNTn中●此时,定时器会减1计数,即TCNTn进行减1计数,当TCMPn=TCNTn时,TOUTn引脚输出取反。

S3C2440定时器相关寄存器●定时器控制寄存器TCON由于各个定时器的工作原理相似,下面以定时器0为例进行讲解。

在定时器控制寄存器TCON中,位[3:0]用于控制定时器0,其含义如表1所示:位功能简述描述0开启/停止0:停止定时器1:开启定时器1手动更新0:未使用1:TCMPB0和TCNTB0中的值会加载到寄存器TCMP0和TCNT0中2输出控制0:当TCMP0=TCNT0时,TOUTO0引脚输出不翻转1:当TCMP0=TCNT0时,TOUTO0引脚输出翻转3自动加载0:自动加载1:当TCNTO0的值减到0时,TCMPB0中的值会加载到寄存器TCMPB0和TCNTB0中●定时器比较值缓存寄存器TCMPBn、计数值缓存寄存器TCNTBn这两个寄存器用于存储定时器的比较值初始值和计数值初始值。

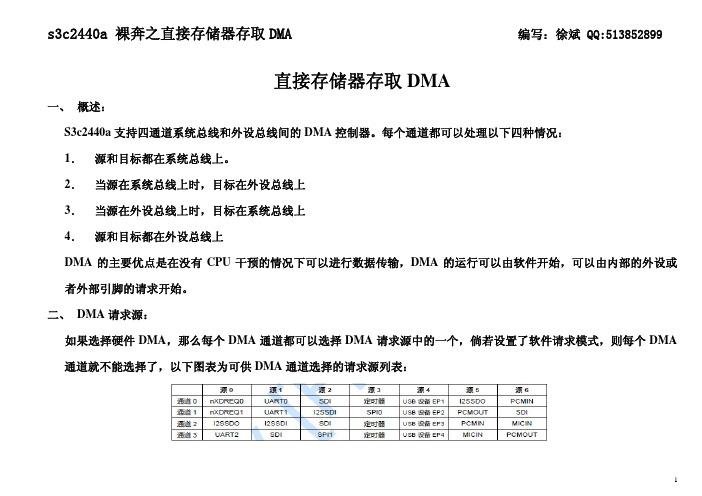

直接存储器存取DMA一、 概述:S3c2440a支持四通道系统总线和外设总线间的DMA控制器。

每个通道都可以处理以下四种情况:1.源和目标都在系统总线上。

2.当源在系统总线上时,目标在外设总线上3.当源在外设总线上时,目标在系统总线上4.源和目标都在外设总线上DMA的主要优点是在没有CPU干预的情况下可以进行数据传输,DMA的运行可以由软件开始,可以由内部的外设或者外部引脚的请求开始。

二、 DMA请求源:如果选择硬件DMA,那么每个DMA通道都可以选择DMA请求源中的一个,倘若设置了软件请求模式,则每个DMA 通道就不能选择了,以下图表为可供DMA通道选择的请求源列表:三.DMA操作:DMA为其运行使用3态FSM(有限状态机),具体过程见如下描述1.作为初始状态DMA等待DMA请求,一旦等到DMA 请求则进入第二状态,在此状态时DMA ACK和INT REQ为0 2.在此状态,DMA ACK 变为1 而且计数器(CURR_TC)从DCON[19:0]寄存器中加载。

注意DMA ACK 保持为1 直到之后将其清除。

3.在此状态,处理DMA 的原子操作的sub-FSM 启动。

sub-FSM 从源地址读取数据,接着写入目标地址。

在此操作中考虑数据大小和传输大小(单次或突发)。

此操作在全服务模式中一直重复直到计数器(CURR_TC)变为0,在单服务模式只执行一次。

当sub-FSM完成了每个原子操作时主FSM(此FSM)倒计数CURR_TC。

此外当CURR_TC 变为0 并且DCON[29]寄存器的中断设置置位为1 时主FSM 发出INT REQ 信号。

另外如果遇到以下状况之一则清除了DMA ACK。

1) 在全服务模式中CURR_TC 变为0;2) 在单服务模式中完成原子操作。

注意在单服务模式中有三个主FSM 的状态要执行并且接着要停止和等待其它DMA REQ。

如果DMA REQ 出现了要重复所有的三个状态。

MDK下S3C2440裸机中断,断断续续将耗费了我将近了一个月的时间,在贵师大图书馆里几乎翻遍了有关图书,有关这方面的介绍寥寥而过,想必出书的人也未必弄得清楚。

网上的资料也五花八门,有些说MDK自带的2440的启动代码有误(确实跟2410的启动代码不同,但经过这段时间的验证,启动代码绝对没有任何问题);有些说必须内存映射到正确的地址,才可以进入相应异常(从NORFLASH启动绝对可以进入IRQ中断);大部分在书写中断服务程序时,__irq关键字都放在函数名的前面(ADS编译器__irq关键之放置在函数名前面,但MDK必须将__irq关键字放在函数最末端);有些说必须修改2440启动代码才能进入中断(没有对启动代码做任何修改,实现了IRQ中断)……在这些一大堆乱七八糟的资料中,我差点都放弃了ARM的学习。

为了实现IRQ中断而很吃力地学习了ARM汇编,试着修改2440的启动代码;学习了内存管理,试着映射异常向量的地址;如今回过头去看,能挺过来挺欣慰的。

为实现简单IRQ中断其实很简单的,真是踏破铁鞋无觅处,得来全不费功夫。

以下是关键的几点程序说明,希望对后面学习的朋友,有些帮助。

void irq_init() //irq初始化,这个函数其实比较简单,适当看看2440PDF就应该能设定寄存器了{GPFCON = 0xaaaa;SRCPND = 0x17;INTMSK &= ~(0x17);INTPND = 0x17;EINTPEND =(1<<4);__asm{nop}EINTMASK &=~(1<<4);__asm{nop}EXTINT0 = 0x0;}//这是个很关键的函数,但其实也简单中断服务函数照着这个形式写就应该没能进入IRQ中断了。

void IRQ_Handler(void) __irq //irq中断函数{int j=0;__asm{nop};__asm{nop};j= INTOFFSET;SRCPND = SRCPND | 0x17;INTPND = INTPND | 0x17;switch(j){case 0:irq_ent0();//为中断0break;case 1:irq_ent1();//外中断1break;case 2:irq_ent2();//外中断2break;case 4:irq_ent4();//外中断4irq_init();break;}}以上两个函数式实现IQR中断的关键函数,能弄清楚上面的两个函数,IRQ中断应该就没什么大问题了。

*********************************************************nand flash裸板驱动的基本流程(s3c2440)*********************************************************NAND FLASH的工作模式①自动启动模式②NAND FLASH 模式(软件)一、自动启动模式:(auto boot)1、H/W set 硬件配置2、复位之后,NAND FLASH的最先4KB的,代码被复制到stepping stone中。

stepping stone为内部SRAM(4Kbytes)3、stepping stone 被映射为Bank0(nGS0),且CPU在此4KB内部SRAM中开始执行启动代码(Bootloader)【注】启动之后stepping stone 可用于其他用途。

由于NAND FLASH的特殊结构和寻址方式(串行),使得无法在NAND FLASH上执行代码。

因此,在程序开始时,需将NAND FLASH上的代码复制到SDRAM中,之后程序在SDRAM中执行。

复制的任务是在stepping stone中完成的,也就是NAND FLASH 中的最开始4KB程序的任务另外,2440A的Memory Map中,只有BANK6/7可以映射SDRAM,最大容量为128M*2=256MB当main代码总量超过这个值时(256MB),就不能采用NAND FLASH启动模式。

只能使用Nor FLASH启动【OM[1:0]=01,10】同样与硬件的使用情况有关。

二、NAND FLASH(软件)模式:======================================================================== NAND FLASH初始化========================================================================1.NFCONF[0x4E000000]TACLS [14:12] CLE&ALE duration = HCLK*TACLSTWRPH0 [10:8] TWRPH0 duration = HCLK*(TWRPH0+1)TWRPH1 [6:4] TWRPH1 duration = HCLK*(TWRPH1+1)AdvFlash(R) [3] Advanced NAND, 0:256/512, 1:1024/2048PageSize(R) [2] NAND memory page sizewhen [3]==0, 0:256, 1:512 bytes/page.when [3]==1, 0:1024, 1:2048 bytes/page.AddrCycle(R) [1] NAND flash addr sizewhen [3]==0, 0:3-addr, 1:4-addr.when [3]==1, 0:4-addr, 1:5-addr.BusWidth(R/W) [0] NAND bus width. 0:8-bit, 1:16-bit.2.NFCONT[0x4E000004]Lock-tight [13] 0:Disable lock, 1:Enable lock.Soft Lock [12] 0:Disable lock, 1:Enable lock.EnablillegalAcINT [10] Illegal access interupt control. 0:Disable, 1:Enable当soft lock 或者lock-tight置一时,NAND FLASH可用区域被锁定其范围为NFSBLK[0x4E000038]和NFEBLK[0x4E00003C]-1指定的区域凡是对可用区域以外的访问都是illegal accessEnbRnBINT [9] RnB interrupt. 0:Disable, 1:EnableRnB_TrandMode [8] RnB transition detection config. 0:Low to High, 1:High to LowSpareECCLock [6] 0:Unlock, 1:LockMainECCLock [5] 0:Unlock, 1:LockInitECC(W) [4] 1:Init ECC decoder/encoder.Reg_nCE [1] 0:nFCE=0, 1:nFCE=1.NANDC Enable [0] operating mode. 0:Disable, 1:Enable.===================================================================== 读取NAND FLASH ID=====================================================================1.NFChipEn(); //使能NAND FLASH2.WrNFCmd(RdIDCMD); //读取ID指令RdIDCMD=0x903.WrNFAddr(0); //写入地址,必须是00h4.While(NFIsBusy()); //等待NFSTAT:0=05.id=RdNFDat()>8); //写入A17~A24if(NandAddr) //如果NAND FLASH容量>32M NandAddr=1否则NandAddr=0WrNFAddr(addr>>16);//NAND FLASH>32MB,写入A25//当NAND FLASH32MB时,page地址线有17根(A9~A25)5.WrNFCmd(ERASECMD1); //块擦除指令EARSECMD1=0xd0【2nd cycle】6.NFChipDs(); //NAND FLASH除能======================================================================== NAND FLASH页读取========================================================================1.NFChipEn(); //NAND FLASH使能2.WrNFCmd(READCMD0) //读取指令READCMD0=0x03.WrNFAddr(0); //由于读页,所以地址页对准,A0~A7=00HWrNFAddr(addr); //写入地址A9~A16WrNFAddr(addr>>8); //写入地址A17~A24if(NandAddr)WrNFAddr(addr>>16); //NAND FLASH>32MB,写入地址A254 InitEcc(); //reset Ecc:rNFCONT|=(1>8); //写入地址A17~A24if(NandAddr)WrNFAddr(addr>>16); //NAND FLASH>32MB时,写入A254.InitEcc(); //reset ECC5.MEccUnlock(); //MEccUnlock: rNFCONT&=~(1>8)&0xff;tmp2=(mecc>>16)&0xff;tmp3=(mecc>>24)&0xff;tmp5=0xff; //0xff将作为good block标识,储存在spare area9.SEccUnlock(); //SEccUnlock:rNFCONT&=~(1>8); //写入地址A17~A24if(NandAddr)WrNFAddr(addr>>16); //NAND FLASH>32MB,写入A255.NFWaitBusy(); //延时+等待NFSTAT:0=0//也可以通过NAND状态读取来查询状态//【注意】等待的子程序中不能有READCMD0等指令写入,//否则pointer指向A块6.data=RdNFDat(); //读取data=NFDATA[0x4E000010]7.WrNFCmd(READCMD0); //读取指令READCMD0=0x0,pointer指向A块(1st main area)8.NFChipDs(); //NAND FLASH除能若data!=0xff,则当前块(addr)为坏块。

TQ2440_LCD驱动编写(裸机)一.前言二.驱动编写三.代码清单1.前言写本文的目的,旨在"授之以渔,而非授之以鱼".关于2440LCD的代码,网上一搜一大堆.当然写得都差不多.这里我是想阐述如何去写驱动程序,如何对照2440的手册,对照LCD的数据手册来配置相关的寄存器的值.(1)在写驱动(裸机程序)之前,我们必须准备好几样东西:①S3C2440数据手册②TQ043TSCM_V0.1_40P(天嵌4.3寸屏手册)③TQ2440_V2核心板原理图④TQ2440底板原理图2.驱动编写驱动的编写大致分为三个部分:(1)配置GPIO用于LCD即:LCD_GPIOInit()a.配置GPIO用于LCD比较简单,阅读TQ2440_V2核心板原理图,找出LCD所需配置的管脚图1:这是TQ2440的核心板原理图的一部分b.从S3C2440手册中搜索GPIO管脚所在位的寄存器.这个想必不用多说.c.对寄存器写入相应的控制字GPCCON|=0xaaaa02a9;//VD[7]~VD[0]\VM\VFRAME\VLINE\VCLK\LENDGPCUP=0x0;//pull upGPDCON|=0xaaaaaaaa;//VD[23]~VD[8]will be enableGPDUP=0x0;//pull upGPGCON|=(3<<8);//LCD_PWRDN enableGPGUP=0x7ff;//pull downd.完成GPIO的设置查阅S3C2440的手册,根据自己的需求,对相应的寄存器写入控制字.(2)设置LCD控制器a.明确概念说到这里,也许有很多人就觉得有点难了.尤其是初学者.为什么会觉得难呢?是因为有"很多"东西需要去设置.如果脑袋里没有任何概念就去设置LCD控制器当然会觉得很难.这样我们在配置LCD控制器之前,我们来明确几个概念.图2:这是天嵌4.3寸屏数据手册①帧频率(Frame Rate).范围:60~90Hz我们都知道图形其实也是由点构成的,形象的比喻一下:"电子枪"通过"描点"来实现图形显示.而图形的基本单位,我们称之为"帧".那么电子枪完成一帧所需要的时间,就是我们关心的问题了.它的倒数便是我们的"帧频率"Frame Rate.而Frame Rate与寄存器的设置有着密不可分的联系,看下芯片手册就能够明白大概.下面这段内容对我们很重要,尤其是对后面寄存器的配置.(最后可以通过下面公式来检验Frame Rate是否超出60~90HZ)图3:这是S3C2440数据手册②点频率(Dot Data Clock/DCLK).范围:9.0~15MHzDot Data Clock,顾名思义即是每一个点所需要的花费的时间.图4:这是S3C2440数据手册从图4可以看出,我们需要设置的东西,图中的VCLK即是DCLK.这个需要我们自己来设置,取值在9~15MHZ均可.HCLK是在系统时钟设置的时候必须设置好的.是已知的.所以这里我们要求的是CLKVAL的值,然后把计算出来的值写入寄存器(LCDCON1中的CLKVAL[17:8]).这里就可以得到我们的Dot Data Clock.③时序图(Timing parameter)时序图的时间设置很关键,那么是配置哪些寄存器中的位呢?图3中有这么一段话,The frame rate is VSYNC signal frequency.The frame rate is related with the field of VSYNC,VBPD,VFPD,LINEVAL,HSYNC,HBPD,HFPD,HOZVAL,and CLKVAL in LCDCON1and LCDCON2/3/4registers.我们组织一下语言就知道是哪些个信号需要配置了.垂直信号:VSYNC,VBPD,VFPD,LINEVAL,(这里遗漏了VSPW)水平信号:HSYNC,HBPD,HFPD,HOZVAL,(这里遗漏了HSPW)其它信号:CLKVAL(这个标志位在LCDCON1中,用于设置VCLK(Dot Data Clock)) PS:这些信号的设置均在LCDCON1~4四个寄存器当中.图5:这是S3C2440数据手册PS:看到上面的图,那么接下来我们要思考的问题是怎么样去设置寄存器呢?这些值可以从哪里获取信息呢?我们带着这些疑问,一步步往下面走。

烧写Nand Flash1.开发板设为Nor Flash启动(开发板有选择Nor Flash或Nand Flash启动的开关)2.接好JLlink后,用JLink的软件J-Flash烧写百问网特制的u-boot.bin到Nor Flash上去3.重启开发板,在串口里操作u-boot烧写Nand Flash步骤1:使用JLink烧写Nor Flash注:JLink只支持烧写Nor Flash,不支持烧写Nand Flash。

1.准备工作:JLink的USB口接到电脑上,JLink的JTAG口用排线和开发板的JTAG口相连,开发板设为Nor Flash启动并上电2.启动J-Flash。

1).选择菜单“File -> Open -> Open Project…”,打开:开发板资料\如何烧写S3C2440裸板程序\s3c2440.jflash。

图2 打开S3C2440工程2).选择菜单“Target -> Connect”图3 连接开发板3).选择菜单“File -> Open”,打开要烧写的二进制文件,比如u-boot.bin,并且在“Start address”里输入0。

图4 打开bin文件4).选择菜单“Target -> Auto”即可自动烧写。

步骤2:Nor Flash上已经有了u-boot,使用u-boot烧写法一(dnw烧写):1.用两根USB线,分别连接板子上的USB和USB-COM1,打开串口调试工具secureCRT,波特率调节为115200.第一次使用板子上的USB口要装驱动(路径:开发板资料\windows\drivers\dnw)→必须手动安装驱动2.把已经烧好的u-boot的开发板上电启动。

在倒数0之前,按下键盘的空格键。

3.输入n 即(download u-boot to nand flash).4.打开软件dnw路径:开发板资料\如何烧写S3C2440裸板程序\工具\windows USB Port ->transmit例:打开开发板资料\bin\hardware\lcd.bin5.烧写成功后,板子断电,拨到nand启动再打开电源,就可以在secureCRT里面调试输出了法二(tftp下载烧写):1.解压tftpboot(开发板资料\windows\tools)到(C:\Program Files\tftpboot),并发送快捷方式到桌面待用。

ADS JLINK裸机仿真实验手册

准备实验

一、硬件

1.Fl2440或者TE2440开发板一套

2.JLINK仿真器一个

二、软件

1.裸机实验代码,init.axf文件

2.ADS1.2开发环境

3.JLINK驱动

实验步骤

一、将JLINK与开发板和PC机连接到一起,这时可以看到JLINK上的电源指示灯亮了

二、打开AXD软件

(三)加载JLINK驱动,单机Options-》Configue Target如下所示(如果没有安装JLINK 驱动请参考开发板准备实验必读手册【实验四JLINK驱动安装】)

(四)点击“OK”后会有如下画面显示:

五、给开发板上电,按下面操作进行

六、点击Load Image后会有如下界面,选择2440init.axf文件,文件路径为:X:\FL2440\Bootloader\目标文件\2440init.axf

找到2440init.s文件,打开

七、点击“运行”让软件跑一会儿,然后点击“停止”,如下图所示

八、按下图所示操作

九、实验源码路径为X:\实验指导&demo\ADS基础实验\实验源码\1.3-led

向上查找init.s源文件,添加

点击“运行”,程序开始运行,如下所示,然后,点击“停止”

点击“运行”,出现如下界面,观察开发板的led灯,第一个已经点亮,稍微多等一会第二个灯也会点亮,这样流水灯的程序演示完毕,你可以根据自己的需求任意改动程序,开发属于自己的led灯。

这里只讲步骤和方法,没有贴具体的源码出来。

首先复制一份光盘里面的无OS测试程序,命名为:led,我们要实现点

亮LED灯的实验。

1、删除src目录下面的除去2440addr.inc,2440init.s,2440lib.c,2440slib.s,Memcfg.inc,Option.inc,mian.c之外的所有文件。

(这里还需要nand.c以及相应的*.h头文件)

2、然后将2440addr.inc,2440init.s,2440lib.c,2440slib.s,

Memcfg.inc,Option.inc复制到新建立的lib目录下。

3、修改main.c文件,在里面的main函数中实现点亮LED的C语言的

代码。

4、建立一个ADS下的项目,添加上刚刚剩余的文件,然后编译。

会有两个主要的错误:

1、undefined symbol RdNF2SDRAM(这个在nand.c文件里有函数定义)

2、undefined symbol PCLK(参考TQ2440_Test.rar里的文件发现PCLK

在option.h里通过GLOBAL_CLK来定义,参考其main.c里发现第一行里有宏定义#define GLOBAL_CLK 1,故需要在自己的main.c文件添加宏定义才可以,但是注意一定要在第一行才能编译通过!)

注意:这样编译肯定会有很多错误的,我们需要根据错误修改对应的文件,其实就是因为剩余的这几个文件还保留了以前的信息所致,简单删除操作就可以解决。

5、编译OK之后,使用uboot的a功能烧写镜像到Nand Flash,然后重启即可。