小数分频器的verilog-hdl设计

- 格式:docx

- 大小:79.89 KB

- 文档页数:4

第24卷 增刊2005年9月国 外 电 子 测 量 技 术Foreign Elect ronic Measurement TechnologyVol.24,Suppl.Sep.,2005作者简介: 尹佳喜(1981-),华中科技大学电气与电子工程学院04级研究生,研究方向电力电子与电力传动。

研究与设计小数分频器的设计及其应用尹佳喜(华中科技大学电气与电子工程学院 湖北武汉430074)摘要:分频器是数字系统设计中最常见的电路之一,在数字系统设计中,经常需要对时钟进行小数倍分频。

本文给出了三种用于实现小数分频的方案,并将三种方案进行了比较。

在此基础上,介绍了小数分频器在直接数字频率合成技术和步进电机驱动速度控制中的两种常见应用。

关键词:小数分频器 直接数字频率合成 步进电机 频率The Design and Application of Decim al Fraction Frequency DividerY in Jiaxi(College of Elect ricit y and Elect ronic Engeneering ,H uaz hong Universit y of S cience and Techlonog y ,W uhan 430074,China )Abstract :Frequency division is one of t he mo st common circuit s in t he design of digital system.Generally ,decimal f raction f requency division is needed.In t his paper ,t hree met hods to realize deci 2mal f raction frequency division are given ,and t he comparison among t he t hree met hods is presented.Applications of decimal Fraction Frequency divider in t he area such as direct digital f requency syn 2t hesis technology and stepper motor drive speed controller are int roduced.K eyw ords :decimal f raction frequency divider ,direct digital frequency synt hesis (DDS ),stepper mo 2tor ,frequency.0 引言 现代电子系统设计中,数字电子系统所占的比例越来越大,现代电子系统发展的趋势是数字化和集成化。

Verilog实现任意分频在Verilog中实现任意分频可以通过使用计数器和分频比例来实现。

下面是一个基于计数器的Verilog代码示例,用于实现任意分频。

```verilogmodule frequency_dividerinput clk,input rst,input [7:0] div_ratio,output reg outreg [7:0] count;beginif (rst)count <= 0;else if (count == div_ratio - 1)count <= 0;elsecount <= count + 1;endbeginif (rst)out <= 0;else if (count == div_ratio - 1)out <= ~out;endendmodule```在以上代码中,我们定义了一个名为"`frequency_divider`"的模块,该模块具有以下输入和输出:- `clk`:时钟信号- `rst`:复位信号- `div_ratio`:分频比例,使用8位二进制表示,范围为0到255- `out`:输出信号我们使用一个8位计数器(`count`)来进行分频。

每当计数器达到分频比例减1时,输出信号取反。

例如,如果分频比例为1,则输出信号将与时钟信号同步;如果分频比例为2,则输出信号将是时钟信号的一半频率;如果分频比例为4,则输出信号将是时钟信号的四分之一频率,以此类推。

需要注意的是,以上示例代码仅展示了分频的基本原理,并未考虑输入和输出信号的时序问题,如使 `div_ratio` 在运行时可更改、输出信号的不稳定性等。

针对具体应用需求,可以根据实际情况做出适当的修改和调整。

希望以上内容对您有所帮助!。

河南工程学院《EDA》课程设计系别电气信息工程系专业电子科学与技术班级0941班组员基于Verilog HDL数字频率计设计与实现摘要:在电子技术中,频率是最基本的参数之一,并且与许多电参量的测量方案、测量结果都有十分密切的关系,因此频率的测量就显得更为重要。

测量频率的方法有多种,其中电子计数器测量频率具有精度高、使用方便、测量迅速,以及便于实现测量过程自动化等优点,是频率测量的重要手段之一。

电子计数器测频有两种方式:一是直接测频法,即在一定闸门时间内测量被测信号的脉冲个数;二是间接测频法,如周期测频法。

直接测频法适用于高频信号的频率测量,间接测频法适用于低频信号的频率测量。

本文阐述了用Verilog HDL语言设计了一个简单的数字频率计的过程关键词:周期;EDA;Verilog HDL;数字频率计;波形仿真目录1 引言......................................................... - 3 -1.1 数字频率计概述.......................................... - 4 -1.2 频率测量的思想和方法.................................... - 4 -2 Verilog HDL简介............................................. - 6 -2.1 Verilog HDL的简介....................................... - 6 -2.2方案比较 (10)3 数字频率计设计原理以及实现................................... - 7 -4 总结......................................................... - 38 - 参考文献....................................................... - 39 -1 引言在电子测量领域中,频率测量的精确度是最高的,可达10—10E-13数量级。

0引言在数字电路中,时钟脉冲信号是最重要的信号之一。

一个数字电路往往需要多种频率的脉冲作为驱动,通常采用一个高频晶振产生一种高频率的脉冲,再利用其它的分频方法进行分频,从而产生各种不同频率的脉冲,是一种常用的方法。

本文设计的分频器是采用Verilog HDL硬件描述语言,采用参数化的设计思想,在FPGA上实现的一种软件化的分频器,且该分频器仅占用FPGA的几个逻辑单元。

1通用分频器的设计分频器分为偶数分频、奇数分频、半整数分频和小数分频等,本文采用参数化的设计思想设计偶数分频器。

所谓参数化就是把程序中的某些参数设计成可以改变的量,使用户可以根据需要设定参数的值,以满足不同的需求。

1.1分频原理在设计偶数分频器时,采用通过一个由待分频时钟上升沿所触发的计数器循环计数来实现N倍(N为偶数)分频的实现方法,这种方法可以实现占空比为50%的任意偶数分频。

1.2设计方法在FPGA上,可以采用两种不同的Verilog HDL程序语句来设计计数器。

用这两种程序语句设计的计数器功能相同,但其实现方式不同,程序结构也不一样。

所以这两种程序语句编译综合后,它们占用的逻辑单元LE数差别很大。

本文对这两种程序语句进行了分析,比较了它们所占用的逻辑单元数的差别,并对产生这种差别的原因进行了分析。

(1)方法1module FPQ_1(CLK,OUT);input CLK;output OUT;parameter bitsize=4;//计数器二进制位数parameter L=9;//1/2倍的计数基数减1reg[bitsize:0]count=0;reg OUT=0;reg counter;always@(posedge CLK)begincount=(count<L)(count+1):0;//计数counter=(count==L)1:0;用Verilog HDL实现基于FPGA的通用分频器的设计Design of General Frequency Divider Based on FPGA Using Verilog HDL罗浩1许艳1,2仲佳嘉3Luo Hao Xu Yan Zhong Jiajia(1.江西理工大学应用科学学院,江西赣州341000;2.武汉理工大学信息学院,湖北武汉430070;3.江西赣州供电公司通信自动化分公司,江西赣州341000)(1.College of Applied Science,Jiangxi Univ.of Science&Technology,Jiangxi Ganzhou341000;2.School of Information Engineering,Wuhan Univ.of Technology,Hubei Wuhan430070;3.Branch of Communication and Automatization,JiangxiGanzhou Electric Power Corporation,Jiangxi Ganzhou341000)摘要:在数字逻辑电路设计中,常常遇到一些对时钟分频的需求。

你好,使用以下程序即可,使用时只需改变N值,N的取值大小请看注释,此程序适合对任意时钟的整数分频(包括奇偶),此程序已通过验证。

根据你的情况,想得到1HZ,N取50000000即可;想得到5HZ,N取10000000即可。

/****************************************************************************** ************Function: 实现时钟的任意整数分频******************************************************************************* *************/module div_N(inputCLK,// 基准时钟outputCLK_div_N// N分频后得到的时钟);wire[31:0]N=20;// N为分频系数,N≥2即可,N的值为CLK除以CLK_div_N后取整(四舍五入) /******************** 产生备用时钟1 ***************/reg[31:0]cnt1;regCLK_div_N_1;always @ (posedge CLK)beginif(N%2==0)// 如果N为偶数beginif(N==2)// 如果N为2CLK_div_N_1 <= ~CLK_div_N_1;elsebeginif(cnt1==(N-2)/2)begincnt1 <= 0;CLK_div_N_1 <= ~CLK_div_N_1;endelsecnt1 <= cnt1+1;endendelse// 如果N为奇数beginif(cnt1==N-1)cnt1 <= 0;elsecnt1 <= cnt1+1;if((cnt1==N-1) || (cnt1==(N-1)/2))CLK_div_N_1 <= ~CLK_div_N_1;else ;endend/*********************** 产生备用时钟2 *********************/wireCLK0=(N%2)? (~CLK):0;// 如果N为偶数,备用时钟2(CLK_div_N_2)恒为0,即不需要用到此备用时钟reg[31:0]cnt2;regCLK_div_N_2;always @ (posedge CLK0)beginif(cnt2==N-1)cnt2 <= 0;elsecnt2 <= cnt2+1;if((cnt2==N-1) || (cnt2==(N-1)/2))CLK_div_N_2 <= ~CLK_div_N_2;end/******************** 产生最终分频时钟************************/assignCLK_div_N = CLK_div_N_1 | CLK_div_N_2;endmodule。

实验六Verilog设计分频器/计数器电路一、实验目的1、进一步掌握最基本时序电路的实现方法;2、学习分频器/计数器时序电路程序的编写方法;3、进一步学习同步和异步时序电路程序的编写方法。

二、实验内容1、用Verilog设计一个10分频的分频器,要求输入为clock(上升沿有效),reset(低电平复位),输出clockout为4个clock周期的低电平,4个clock周期的高电平),文件命名为fenpinqi10。

v.2、用Verilog设计一异步清零的十进制加法计数器,要求输入为时钟端CLK(上升沿)和异步清除端CLR(高电平复位),输出为进位端C和4位计数输出端Q,文件命名为coute r10.v。

3、用Verilog设计8位同步二进制加减法计数器,输入为时钟端CLK(上升沿有效)和异步清除端CLR(低电平有效),加减控制端UPDOWN,当UPDOWN为1时执行加法计数,为0时执行减法计数;输出为进位端C和8位计数输出端Q,文件命名为couter8.v。

4、用VERILOG设计一可变模数计数器,设计要求:令输入信号M1和M0控制计数模,当M1M0=00时为模18加法计数器;M1M0=01时为模4加法计数器;当M1M0=10时为模12加法计数器;M1M0=11时为模6加法计数器,输入clk上升沿有效,文件命名为mcout5。

v。

5、VerilogHDL设计有时钟时能的两位十进制计数器,有时钟使能的两位十进制计数器的元件符号如图所示,CLK是时钟输入端,上升沿有效;ENA是时钟使能控制输入端,高电平有效,当ENA=1时,时钟CLK才能输入;CLR是复位输入端,高电平有效,异步清零;Q[3.。

0]是计数器低4位状态输出端,Q[7..0]是高4位状态输出端;COUT是进位输出端.三、实验步骤实验一:分频器1、建立工程2、创建Verilog HDL文件3、输入10分频器程序代码并保存4、进行综合编译5、新建波形文件6、导入引脚7、设置信号源并保存8、生成网表9、功能仿真10、仿真结果分析由仿真结果可以看出clockout输出5个clock周期的低电平和5个clock的高电平达到10分频的效果,设计正确。

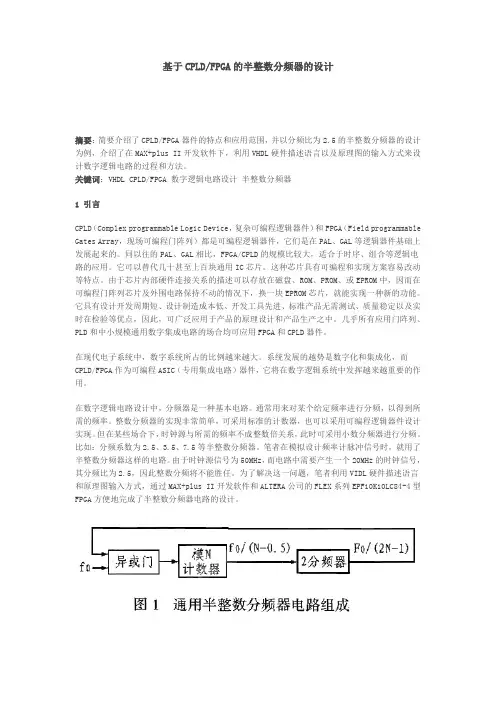

基于CPLD/FPGA的半整数分频器的设计摘要:简要介绍了CPLD/FPGA器件的特点和应用范围,并以分频比为2.5的半整数分频器的设计为例,介绍了在MAX+plus II开发软件下,利用VHDL硬件描述语言以及原理图的输入方式来设计数字逻辑电路的过程和方法。

关键词:VHDL CPLD/FPGA 数字逻辑电路设计半整数分频器1 引言CPLD(Complex programmable Logic Device,复杂可编程逻辑器件)和FPGA(Field programmable Gates Array,现场可编程门阵列)都是可编程逻辑器件,它们是在PAL、GAL等逻辑器件基础上发展起来的。

同以往的PAL、GAL相比,FPGA/CPLD的规模比较大,适合于时序、组合等逻辑电路的应用。

它可以替代几十甚至上百块通用IC芯片。

这种芯片具有可编程和实现方案容易改动等特点。

由于芯片内部硬件连接关系的描述可以存放在磁盘、ROM、PROM、或EPROM中,因而在可编程门阵列芯片及外围电路保持不动的情况下,换一块EPROM芯片,就能实现一种新的功能。

它具有设计开发周期短、设计制造成本低、开发工具先进、标准产品无需测试、质量稳定以及实时在检验等优点,因此,可广泛应用于产品的原理设计和产品生产之中。

几乎所有应用门阵列、PLD和中小规模通用数字集成电路的场合均可应用FPGA和CPLD器件。

在现代电子系统中,数字系统所占的比例越来越大。

系统发展的越势是数字化和集成化,而CPLD/FPGA作为可编程ASIC(专用集成电路)器件,它将在数字逻辑系统中发挥越来越重要的作用。

在数字逻辑电路设计中,分频器是一种基本电路。

通常用来对某个给定频率进行分频,以得到所需的频率。

整数分频器的实现非常简单,可采用标准的计数器,也可以采用可编程逻辑器件设计实现。

但在某些场合下,时钟源与所需的频率不成整数倍关系,此时可采用小数分频器进行分频。

比如:分频系数为2.5、3.5、7.5等半整数分频器。

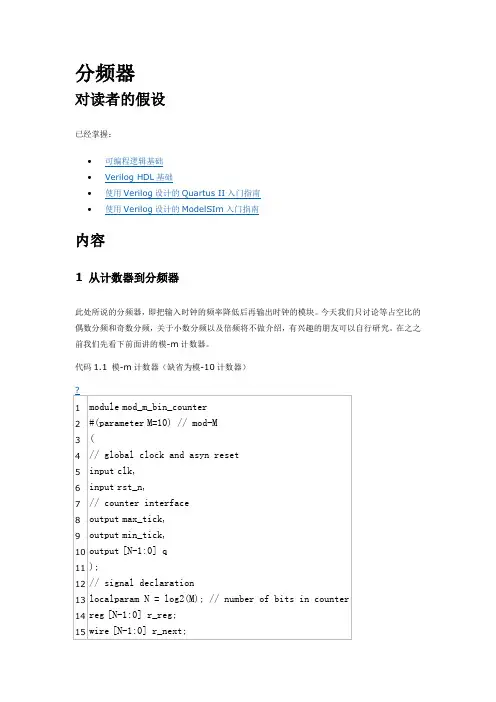

分频器对读者的假设已经掌握:∙可编程逻辑基础∙Verilog HDL基础∙使用Verilog设计的Quartus II入门指南∙使用Verilog设计的ModelSIm入门指南内容1 从计数器到分频器此处所说的分频器,即把输入时钟的频率降低后再输出时钟的模块。

今天我们只讨论等占空比的偶数分频和奇数分频,关于小数分频以及倍频将不做介绍,有兴趣的朋友可以自行研究。

在之之前我们先看下前面讲的模-m计数器。

代码1.1 模-m计数器(缺省为模-10计数器)根据这个模-m计数器,我们再写一个testbench。

代码1.2 模m-计数器的testbench(重新配置为模-10计数器)但是我在使用Quartus II + Modelsim_Altera仿真的时候出现了下面的错误提示。

代码2的第10行,变量N未定义,然后第11行用N来索引的q数组也没有定义。

奇怪了,我在Quartus II都能综合通过,而且RTL视图也是正确的,为什么Modelsim_Altera就不可以这样定义呢?咳,把常量(localparam)换成参数(parameter)即可。

代码1.3 改进后的模-m计数器(重新配置为模-10计数器)修改完,在Quartus II 里再综合一下。

接下来就是按照[文档].艾米电子 - 使用Verilog 设计的Quartus II入门指南再做一次仿真。

告诉大家一个技巧,如果执行完一次RTL 级或门级的仿真,那么Quartus II 会为我们的主模块及其testbench生成do 文件的。

这样假如有错误,就无需重新启动Modelsim_Altera ,只需重新load 一下do 文件即可。

(路径格式:Quarter II 工程文件夹\simulation\modelsim \mod_m_bin_counter_run_msim_rtl_verilog.do ) 下面看下RTL 级仿真波形。

下面讨论一下如何测量波形的长度,我们注意两个工具。

小数分频器的设计摘要:通过小数分频器的基本实现原理进行小数分频器主模块的设计与实现。

程序用VHDL硬件描述语言设计,在MAX+ plus Ⅱ开发软件下分析编译并进行仿真调试。

关键词:小数分频,VHDL一、小数分频的基本原理:小数分频器的功能就是当在输入端给定不通输入数据时,将对输入的时钟信号有不同的分频比,即对较高频率的信号分频,以得到所需要的低频信号。

小数分频器的实现方法很多, 但其基本原理一样,即在若干个分频周期中采取某种方法使某几个周期多计或少计1 个数, 即吞脉冲或插入脉冲的方法,从而在平均意义上获得1 个小数分频比,设要进行分频比为N 的小数分频, N 可表示为N = K + 10- nX式中, n , K, X 均为正整数; n 为到X 的位数,即N 有n 位小数。

另一方面,分频比又可以写成:N = M/ P式中:M 为分频器输入脉冲数; P 为输出脉冲数。

M = N P = ( K + 10- nX) P令P = 10 n ,则有M = 10 nK + X以上是小数分频器的一种实现方法, 即在进行10 nK 次分频时,设法多输入X 个脉冲。

二、仿真软件:MAX-plusⅡ。

可识别编译AHDL,VHDL,V erilog hdl等硬件语言。

三、设计的小数分频器主模块:设计(一):1、源代码:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY ClkDivy ISPORT(clk:IN STD_LOGIC;clkdivp:OUT STD_LOGIC);END ClkDivy;ARCHITECTURE rtl OF ClkDivy ISCONSTANT md :STD_LOGIC_VECTOR(1 DOWNTO 0):="10";SIGNAL counter :STD_LOGIC_VECTOR(1 DOWNTO 0);SIGNAL tmpclk :STD_LOGIC;SIGNAL clkdiv5 :STD_LOGIC;SIGNAL tmpdiv2p5 :STD_LOGIC;BEGINp1:PROCESS(tmpclk)BEGINIF(tmpclk'event AND tmpclk='1')THENIF(counter="00")THENcounter<=md;tmpdiv2p5<='1';ELSEcounter<=counter-1;tmpdiv2p5<='0';END IF;END IF;END PROCESS p1;p2:PROCESS(tmpdiv2p5)BEGINIF(tmpdiv2p5'event AND tmpdiv2p5='1')THENclkdiv5<=NOT clkdiv5;END IF;END PROCESS p2;tmpclk<=clk XOR clkdiv5;clkdivp<=tmpdiv2p5;END rtl;2、生成的模块文件图3、仿真时序图:设计(二)1.源代码:library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;entity HalfDivy isport(Inclk : in std_logic;Preset : in std_logic_vector(3 downto 0);Outclk : buffer std_logic);end HalfDivy;architecture Behavioral of HalfDivy issignal clk,divclk : std_logic := '0';signal count : std_logic_vector(3 downto 0) := "0000"; beginclk <= Inclk xor divclk;process(clk)beginif(clk'event and clk = '1') thenif(count = "0000") thencount <= preset-1;Outclk <= '1';elsecount <= count-1;Outclk <= '0';end if;end if;end process;process(Outclk)beginif(Outclk'event and Outclk='1') thendivclk<=not divclk;end if;end process;end Behavioral;2、生成的模块文件图3、仿真时序图:四:总结分频器完成对输入信号的整数或半整数分频功能,当然这只是分频器主模块,我们还要相应设计输入信号产生模块,控制模块等等,从而实现不同需要的信号分频,得到所需频段信号理想的效果。

基于Verilog HDL数字频率计设计与实现课程设计任务书学院:计算机与通信工程学院专业:网络工程专业课程名称计算机组成原理课程设计时间2010~2011学年第一学期17~18周学生姓名郭祥斌指导老师陈沅涛题目主要内容:(1)数字频率计前端信号的放大整形处理(2)数字频率计的Verilog HDL设计实现(3)数字频率计的CPLD/FPGA制作要求:(1)通过对相应文献的收集、分析以及总结,给出相应课题的背景、意义及现状研究分析。

(2)通过课题设计,掌握计算机组成原理的分析方法和设计方法。

(3)学按要求编写课程设计报告书,能正确阐述设计和实验结果。

(4)学生应抱着严谨认真的态度积极投入到课程设计过程中,认真查阅相应文献以及实现,给出个人分析、设计以及实现。

应当提交的文件:(1)课程设计报告。

(2)课程设计附件(主要是源程序)。

课程设计成绩评定学院计算机通信工程专业网络工程班级网络08-02 班学号200858080223 学生姓名郭祥斌指导教师陈沅涛课程成绩完成日期2010年12月31日指导教师对学生在课程设计中的评价评分项目优良中及格不及格课程设计中的创造性成果学生掌握课程内容的程度课程设计完成情况课程设计动手能力文字表达学习态度规范要求课程设计论文的质量指导教师对课程设计的评定意见综合成绩指导教师签字年月日基于Verilog HDL数字频率计设计与实现学生:郭祥斌指导老师:陈沅涛摘要:在电子技术中,频率是最基本的参数之一,并且与许多电参量的测量方案、测量结果都有十分密切的关系,因此频率的测量就显得更为重要。

测量频率的方法有多种,其中电子计数器测量频率具有精度高、使用方便、测量迅速,以及便于实现测量过程自动化等优点,是频率测量的重要手段之一。

电子计数器测频有两种方式:一是直接测频法,即在一定闸门时间内测量被测信号的脉冲个数;二是间接测频法,如周期测频法。

直接测频法适用于高频信号的频率测量,间接测频法适用于低频信号的频率测量。

分频器设计一、实验目的1、熟悉分频器的原理;2、掌握采用Verilog HDL 语言设计分频器的方法;3、进一步学习利用VerilogHDL 语言进行层次设计的方法。

二、实验内容1、采用Verilog 语言设计一个十分频器,记录Verilog 程序;2、对十分频器进行功能仿真,观察仿真波形;3、仿真没有问题后,将分频比改为50000000,实现一个50M 分频器。

利用此分频器和开发板上的50MHz 时钟信号,得到1Hz 的秒脉冲信号,完成如图1-2.28所示的秒计数器。

50M分频器50MHz 脉冲信号二位十进制计数器1Hz 秒脉冲数码管(个位)数码管(十位)复位和计数使能(拨码开关)程序设计如下:module fenp(clk_out,clk_in,reset);output clk_out;input clk_in;input reset;reg [1:0] cnt;reg clk_out;always@(posedge clk_in or posedge reset)beginif(reset)begincnt<=0;clk_out<=0;endelsebeginif(cnt==24999999)beginclk_out<=!clk_out;cnt<=0;endelsecnt<=cnt+1;endendendmodule本程序经验证,完全可以实现实验要求。

文章来自某大学EDA实验课。

远程FPGA虚拟实验平台⽤SystemVerilogHDL实现计数器和分频器远程FPGA虚拟实验平台⽤SystemVerilog HDL实现计数器和分频器原理计数器本实验中,材料给出的计数器是⼆进制来分频的,就搞得还挺⿇烦。

/** The input port is replaced with an internal signal **/wire reset =PB[0];wire clk;/************* The logic of this experiment *************/logic [23:0] count;always@(posedge CLOCK or posedge reset)beginif(reset)count <=0;elsecount <= count+1;endassign clk = count[22];//2^23,详解见下⽅logic [7:0]q;always @ (posedge clk or posedge reset)if(reset)q <=1;elseq <={q[6:0], q[7]};/****** Internal signal assignment to output port *******/assign L[7:0]= q[7:0];endmodule由代码可知,在CLOCK输出2个信号后,clk=1,然后CLOCK需要再输出2个信号,使clk=0。

这个过程的时间是2(次)/10M(次/秒),约为838毫秒。

测试界⾯的刷新间隔T实际上是,每隔T时间显⽰⼀下虚拟实验⾯板当前的情况,如果在测试时刷新间隔T=1000ms,会使得刷新不完全按照分频器转换后的频率来,所以刷着刷着就跳过了某⼏次,这个“某⼏次”是可以算的,但是我懒得算。

也就是说,只要刷新间隔T<=838ms就能让每个灯都亮了,但是如果不是838的倍数,灯亮的时候就不匀速,有点抽风。

小数分频频率合成器中Σ-Δ调制器设计与实现晏敏;徐欢;乔树山;杨红官;郑乾;戴荣新;程呈【摘要】介绍了一种应用于小数分频频率合成器的Σ-Δ调制器的设计,该调制器采用三阶级联的MASH1-1-1结构,并利用流水线技术,提高了调制器的工作频率.电路设计采用Verilog HDL硬件描述语言实现,基于QuartusⅡ工具进行测试验证,结果表明,调制器最高工作频率为240.56 MHz.最终采用SMIC 0.18μm CMOS 工艺,完成了电路版图设计.芯片面积为34148.5μm2,芯片总功耗为1.284 mW,与传统设计相比,面积降低了31.23%,功耗降低了46.14%.%This paper presented a design and implementation study of a three-order all-digital MASHΣ-Δmodulator,which can be used in Fractional-N Frequency Synthesizer applications.To achieve the de-sired operation frequency while providing low-power dissipation and small area,the pipelining technique was utilized in the design.The circuit was described by using the Verilog hardware description language, and the operating frequency of the modulator is 240.56 MHz based on QuartusⅡ.Eventually,the SMIC 0.18μm CMOS process was adopted,and the circuit layout was completed.The chip's area is 34148.5μm2 ,and the total power of the chip is 1.28 pared with traditional design,it can result in a 31. 23% area reduction and 46.14% power reduction.【期刊名称】《湖南大学学报(自然科学版)》【年(卷),期】2014(000)010【总页数】5页(P91-95)【关键词】调制器;频率合成器;MASH1-1-1;流水线技术;CMOS【作者】晏敏;徐欢;乔树山;杨红官;郑乾;戴荣新;程呈【作者单位】湖南大学物理与微电子科学学院,湖南长沙 410082;湖南大学物理与微电子科学学院,湖南长沙 410082; 中国科学院微电子研究所,北京 100029;中国科学院微电子研究所,北京 100029;湖南大学物理与微电子科学学院,湖南长沙 410082;湖南大学物理与微电子科学学院,湖南长沙 410082;湖南大学物理与微电子科学学院,湖南长沙 410082;湖南大学物理与微电子科学学院,湖南长沙 410082【正文语种】中文【中图分类】TN74频率合成器是无线通信射频前端的一个关键模块,其作用是为收发机射频前端产生频率源,进行频率变换和信道选择[1].随着无线通信、数字电视、物联网等现代高科技技术的广泛应用和不断发展,对频率源的频率稳定度、频谱纯度和输出频率的精度要求越来越高,因此对频率合成器的性能要求也越来越高[2].在频率合成器中,分频器是一个非常重要的模块,它是频率合成器能提供多个高精度频率信号并同时实现高频低功耗工作的关键和前提[3].因此,对频率合成器中分频器的研究、设计与实现有重要的现实意义和工程应用价值.传统的频率合成器中分频器为整数分频结构,为了能产生相邻且频率间隔较小的信道频率,要求参考频率较小,分频系数较大,因此抗噪能力差[4].基于Σ-Δ调制器技术的小数分频可以获得较高频率分辨率和极低的相位杂散,方便实现各种数字调制.本文采用MASH1-1-1结构,运用流水线技术,采用Verilog硬件描述语言,设计完成了一款应用于小数分频频率合成器的Σ-Δ调制器的设计;采用Verilog 硬件描述语言进行描述,最终采用SMIC 0.18μm CMOS工艺,完成了电路版图.1 小数N分频频率合成器小数N分频频率合成器的电路如图1所示,电路由鉴频鉴相器(Phase Frequency Detector,PFD)、电荷泵(Charge Pump,CP)、环路滤波器(Loop Filter,LPF)、压控振荡器(Voltage Control Oscillator VCO)及分频器构成.外部输入的参考频率与VCO经过分频后的频率进行比较,输出产生的相位差函数作用于电荷泵,经过环路滤波器滤除高频分量和噪声,成为压控振荡器的控制电压,通过不断反复调整,输出稳定的FVCO,达到锁定状态[5].图1 小数分频频率合成器结构图Fig.1 The structure of fractional-N frequency synthesizer传统小数分频利用相位累加器进行设计,提高了分频器的分辨率,但同时给环路输出带来了信噪比低、输出频率的相位扰动增加等问题.为了获得良好的频率输出,Σ-Δ调制概念被引入小数分频器设计中,从而可获得高质量的小数平均功率输出.2 Σ-Δ调制器2.1 一阶Σ-Δ调制器一阶数字Σ-Δ调制器的Z域数学模型如图2所示[6],可推算出传输函数为:式中:F(Z)为调制器小数部分输入;Eq1(Z)为量化噪声[7].图2 一阶Σ-Δ调制器Z域模型Fig.2 The Zmodel of first-orderΣ-Δmodulator从传输函数可看出,(1-Z-1)项对量化噪声呈现出高通特性,可将由小数分频引起的量化噪声推向高频,再通过一个低通滤波器将噪声加以滤除,使得量化噪声对输出几乎没有影响.同时Σ-Δ调制器的输出为一个随机序列,受其控制的分频比也呈现随机性,从而保证了环路相位误差的随机性,消除了VCO控制电压的低频交流成分,减少了小数杂散[8].2.2 MASH1-1-1Σ-Δ 调制器基于一阶的Σ-Δ调制器的频率合成器由于小数毛刺的影响很难在实际产品中得到应用,为了避免稳定性的问题而又能获得很好的噪声整形性能,可以通过将一阶和二阶的调制器级联,这就是Multi-Stage-Noise-Shaping(MASH)型调制器.MASH结构相对于单环结构更稳定,动态范围与阶数无关,更易采用流水线工作方式.级联的高阶Σ-Δ调制器可以将噪声推向高频处,再通过环路滤波器进行低通滤波,滤掉高频噪声,从而达到噪声整形的目的[9].Σ-Δ调制器的阶数越高,噪声整形效果越好,然而随着阶数的提高,引入的量化噪声功率总量也增加,需要高阶环路滤波器来抑制它的高频噪声.一般情况下,2阶或者3阶Σ-Δ调制器就足以满足小数频率合成器的要求[10].MASHΣ-Δ调制器一般由累加器结构的一阶调制器级联构成,也称MASH1-1-1结构.等效模型如图3所示,可以得出其传输函数:图3 三阶 MASH1-1-1调制器结构Fig.3 The structure of three-order MASH1-1-1modulator因此,高阶MASH调制器的噪声传输函数是阶数为3的高通滤波函数.在Z平面上,该噪声传输函数包含3个位于原点的极点和3个位于单位圆上的零点.同时,此调制器对输入信号只是起到原样保持的作用,因此不影响预先设置的平均分频比.在小数频率合成器中,有因此,可以得出:式(7)右边,第一部分是所需要的频率,第二部分是由于量化而引起的噪声,这个噪声会在输入VCO之前被低通滤波器滤除[11].3 Σ-Δ调制器的设计与实现图4为MASH调制器的具体电路结构.累加器由16-bit流水线加法器和16-bit 寄存器组成.可以看出进位溢出要经过一个比较长的延时链,因此,需要使用一个1-bit寄存器以保证信号的同步[12].噪声整形电路是为了消除前两级的量化噪声,提高了Σ-Δ调制器的性能[13].图4 三阶MASH1-1-1调制器电路实现Fig.4 The circuit of three-order MASH1-1-1modulator16-bit加法器可以采用16-bit的全加器实现,然而较长进位输出会降低整个设计的工作频率.为了提高工作频率,采用4个级联的超前进位加法器(Carry-Look-Ahead,CLA)代替16-bit的加法器,以更快地产生进位.然而,随着位宽的增加,硬件消耗也呈指数级增加.解决的办法就是采用流水线技术,只需在CLA之间插入一个1-bit寄存器[14].在常规的流水线加法器结构中,每级CLA输入需要额外添加寄存器与实际输入同步,同时输出也要添加寄存器来保证与输入同步,但由于Σ-Δ调制器的输入为固定值,可以将这些寄存器去除,而不会影响电路功能.图5为 MASH1-1-1的噪声整形电路.电路实现公式(8)的功能.图5 MASH1-1-1噪声整形电路Fig.5 The noise-shaping circuit of MASH1-1-14 结果分析当整数分频输入为FP=8,小数分频输入IP=2 772时,目标分频比可以计算得出为8.042 3,程序仿真结果如图6所示.将输出结果d_out导出求出其平均值为8.042 3,与目标分频比一致,调制器功能正确.同时基于CycloneⅢ的EP3C5E144C7,对设计用QuratusⅡ进行验证,结果表明:最大工作频率为240.56MHz,与未采用流水线技术最大工作频率200.03MHz相比有较明显的提升.图6 Modelsim仿真波形Fig.6 The waveform based Modelsim同时芯片采用中芯国际SMIC 0.18μm的数字CMOS工艺,完成Σ-Δ调制器电路版图如图7所示,图中实线框为Σ-Δ调制器部分,芯片面积为34 148.5μm2,芯片总功耗为1.284mW.表1为本文设计与已有文献的比较结果.由于工艺条件不同,面积利用工艺库下单个与非门的面积进行归一化,功耗利用公式(9)将功耗进行归一化[15].式中Pori为归一化前的功耗,Vcc为供电电压.从表中可以得出面积降低了31.23%,功耗降低了46.14%.图7 芯片电路版图Fig.7 The layout of the chip表1 和已有文献的比较结果Tab.1 Comparison with existing arts?5 结束语本文提出了一种应用于小数分频频率合成器中的三阶 MASH1-1-1Σ-Δ调制器的结构,采用Verilog实现,采用流水线技术,提高了工作频率,同时采用SMIC 0.18μm工艺,完成电路版图,芯片面积为34 148.5μm2,总功耗为1.284mW,与传统设计相比,面积降低了31.23%,功耗降低了46.14%.同时该设计具有设计简单、面积小、功耗低、方便实现等优点,已用于基于小数分频频率合成器的无线低功耗收发芯片中.参考文献[1]SLEIMAN S B,ATALLAH J G,RODRIGUEZ S,et al.OptimalΣ-Δmodulator architectures for fractional-N frequency synthesis[J].IEEE Transactions on Very Large Scale Integration Systems,2010,18(2):194-200.[2]吴小林,朱学勇.锁相环小数N分频频率合成器中的Sigmadelta调制器设计[J].器件与应用,2011,35(17):55-58.WU Xiao-lin,ZHU Xue-yong.Design of sigma-delta modulator in fractional-N PLL frequency synthesizer[J].Parts & Applications,2011,35(17):55-58.(In Chinese)[3]刘德建.频率合成器中Σ-Δ调制器的设计与实现[J].计算机工程与科学,2009,31(12):121-123.LIU De-jian.Design and implementation of a sigma-delta modulator in the frequency synthesizer[J].Computer Engineering&Science,2009,31(12):121-123.(In Chinese)[4]FATAHI N,NABOVATI H.Design of low noise fractional-N frequency synthesizer using sigma-delta modulation technique[C]//Proceedings of 27th International Conference on Microelectronics.New York:IEEE,2010:369-372.[5]ZANUSO M,LEVANTINO S,SAMORI C,et al.A wideband 3.6GHz digitalΔΣfractional-N PLL with phase interpolation divider and digital spur cancellation[J].IEEE Journal of Solid-State Circuits,2011,46(3):627-638.[6]石立春,杨银汤.高精度Sigma-delta调制器系统设计与仿真[J].湖南大学学报:自然科学版,2010,37(5):54-59.SHI Li-chun,YANG Yin-tang.Systematic design and simulation of a high resolution sigma-delta modulator[J].Journal of Hunan University:Natural Sciences,2010,37(5):54-59.(In Chinese)[7]TEMPORITI E,WILTIN-WU C,BALDI D,et al.A 3GHz fractional all-digital PLL with a 1.8MHz bandwidth implementing spur reduction techniques[J].IEEE Journal of Solid-State Circuits,2009,44(3):824-834.[8]唐圣学,何怡刚.基于Σ-Δ调制技术的信号发生器设计[J].湖南大学学报:自然科学版,2007,34(5):44-48.TANG Sheng-xue,HE Yi-gang.Design of signal generation based onΣ-Δmodulator technique [J].Journal of Hunan University:Natural Sciences,2007,34(5):44-48.(In Chinese)[9]ZANUSO M,LEVANTINO S.Time-to-digital converter with 3-ps resolution and digital linearization algorithm [C]//Proceedings of the ESSCIRC.New York:IEEE,2010:262-265.[10]BORREMANS J,VENGATTARAMANE K,GIANNINI V,et al.A86MHz-to-12GHz digital-intensive phase-modulated fractional-N PLL using a 15pJ/shot 5ps TDC in 40nm digital CMOS[C]//Proceedings of 2010IEEE ISSCC.New York:IEEE,2010:480-481.[11]MADOGLIO P,ZANUSO M.Quantization effects in all-digital phase -locked loops[J].IEEE Transactions on Circuits System,2007,51(12):1120-1124.[12]WU Wang-hua,BAI Xue-fei.A 56.4-to-63.4GHz spuriousfree all -digital Fractional-N PLL in 65nm CMOS[C]//Proceedings of2013IEEE International Solid-State Circuits Conference.New York:IEEE,2013:352-354.[13]舒海勇.PLL频率综合器中整数和小数分频器设计与实现[D].南京:东南大学,2010.SHU Hai-yong.Design and realization of integer-N and fractional-N divider in PLL frequency synthesizer[D].Nanjing:Southeast University,2010.(In Chinese)[14]HUANG Y C,WANG Z G,LIU W F,et al.Design of a delta-sigma modulator structured in MASH 2-1-2with dither of error feedback[C]//Proceedings of 2011IEEE International Conference on Applied Superconductivity and Electromagnetic Devices.New York:IEEE,2011:33-36.[15]CHEN Tsan-wen,TSAI Ping-yuan.A sub-nW all-digital signal component separator with branch mismatch compensation for OFDM LINC transmitters[J].IEEE Journal of Solid-State Circuits,2011,46(11):2514-2522.。

Verilog HDL实验报告Verilog 实验报告题目:分频器系部名称:通信工程专业名称:通信工程班级:班内序号:学生姓名:时间:2010.12.12一、实验要求:设计一个将10MHz时钟分频为500KHz的时钟,有复位端;二、实验内容:源文件module fenpin(clr,a,b);input a;input clr;output b;integer i=0;reg b;always @(negedge clr or posedge a)if(!clr)beginb=0;i=0;endelsebegini=i+1;if(i==11)beginb=~b;i=1;endendendmodule测试文件`timescale 10ns/100psmodule fenpin_test;reg a;reg clr;wire b;fenpin u1(clr,a,b);initialbegin$monitor($time,"clr=%b,a=%b,b=%b",clr,a,b);clr=1'b0;a=1'b0;#5 clr=1'b1;endalways#5 a=~a;endmodule# 0clr=0,a=0,b=0 # 5clr=1,a=1,b=0 # 10clr=1,a=0,b=0 # 15clr=1,a=1,b=0 # 20clr=1,a=0,b=0 # 25clr=1,a=1,b=0 # 30clr=1,a=0,b=0 # 35clr=1,a=1,b=0 # 40clr=1,a=0,b=0 # 45clr=1,a=1,b=0 # 50clr=1,a=0,b=0 # 55clr=1,a=1,b=0 # 60clr=1,a=0,b=0 # 65clr=1,a=1,b=0 # 70clr=1,a=0,b=0 # 75clr=1,a=1,b=0 # 80clr=1,a=0,b=0 # 85clr=1,a=1,b=0 # 90clr=1,a=0,b=0 # 95clr=1,a=1,b=1 # 100clr=1,a=0,b=1 # 105clr=1,a=1,b=1 # 110clr=1,a=0,b=1 # 115clr=1,a=1,b=1 # 120clr=1,a=0,b=1 # 125clr=1,a=1,b=1 # 130clr=1,a=0,b=1 # 135clr=1,a=1,b=1三、实验心得:通过本实验,我更加熟悉了Verilog这门语言并能使用ModelSim软件,能自己设计编写一些程序和其测试文件,并将测试结果输出,验证理论的学习,加深理论知识的理解;这样可以更直观形象的理解各种电路器件的工作,有助于今后的学习。

频率合成技术是现代通讯系统的重要组成部分,他将一个高稳定和高准确度的基准频率,经过四则运算,产

生同样稳定度和基准度的频率。分频器是集成电路中最基础也是最常用的电路。整数分频器的实现比较简

单,可采用标准的计数器或可编程逻辑器件设计实现。但在某些场合下,时钟源与所需的频率不成整数倍关

系,此时可采用小数分频器进行分频。本文利用veriloghdl硬件描述语言的设计方式,通过modelsimse开

发软件进行仿真,设计基于fpga的双模前置小数分频器。随着超大规模集成电路的发展,利用fpga小数分

频合成技术解决了单环数字频率合成器中高鉴相频率与小频间隔之间的矛盾。

1双模前置小数分频原理

小数分频器的实现方法很多,但其基本原理一样,即在若干个分频周期中采取某种方法使某几个周期多计或

少计一个数,从而在整个计数周期的总体平均意义上获得一个小数分频比,设要进行分频比为k的小数分

频,k可表示为:

式中:n,n,x均为正整数;n为到x的位数,即k有n位小数。另一方面,分频比又可以写成:

式中:m为分频器输入脉冲数;p为输出脉冲数。

令p=10n,则:

以上是小数分频器的一种实现方法,即在进行10n次n分频时,设法多输入x个脉冲。

2电路组成

每个周期分频n+10-n.x,其电路双模前置小数分频器电路由÷n/n+1双模分频器、控制计数器和控制逻辑

3部分组成。当a点电平为1时,进行÷n分频;当a点电平为0时进行÷n+1分频。适当设计控制逻辑,使

在10n个分频周期中分频器有x次进行÷n+1分频,这样,当从fo输出10n个脉冲时,在fi处输入了

x.(n+1)+(10n-x).n个脉冲,也就是10n.n+x个脉冲,其原理如图1所示。

3小数分频器的verilog-hdl设计

现通?过设计一个分频系数为8.7的分频器来给出使用veriloghdl语言设计数字逻辑电路的一般设计方法。

这里使用÷8/9双模前置分频器,按照前面的分析,可以通过计数器计数先做3次8分频,后做7次9分频,

即可得到平均分频系数8.7。由于从n分频切换到n+1分频和从n+1分频切换到n分频都会产生一个随时

间增长的相位移,如果简单的先进行3次8分频后做7次9分频将会产生很大的相位波动。考虑到该小数

分频器要进行多次8分频和9分频,那么就设法将两种分频混合均匀,这种“均匀”工作是通过计数器来完

成的,在这里只讨论一位小数的情况,下面简要介绍这种混合的方法:

每进行一次分频,计数值为10减去分频系数的小数部分,各次计数值累加。若累加结果小于10,则进行n+1

分频,若大于10或等于10,则进行n分频。该例中计数值为(10-7)=3,前3次累加结果都小于10,所以

为9分频,第四次累加结果为12,则去掉十位数后累加结果变为2,同时进行8分频,表1给出了该分频器的

分频过程。

若分频系数后为两位小数,则用100减去分频系数的小数部分。用veriloghdl设计÷8/9双模前置分频器

的描述程序如下:

4波形仿真

上述的÷8/9双模前置分频器的描述程序经modelsim编译、时序模拟后,得到的波形如图2所示。

由图2可见,当reset为0时,分频器复位,当a为1时,进行8分频,当a为0时则进行9分频。

如图3所示,在前3个时钟,a值为0,则进行9分频,其后一个时钟a为1,进行8分频,后两个脉冲,又进行

9分频,后进行一次8分频,然后又进行两次9分频,最后进行一次8分频。

5电路实现

fpga现场可编程门阵列(fieldprogrammablegatearray)是20世纪80年代中期出现的高密度可编程逻

辑器件。fpga及其软件系统是开发数字电路的最新技术。他利用eda技术,以电路原理图、硬件描述语言、

状态机等形式输入设计逻辑;他提供功能模拟、时序仿真等模拟手段,在功能模拟和时序仿真度满足要求后,

经过一系列的变换,将输入逻辑转换成fpga器件的编程文件,以实现专用集成电路。本设计选用xilinx公

司推出的90nm工艺制造的现场可编程门陈列spartan-3来设计小数分频器,体积减小,可靠性提高。

6结语

采用前置双频分频器设计的小数分频器,小数分频器的精度受控制计数器的影响,当n值为100时,小数分

频的精度达到1/100;当n值为1000时,小数分频的精度达到1/1000;依此类推。fpga有相当丰富的硬件

资源,因此可以用fpga设计高精度的小数分频器。采用fpga组成的数字频率合成器,单环鉴相频率达

100mhz以上,分辨率可达10-6。这种小数分频器得到了广泛的应用,例如,对图象采集系统中的行分频和

列分频的设计,就可以应用本分频器电路作为时钟发生器。