FIR滤波器的FPGA实现方法

- 格式:pdf

- 大小:839.45 KB

- 文档页数:7

vivado fir 原理Vivado FIR滤波器原理FIR(Finite Impulse Response)滤波器是一种常见的数字信号处理滤波器,它的设计和实现对于数字信号的处理非常重要。

Vivado 是一款由Xilinx公司开发的集成电路设计工具,可以用于FPGA (Field-Programmable Gate Array)的设计和实现。

本文将介绍Vivado中FIR滤波器的原理以及相关实现方法。

FIR滤波器是一种线性时不变系统,通过对输入信号进行加权求和来实现滤波效果。

其基本原理是,将输入信号与一组可调节的滤波系数进行卷积运算,得到输出信号。

滤波系数决定了滤波器的特性,可以通过调节系数来实现不同的滤波效果。

在FPGA中,FIR滤波器可以通过硬件电路实现,也可以通过硬件描述语言进行描述并在FPGA上实现。

Vivado中的FIR滤波器实现主要包括以下几个步骤:1. 设计滤波器:在Vivado中,可以使用FIR Compiler来设计FIR 滤波器。

FIR Compiler是Vivado中的一个IP核,可以根据用户定义的滤波器规格自动生成滤波器的硬件描述代码。

用户可以通过设置滤波器的通带频率、阻带频率、过渡带宽等参数来定义滤波器的特性。

2. 生成硬件描述代码:FIR Compiler会根据用户设置的滤波器规格生成相应的硬件描述代码,这些代码描述了滤波器的结构和功能。

可以使用Vivado中的HDL语言(如VHDL或Verilog)来编写这些描述代码。

3. 综合和实现:使用Vivado中的综合工具将硬件描述代码综合为逻辑门级的网表。

然后,使用实现工具将网表映射到目标FPGA器件上,并生成配置比特流文件。

4. 下载和验证:将生成的比特流文件下载到目标FPGA器件上,通过FPGA的输入输出端口连接输入信号和输出信号。

使用测试向量对FIR滤波器进行验证,确保其滤波效果符合设计要求。

在Vivado中实现FIR滤波器的过程中,需要注意以下几个关键点:1. 选择适当的滤波器类型:FIR滤波器可以有不同的类型,如低通、高通、带通和带阻等。

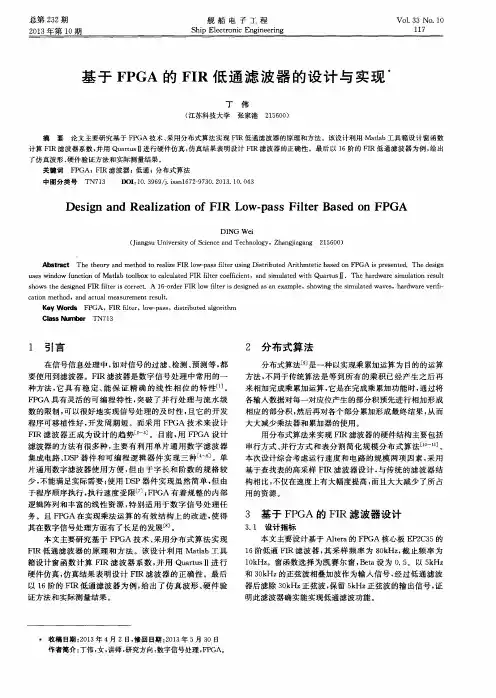

32阶FIR 滤波器的FPGA 实现范晓东1,蔡德林2,桂 岳1,梁本仁1(1.安徽大学电子科学与技术学院 安徽合肥 230039;2.中国电子科技集团公司第38研究所 安徽合肥 230031)摘 要:阐述了有限冲击响应(FIR )低通滤波器的窗函数设计方法,利用并行分布式算法在现场可编程门阵列上实现了32阶FIR 低通滤波器。

采用Altera 公司中Stratix 系列芯片内部的ROM 实现了一种基于查找表结构的FIR 数字滤波器,从而将卷积运算变换成一种查表后的加法运算,提高了运算速度,节省了逻辑单元。

仿真结果表面,基于并行分布式算法的FIR 滤波器最大处理速度可以达到200M Hz 。

关键词:FIR 滤波器;FP GA ;并行分布式算法;Matlab ;Quartus Ⅱ中图分类号:TN713 文献标识码:A 文章编号:10042373X (2009)212186203Implement of 32Orders FIR Filter on FPG AFAN Xiaodong 1,CAI Delin 2,GU I Yue 1,L IAN G Benren 1(1.Electronic Science and Technology Institute ,Anhui University ,Hefei ,230039,China ;2.No.38Institute ,China Electronics Technology Group Corporation ,Hefei ,230031,China )Abstract :Windows function design method of FIR digital filter is introduced ,and the parallel distributed arithmetic is used to implement a 32orders FIR digital ing the Altera ′s Stratix series FP GA to design a new structure of ing the ROM in FP GA ,this design can convert convolution to summation.Thus ,a high process speed is improved and the Logic Ele 2ments (L E )is saved.The result of simulation shows that the max speed of FIR filter can arrive at 200M Hz based on parallel distributed arithmetic.K eywords :FIR filter ;FP GA ;parallel distributed arithmetic ;Matlab ;Quartus Ⅱ收稿日期:2009204222 随着软件无线电的发展,对于滤波器的处理速度要求越来越高。

FPGA的FIR抽取滤波器设计用FPGA实现抽取滤波器比较复杂,主要是因为在FPGA中缺乏实现乘法运算的有效结构,现在,FPGA中集成了硬件乘法器,使FPGA在数字信号处理方面有了长足的进步。

本文介绍了一种采用Xilinx公司的XC2V1000实现FIR抽取滤波器的设计方法。

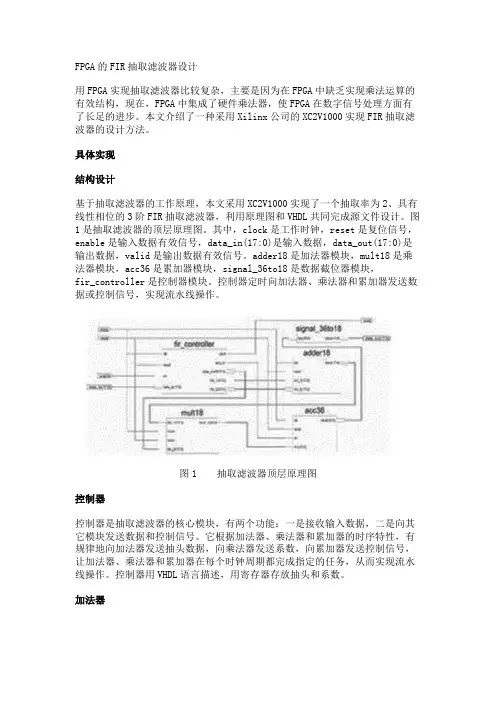

具体实现结构设计基于抽取滤波器的工作原理,本文采用XC2V1000实现了一个抽取率为2、具有线性相位的3阶FIR抽取滤波器,利用原理图和VHDL共同完成源文件设计。

图1是抽取滤波器的顶层原理图。

其中,clock是工作时钟,reset是复位信号,enable是输入数据有效信号,data_in(17:0)是输入数据,data_out(17:0)是输出数据,valid是输出数据有效信号。

adder18是加法器模块,mult18是乘法器模块,acc36是累加器模块,signal_36to18是数据截位器模块,fir_controller是控制器模块。

控制器定时向加法器、乘法器和累加器发送数据或控制信号,实现流水线操作。

图1 抽取滤波器顶层原理图控制器控制器是抽取滤波器的核心模块,有两个功能:一是接收输入数据,二是向其它模块发送数据和控制信号。

它根据加法器、乘法器和累加器的时序特性,有规律地向加法器发送抽头数据,向乘法器发送系数,向累加器发送控制信号,让加法器、乘法器和累加器在每个时钟周期都完成指定的任务,从而实现流水线操作。

控制器用VHDL语言描述,用寄存器存放抽头和系数。

加法器加法器的输入和输出都是18 bit,用VHDL语言描述实现。

它有两个工作时钟的延迟,在输入数据准备好的情况下,第一个时钟得出相加结果,第二个时钟把相加结果锁存输出。

乘法器乘法器为18 bit输入,36bit输出,用库元件MULT18X18S和36 bit锁存器实现。

MULT18X18S是XC2V1000自带的18×18bit硬件乘法器,单个时钟就可完成乘法运算。

基于FPGA乘法器的FIR滤波器系统设计FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,可以根据设计者的需求和要求进行编程,实现各种数字电路功能。

FIR (Finite Impulse Response)滤波器是一种常用的数字滤波器,其特点是能够对输入信号的有限长度的响应进行滤波处理。

本文将介绍基于FPGA乘法器的FIR滤波器系统设计。

首先,介绍FIR滤波器的原理。

FIR滤波器是一种线性时不变系统,其输出信号由输入信号的加权和组成。

FIR滤波器的输入经过一串系数的加权运算后,得到滤波器的输出。

FIR滤波器的传输函数为:H(z) = b0 + b1*z^(-1) + b2*z^(-2) + ... + bn*z^(-n)其中,bi是滤波器的系数,n是滤波器的阶数,z为单位延迟。

FIR 滤波器的输出信号可以表示为:y(n) = b0*x(n) + b1*x(n-1) + b2*x(n-2) + ... + bn*x(n-n)其中,x是输入信号,y是输出信号。

FIR滤波器的阶数决定了滤波器的性能,阶数越高,滤波器的频率响应越陡峭。

接下来,介绍基于FPGA乘法器的FIR滤波器系统设计。

FPGA乘法器是FPGA中的一种硬件资源,通常用于实现乘法运算。

FPGA乘法器的乘法操作可以并行地执行,可以大大提高FIR滤波器的运算速度。

在设计基于FPGA乘法器的FIR滤波器系统时,首先需要确定FIR滤波器的阶数和系数。

根据滤波器的需求,可以选择不同的阶数和系数。

然后,根据FIR滤波器的传输函数,可以将其转化为差分方程形式。

差分方程形式如下:y(n) = b0*x(n) + b1*x(n-1) + b2*x(n-2) + ... + bn*x(n-n)然后,将差分方程形式转化为数据流形式。

数据流形式中的每一步计算只涉及到少量的数据,可以并行地执行。

数据流形式如下:y(n) = b0*x(n) + b1*x(n-1) + b2*x(n-2) + ... + bn*x(0)接下来,需要将数据流形式转化为硬件电路。

基于fpga的滤波器设计与实现基于FPGA的滤波器设计与实现一、引言滤波器是信号处理中常用的一种工具,它可以通过剔除或增强信号中的特定频率分量来改变信号的特性。

而基于FPGA的滤波器是一种利用可编程逻辑器件FPGA来实现滤波功能的方法。

本文将介绍基于FPGA的滤波器的设计与实现过程。

二、滤波器的基本原理滤波器主要通过改变信号的频谱特征来实现滤波效果。

它可以分为两类:低通滤波器和高通滤波器。

低通滤波器通过剔除高频分量,保留低频分量;高通滤波器则相反,剔除低频分量,保留高频分量。

滤波器的设计需要根据具体的需求选择合适的滤波器类型和参数。

三、基于FPGA的滤波器设计与实现基于FPGA的滤波器设计与实现可以分为以下几个步骤:1. 确定滤波器类型和参数:根据实际需求,选择合适的滤波器类型和参数。

例如,如果需要设计一个低通滤波器,需要确定截止频率和滤波器阶数等参数。

2. 数字滤波器设计:将滤波器的模拟设计转化为数字滤波器的设计。

常见的数字滤波器设计方法有FIR滤波器设计和IIR滤波器设计。

FIR滤波器是一种无反馈的滤波器,具有线性相位特性;IIR滤波器则具有反馈结构,可以实现更高阶的滤波器。

3. 将数字滤波器转化为FPGA可实现的结构:将数字滤波器转化为FPGA可实现的结构,可以采用直接形式实现、级联形式实现或者管线化实现等方法。

其中,直接形式实现是最简单直观的方法,但其硬件资源占用较多;级联形式实现可以减少硬件资源的占用,但增加了延迟;管线化实现则可以兼顾硬件资源和延迟。

4. 使用HDL语言进行FPGA设计:使用HDL语言,如VHDL或Verilog,进行FPGA设计。

根据设计的结构和功能,编写相应的HDL代码。

在编写代码时,需要注意代码的可重用性和可维护性,以便后续的设计和调试。

5. 硬件验证和性能优化:完成HDL代码后,进行FPGA的硬件验证和性能优化。

通过仿真和验证,确保设计的正确性和稳定性。

同时,可以根据实际需求对硬件进行优化,如减小资源占用、降低功耗等。

FPGA实现FIR抽取滤波器的设计之蔡仲巾千创作FIR(fini te impulse response)滤波器是数字信号处理系统中最基本的元件,它可以在包管任意幅频特性的同时具有严格的线性相频特性,同时其单位冲激响应是有限的,没有输入到输出的反馈,系统稳定。

因此,FIR滤波器在通信、图像处理、模式识别等领域都有着广泛的应用。

在工程实践中,往往要求对信号处理要有实时性和灵活性,而已有的一些软件和硬件实现方式则难以同时达到这两方面的要求。

随着可编程逻辑器件的发展,使用FPGA来实现FIR滤波器,既具有实时性,又兼顾了一定的灵活性,越来越多的电子工程师采取FPGA器件来实现FIR滤波器。

1 FIR滤波器工作原理在进入FIR滤波器前,首先要将信号通过A/D器件进行模数转换,使之成为8bit的数字信号,一般可用速度较高的逐次逼进式A/D转换器,不管采取乘累加方法还是分布式算法设计FIR 滤波器,滤波器输出的数据都是一串序列,要使它能直观地反应出来,还需经过数模转换,因此由FPGA构成的FIR滤波器的输出须外接D/A模块。

FPGA有着规整的内部逻辑阵列和丰富的连线资源,特别适合于数字信号处理任务,相对于串行运算为主导的通用DSP芯片来说,其并行性和可扩展性更好,利用FPGA乘累加的快速算法,可以设计出高速的FIR数字滤波器。

2 16阶滤波器结构在滤波过程中实现抽取,对于抽取率为N的抽取滤波器而言,当进来N个数据时滤波器完成1次滤波运算,输出1次滤波结果。

抽取滤波器的结果和先滤波后抽取的结果是一致的,只是对于同样的数据,进行滤波运算的次数大大减少。

在数字系统中采取拙取滤波器的最大优点是增加了每次滤波的可处理时间,从而达到实现高速输入数据的目的。

采样数据与滤波器系数在控制电路的作用下,分别对应相乘并与前一个乘积累加,经过多次(有多少阶就要多少次)反复的乘累加最后输出滤波结果,将相同系数归类,16阶滤波器公式:乘法器的数量减少一半,但加法器的数量增多了,但相对乘法运算来说,加法运算所占用的资源少的多,运算的速度也快得多。

基于FPGA的FIR数字滤波器的设计和实现摘要:本文基于FPGA平台实现了一种FIR数字滤波器,通过对滤波器的设计与实现过程的详细介绍,展示了FPGA在数字滤波器中的应用优势。

首先介绍了数字滤波器的原理及其在信号处理中的重要性,并对FPGA及其特点进行了概述。

接着,详细介绍了FIR滤波器的原理以及其在FPGA上的实现步骤,分析了滤波器设计中需要考虑到的各种因素。

最后,通过实验验证了FPGA上实现的FIR滤波器的性能,并对优化策略进行了讨论。

关键词:FPGA,FIR滤波器,数字信号处理,性能优化1. 引言数字滤波器是现代信号处理的重要组成部分,通过选择性地传递或抑制输入信号的特定频率组成部分,对信号进行处理和改善。

FIR滤波器是数字滤波器中最常用的一种类型,具有线性相位特性、稳定性较强以及易于实现等优势。

而FPGA作为一种可编程逻辑器件,具有灵活性高、可重构性强等特点,成为实现数字滤波器的理想平台。

2. FIR滤波器的原理FIR滤波器是一种线性时不变系统,其输出仅和当前输入值以及过去若干个输入值有关。

该滤波器的输出可以通过输入信号的线性加权和来计算,其中,每个输入值的加权系数通过FIR 滤波器的系数来确定。

FIR滤波器的系数决定了它对不同频率分量的响应,从而实现了信号的滤波目的。

3. FIR滤波器在FPGA上的实现步骤(1)选择合适的FPGA平台和开发工具,如Xilinx FPGA平台和Vivado开发工具。

(2)根据所要设计的滤波器的需求,确定其采样频率、截止频率和滤波器类型等参数,并进行系统级设计。

(3)根据所选参数,设计FIR滤波器的传递函数,并确定滤波器的阶数和系数。

(4)通过数学运算或者通过滤波器设计软件生成滤波器的差分方程。

(5)根据生成的差分方程,使用HDL(HardwareDescription Language)进行滤波器的编写。

(6)进行FPGA的综合、布局与布线、下载与验证,完成滤波器的硬件实现。

基于fpga的滤波器设计与实现基于FPGA的滤波器设计与实现一、引言滤波器是信号处理中常用的工具,用于去除信号中的噪声或不需要的频率成分。

在数字信号处理中,滤波器可以通过软件算法实现,但随着现代电子技术的发展,使用基于FPGA的滤波器可以实现更高效、实时的信号处理。

本文将介绍基于FPGA的滤波器设计与实现的方法和步骤。

二、FPGA的基本原理FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,由大量的逻辑门、存储单元和可编程连接组成。

FPGA的特点是可重构性强,可以根据需要编程实现各种逻辑功能。

在数字信号处理中,可以将滤波器的算法实现在FPGA中,利用其并行处理的能力来提高处理速度和效率。

三、滤波器的基本原理滤波器可以根据其频率响应的特点分为低通滤波器、高通滤波器、带通滤波器和带阻滤波器等。

滤波器的设计目标是在保留需要的信号成分的同时,去除不需要的噪声或频率成分。

常用的滤波器设计方法有FIR滤波器和IIR滤波器。

四、基于FPGA的滤波器设计步骤1. 确定滤波器的类型和设计要求:根据信号处理的需求,确定滤波器的类型(低通、高通等)和性能指标(截止频率、通带衰减等)。

2. 确定滤波器的结构:选择合适的滤波器结构,如直接形式、级联形式等。

3. 设计滤波器的传递函数:根据滤波器的类型和设计要求,设计出满足要求的传递函数。

4. 将传递函数转化为差分方程:根据所选滤波器结构,将传递函数转化为差分方程。

5. 实现差分方程的计算:将差分方程转化为FPGA可以计算的形式,使用硬件描述语言(如Verilog、VHDL)编写计算模块。

6. 将计算模块综合到FPGA中:使用相应的工具将计算模块综合到FPGA中,生成比特流文件。

7. 下载比特流文件到FPGA:将生成的比特流文件下载到FPGA中,使其开始工作。

8. 测试和优化:对设计的滤波器进行测试,并根据测试结果进行优化,以满足设计要求。

高斯滤波的FPGA实现高斯滤波是一种常用的图像滤波算法,用于平滑图像并减少噪声。

FPGA(Field Programmable Gate Array)是一种可重新配置的硬件芯片,由于其并行计算的特性,适合用于高性能的图像处理任务。

因此,将高斯滤波算法实现在FPGA上可以实现实时性能和功耗优化。

实现高斯滤波的FPGA设计主要包括以下几个步骤:输入数据接口模块,FIR滤波器模块,图像存储器,以及输出数据接口模块。

首先,输入数据接口模块用于接收来自图像源的原始数据。

由于FPGA对数据的处理是以离散时间片的方式进行的,因此需要将输入数据进行采样和量化处理,以适应FPGA的输入要求。

接着,将采样后的数据传输到FIR滤波器模块进行滤波处理。

FIR滤波器模块采用一维FIR滤波器进行高斯滤波。

FIR滤波器是一种基于差分方程的滤波器,可以通过调整滤波器的系数来实现不同的滤波效果。

在高斯滤波中,滤波器的系数取决于高斯函数的离散化。

滤波器模块首先需要将输入数据存储在一个缓存器中,然后对缓存器中的数据进行卷积运算。

卷积运算是FIR滤波器的核心操作,可以通过多级线性插值运算来实现。

最后,将卷积运算结果存储在图像存储器中。

图像存储器用于存储滤波器模块输出的图像数据。

由于高斯滤波是一种卷积运算,它将对输入图像进行平滑处理并生成一个平滑后的输出图像。

因此,图像存储器的大小需要与输入图像的大小相匹配。

最后,输出数据接口模块用于将经过高斯滤波处理后的图像数据传输给显示设备或其他存储设备。

输出数据接口模块的设计与输入数据接口模块类似,需要进行数据的采样和量化处理。

为了进一步提高高斯滤波的性能,可以采用流水线技术将不同的模块并行化处理。

流水线技术可以将多个操作同时进行,从而提高整个系统的并行处理能力和效率。

总结来说,高斯滤波的FPGA实现主要包括输入数据接口模块,FIR 滤波器模块,图像存储器,以及输出数据接口模块。

通过合理设计这些模块的功能和流水线技术的运用,可以实现高性能和功耗优化的高斯滤波FPGA设计。

FIR滤波器的FPGA实现方法关键字::FIR FFT FPGA关键字在数字信号处理系统中,有限脉冲响应(finite impulse response,FIR)数字滤波器是一个非常重要的基本单元。

近年来,由于FPGA具有高速度、高集成度和高可靠性的特点而得到快速发展。

随着现代数字通信系统对于高精度、高处理速度的需求,越来越多的研究转向采用FPGA来实现FIR滤波器。

而对于FIR滤波器要充分考虑其资源与运行速度的合理优化,各种不同的FIR滤波结构各具优缺点,在了解各种结构优缺点后才能更好地选择合适结构来实现FIR滤波。

1FIR数字滤波器FIR数字滤波器由有限个采样值组成,设计中在满足幅值特性时,还能保证精确、严格的相位特性,因此在信号处理等领域得到广泛的应用。

对于FIR滤波器,其输出y(n)表示为如下形式:式中:N为滤波器的阶数(或抽头数);x(i)表示第i时刻的输入样本;h(i)为FIR滤波器的第i级抽头系数。

由于FIR滤波器的冲击响应为一个有限序列,其系统函数可表示为:FIR滤波器的基本结构如图1所示。

FIR滤波器只在原点处存在极点,所以这使得FIR 滤波器具有全局稳定性。

同时FIR滤波器满足线性相位条件,其冲击响应序列为实数且满足奇对称或偶对称条件,即:2实现方法运用FPGA来实现FIR数字滤波器的结构多种多样,但是主要有以下几类:串行结构、并行结构、转置型结构、基于FFT算法结构、分布式结构。

其他类型的FIR滤波器结构都可以由以上几种结构衍生而来。

2.1串行结构由表达式(1)可知,FIR滤波器实质是做一个乘累加运算,其滤波器的阶数决定了一次乘累加的次数,其串行结构如图2所示。

串行结构的FIR滤波器结构简单,硬件资源占用少,只需要复用1个乘法器和1个加法器,所以成本较低。

但是,这种结构的FIR滤波器要经过多个时钟周期才有输出,同时,内部时钟周期还受到乘法器运算速度的影响,所以该结构的FIR滤波器处理速度慢,只适用于滤波阶数较低且处理速度要求低的系统。

2.2并行结构将串行结构的FIR滤波器展开就可以得到并行结构的FIR滤波器,并行FIR滤波器结构又称作直接型FIR滤波器结构,这种结构是直接根据图1的滤波器结构,用多个乘法器和加法器并行实现。

通常考虑到其滤波器系数的对称性,先对输入值进行加法运算,再进行乘法运算,最后累加输出,以此来减少乘法器的个数,其结构如图3所示。

并行结构的FIR滤波器在1个周期内可以完成1次滤波,运行速度快,虽然利用滤波系数对称性,但仍要占用大量的乘法器和加法器,特别对于滤波阶数高的滤波器,其资源占用较多,如对于256阶的滤波器,其需要128个乘法器来实现。

为提高滤波器速度,常引入流水线结构,即在每次加法或者乘法运算后加入1个寄存器存储数据,使得滤波器可以运行在更高的频率上。

2.3转置型结构根据转置定理,如果将网络中所有的支路方向倒转,并将输入x(n)和输出y(n)相互交换,则其系统函数H(z)不变。

通过转置定理,将并行结构的FIR滤波器变换就可以得到转置型FIR滤波器,其结构如图4所示。

基于并行结构的转置型FIR滤波器实现了数据的并行输入,在1个周期内就能完成1次滤波,并且各级结构相同,在每个阶段都可以读出数据,可以对滤波阶数进行扩展或者缩减,实现任意阶数的滤波器。

但是由于基于的是并行结构,便有着并行结构的一些缺点,主要是对于高阶的滤波器,其资源占用量是巨大的,设计成本高。

虽然这样,转置型FIR滤波器仍是应用广泛的一种滤波器。

2.4基于FFT的结构应用快速傅里叶变换(fast fourier transform,FFT)实现FIR滤波器是一种快速实现滤波算法的重要途径。

由式(1)可知,FIR滤波器的输出y(n)是输入x(n)与系统冲击响应序列h(n)的卷积,应用FFT可以快速实现卷积变换。

如图5所示,先将输入信号x(n)通过FFT变换为它的频谱采样值X(k),然后再与FIR滤波器的频响采样值H(k)相乘,H(k)可事先存放在存储器中,最后再将乘积X(k)H(k)通过快速傅里叶反变换(IF-FT)还原为时域序列,即得到输出y(n)。

为实现FFT,根据两有限长序列的线性卷积可用其循环卷积代替而不发生混叠,必须选择循环卷积长度N≥N1+N2-1,即将x(n)和h(n)补零至长度为N的序列,即:在基于FFT的FIR滤波器结构中,求X(k),H(k)以及反傅里叶变换y(n)需要的乘法次数均为N/2log2N,而计算X(k)H(k)需要N次乘法,所以基于FFT的总乘法次数为mf=3/2Nlog2N+N。

由于h(n)满足式(3)条件,所以直接卷积所需的乘法次数为md=1/2N1N2。

假设N1=N2,则比较这两种乘法计算量有:从表1可知,当N1<42时,FFT法的运算量小于直接卷积的运算量,当N1=42时,FFT 法的运算量与直接卷积的运算量相当,当N1>42时,FFT法的运算量大于直接卷积的运算量,并且随着N1增加,FFT法的运算速度越来越快,特别是N1=8192时,FFT法的运算速度与直接卷积相比快上将近100倍。

2.5分布式结构2.5.1分布式算法原理分布式算法(distributed arithmetic,DA)于1973年就由Croisier提出,但是直到FPGA出现,才广泛的被应用于FPGA中计算乘累积和。

对于有符号数x(n)可以用下式的补码形式表示:对于式(7)中的h(i)xb(n-i)代表着输入数据x(n-i)的第i位与抽头系数h(i)的乘积,对于FIR滤波器,其系数h(i)是常数,所以可以事先构造一个查找表。

该查找表存储所有h(i)xb(n-i)的乘积值,通过输入(xb(N-1),xb(N-2),…,xb(0))对该表寻址,然后将查得的值乘上2b后移位累加便得到滤波器输出y(n)。

该查找表构造规则如表2所示。

2.5.2基于分布式算法的FIR滤波器结构基于分布式算法的FIR滤波器主要有3种结构类型。

(1)第一种结构为串行分布式结构。

串行分布式FIR滤波器的原理为,首先用所有N个输入量的最低位对DA查找表进行寻址查值,得到一个部分积,将部分积右移一位即相当于除以2后放到寄存器中暂存。

同时,N个输入量的次低位开始对DA查找表进行寻址查值,得到另一个部分积,把该部分积与上一个储存在寄存器中的值进行相加,相加后的值再右移一位放到寄存器中。

以此重复循环累加,直到所有位数都寻址完成,注意最高位寻址后的部分积是相减,最后所得到的值就是所需要的结果。

当N过大,即FIR滤波器的滤波阶数很高时,采用一个查找表来实现将使得存储查找表的ROM变得十分庞大。

为此可采用部分表结构,即将查找表划分为多个部分,N个输入量的同一位对应不同的部分表寻址。

图6所示即为基于4输入部分表结构的串行DA结构。

(2)第二种结构为并行分布式结构。

并行分布式结构就是将N个输入量的不同位进行同时查表,而相同位送入同一个ROM寻址,不同位有不同的ROM。

其结构如图7所示。

第三种结构为串并结合分布式结构。

它是一种折中方案,既要求速度不太高又要求资源占用少。

对于串行分布式算法,是一次一位(one bit-at-a-time,1BAAT)查找表,而并行分布式算法是一次B位(B bits-at-a-time)。

所以串并结合分布式算法采用一次多位,如2BAAT,3BA-AT。

图8所示为4BAAT查找表结构图。

图8中位数B是4的倍数,SRL为移位寄存器。

SRL中第1行从右边数第1列为数据的0位,第2列为数据的1位,第3列为数据的2位,第4列为数据的3位。

类似地,第2行右数第1列为数据的4位,第2列为数据的5位,第3列为数据的6位,第4列为数据的7位。

以后各行按相似的数位顺序排列。

在第一个时钟周期,数据的0,4,…,B-4位同时进入查找表ROM中,查出所要的数据,第二个时钟周期,1,5,…,B-3位同时进入ROM中,查出所要的数据,所查得的数据传递给下一级累加器进行累加,这样依次对剩下的各数据位进行同样的操作。

由于每个块之间相差4位,即16倍,为了对应位相加,所以乘16。

FIR滤波器的分布式算法结构比单独用乘法器实现的速度快,特别是滤波阶数越高,其优势更加明显。

分布式结构中,串行结构是1次查询1位,所以对B位的数据在不算上移位寄存等的时间,完成1次滤波需要B个时钟周期;而并行结构只需要1个时钟周期便完成滤波,所以并行结构是速度最优的结构,但是并行结构需要B个DA查找表,需要大量的ROM来储存,加大了硬件资源的消耗,特别是阶数越高,硬件规模将十分膨大;串并结构综合两种结构优势,实现在速度和规模上的协调。

实际应用中。

需根据系统的要求来选择合适的结构。

3结语本文定性地分析了各种FIR滤波器的FPGA实现方法。

对于低阶的FIR滤波器可采用串行结构、并行结构以及转置型结构来实现,而并行结构和转置型结构的FIR滤波器以牺牲资源损耗来实现了速度上优势;对于高阶的FIR滤波器,基于乘法器结构的串行结构、并行结构及转置型结构在速度上难以达到高速处理的要求,而分布式算法将乘法转换为查表和累加的结构,使得分布式结构的FIR滤波器在速度上得到了提高,但三种不同形式的分布式结构要在综合考虑资源以及速度的基础上进行合理选择;同样采用FFT实现的FIR滤波器以减少运算量来获得了速度上的提高,特别是滤波阶数越高其速度提升越明显。

现代工程技术领域对滤波系统的带宽、高速、信号的实时性处理等方面要求越来越高,在运用FPGA来实现FIR滤波中,基于乘法器结构的FIR滤波器无法满足以上要求,而分布式结构的FIR滤波器巧妙地运用ROM查找表来实现固定系数的乘累加运算,避免了乘法运算,并且在随后的每级加法运算中引入流水线结构,提高了速度。

因此采用分布式算法实现FIR滤波器是目前研究的热点,同时无论哪种分布式算法都要使用ROM来做查找表,但是随着滤波阶数的增加,ROM的数量将会增加,在进一步提高速度的情况下如何减少ROM的数量是今后亟待解决的问题。