CMOS 电路中ESD 保护结构的设计

- 格式:pdf

- 大小:422.73 KB

- 文档页数:8

CMOS 片上电源总线ESD 保护结构设计王怡飞,胡新伟,郭立(中国科学技术大学电子科学与技术系,合肥230027)摘要:随着集成电路制造技术的高速发展,特征尺寸越来越小,静电放电对器件可靠性的危害也日益增大,E SD 保护电路设计已经成为IC 设计中的一个重要部分。

讨论了三种常见的CMOS 集成电路电源总线E SD 保护结构,分析了其电路结构、工作原理和存在的问题,进而提出了一种改进的ESD 保护电源总线拓扑结构。

运用HSPICE 仿真验证了该结构的正确性,并在一款自主芯片中实际使用,ESD 测试通过±3000V 。

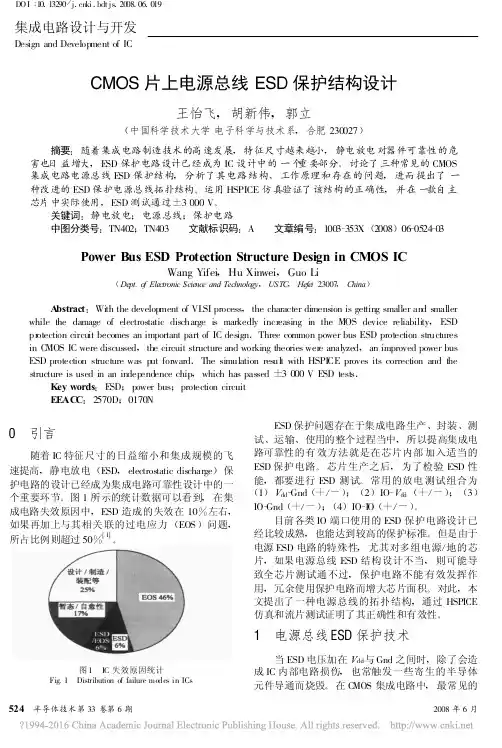

关键词:静电放电;电源总线;保护电路中图分类号:TN402;TN403 文献标识码:A 文章编号:1003-353X (2008)06-0524-03Power Bus ESD Protection Structure Design in CMOS ICWang Yifei ,Hu Xinwei ,Guo Li(Dept .o f Electronic Science and Technolo gy ,USTC ,Hefei 23007,China )A bstract :With the development of VLSI process ,the character dimension is getting smaller and smaller while the damage of electrostatic discharge is markedly incr easing in the MOS device reliability ,ESD pr otection circuit becomes an important part of IC design .Three common power bus ESD protection structures in C MOS IC were discussed ,the circuit structure and working theories wer e analyzed ,an improved power bus ESD protection structure was put for ward .The simulation result with HSPI CE proves its correction and the structure is used in an independence chip ,which has passed ±3000V E SD tests .Key words :E SD ;power bus ;protection circuit EEAC C :2570D ;0170N图1 IC 失效原因统计Fig .1 Distribution of failure modes in ICs0 引言随着IC 特征尺寸的日益缩小和集成规模的飞速提高,静电放电(E SD ,electrostatic discharge )保护电路的设计已经成为集成电路可靠性设计中的一个重要环节。

CMOS电路中ESD保护结构的设计上海交通大学微电子工程系王大睿1 引言静电放电(ESD,Electrostatic Discharge)给电子器件环境会带来破坏性的后果。

它是造成集成电路失效的主要原因之一。

随着集成电路工艺不断发展,互补金属氧化物半导体(CMOS,ComplementaryMetal-Oxide Semiconductor)的特征尺寸不断缩小,金属氧化物半导体(MOS,Metal-Oxide Semiconductor)的栅氧厚度越来越薄,MOS管能承受的电流和电压也越来越小,因此要进一步优化电路的抗ESD性能,需要从全芯片ESD保护结构的设计来进行考虑。

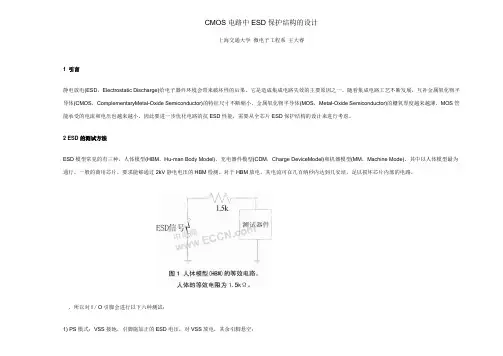

2 ESD的测试方法ESD模型常见的有三种,人体模型(HBM,Hu-man Body Model)、充电器件模型(CDM,Charge DeviceModel)和机器模型(MM,Machine Mode),其中以人体模型最为通行。

一般的商用芯片,要求能够通过2kV静电电压的HBM检测。

对于HBM放电,其电流可在几百纳秒内达到几安培,足以损坏芯片内部的电路。

,所以对I/O引脚会进行以下六种测试:1) PS模式:VSS接地,引脚施加正的ESD电压,对VSS放电,其余引脚悬空;2) NS模式:VSS接地,引脚施加负的ESD电压,对VSS放电,其余引脚悬空;3) PD模式:VDD接地,引脚施加正的ESD电压,对VDD放电,其余引脚悬空;4) ND模式:VDD接地,引脚施加负的ESD电压,对VDD放电,其余引脚悬空;5) 引脚对引脚正向模式:引脚施加正的ESD电压,其余所有I/O引脚一起接地,VDD和VSS引脚悬空;6) 引脚对引脚反向模式:引脚施加负的:ESD电压,其余所有I/O引脚一起接地,VDD和VSS引脚悬空。

VDD引脚只需进行(1)(2)项测试3 ESD保护原理ESD保护电路的设计目的就是要避免上作电路成为ESD的放电通路而遭到损害,保证在任意两芯片引脚之间发生的ESD,都有适合的低阻旁路将ESD电流引入电源线。

MOS芯片的ESD保护电路设计ESD(Electrostatic Discharge)保护电路是在MOS芯片设计中非常重要的一部分,其主要作用是保护芯片免受静电放电和其他电压干扰引起的损坏。

在设计ESD保护电路时,需要考虑静电放电的强度、放电路径、放电时间以及芯片的特性。

本文将详细介绍MOS芯片的ESD保护电路设计。

首先,设计ESD保护电路需要了解芯片的工作电压范围和工作环境。

这些参数将决定所需的ESD保护等级和保护电路的设计方案。

通常,ESD保护电路需要满足以下几个基本要求:1.渠道长度匹配:ESD保护电路通常需要使用多个MOS管来承受ESD电流。

为了提高保护效果,这些MOS管的渠道长度应该尽量相等,以保证它们可以均匀分担ESD电流。

在设计过程中,可以采用各种技术来实现渠道长度匹配,例如采用仿射布局或者通过电路设计巧妙应用。

2.延迟时间:ESD保护电路需要尽快响应ESD事件,并将电压降低到安全的范围内。

因此,保护电路的响应时间应该尽量短,以确保芯片能够在ESD事件发生时快速响应,避免损坏。

延迟时间通常可以通过选择合适的电阻和电容参数来调整。

3.低电压降:在ESD事件中,保护电路需要将电压降低到芯片所能接受的安全范围内,以避免芯片受损。

为了实现低电压降,通常会采用多级级联的保护结构,通过分级响应来降低电压。

此外,选择合适的电阻和电容参数也可以帮助减小电压降。

4.高可靠性:ESD保护电路需要能够经受多次击打,无损耗或自愈。

因此,在设计中需要使用具有较高可靠性的器件和元件。

例如,可以采用具有低漏电流和高耐压能力的二极管、MOSFET等元件。

在具体的ESD保护电路设计中,常用的保护结构包括二极管保护、级联保护和母线保护等。

例如,二极管保护方法主要通过将二极管连接在输入和输出之间来分散ESD放电能量,以提供保护。

级联保护方法则通过将多个保护器件级联并设置适当的门控电压来提高保护效果。

除了以上核心的保护电路设计,还可以采取一些其他的措施来增强芯片的ESD保护能力。

摘要静电放电(简写为ESD)是集成电路(简写为IC)在制造、运输、以及使用过程中经常发生并导致IC芯片损坏或失效的重要原因之一。

工业调查表明大约有40%的IC失效与ESD/EOS(过强的电应力)有关。

因此,为了获得性能更好更可靠的IC芯片,对ESD开展专门研究并找到控制方法是十分必要的。

随着芯片尺寸的持续缩小,ESD问题表现得更加突出,已成为新一代集成电路芯片在制造和应用过程中需要重视并着力解决的一个重要问题。

论文论述了CMOS集成电路ESD 保护的必要性,研究了在CMOS电路中ESD 保护结构的设计原理,分析了该结构对版图的相关要求,重点讨论了在I/O电路中ESD 保护结构的设计要求。

论文所做的研究工作和取得的结果完全基于GGNMOS的器件物理分析,是在器件物理层次上研究ESD问题的有益尝试;相对于电路层次上的分析结果,这里的结果更加准确和可靠,可望为GGNMOS ESD保护器件的设计和制造提供重要参考。

关键词:静电放电(ESD);接地栅NMOS;保护器件;电源和地AbstractThe electrostatic discharge (ESD) is integrated circuit (IC) in manufacturing, transportation, and use process occurs frequently and cause IC chips damage or failure of one of the important reasons. Industrial survey shows that about 40 percent of IC failure and ESD/EOS (overpowered electrical stress) relevant. Therefore, in order to obtain better performance more reliable IC chips, to carry out special research and find the ESD control method is very necessary. Along with the continuous narrowing, chip size behaved more prominent ESD problems, has become a new generation of integrated circuit chip in the manufacture and application process needed to pay attention to and addressing an important question.This paper discusses the CMOS integrated circuit, the necessity of ESD protection in CMOS circuit was studied in the structure of ESD protection design principle, analyzes the structure on the map the relevant requirements, especially discussed in the I/O circuit ESD protection structure design requirements.Keywords:Electrostatic Discharge, GND gate NMOS, Protected Device, Power and Ground目录摘要 (1)Abstract (2)第1章绪论 (4)1.1 集成电路的发展状况 (4)1.1.1 集成度的提高 (4)1.1.2 摩尔定律 (4)1.2 集成电路中的ESD保护 (5)1.2.1 为何出现ESD (5)1.2.2 ESD保护的必要性 (5)第2章关于版图设计与版图设计环境的介绍 (7)2.1 集成电路版图设计 (7)2.2 版图结构 (7)2.3 版图设计流程与方法 (8)2.4 版图设计环境 (8)2.4.1 Technology file 与Display Resource File 的建立 (9)2.4.2 Virtuoso工具的使用 (9)第3章CMOS电路的ESD保护结构版图设计 (13)3.1 CMOS电路中ESD测试 (13)3.2 ESD保护原理 (14)3.3 CMOS电路ESD保护结构的设计 (14)3.3.1 CMOS电路ESD保护器件 (15)3.4 CMOS电路ESD保护结构的版图设计 (16)3.4.1 版图设计原则 (16)3.4.2 ESD保护结构版图设计 (17)第4章结束语 (18)参考文献 (19)致谢 (20)第1章绪论1.1 集成电路的发展状况1.1.1 集成度的提高真正导致数字集成电路技术发生革命性变化的是半导体存储器和微处理器的引入。

CMOS集成电路ESD保护技术研究董培培;张海涛【摘要】介绍了 ESD 保护原理、测试方法及典型的 ESD 保护电路,针对2000V 的 HBM模型ESD 保护指标要求,采用 CSMC 0.5μm 25V(VGS)/25V (VDS)DPTM工艺模型和 GGMOS 器件进行了全芯片的 ESD 保护电路设计,并对 ESD 保护管的输出驱动级做了探索,在保证输出级 ESD 保护能力的同时,提高了输出端口的带负载能力。

鉴于 ESD 保护结构工艺移植性较差,保护性能与工艺密切相关的特点,结合具体版图设计实践,总结了 ESD 保护结构版图设计的通用原则。

这些原则旨在提高 ESD 保护结构的抗静电能力或提高 ESD 保护器件的工作可靠性,与具体的实现工艺无关。

流片后的 ESD 实验表明,设计的 ESD 保护结构可以承受2000V HBMESD 攻击。

%The principles,measurement methods and typical circuits of ESD Protection are introduced in this ing CSMC 0.5μm 25V(VGS)/25V(VDS)DPTMProcess and GGMOS devices,the ESD protection circuits of the whole chip are designed to achieve 2000V HBMESD protection ability,and output driver designed with ESD protection FETs is explored to raise the driving ability of output pin while keeping the ESD protection ability.Because technology portability of ESD protection circuits is bad and ESD protection ability is highly related with technology,combined with layout design practice,the general principles of ESD layout design are presented.The principles,regardless of technology,aim at raising the protection ability or reliability of ESD protection structure.The ESD experiment of the fabricated chip shows that the designed ESD protection structure can endure 2000V HBMESD attack.【期刊名称】《微处理机》【年(卷),期】2016(037)005【总页数】4页(P9-12)【关键词】ESD保护;GGMOS 器件;电路设计;版图设计;通用原则;工作可靠性【作者】董培培;张海涛【作者单位】中国电子科技集团公司第四十七研究所,沈阳 110032;中国人民解放军 95979 部队,辽宁,沈阳 110045【正文语种】中文【中图分类】TN4随着电路设计和制造工艺水平的发展,CMOS集成电路工艺尺寸不断缩小,单芯片集成度不断变大,且电路结构越来越复杂,极大提高了集成电路的性价比。

随着CMOS集成电路产业的高速发展,越来越多的CMOS芯片应用在各种电子产品中,但在电子产品系统的设计过程中,随着CMOS工艺尺寸越求越小,单位面积上集成的晶体管越来越多,极大地降低了芯片的成本,提高了芯片的运算速度。

但是,随着工艺的进步和尺寸的减小,静电释放(ESD),Elecyro Static Discharge)问题变得日益严峻。

据统计,在集成电路设计中大约40%的失效电路是ESD问题造成的。

MOS晶体管是绝缘栅器件,栅极通过薄氧化层和其他电极之间绝缘。

如果栅氧化层有较大的电压,会造成氧化层击穿,使器件永久破坏。

随着器件尺寸减少,栅氧化层不断减薄,氧化层能承受的电压也不断下降,引起氧化层本征击穿的电场强度约为1 X 107V/cm。

如栅氧化层厚度是50 nm 则可承受的最大电压约50 V,当栅氧化层厚度减少到5 nm,则所能承受的最大电压约为5 V。

因此外界的噪声电压容易引起栅击穿。

特别是外界各种杂散电荷会在栅极上积累,由于MOS 晶体管的栅电容很小,只要少量的电荷就能形成很大的等效栅压,引起器件和电路失效,这就是ESD 问题。

例如,人体所带的静电荷可产生高达几kV的电压,在80%的湿度情况下,人走过化纤地毯可能产生1.5 kV静电压。

ESD对CMOS集成电路的损伤,不仅会引起MOS器件栅击穿,还可能诱发电路内部发生闩锁效畸应。

另外,静电释放产生的瞬时大电流可能造成芯片局部发热,损害器件和电路。

在一般的条件下,ESD不会导致器件即时失效,它往往潜伏在集成电路器件中,这种存在有潜在缺陷的器件在使用时容易失效。

特别是在深亚微米CMOS工艺中,由于溥栅氧化层的击穿电压较低,必须加入有效的在片ESD保护电路以箝位加到内部电路栅氧化层上的过充电压。

1 ESD放电模式与设计方案电路的输入或输出端与电源和地之间的ESD应力有4种模式在集成电路中和外界相连的输入、输出端子比内部器什更容易受到ESD损伤。

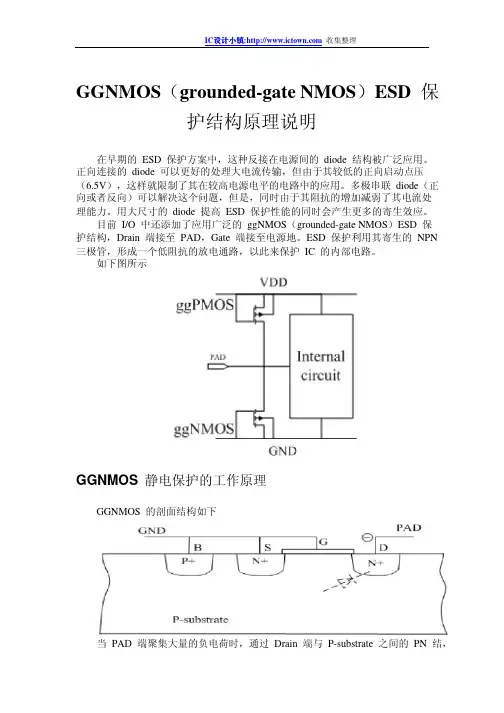

IC设计小镇:收集整理GGNMOS(grounded-gate NMOS)ESD保护结构原理说明在早期的ESD 保护方案中,这种反接在电源间的diode 结构被广泛应用。

正向连接的diode 可以更好的处理大电流传输,但由于其较低的正向启动点压(6.5V),这样就限制了其在较高电源电平的电路中的应用。

多极串联diode(正向或者反向)可以解决这个问题,但是,同时由于其阻抗的增加减弱了其电流处理能力。

用大尺寸的diode 提高ESD 保护性能的同时会产生更多的寄生效应。

目前I/O 中还添加了应用广泛的ggNMOS(grounded-gate NMOS)ESD 保护结构,Drain 端接至PAD,Gate 端接至电源地。

ESD 保护利用其寄生的NPN三极管,形成一个低阻抗的放电通路,以此来保护IC 的内部电路。

如下图所示GGNMOS静电保护的工作原理GGNMOS 的剖面结构如下当PAD 端聚集大量的负电荷时,通过Drain 端与P-substrate 之间的PN 结,IC设计小镇:收集整理电荷由 B 端泻放到GND。

当PAD 端聚集大量的正电荷时,利用的是寄生的三极管。

寄生三极管的启动原理如下说明。

1、大量的正电荷聚集在Drain 端,一定的正电荷通过Drain 和P-substrate之间反偏的PN 结转移至Psubstrate,这部分正电荷聚集到同为P 型材料的 B 端,转移到GND。

如下图所示2、3、聚集到 B 端的正电荷,使得与Source 端的PN 结导通,由此导通寄生的三极管。

如下图所示寄生的三极管被打开,大量的正电荷通过Gate 下面的区域迅速由Drain 端转移到Source 端。

聚集的正电荷得以快速的泻放到地。

如下图所示在GGNMOS 结构的ESD 保护中,器件的的不均匀性将影响到其性能,在layoutIC设计小镇:收集整理的时候需要充分考虑到这个问题,同时可对器件进行改进,增加Drain 端的宽度,在电路中相当于添加小电阻,减小电流,提高其均匀性。

ESD保护结构设计静电放电会给电子器件带来破坏性的后果,它是造成集成电路失效的主要原因之一。

随着集成电路工艺不断发展,CMOS电路的特征尺寸不断缩小,管子的栅氧厚度越来越薄,芯片的面积规模越来越大,MOS管能承受的电流和电压也越来越小,而外围的使用环境并未改变,因此要进一步优化电路的抗ESD性能,如何使全芯片有效面积尽可能小、ESD性能可靠性满足要求且不需要增加额外的工艺步骤成为IC设计者主要考虑的问题。

ESD保护原理ESD保护电路的设计目的就是要避免工作电路成为ESD的放电通路而遭到损害,保证在任意两芯片引脚之间发生的ESD,都有适合的低阻旁路将ESD电流引入电源线。

这个低阻旁路不但要能吸收ESD电流,还要能箝位工作电路的电压,防止工作电路由于电压过载而受损。

在电路正常工作时,抗静电结构是不工作的,这使ESD保护电路还需要有很好的工作稳定性,能在ESD发生时快速响应,在保护电路的同时,抗静电结构自身不能被损坏,抗静电结构的负作用(例如输入延迟)必须在可以接受的范围内,并防止抗静电结构发生闩锁。

CMOS电路ESD保护结构的设计大部分的ESD电流来自电路外部,因此ESD保护电路一般设计在PAD 旁,I/O电路内部。

典型的I/O电路由输出驱动和输入接收器两部分组成。

ESD通过PAD导入芯片内部,因此I/O里所有与PAD直接相连的器件都需要建立与之平行的ESD低阻旁路,将ESD电流引入电压线,再由电压线分布到芯片各个管脚,降低ESD的影响。

具体到I/O电路,就是与PAD相连的输出驱动和输入接收器,必须保证在ESD发生时,形成与保护电路并行的低阻通路,旁路ESD电流,且能立即有效地箝位保护电路电压。

而在这两部分正常工作时,不影响电路的正常工作。

常用的ESD保护器件有电阻、二极管、双极性晶体管、MOS管、可控硅等。

由于MOS管与CMOS 工艺兼容性好,因此常采用MOS管构造保护电路。

CMOS工艺条件下的NMOS管有一个横向寄生n-p-n(源极-p型衬底-漏极)晶体管,这个寄生的晶体管开启时能吸收大量的电流。

cmos电路中esd保护结构的设计CMOS电路被广泛运用于各种数字和模拟电路中。

然而,由于ESD(静电放电)事件的影响,CMOS电路仍然面临着破坏的风险。

因此,保护CMOS电路免受ESD的影响是非常重要的。

本文将讨论ESD保护结构的设计。

1. ESD基础知识ESD是指在接触、分离或摩擦两个带电物体时,由于静电作用而产生的瞬时放电现象。

在CMOS电路中,ESD事件可能破坏器件的PN结、栅极氧化层和金属线等。

2. ESD保护结构的形成ESD保护结构的设计基于两个原则:首先,防止ESD电荷积聚,并尽快将电荷从器件移走。

其次,减小ESD电荷得以穿透器件的功率密度。

为了满足这两个原则,ESD保护结构通常由以下四个组成部分组成:(1) ESD灵敏结构:ESD电荷积累在这个结构中,以便快速释放。

(2) 过压保护结构:当CMOS电路受到过高供电电压的打击时,过压保护结构会将电荷从器件中移走。

(3) 电感结构:电感结构可以提高ESD耐压强度,并防止ESD电荷在CMOS电路中传播。

(4) 负载结构:负载结构用于吸收ESD放电产生的能量。

3. ESD保护结构的实现ESD保护结构的实现可以通过以下方式:(1) 使用二极管结构:这种结构使用单极或双极二极管,以将ESD电荷移走。

(2) 使用MOSFET结构:这种结构使用N型或P型MOSFET,以将ESD电荷移走。

(3) 使用双向瞬态抑制器(TVS):这种结构是一种二极管并联的瞬态抑制器,能够快速移走ESD电荷。

(4) 使用正弦脉冲阻抗(SPI):这种结构是一种多级阻抗网络,可以提高ESD耐压能力。

4. 结论ESD保护结构的设计是保证CMOS电路稳定性的重要一环。

通过设计合适的ESD保护结构可以最大限度地减小ESD事件对CMOS电路的影响,从而提高电路的寿命和可靠性。

ESD保护电路的设计静电放电(ESD)会给电子产品带来致命的危害,它不仅降低了产品的可靠性,增加了维修成本,而且不符合欧洲共同体规定的工业标准EN61000-4-2,产品就不能够在欧洲销售。

所以电子设备制造商通常会在电路设计的初期就考虑ES D保护。

本文将讨论ESD保护电路的几种方法。

ESD的危害ESD基本上可以分为三种类型,一是各种机器引起的ESD,二是家俱移动或设备移动引起的ESD,三是人体接触或设备移动引起的ES D。

这三种种ES D对于半导体器件的生产和电子产品的生产都非常重要。

电子产品在使用过程最容易受到第三种ES D的损坏,便携式电子产品尤其容易受到人体接触产生的ESD的损坏。

在一般情况下ES D会损坏与之相连的接口器件,另一种情况是遭受ES D冲击后的器件可能不会立即损坏,而是性能下降导致产品过早出现故障。

当集成电路(IC)经受ESD时,放电回路的电阻通常都很小,无法限制放电电流。

例如将带静电的电缆插到电路接口上时,放电回路的电阻几乎为零,造成高达数十安培的瞬间放电尖峰电流,流入相应的IC管脚。

瞬间大电流会严重损伤IC,局部发热的热量甚至会融化硅片管芯。

ESD对IC的损伤还包括内部金属连接被烧断,钝化层受到破坏,晶体管单元被烧坏。

ESD还会引起IC的死锁(LATCHUP)。

这种效应和CMOS器件内部的类似可控硅的结构单元被激活有关。

高电压可激活这些结构,形成大电流信道,一般是从VCC到地。

串行接口器件的死锁电流可高达1A。

死锁电流会一直保持,直到器件被断电。

不过到那时,IC通常早已因过热而烧毁了。

ESD冲击后可能存在两个不易被发现的问题,一般用户和IEC测试机构使用传统的“环路反馈方法”和“插入方法”进行测试,通常检测不出这两个问题。

一个问题是RS-232接口电路中接收器对发送器产生交叉串扰。

同类产品RS-232接口电路中的ESD保护结构可能对某种波形的ESD或某个ESD冲击电压失效,经过ESD冲击后在接收器输入端和发送器输出端之间形成通路,从而导致接收器对发送器产生交调(图1)。

收稿日期:2008-06-23基金项目:国家自然科学基金资助(60206006);教育部新世纪优秀人才计划资助(681231366);国家部委预研基金资助(51308040103);西安应用材料创新基金资助(XA -AM -200701)作者简介:刘红侠(1968-),女,教授,博士,E -mail :hxliu @mail .xidian .edu .cn .0.18μm CMOS 工艺下的新型ESD 保护电路设计刘红侠,刘青山(西安电子科技大学宽禁带半导体材料与器件教育部重点实验室,陕西西安 710071)摘要:为了有效地保护0.18μm CM OS 工艺下箝位器件的栅极,设计了一款新型的电源和地之间的静电保护电路.该电路在检测电路部分加了一个N M O S 反馈器件,同时在检测电路的下一级使用了动态传输结构.反馈器件能够提高电路中各器件工作状态的转换速度,使得保护电路能够及时关闭,避免箝位器件栅极电流保持过长时间,保护了箝位器件的栅极.此外,该电路采用0.18μm CM O S 工艺下的普通器件,节省了电路的成本.关键词:静电放电;保护电路;反馈;动态传输中图分类号:T N431.1 文献标识码:A 文章编号:1001-2400(2009)05-0867-04Analysis and design of novel ESD protection circuitin 0.18μm CMOS processLIU Hong -x ia ,L IU Qing -shan(M inistry of Educatio n K ey Lab .of W ide Band -G ap Semico nduc to r M a te rialsand Devices ,Xidian U niv .,Xi an 710071,China )A bstract : Based on the 0.18μm CM O S pro ce ss ,a new type o f pow er -rail ESD pro tection circuit fo rpr otecting the ga te o f the ESD clamp device is proposed .A n N M OS feedback device is added in thedetectio n circuit ,and the dynamic tra nsmissio n str ucture is applied .T he w o rking states a re enhanced bythe feedback structure ,w hich can shutdo wn the pr otectio n circuit immedia te ly ,reduce the hold time o fthe cur rent across the ga te of the clamp device ,and protect the ga te .T his circuit uses the no rmal devicesfor the 0.18μm CM O S pr ocess ,thus saving the cost gr eatly .T he effectiv eness o f this new pro tectioncircuit is ve rified by the research results .Key Words : electro -static dischar ge (ESD );pro tection cir cuits ;feedback ;dy namic transmission伴随工艺技术的日臻完善,可靠性问题越来越成为制约集成电路发展的瓶颈.而在众多失效原因中,静电放电(ESD )问题尤为严重,统计结果表明:大约40%以上的集成电路失效都是由于ESD 失效引起的.在许多芯片测试中发现[1-5]:虽然芯片有良好的输入输出防护设计,而且输入输出接口均正常工作,但是芯片内部却出现了异常损伤.图1就是在ND 模式的静电放电情况下芯片内部出现损伤的现象.图中负电压出现在输入焊盘和V DD 之间,V D D 在ND 模式测试时候是接地的.此负的ESD 电压首先由静电防护电路到达V SS 电源线,在该测试情况下V SS 是浮接的,因此在V DD 和V SS 之间存在电压降.如果这个电压不能及时泄放掉,就会造成芯片内部器件的损伤.同时为了节省面积,内部电路通常都采用最小尺寸设计,芯片就更容易遭受ESD 损伤.现在的系统芯片SOC (Sy stem on chip )要求把数字电路和模拟电路做在同一块芯片上,为了防止信号干扰,通常把模拟部分和数字部分的电源分开,在芯片内部出现多对电源线和地线,电源和地之间的ESD 保护就显得格外重要了.2009年10月第36卷 第5期 西安电子科技大学学报(自然科学版)JOUR NAL OF XIDI AN UNIV ER SI TY Oct .2009Vol .36 No .5图1 电路中的异常损伤国外对于ESD 的研究始于上世纪末,全球各大公司都将ESD研究作为可靠性研究的重点,ESD 设计也成为可靠性设计的关键,现在已有800余项美国专利发表,而且逐年还有递增趋势.与ESD相关的研究论文累计有几千篇,IEEE 每年都会收录大概一百多篇ESD 方面的论文.但是纵观这些专利和研究论文发现,目前对于新的电路结构的研究和改进不是很多,还局限于以往的那几种成熟的电路上面,工作重点在于器件方面,以使用新的器件结构来获得更好的静电防护效果.但是这样做的结果提高了电路的成本.笔者设计的保护电路结构,使用的是0.18μm 工艺下的普通器件.由于使用了新的反馈技术,既能有效地提高电路的抗静电能力,而且不会提高制造成本.1 动态检测的保护电路图2给出了动态检测电路示意图.图2 动态检测电路示意图这种保护电路使用RC 网络来侦测ESD 电压,把侦测到的ESD 电压通过一个反相器输送到箝位器件上,将静电电流泄放掉.箝位器件的种类很多,有NM OS 器件、S TFOD 器件等.其中S TFOD 器件具有较强的单位静电释放能力,可以在较小的面积下提供高的防护电压.这种电路的ESD 脉冲上升时间仅有10ns 左右,电路正常上电延迟时间大概是1μs ~1ms 之间,而ESD 侦测电路中RC 时间常数介于这两者之间.当一个正的ESD 脉冲来临时,电容C 充电速度没有静电电压的上升速度快,A 点的电压就为低电压`0',PMOS 导通,将静电加载在箝位晶体管的栅极,形成一个低阻通路,箝位NMOS 器件开启,泄放ESD 电流.当电容充电完毕时,A 点的电位为`1',箝位晶体管的栅极电压为`0',晶体管关闭.在电路正常工作的时候,A 点是高电压,使箝位器件的栅极电压处于低电位,形成一个高阻断路,不影响内部电路的正常工作.在图2(b )的输出结果中,上升时间为10ns ,脉冲电压幅度为5V ,V (A ),V (B )分别是在脉冲电压作用下A 点和B 点电压的波形.这种电路最大的缺点是:在ESD 电压来临之际,箝位器件在泄放完静电以后不能及时关闭,使得静电电压在箝位器件的栅上保持时间较长,可能导致箝位器件发生热电击穿.为了有效地保护箝位器件的栅,使其免于遭受热电击穿.就需要特别设计RC 网络时间常数和电阻R 的大小.R 值太大的话,保持时间太长,会损坏器件的栅极;R 值如果太小,保持时间很短,不能将电流泄放完毕.研究结果表明,栅压最佳保持时间一般在20~30ns 之间.由于集成电路中电阻和电容的工艺参数漂移通常都很严重,而且集成电路的工艺角比较多,所以要很好地控制R 值的大小比较困难.同时,设计中使用了电容,而0.18μm 工艺中的单位面积MOS 电容为1fF /μm 2,通常电容会占用很大的芯片面积,设计中需要综合考虑两者的影响.868 西安电子科技大学学报(自然科学版) 第36卷2 采用反馈和动态延时的保护电路2.1 保护电路结构和工作原理 笔者设计了一种新的电路,即采用反馈以及动态延时结构[6-8].保护电路结构如图3所示.电路采用了RC 网络检测静电电压的变化,将A 点的电压通过一个反相器传输到B 点,再在B 点接一个倒比管,作进一图3 采用反馈和动态延时的保护电路步延时,最后传输到箝位器件上,通过控制箝位器件的开启,将静电泄放掉.该电路和普通电路最大的区别是:在检测电路上加了一个NMOS 反馈器件,同时采用了一个倒宽长比的NM OS 器件作为一级延迟器件.这个反馈器件的特征尺寸不用很大,通常为反相器的NMOS 器件特征尺寸的1/2到1/3.它在静电电压来临时形成一个低阻通路,同时也起到泄放电流的目的,加大了电流的泄放力度,减少最后一级主泄放通路的压力.由于采用了反馈操作,使得电路能够在静电发生时间内迅速地将静电电流泄放掉,及时将保护电路关闭,避免将箝位器件的栅氧化层损坏,同时避免产生误操作.综合考虑芯片面积和栅压保护时间,笔者在设计中使用的电阻为60k Ψ,电容为1.5pF .在电路正常工作情况下,电容的作用使A 点的电位为`0',反向器的作用使B 点的电位为`1',NMOS 导通.C 点的电位降为`0',箝位晶体管关闭.从而保证在电路正常工作情况下,静电保护电路关闭,不会影响内部电路的正常工作.但是当静电来临时,由于RC 时间常数小于静电脉冲上升的时间,A 点的电压跟随静电电压变为`1',这样,B 点的电压就为`0',NM OS 关闭,因此C 点的电压为`1',最后一级箝位晶体管开启,将静电放电电流泄放掉[9].随着电容的不断充电,A 点的电势逐渐降低,各器件工作状态开始反转.反馈NM OS 及时开启,A 点的电势迅速降为`0',最后一级箝位器件栅上面的电压保持时间不会过长,有效地保护了箝位器件的栅极.因为对于0.18μm 的工艺来说,栅氧化层厚度只有4nm ,能够承受的最大电压只有几伏.因此,栅上面的静电电压不能维持太长时间,一般为几十纳秒就可以了,这样既可以将静电电流泄放掉,还可以有效地保护箝位器件的栅极.2.2 电压特性设计采用的是台积电(TSM C )1.8V 1P6M 0.18μm CM OS 的工艺,RC 时间常数设置为90ns ,对于每种工艺角都进行研究和分析.图4是在SS 工艺角静电作用下C 点的电压波形.采用5V 脉冲电压,上升时间为10ns .从结果可以看出,在最坏的情况SS 工艺角下,箝位器件的栅压在保持了35ns 后,迅速降为`0',箝位器件处于关闭状态.由于采用负反馈器件,电路可以产生一个振荡回路,使A 点和B 点电压保持稳定,强化了保护电路中各器件的工作状态.图4 SS 工艺角静电作用下C 点电压波形图5 快速上电情况下C 点的电压波形 在芯片正常上电情况下,箝位器件的峰值电压仅仅只有几十毫伏,保护电路不会开启,不会影响内部电路的正常工作.但是有些电路的上电速度比较快,就有可能造成保护电路将这种正常上电误以为是静电来临,从而开启导通,影响内部电路正常工作.取它们能够达到的最快上电速度1μs 进行研究,图5是正常上电情况下C 点的电压波形.可以发现这个时候箝位器件的栅压不到200mV ,低于箝位器件的阈值电压,而且保869第5期 刘红侠等:0.18μm CM OS 工艺下的新型ESD 保护电路设计持时间只有几十纳秒,这样电路仍然能够在快速上电情况下处于关闭状态,不会影响电路正常工作状态,避免电路出现误操作现象.2.3 温度特性图6是静电作用下,不同温度下C点的电压波形.对不同的工艺角,从-40℃到125℃都进行温度扫描分析,可以发现电路即使在最坏情况下(125℃,SS工艺角),栅上面的电压保持时间不超过50ns,电路也能起到正常的保护作用.由此可以得出结论,这种保护电路能够适应在不同温度下工作的需求.图6 静电作用下,不同温度下C点的电压波形图7 电源噪声影响下,C点的电压波形2.4 噪声特性正常上电情况下,电源上面会有一些噪声出现,这些噪声通常具有高的转换速度,也有可能会触发保护电路,使电路开启.因此,在1.8V正常工作电压下,加上峰值为0.2V,频率为250M H z的方波,进行噪声分析.图7是在电源噪声影响下C点的电压波形.从结果可见,在这种情况下,箝位晶体管的栅压不超过50mV,不能开启,不会产生误操作.图8 正常工作情况下,保护电路的漏电流2.5 漏电流特性当整个电路都处在正常工作状态时,保护电路的漏电流是一个很关键的参数.从图8可知,在1.8V1P6M0.18μm CM OS工艺下,当电源电压从0V变化到3V的时候,保护电路的漏电流从0变化到190pA,而使用1.8V供电,漏电流只有110pA,低于1.8V工艺下,漏电流不得超过1nA的要求.此时保护电路的功耗也不到0.2nW,完全符合设计要求.3 总 结笔者设计了一款新型的电源和地之间ESD保护电路.该电路采用单管M OS器件产生反馈,使得保护电路在静电泄放完毕以后能够及时关闭,栅压保持时间在最坏情况下也不超过50ns,既能有效地保护箝位晶体管的栅极,还能有效地保护内部电路.同时由于采用了动态延时电路,使得电路能够有效地抑制错误触发和电源噪声.在正常工作情况下,电路的漏电流仅有110pA,功耗很小,只有不到0.2nW,不会影响内部电路的特性.和常规的保护电路相比,笔者设计的电路具有更好的保护效果.此外,该电路采用了0.18μm工艺下的普通器件,并没有使用特殊器件以及工艺,可以大大节省电路的成本.参考文献:[1]K er M D.W ho le-chip ESD P ro tectio n Desig n w ith Efficient VDD-to-V SS ESD Clamp Circuits fo r Submicr on CM O S V L SI[J].IEEE T rans o n Electronic Devices,1999,46(1):173-183.[2]Andrea C,Simo ne G,A ugusto T,e t al.Electro static Discha rge Effects in U ltrathin G ate O xide M O SFET s[J].IEEET rans on Devices and M aterials Reliability,2006,6(1):87-94.[3]Smith J C,Boselli G.A M OSF ET Pow er supply clamp with feedback enhanced trig ge ring fo r ESD pr otectio n in adv ancedCM O S technologies[J].M icr oelectr onics Reliability,2005,45(2):201-202.(下转第926页)[4]叶世榕.G PS非差相位精密单点定位理论与实现[D].武汉:武汉大学,2002.Y e Shirong.T heo ry and Its Realizatio n of GP S Pr ecise Point Po sitioning U sing Un-differenced P hase O bser vatio n[D].W uhan:W uhan U niver sity,2002.[5]张小红,动态精度单点定位(P PP)的精度分析[J].全球定位系统,2006(1):7-8.Zhang Xiaohong.P recision A naly sis o f Kinematic Precise Po io nt P ositioning[J].G nss Wo rld o f China,2006(1):7-8.[6]李天文.G PS原理与应用[M].北京:科学出版社,2006:115-130.[7]李征航,黄劲松.G PS测量与数据处理[M].武汉:武汉大学出版社,2005:38-74.[8]W u J T,Wu S C,Hajj G A,et al.Effects of A ntenna O rientation o n GP S Car rier P ha se[J].M an Geo de tica,1993(18):91-98.[9]M cCar thy D D.I ERS Technical N o te21,IERS Convention[R].Paris:U S N aval Obse rva to ry,1996:55-65.[10]T eunissen P J G,A miri-Simkoo ei A R.Least-squares V ariance Co mpo nent Estimation[J].J G eod,2008(82):65-82.[11]D ach R,H ug entobler U,F ridez P,et al.Bernese G PS So ftwa re Ve rsion5.0[S].Bern:A stro nmical I nstitute,U nive rsity of Be rn,2007:143-144.[12]K ing R W,Bock Y.Documentation for the G AM I T G PS A naly sis Sof twar e[R].Cambridge:M assachusetts Institute o fT echno lo gy,1999.[13]李耀清.实验的数据处理[M].合肥:中国科技大学出版社,2003:54-60.(编辑:郭 华) (上接第870页)[4]K er M D,Chen J H.Self-Subst rate-T rigg ered T echnique to Enhance T urn-O n U nifo rmity of multi-Finge r ESD P ro tectionDev ices[J].IEEE So lid-State Circuit,2006,41(11):2601-2609.[5]Ker M D,L in K H.T he Impac t o f Low-holding-vo ltag e I ssue in Hig h-voltage CM OS Technolo gy and Design of L atchup-f ree Po wer-rail ESD Clamp Circuit fo r LCD D riv er IC[J].IEEE So lid-State Cir cuit,2005,40(8):1751-1759.[6]杜鸣,郝跃.CM O S工艺下栅耦合ESD保护电路[J].西安电子科技大学学报,2006,33(4):547-549.D u M ing,H ao Yue.Desig n o f the ESD Pro tection Circuit with the Ga te-co uple T echnique in CM O S Technology[J].Jo ur nal of Xidian Univ ersity,2006,33(4):547-549.[7]Chou H M,Lee J W,Li P Y.A F lo ating Ga te Desig n fo r ESD Pr otectio n Cir cuits[J].T he V LSI Journal,2007,40(2):161-166.[8]Feng Haiqiang,Chen Guang,Z han Ro uy ing,et al.A M ix ed-mo de ESD P ro tection Circuits Simula tion-de sig nM etho do lo gy[J].IEEE So lid-State Circuit,2003,38(6):995-1006.[9]K er M D,Chang W J.ESD P rotectio n Desig n with O n-chip ESD Bus and H ig h-v oltage-to ler ant ESD Clamp Circuit forM ixed-vo ltag e I/O Buffer s[J].I EEE Solid-S ta te Circuit,2008,55(6):1409-1416.(编辑:郭 华) 。

2001年4月第2期电子产品可靠性与环境试验E LECTRONIC PRODUCT RE LI ABI L ITY AND ENVIRONMENT A L TESTI N GApril.2001N o.2CMOS集成电路的ESD设计技术于宗光(信息产业部电子第五十八研究所,江苏 无锡 214035)摘要:首先论述了C M OS集成电路ES D保护的必要性,接着介绍了C M OS集成电路ES D保护的各种设计技术,包括电流分流技术、电压箝位技术、电流均衡技术、ES D设计规则、ES D注入掩膜等。

采用适当的ES D保护技术,018μm C M OS集成电路的ES D能力可以达到3000V。

关键词:互补金属氧化物半导体;集成电路;静电放电;技术;设计中图分类号:T N432 文献标识码:ADesign Technologies for ESD Protection of CMOS IC p sY U Z ong-guang(Wuxi Microelectronics Institute,Wuxi214035,China)Abstract:The necessity of ES D protection for C M OS IC is discussed first1The various design tech2 niques for C M OS IC’s ES D protection,such as current shunt,v oltage clam p,current crowding preven2 tion technology,design rules for ES D,ES D im plant M ASK technology,are presented1With the proper ES D protection technologies,the ES D tolerance of3000V are obtained for018μmicro C M OS ICs1K eyw ords:C M OS;IC;ES D;technology;design1 引 言多数C M OS集成电路的输入端是直接接到栅上。

CMOS电路ESD保护结构设计

张伟;唐拓

【期刊名称】《微处理机》

【年(卷),期】2010(31)2

【摘要】静电放电是CMOS电路中最为严重的失效机理之一,严重的会造成电路自我烧毁.论述了CMOS集成电路ESD保护的必要性,研究了在CMOS电路中ESD保护结构的设计原理,分析了该结构对版图的相关要求,重点讨论了在I/O电路中ESD保护结构的设计要求.

【总页数】3页(P30-31,35)

【作者】张伟;唐拓

【作者单位】中国电子科技集团公司第四十七研究所,沈阳,110032;中国电子科技集团公司第四十七研究所,沈阳,110032

【正文语种】中文

【中图分类】TN4

【相关文献】

1.CMOS电路芯片ESD保护电路设计技术的发展 [J], 赵近

2.亚微米BiCMOS电路纵向NPN管的ESD保护研究 [J], 王德进;聂卫东;张炜;李冰

3.亚微米CMOS电路中VDD-VSS ESD保护结构的设计 [J], 蒋红利;刘明峰;于宗光

4.CMOS电路中ESD保护结构的设计 [J], 王大睿

5.用于双极电路ESD保护的SCR结构设计失效分析 [J], 冯筱佳;刘玉奎;朱坤峰因版权原因,仅展示原文概要,查看原文内容请购买。

CMOS电路是当今集成电路中最常见的一种电路类型,而ESD (Electrostatic Discharge,静电放电)则是一个不可忽视的问题。

在CMOS电路中,ESD对电路的损坏可能会导致严重影响甚至可能造成整个系统的失效。

了解CMOS电路中的ESD泄放原理对于电路设计和集成电路的稳定性至关重要。

一、CMOS电路简介1. CMOS电路特点CMOS电路是一种使用互补型金属氧化物半导体(Complementary Metal-Oxide-Semiconductor,简称CMOS)技术制作的集成电路。

CMOS电路具有低功耗、高噪声抑制、集成度高等优点,因此被广泛应用于数字集成电路、微处理器、存储器等领域。

2. CMOS电路结构CMOS电路由P型金属氧化物半导体(P-MOS)和N型金属氧化物半导体(N-MOS)两种类型的MOSFET器件组成。

它利用P-MOS和N-MOS的互补特性,实现高密度和低功耗。

二、ESD泄放原理1. ESD的危害ESD是指人体或物体在静电充电后,与另一对象或地面突然放电的现象。

在现代集成电路中,ESD是造成电路损坏和性能降低的主要原因之一。

当ESD发生时,电流冲击会对CMOS电路中的敏感元件产生破坏性影响。

2. ESD泄放原理ESD泄放是指在CMOS电路中设计专门的保护电路,以接受和限制ESD脉冲,从而保护电路不受损坏。

它通过引入ESD元件并将其连接到电源和地,以吸收来自ESD事件的能量,从而降低ESD对电路的损害。

三、CMOS电路中的ESD保护技术1. ESD保护器件在CMOS电路中,常用的ESD保护器件包括二极管、二极管堆、金属氧化物半导体场效应晶体管(Metal-Oxide-Semiconductor Field-Effect Transistor,简称MOSFET)等。

这些保护器件能够有效限制ESD脉冲的能量,保护主要电路不受损坏。

2. ESD保护电路设计原则在设计CMOS电路的ESD保护电路时,需要考虑ESD脉冲的能量、速度以及保护电路的响应时间等因素。

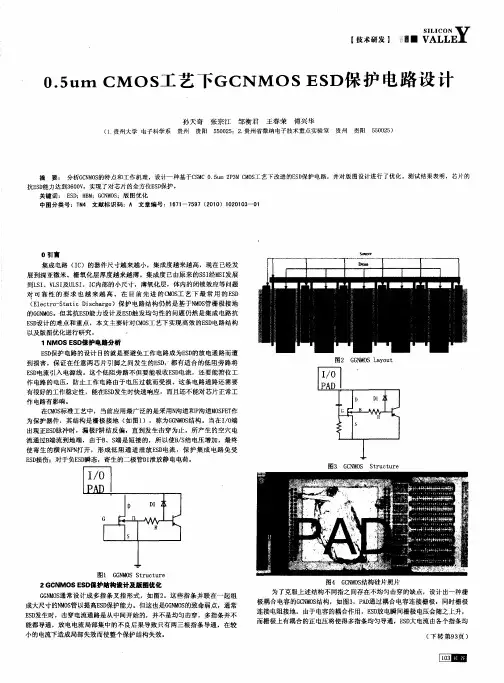

低触发电压的可控硅结构保护电路设计的详细介绍低触发电压的可控硅ESD 保护结构的设计摘要:当前的集成电路设计中大量采用了可控硅的设计结构来进行ESD 的保护,但是一般的SCR 保护结构很难满足现在低电压,以及一些特殊要求的集成电路ESD 保护的要求。

研究一种低触发电压的可控硅结构保护电路,通过和工艺寄生参数的结合,满足了低触发电压的设计要求。

关键词:集成电路设计;静电保护;可控硅结构;触发电流1 引言静电放电(ESD)对CMOS 集成电路的可靠性构成了很大威胁[1]。

随着集成电路设计水平的提高和应用领域的扩大,对于CMOS 集成电路来说,由于特征尺寸较小,电源电压较低,ESD 保护仅仅采用传统的二极管结构已经不能满足要求。

目前广泛使用的ESD 保护电路中,可控硅(SCR)结构具有单位面积下最高的ESD 保护性能[2],同时具有很好的大电流特性[3]。

如图1 所示,是常用的SCR 结构示意图。

在P 型衬底上有相邻的N 阱及P 阱, P 阱中的P 型注入区,P 阱中的N 型注入区,N 阱中的P 型注入区,N 阱中的N 型注入区组成了PNPN 半导体结构。

图2 为图1 所示SCR 保护结构的等效电路图。

其结构包含一个寄生PNP 三极管Q1,一个寄生NPN 三极管Q2,以及寄生电阻R1,R2。

图1 所示SCR 保护结构的触发电压为P 阱和N 阱所形成PN 结的雪崩击穿电压。

一般情况下P 阱和N 阱的掺杂浓度较低,触发电压通常大于几十伏。

在这种情况下,有可能SCR 保护结构还未开启,CMOS 集成电路的内部电路由于ESD 放电而被损坏。

为了降低SCR 保护结构的触发电压,同时满足电路应用中大触发电流的要求,本文设计了一种改进的SCR 保护结构,可以有效地解决上述问题。

2 高触发电流和低开启电压的SCR 结构的设计LVTSCR 的设计原理。

对于低压触发的SCR(Low-V oltage Triggered SCR,LVTSCR)的。

CMOS电路中ESD保护结构的设计作者 王大睿上海交通大学 微电子工程系摘 要:本文研究了在CMOS 工艺中I/O 电路的 ESD保护结构设计以及相关版图的要求,其中重点讨论了PAD到VSS电流通路的建立。

关键词:ESD保护电路,ESD设计窗口,ESD 电流通路Construction Strategy of ESD Protection Circuit Abstract:The principles used to construct ESD protection on circuits and the basic concept ions of ESD protection design are presented.Key words:ESD protection/On circuit, ESD design window, ESD current path1引言静电放电(ESD,Electrostatic Discharge)给电子器件环境会带来破坏性的后果。

它是造成集成电路失效的主要原因之一。

随着集成电路工艺不断发展,互补金属氧化物半导体(CMOS,Complementary Metal-Oxide Semiconductor)的特征尺寸不断缩小,金属氧化物半导体(MOS, Metal-Oxide Semiconductor)的栅氧厚度越来越薄,MOS管能承受的电流和电压也越来越小,因此要进一步优化电路的抗ESD性能,需要从全芯片ESD保护结构的设计来进行考虑。

2ESD的测试方法ESD模型常见的有三种,人体模型(HBM ,Human Body Model)、充电器件模型(CDM,Charge Device Model)和机器模型(MM,Machine Mode),其中以人体模型最为通行。

一般的商用芯片,要求能够通过2kV静电电压的HBM检测。

对于HBM放电,其电流可在几百纳秒内达到几安培,足以损坏芯片内部的电路。

图1人体模式(HBM)的等效电路。

人体的等效电阻为1.5kΩ。

进入芯片的静电可以通过任意一个引脚放电,测试时,任意两个引脚之间都应该进行放电测试,每次放电检测都有正负两种极性,所以对I/O引脚会进行以下六种测试:1)PS模式:VSS接地,引脚施加正的ESD电压,对VSS放电,其余引脚悬空;2)N S模式:VSS接地,引脚施加负的ESD电压,对VSS放电,其余引脚悬空;3)P D模式:VDD接地,引脚施加正的ESD电压,对VDD放电,其余引脚悬空;4)N D模式:VDD接地,引脚施加负的ESD电压,对VDD放电,其余引脚悬空;5)引脚对引脚正向模式:引脚施加正的ESD电压,其余所有I/O引脚一起接地,VDD和VSS引脚悬空;6)引脚对引脚反向模式:引脚施加负的ESD电压,其余所有I/O引脚一起接地,VDD和VSS引脚悬空。

VDD引脚只需进行(1)(2)项测试3ESD保护原理ESD保护电路的设计目的就是要避免工作电路成为ESD的放电通路而遭到损害,保证在任意两芯片引脚之间发生的ESD,都有适合的低阻旁路将ESD电流引入电源线。

这个低阻旁路不但要能吸收ESD电流,还要能钳位工作电路的电压,防止工作电路由于电压过载而受损。

这条电路通路还需要有很好的工作稳定性,能在ESD发生时快速响应,而且还不能对芯片正常工作电路有影响。

4CMOS电路ESD保护结构的设计根据ESD的测试方法以及ESD保护电路的原理可知,在芯片中我们需要建立六种低阻ESD电流通路,它们分别是:1)引脚焊块(PAD)到VSS的低阻放电通路2)VSS到PAD的低阻放电通路3)PAD到VDD的低阻放电通路4)VDD到PAD的低阻放电通路5)PAD受到正向ESD放电时,PAD到PAD的通路6)PAD受到负向ESD放电时,PAD到PAD的通路7)VDD与VSS之间的电流通路大部分的ESD电流来自电路外部,(CMD模型除外,它是基于已带电的器件通过管脚与地接触时,发生对地放电引起器件失效而建立的),ESD保护电路一般设计在PAD旁,输入输出(I/O, Input/Output)电路内部。

典型的I/O电路示意图(如图2),它的工作电路由两部分组成输出驱动(Output Driver)和输入接收器(Input Receiver). ESD通过PAD导入芯片内部,因此I/O里所有与PAD直接相连的器件都需要建立与之平行的ESD低阻旁路,将ESD电流引入电压线,再由电压线分布到芯片各个管脚,降低ESD 的影响。

具体到I/O,就是与PAD相连的输出驱动和输入接收器。

根据对ESD低阻放电通路的要求,上面六条通路必须保证在ESD发生时,形成与保护电路并行的低阻通路,旁路ESD电流,且能立即有效地钳位保护电路电压。

而在这两部分正常工作时,不影响电路的正常工作。

图2典型的I/O电路示意图输出驱动图3是加入ESD 电流通路的I/O 电路,在图3所列的所有器件中,HBM 模式下 输出驱动上的N 型MOS 管(NMOS)是最容易受损坏的。

因此下面会对输出驱动中NMOS 管的ESD 低阻旁路给出比较详细的介绍。

z PS 模式下PAD, VSS 之间的ESD 低阻旁路每一个I/O 引脚电路中都应建立一个PAD 到VSS 的ESD 保护电路(图4)。

(a)图4 PAD对VSS反向ESD放电时的电流通路.常用的ESD保护器件有电阻、二极管、双极性晶体管、MOS管、可控硅(SCR)等。

由于MOS管与CMOS工艺兼容性好,我们常采用MOS管构造保护电路。

CMOS 工艺条件下的NMOS管有一个横向寄生n-p-n(源极-p型衬底–漏极)晶体管,如图5(a)所示V(b)这个寄生的晶体管开启时能吸收大量的电流。

利用这一现象可在较小面积内设计出较高NMOS(GGNMOS,Gate当ESD发生时,漏极和衬底的耗尽区将发生雪崩,并伴随着电子空穴对的产生。

一部分产生的空穴被源极吸收,其余的流过衬底。

由于衬底电阻PN 结正偏时,被加速,产生电子、空穴的碰撞电离,从而形成更多的电子空穴对,使流过n-p-n晶体管的电流不断增加,最终使NMOS晶体管发生二次击穿,此时的击穿不再可逆,则NMOS管损坏。

图5(b)展示了这一过程的I-V特性,其中(Vt1,It1)为衬底和源之间的PN结正偏,横向晶体管开启时的电压电流,(Vh,Ih)为NMOS横向晶体管的钳位电压和电流,(Vt2,It2)是NMOS横向晶体管发生二次击穿时的电压和电流。

NMOS管正常工作的区域在Vop之内。

为了防止如噪音等外界影响使NMOS在正常工作区域触发,Vop与Vh之间需要一个安全区。

Vox是NMOS管的栅氧击穿电压 .如果ESD保护器件的电压设计在安全区与栅氧击穿区之间,电流设计在It2以内。

ESD保护器件就能在不损伤管子也不影响工作电路的情况下完成对电路的保护我们可以通过ESD钳制电路的HBM耐压值来推断ESD钳制电路器件的大概宽度。

如果GGNMOS可通的最大电流密度是10mA/μm, 则要达到2kv HBM耐压值 这个ESD钳制电路要经受1.33A的电流(图1),NMOS的宽度至少是133μm。

为了在较小的面积内画出大尺寸的NMOS管子,在版图中我们采用常把它画成手指狀(finger-type),把NMOS管中的单一“手指”作为一个单元,然后多次引用这个单元。

画版图时应严格遵循I/O ESD的设计规则.为了进一步降低输出驱动上NMOS在ESD时两端的电压,可在ESD保护器件与GGNMOS之间加一个电阻(图6)。

这个电阻不能影响工作信号,因此不能太大。

画版图时可采用多晶硅(poly)电阻。

(a)在ESD发生时,不一定每一个NMOS“手指”会一齐导通,这样ESD保护电路的有效耐压值就由开始导通的几个NMOS“手指”决定。

为了避免这种情况,提高ESD器件防护能力可在NMOS栅极和地之间加一个电阻Rgate(图7)。

由于栅漏间寄生电容的存在,ESD瞬态正电压加在PAD上时,图7中NMOS上的栅极也会耦合一个瞬态正电压,因此NMOS上的每一个“手指”会一齐导通, 不用到达Vt1就能进入寄生横向晶体管骤回崩溃区(snapback region). 栅极电压由Rgate放电到地. 这个瞬态电压持续的时间由栅漏寄生电容和栅地电阻组成的RC时间常数决定。

栅地电阻必须足够大,保证在电路正常工作时这个栅极耦合NMOS管是关闭的。

图7 a)在输出驱动NMOS管栅地间加上电阻b)栅地加电阻后,ESD时的等效电路图,Cdg为NMOS管栅漏间的寄生电容只采用初级ESD保护,在大ESD电流时,电路内部的管子还是有可能被击穿。

如图8所示,GGNMOS导通,理想状况下(图8a),衬底和金属连线上都没有电阻,吸收大部分ESD电流。

实际情况是(图8b),GGNMOS导通,由于ESD电流很大,衬底和金属连线上电阻都不能忽略,此时GGNMOS并不能钳位住输入接收端栅电压,因为让输入接收端氧化栅的电压达到击穿电压的是GGNMOS与输入接收端衬底间的IR压降。

为避免这种情况可在输入接收端附近加一个小尺寸GGNMOS进行二级ESD保护(图8c),用它来钳位输入接收端栅电压。

在画版图时,必须注意将 二级ESD保护电路紧靠输入接收端,以减小输入接收端与二级ESD保护电路之间衬底及其连线的电阻。

z NS模式下VSS,PAD之间ESD低阻旁路在ESD过程中,如果PAD对VSS负向放电,放电通路由p型衬底和每一个与PAD 相连NMOS的漏极产生的寄生二极管组成(图9)所示。

此时二极管正向导通,因为二极管正向导通电压小,导通电阻小,有很高ESD防护能力,PAD对VSS的负向放电可以很容易的分布到芯片各个管脚。

图9 PAD对VSS反向ESD放电时的电流通路z PD模式下PAD,VDD之间ESD低阻旁路在ESD过程中,如果PAD对VDD正向放电,放电通路由N阱和每一个与PAD相连PMOS的漏极产生的寄生二极管组成。

此时二极管正向导通,有很高ESD防护能力,PAD 对VDD的正向放电可以很容易的分布到芯片各个管脚。

z ND模式下VDD,PAD之间ESD低阻旁路在ESD过程中,如果PAD对VDD负向放电,放电通路如图10。

PAD对VDD负向放电通路由PMOS横向寄生晶体管组成。

电路原理和结构与PS模式下PAD到VSS的电路类似。

输出驱动图10 PAD对VDD反向放电电流通路z VDD,VSS之间ESD低阻旁路VDD,VSS的PAD上也可能发生ESD事件,因此也需要有ESD保护。

在ESD过程中,如果VDD对VSS正向放电,基本的VDD到VSS的保护电路结构是在VDD和VSS之间加一个大尺寸的GGNMOS(如图11)。

为了提高VDD到VSS之间保护电路的效率,减小电源线间寄生电阻电容对其ESD保护性能的影响,可将这个保护电路复制多份,分布到芯片中去。