整理为word 格式

电子科技大学网络教育考卷(C 卷)

(20 年至20 学年度第 学期)

考试时间 年 月 日(120分钟) 课程 数字逻辑设计及应用(本科) 教师签名_____

大题号 一 二 三 四 五 六 七 八 九 十 合 计 得 分

一、填空题(每空1分,共20分)

1、10111012= 135 8= 5D 16= 1110011 格雷码

2、FF 16= 255 10= 001001010101 8421BCD = 010********* 余3码

3、已知某数的反码是1010101,则该数的对应的原码是 1101010 ,补码是 1101011 ;

4、逻辑运算的三种基本运算是 与或非 ;

5、一个逻辑在正逻辑系统下,表达式为B A +,则该逻辑在负逻辑系统下,表达式为 AB ;

6、逻辑式A /(B+CD /)的反演式为 A+B /(C /

+D) ; 7

、

已

知

∑=)

3,1,0(),,(m C B A F ,则

∑=m

F /( 2,4,5,6,7 )M ∏=( 2,4,5,6,7 );

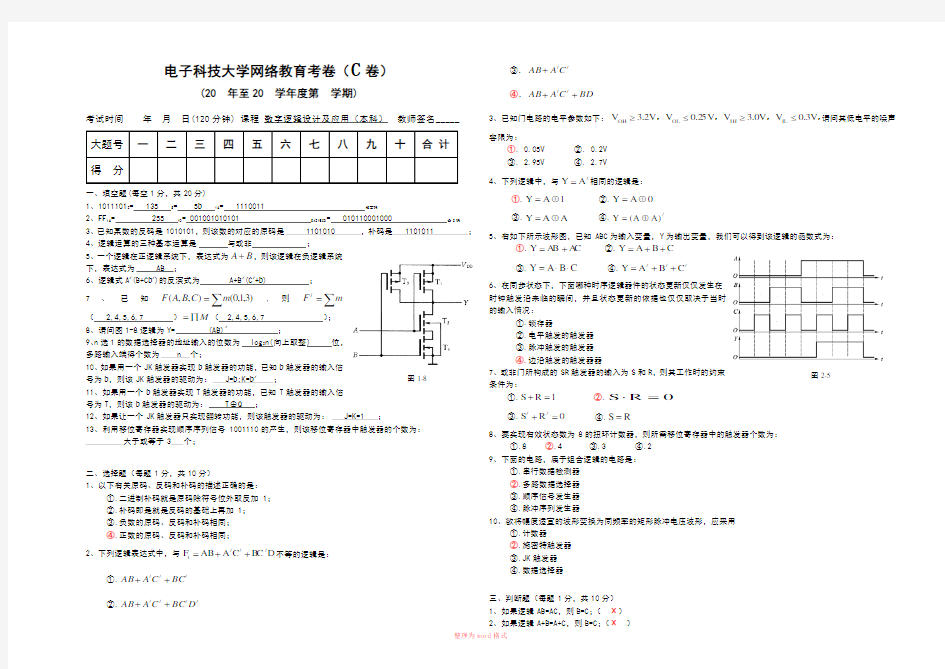

8、请问图1-8逻辑为Y= (AB)/

; 9、n 选1的数据选择器的地址输入的位数为 log 2n(向上取整) 位,多路输入端得个数为 n 个; 10、如果用一个JK 触发器实现D 触发器的功能,已知D 触发器的输入信

号为D ,则该JK 触发器的驱动为: J=D;K=D /

;

11、如果用一个D 触发器实现T 触发器的功能,已知T 触发器的输入信号为T ,则该D 触发器的驱动为: T ⊕Q ;

12、如果让一个JK 触发器只实现翻转功能,则该触发器的驱动为: J=K=1 ;

13、利用移位寄存器实现顺序序列信号1001110的产生,则该移位寄存器中触发器的个数为: 大于或等于3 个;

二、选择题(每题1分,共10分)

1、以下有关原码、反码和补码的描述正确的是: ①.二进制补码就是原码除符号位外取反加1; ②.补码即是就是反码的基础上再加1; ③.负数的原码、反码和补码相同; ④.正数的原码、反码和补码相同;

2、下列逻辑表达式中,与D BC C A AB F /

/

/

1++=不等的逻辑是: ①./

/

/

BC C A AB ++ ②./

/

/

/

D BC C A AB ++

③./

/C A AB + ④.BD C A AB ++/

/

3、已知门电路的电平参数如下:,,,,V 3.0V V 0.3V V 25.0V V 2.3V L I IH OL OH ≤≥≤≥请问其低电平的噪声容限为:

①. 0.05V ②. 0.2V ③. 2.95V ④. 2.7V

4、下列逻辑中,与/A Y =相同的逻辑是:

①.1A Y ⊕= ②.0A Y ⊕= ③.A A Y ⊕= ④./

)A A (Y ⊕=

5、有如下所示波形图,已知ABC 为输入变量,Y 为输出变量,我们可以得到该逻辑的函数式为:

①.AC AB Y += ②.C B A Y ++=

③.C B A Y ??= ④./

/

/

C B A Y ++=

6、在同步状态下,下面哪种时序逻辑器件的状态更新仅仅发生在时钟触发沿来临的瞬间,并且状态更新的依据也仅仅取决于当时的输入情况:

①.锁存器

②.电平触发的触发器

③.脉冲触发的触发器 ④.边沿触发的触发器器

7、或非门所构成的SR 触发器的输入为S 和R ,则其工作时的约束条件为:

①.1R S =+ ②.0R S =?

③.0R S /

/

=+ ④.R S =

8、要实现有效状态数为8的扭环计数器,则所需移位寄存器中的触发器个数为:

①.8 ②.4

③.3 ④.2

9、下面的电路,属于组合逻辑的电路是:

①.串行数据检测器 ②.多路数据选择器 ③.顺序信号发生器 ④.脉冲序列发生器

10、欲将幅度适宜的波形变换为同频率的矩形脉冲电压波形,应采用 ①.计数器

②.施密特触发器 ③.JK 触发器 ④.数据选择器

三、判断题(每题1分,共10分) 1、如果逻辑AB=AC ,则B=C ;( Х) 2、如果逻辑A+B=A+C ,则B=C ;(Х )

姓名__________________ 专业名称__________________ 班号________________学号__________________教学中心_________________

…………………… …… … … … … …密………………… …… … … … … ……封……………… …… … … …线… … … …… … … ……………………

图1-8 图2-5

整理为word 格式

3、如果逻辑AB+AC=1,则A=1;( √ )

4、如果逻辑AB+AC=0,则A=0;(Х )

5、若干个逻辑信号进行异或操作,如果这些信号中逻辑“1”的个数为奇数,则输出结果为1;( √ )

6、A ⊕1=A /

;( √ ) 7、A+A+A=A ·A ·A ;( √ )

8、对于CMOS 集成门电路而言,与门的结构比与非门的结构更为简单一些;(Х ) 9、TTL 逻辑比CMOS 逻辑的运行功耗更低,所以更利于集成;(Х ) 10、影响CMOS 集成门电路的运行速度主要是传输延迟和转换时间;( √ )

四、卡诺图化简(8分)

将逻辑F (A,B,C,D )=Sm(0,1,3,4,6,7,14,15)+d(8,9,10,11,12,13)化成最简或与函数式;

F=C /D /

+B /

D+BC

答案不唯一

五、组合逻辑分析,要求如下(8分)

完成图5所示电路的逻辑分析,并写出: 1、 逻辑Y 的函数式 2、 写出该逻辑的真值表 1、 函数式

2、 真值表

六、时序逻辑分析,要求如下:(14分)

请分析图6所示电路的逻辑,并写出: 1、 驱动方程和输出方程; 2、 状态方程;

3、 画出状态转换图或者状态转换表;

驱动方程:21'?=Q X EN ,

12Q J =,12=K

状态方程:121121111*1Q Q Q X Q Q X Q EN Q EN Q ?+?'+'?'?=?'+'?=

122222*2Q Q Q K Q J Q ?'=?'+'?=

输出方程:21'?+?'=Q X Q X Z 状态表:

或者状态图:

图5

图6

C

B A

C B A C

B A

C B A F /

/

/

///??+??+??+??=

整理为word 格式

七、组合逻辑设计,要求如下:(8分)

请利用一块8选1的数据选择器芯片74153来实现如下逻辑:BC AC AB Y ++=;可加一定的门电路来实现。

先对数据选择器进行扩展, 然后在赋值

八、时序逻辑设计,要求如下:(10分)

请利用移位寄存器74194和一定的门电路结构,设计一个3位的扭环计数器,要求该电路能够自行启动 1、画出能够自行启动的3位扭环计数器状态图

2、请在74194芯片上完成该逻辑,已知74194芯片的逻辑功能定义如下:

能够自行启动的3位扭环计数器,其状态图和反馈函数定义如下:

求反馈函数:

F=Q2/

+Q1/

Q0

选择右移方式,完成电路图如下:

九、时序逻辑设计,要求如下:(12分)

已知一个时序逻辑的状态转换图如图9所示。请完成该逻辑电路的设计,无须考虑自启动问题。选择D 触发器来实现。要求写出:

1、 状态方程

2、 驱动方程和输出方程;

3、 画出逻辑图

(已知三个状态的编码分别为S0:Q1Q0=00;S1:Q1Q0=01;S2:Q1Q0=10; 状态表如下:

状态方程:

Q X 0Q 1XQ 0Q 1Q X 0XQ 1Q /

/

/

*

/*+=+=

驱动方程和输出方程:

1

XQ Y 0Q X 0Q 1XQ 0Q 0D 1Q X 0XQ 1Q 1D ///*/*=+==+== 电路图略;

友情提示:本资料代表个人观点,如有帮助请下载,谢谢您的浏览!

图9

1/1