Verilog实验报告

- 格式:doc

- 大小:776.00 KB

- 文档页数:44

西安邮电大学Verilog HDL大作业报告书学院名称:电子工程学院学生姓名:专业名称:电子信息工程班级:实验一异或门设计一、实验目的(1)熟悉Modelsim 软件(2)掌握Modelsim 软件的编译、仿真方法(3)熟练运用Modelsim 软件进行HDL 程序设计开发二、实验内容my_or,my_and和my_not门构造一个双输入端的xor门,其功能是计算z=x’y+xy’,其中x和y为输入,z为输出;编写激励模块对x和y的四种输入组合进行测试仿真1、实验要求用Verilog HDL 程序实现一个异或门,Modelism仿真,观察效果。

2、步骤1、建立工程2、添加文件到工程3、编译文件4、查看编译后的设计单元5、将信号加入波形窗口6、运行仿真实验描述如下:module my_and(a_out,a1,a2);output a_out;input a1,a2;wire s1;nand(s1,a1,a2);nand(a_out,s1,1'b1);endmodulemodule my_not(n_out,b);output n_out;input b;nand(n_out,b,1'b1); endmodulemodule my_or(o_out,c1,c2);output o_out;input c1,c2;wire s1,s2;nand(s1,c1,1'b1);nand(s2,c2,1'b1);nand(o_out,s1,s2); endmodulemodule MY_XOR(z,x,y);output z;input x,y;wire a1,a2,n1,n2;my_not STEP01(n1,x);my_not STEP02(n2,y);my_and STEP03(a1,n1,y);my_and STEP04(a2,n2,x);my_or STEP05(z,a1,a2); Endmodulemodule stimulus;reg X,Y;wire OUTPUT;MY_XOR xor01(OUTPUT,X,Y);initialbegin$monitor($time,"X=%b,Y=%b --- OUTPUT=%b\n",X,Y,OUTPUT);endinitialbeginX = 1'b0; Y = 1'b0;#5 X = 1'b1; Y = 1'b0;#5 X = 1'b1; Y = 1'b1;#5 X = 1'b0; Y = 1'b1;endendmodule二、实验结果波形图:三、分析和心得通过这次的实验,我基本熟悉Modelsim 软件,掌握了Modelsim 软件的编译、仿真方法。

《数字系统设计与Verilog HDL》实验报告(五)班级: 自动1003班**: **学号: ********实验五、自动售饮料机系统设计一、实验目的1、了解及掌握状态机的基本构成用法;二、通过ModelSim软件编写程序, 用状态机可以编程设计简单的自动控制系统。

三、实验内容四、设计一个自动售饮料机。

假定每瓶饮料售价为2.5元, 可使用两种硬币, 即5角和1元, 机器有找零功能。

五、机器设计有2个投币孔, 可用2个按键来代替。

还设有2个输出孔, 分别输出饮料和找零, 提示用户取走饮料和零钱。

六、实验步骤及源程序新建工程及文件, 分别添加设计程序及测试程序, 进行编译及纠错, 编译通过后运行程序仿真进行调试得出结果。

设计模块:module sell(yi_yuan,wu_jiao, get,half_out,sell_out,reset,clk);parameter idle=0, half=1, one=2,two=3,three=4;input yi_yuan,wu_jiao,reset,clk;output get,half_out,sell_out;reg get,half_out,sell_out;reg[2:0] s;always @(posedge clk)beginif(reset)beginsell_out=0; get=0; half_out=0; s=idle;endelsecase(s)idle: beginsell_out=0; get=0; half_out=0;if(wu_jiao) s=half;else if(yi_yuan)s=one;endhalf: beginif(wu_jiao) s=one;else if(yi_yuan)s=two;endone: beginif(wu_jiao) s=two;else if(yi_yuan)s=three;endtwo: beginif(wu_jiao) s=three;else if(yi_yuan)beginsell_out=1;get=1; s=idle;endendthree: beginif(wu_jiao)beginsell_out=1; get=1; s=idle;endelse if(yi_yuan)beginsell_out=1;get=1;half_out=1; s=idle;endenddefault:beginsell_out=0; get=0; half_out=0; s=idle; endendcaseendendmodule测试模块:`timescale 1ns/1nsmodule sell_top;reg yi_yuan,wu_jiao,reset,CLK;wire get,half_out,sell_out;always #50 CLK=~CLK;initialbeginCLK =0; reset=1;#100 reset=0;yi_yuan=0;wu_jiao=0;endalways@(posedge CLK)beginwu_jiao={$random}%2;#50 wu_jiao=0;endalways@(posedge CLK)beginif(!wu_jiao)yi_yuan=1;#50 yi_yuan=0;endsell m(.yi_yuan(yi_yuan),.wu_jiao(wu_jiao), .get(get),.half_out(half_out),.sell_out(sell_out),.reset(reset),.clk(CLK));endmodule七、实验结果八、实验心得体会由于老师在实验前已经很详细的为我们讲解了这次实验的要点和要注意的问题, 所以这次实验我们完成的还是很成功的。

电子科技大学实验报告一、实验室名称:虚拟仪器实验室二、实验项目名称:交通灯设计实验三、实验学时:4学时四、实验原理假设交通灯处于南北和东西两条大街的“十”字路口,如图1所示。

用FPGA 开发板的LED 灯来模拟红、黄、绿3种颜色信号,并按一定顺序、时延来点亮LED ,如图2所示。

图3给出了交通灯的状态转移图。

设计使用频率为1Hz 的时钟来驱动电路(注1:仿真时采用1MHz 的时钟来驱动电路),则停留1个时钟可得到1S 的延时,类似停留3个时钟可得到3S 的延时,停留15个时钟可得到15S 的延时(注2:开发板工作时钟为50MHz )。

北南西东图1. 六个彩色LED 可以表示一组交通信号灯南北 东西 红 黄 绿 红 黄 绿 S0 1 0 0 0 0 1 S1 1 0 0 0 1 0 S2 1 0 0 1 0 0 S3 0 0 1 1 0 0S4 0 1 0 1 0 0S5 1 0 0 1 0 0图3. 交通灯的状态转移图顶层模块时钟分频模块状态机跳转模块图4. 交通灯的原理框图五、实验目的本实验是有限状态机的典型综合实验,掌握如何使用状态转移图来定义Mealy状态机和Moore状态机,熟悉利用HDL代码输入方式进行电路的设计和仿真的流程,掌握Verilog语言的基本语法。

并通过一个交通灯的设计掌握利用EDA软件(Xilinx ISE 13.2)进行HDL代码输入方式的电子线路设计与仿真的详细流程。

六、实验内容在Xilinx ISE 13.2上完成交通灯设计,输入设计文件,生成二进制码流文件下载到FPGA开发板上进行验证。

七、实验器材(设备、元器件)1、计算机(安装Xilinx ISE 13.2软件平台);2、BASYS2 FPGA开发板一套(带USB-MIniUSB下载线)八、实验步骤(1)新建工程,设置器件属性:在Xilinx ISE 13.2平台中,新建一个工程(注意命名规范),输入工程名称以及工程所在的目录,设置芯片的具体型号(Spartan 3E XC3S100E)、封装类型(CP132)以及编码使用的语言(Verilog)。

课程名称:Verilog数字系统设计实验实验项目:时钟姓名:专业:计算机科学与技术班级:学号:计算机科学与技术学院201年月日哈尔滨理工大学计算机科学与技术学院实验报告实验项目名称:时钟设计一、实验目的1. 掌握 Verilog HDL 语言的基本运用;2. 熟悉 QuartusⅡ的简单操作;3. 掌握一个基本 EDA 工程设计流程;4. 掌握时钟的设计基本原理。

二、实验内容计数器部分中包含有三个主要计数部分,分别是十进制、六进制以及二十四进制,其中六进制和十进制共同组成六十进制,即实现分和秒的计数,之所以将其分开是便于分别显示个位和十位,通过编写计数器,来计数信号的数量,从而实现时分秒按各自的进制正常计数,同时,将前一时钟单位的进位信号作为下一时钟单位的clk,即从后向前驱动,这样便实现了时钟的正常运转。

三、实验要点及说明1.编写各个模块的 VHDL 代码并进行编译与波形仿真, 仿真无误后生成元件符号。

2.设计数字钟电路的顶层文件,在顶层文件中调入第一步中生成的元件符号,并根据连接关系将它们连接在一起。

3.引脚分配,为顶层设计文件中的各个输入输出端口分配芯片相应的引脚。

4.下载程序到芯片,观看实验现象是否为预想的那样。

同时使用清零按键看能否实现清零,时间正常走动情况下通过按键能否实现校时。

四、实验结果下载成功后,拨动开关 DP4至髙电平,使六个数码管复位淸零;拨动开关 DP4 至低电平,数字钟开始自动计,此过程中可以通过 1键设置小时数,2 键设置分钟数。

当秒数满 60 则进一位, 分钟数满60 进一位,当显示为 23:59:59 时,秒数在加一则显示 00:00:00,同时指示一天结束的 LED 灯亮 10 秒,之后从新计时。

五、程序代码module clock(clk,rst,load,data,lamp,de, led_g,st_stop,ledcom);// clk-时钟10M,rst-复位,load-初始值设置,st_stop-启动暂停input clk,rst,load,st_stop;input [7:0] data; //初始值output lamp; //倒计时结束指示灯output [2:0]de; //数码管位选output [7:0]led_g; //数码管段码output ledcom; //指示灯公共端reg clk_g; // ..... LED扫描时钟信号......reg clk_s;// 秒时钟reg[15:0] cnt1; // 10ms 分频计数器reg[23:0] cnt2; // 1s 分频器计数器reg[3:0] bcd1; // 个位bcd码reg[3:0] bcd2; // 十位bcd码reg lamp; // 指示灯reg[1:0]state1; // 2位数码管扫描位置寄存器reg[3:0]led_g_bcd; // bcd转段码寄存器parameterLED1=3'b000,//数码管1LED2=3'b001;//数码管2assign ledcom=1;//// 10Mhz 晶振用2个分频器分别产生数码管扫描时钟和秒时钟// 10ms方波时钟clk_galways @(posedge clk)beginif (cnt1 >=50000)begincnt1 <= 0;clk_g <= ~clk_g;endelsecnt1 <= cnt1 +1'b1;end// 1s方波时钟clk_salways @(posedge clk)beginif (cnt2 >=5000000)begincnt2 <= 0;clk_s <= ~clk_s;endelsecnt2 <= cnt2 +1'b1;endalways@(posedge clk_s or negedge rst or posedge load ) beginif(!rst) //复位初始状态beginlamp<=0; //灭灯bcd1<=0; //数码管输出0bcd2<=0; //endelseif (load)beginbcd1<=data[3:0];//设置初值bcd2<=data[7:4];//endelseif (st_stop) // 启动暂停切换//BCD倒计时计算,到0时亮灯beginif(bcd1==9) //个位/*******/beginif(bcd2==5) lamp<=1;elsebeginbcd1<=0;bcd2<=bcd2+1;endend/******/elsebeginbcd1<=bcd1+1;lamp<=0;endendend//数码管对应位置扫描输出always @(posedge clk_g or negedge rst)beginif(!rst)beginstate1<=LED1;led_g_bcd<= 0;endelsecase(state1)LED1:beginled_g_bcd<=bcd1;state1<=LED2;endLED2:beginled_g_bcd<=bcd2;state1<=LED1;endendcaseendassign de=state1; //位置//数码管段码表译码assign led_g=(led_g_bcd==0)? 8'h3F:(led_g_bcd==1)? 8'h06:(led_g_bcd==2)? 8'h5b:(led_g_bcd==3)? 8'h4f:(led_g_bcd==4)? 8'h66:(led_g_bcd==5)? 8'h6d:(led_g_bcd==6)? 8'h7d:(led_g_bcd==7)? 8'h07:(led_g_bcd==8)? 8'h7f:(led_g_bcd==9)? 8'h6f:8'h00; endmodule。

verilog全加器实验报告Verilog-全加器上机实验报告西安邮电學院基于Verilog的HDL设计基础实验报告学院名称 :学生姓名 : 专业名称 :班级 : 学时通信与信息工程学院通信工程号 : 间 :2010年11月24日实验题目全加器一、实验内容对一位二进制全加器的设计与验证;再对其进行综合生成网表文件;然后进行后仿真。

二、技术规范1、输入引脚: a,b,c_in;输出引脚:sum,c_out。

2、功能:这是一位二进制全加器。

a,b为输入的两个二进制加数,c_in为低位向本位的借位,sum为全加和,c_out为本位向高位的进位。

三、实验步骤1、在modulesim软件中进行两个一位二进制数的全加器的设计与验证,直到运行结果全部正确;2、在Quartus软件中对刚刚完成的计数器进行综合,生成网表文件;3、在modulesim软件中对计数器进行进行后仿真。

四、源代码1. 设计模块:module Count4(sum,c_out,a,b,c_in);output [3:0] sum;output c_out;input [3:0] a,b;input c_in;wire c1,c2,c3;Count Ca0(sum[0],c1,a[0],b[0],c_in);Count Ca1(sum[1],c2,a[1],b[1],c1);Count Ca2(sum[2],c3,a[2],b[2],c2);Count Ca3(sum[3],c_out, a[3],b[3],c3); Endmodulemodule Count(sum, c_out,a,b,c_in);output sum,c_out;input a,b,c_in;wire s1,c1,c2;xor(s1,a,b);and(c1,a,b);xor(sum,s1,c_in);and(c2,s1,c_in);xor(c_out,c2,c1);endmodule2.激励模块:module jili;reg [3:0] A, B;reg C_IN;wire [3:0] SUM ;wire C_OUT;Count4 CT_4(SUM,C_OUT,A,B,C_IN);initialbegin$monitor($time,A=%b,B=%b,C_IN=%b,---C_OUT=%b,SUM=%b\n,A,B ,C_IN,C_OUT,SUM);endinitialbeginA=4'd0;B=4'd0;C_IN=1'b0;#5 A=4'd3;B=4'd4;#5 A=4'd2;B=4'd5;#5 A=4'd9;B=4'd9;#5 A=4'd10;B=4'd15;#5 A=4'd10;B=4'd5;C_IN=1'b1;endendmodule五、仿真结果及分析五、调试情况,设计技巧及体会1、程序调试:开始时程序一直都编译不出来,总是出现错误,认真修改后,总算是编译成功了,但在SIMULATE时又出现错误,~在同学的帮助下,经过认真的改正,最终修改正确运行成功。

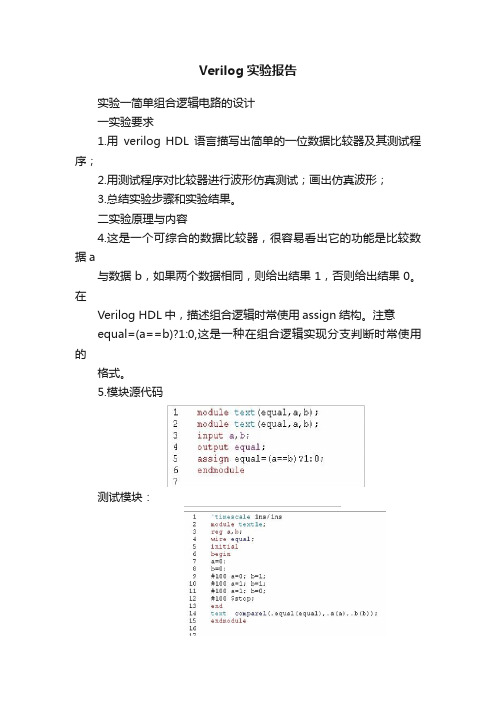

Verilog实验报告实验一简单组合逻辑电路的设计一实验要求1.用verilog HDL语言描写出简单的一位数据比较器及其测试程序;2.用测试程序对比较器进行波形仿真测试;画出仿真波形;3.总结实验步骤和实验结果。

二实验原理与内容4.这是一个可综合的数据比较器,很容易看出它的功能是比较数据a与数据b,如果两个数据相同,则给出结果1,否则给出结果0。

在Verilog HDL中,描述组合逻辑时常使用assign结构。

注意equal=(a==b)?1:0,这是一种在组合逻辑实现分支判断时常使用的格式。

5.模块源代码测试模块:6.波形图:四结实验步骤和实验结果由图可看出,每当输入的电位值不同时输出为0,这与实验要求一致,相同时输出为1,故此程序是可行的。

实验三在verilog HDL中使用函数一实验要求1.掌握函数在模块中的使用2.用测试程序进行波形仿真测试;画出仿真波形3.总结实验步骤和实验结果二实验原理与内容与一般的程序设计语言一样;verilog HDL也可以使用函数已是应对不同变量采取同一运算的操作。

verilog HDL函数在综合时被理解成具有独立运算功能的电路,每调用一次函数相当于改变这部分电路的输入以得到相应的计算结果。

模块源代码:module ex3(clk,n,result,reset);output[31:0] result;input[3:0] n;input reset,clk;reg[31:0] result;always @(posedge clk)beginif(!reset)result <= 0;elsebeginresult <= n*factorial(n)/((n*2)+1);endendfunction[31:0] factorial;input[3:0] operand;reg[3:0] index;beginfactorial = operand ? 1:0;for(index = 2;index <= operand;index = index+1) factorial = index*factorial;endendfunctionendmodule`timescale 1ns/100ps`define clk_cycle 50module ex3_t();reg[3:0] n,i;reg reset,clk;wire[31:0] result;initialbeginn=0;reset=1;clk=0;#100 reset=0;#100 reset = 1;for(i=0;i <= 15;i=i+1)begin#200 n=i;end#100 $stop;endalways #`clk_cycle clk =~ clk;ex3 ex30(.clk(clk),.n(n),.result(result),.reset(reset)); always @(negedge clk)$display("at n=%d,result=%d",n,result);endmodule波形图:实验四在verilog HDL中使用任务一实验要求1.掌握任务在结构化verilog HDL设计中的应用2.用测试程序进行波形仿真测试;画出仿真波形3.总结实验步骤和实验结果二实验原理与内容仅有函数并不能满足verilog HDL中的运算需求。

流水灯实验目的:在basys2开发板上实现LED灯的花样流水的显示,如隔位显示,依次向左移位显示,依次向右移位显示,两边同时靠中间显示。

实验仪器:FPGA开发板一块,计算机一台。

实验原理:当一个正向的电流通过LED时,LED就会发光。

当阳极的电压高于阴极的电压时,LED就会有电流通过。

当在LED上增添一个典型值为1.5V—2.0V之间的电压时,LED就会有电流通过并发光。

实验内容:顶层模块:输入信号:clk_50MHz(主时钟信号),rst(重置信号),输出信号:[7:0] led(LED灯控制信号)。

module led_top(clkin,rst,led_out);input clkin, rst;output [7:0] led_out;wire clk_1hz;divider_1hz d0(clkin, rst, clk_1hz);led l0(clk_1hz, rst, led_out);endmodule分频模块:module divider_1hz(clkin,rst,clkout);input clkin,rst;output reg clkout;reg [24:0] cnt;always@(posedge clkin, posedge rst)beginif(rst) begincnt<=0;clkout<=0; endelse if(cnt==24999999) begincnt<=0;clkout=!clkout; endelse cnt<=cnt+1;endendmodule亮灯信号模块:module led(clkin,rst,led_out);input clkin,rst;output [7:0] led_out;reg [2:0] state;always@(posedge clkin, posedge rst)if(rst) state<=0;else state<=state+1;always@(state)case(state)3'b000:ledout<=8'b0000_0001;3'b001:ledout<=8'b0000_0010;3'b010:ledout<=8'b0000_0100;3'b011:ledout<=8'b0000_1000;3'b100:ledout<=8'b0001_0000;3'b101:ledout<=8'b0010_0000;3'b110:ledout<=8'b0100_0000;3'b111:ledout<=8'b1000_0000;endcaseendmodule实验中存在的问题:1 芯片选择问题automotive spartan3EXA3S100E XA3S250E CPG132spartan3EXC3S100E XC3S250E CP1322 时序逻辑部分,阻塞赋值和非阻塞赋值混用always@(posedge clk)begina=b+c;d<=e+f;end3 UCF文件格式错误NET “CLK” LOC = “B8”;NET “a” LOC = “N11”;NET “b” LOC = “G13”;NET “c[0]”LOC =“K11;数码管实验目的:设计一个数码管动态扫描程序,实现在四位数码管上动态循环显示“1”、“2”“3”“4”;实验仪器:FPGA开发板一块,计算机一台。

Verilog实验报告---第四次交通灯班级:集电0802班姓名:张鹏学号: 04086057序号: 16一、规范(1)具有开关功能:当reset=0时红绿灯关闭,使主支干道六个灯全灭;(2)具有四个功能:当reset=1且func=2’b00时,主干道和支路正常计数;且func=2’b01时,支干道一直绿灯,主干道一直红灯;且func=2’b10时,主干道一直绿灯,支干道一直红灯;且func=2’b11时,主干道和支干道一直黄灯闪;(3)计数器频率:运行频率2Hz计数器;(4)信号灯种类:红、黄、绿;(5)信号灯计执行时间关系:主干道:绿灯常亮+绿灯闪+黄灯=支干道:红灯常亮;此设计中:主干道:绿灯常亮=57s,T绿灯闪=3s,T黄灯亮=3s支干道:绿灯常亮=15s,T绿灯闪=3s,T黄灯亮=3s(6)信号灯到计时功能:信号灯预置后,开始执行2Hz计数器;(7)信号灯跳转功能:当各信号灯计时至T时在下一个时钟信号上升沿到来时自动转为下一状态;(8)信号灯各状态跳转关系:绿-黄-红-绿;二、输入输出定义状态转移图:四、测试代码module frequency_divider_small(reset,clk,out); //重写一个小分频模块测试交通灯主模块功能input reset,clk;output out;reg [1:0] temp;reg out;always @ (posedge clk or negedge reset)if (!reset)temp<=2'b00;elsetemp<=(temp==2'b11)?2'b00:temp+2'b01;always @ (temp)out=(temp==2'b11);endmodulemodule test_traffic_light;reg reset,clk;reg [1:0] func;wire [1:0] green;wire [1:0] red;wire [1:0] yellow;traffic_lightsimulation(.reset(reset),.clk(clk),.func(func),.green(green),.red(red),.yellow( yellow));always #10 clk=~clk;initialbeginreset=0;clk=1;func=2'b00;#20 reset=1;#21000 func=2'b01;#10000 func=2'b10;#10000 func=2'b11;endendmodule波形:五、源代码module frequency_divider(reset,clk,out);//分频模块,把50MHz时钟分成半秒计时器 input reset,clk;output out;reg [5:0] mol1,mol2;reg [6:0] mol3,mol4;reg out1,out2,out3,out;always @ (posedge clk or negedge reset)//把25000000分成40*40*125*125if(!reset)mol1<=6'd0;elsemol1<=(mol1==6'd39)?6'd0:mol1+6'd1;always @ (posedge clk or negedge reset)if(!reset)mol2<=6'd0;else if(out1)mol2<=(mol2==6'd39)?6'd0:mol2+6'd1;always @ (posedge clk or negedge reset)if(!reset)mol3<=7'd0;else if(out2)mol3<=(mol3==7'd124)?7'd0:mol3+7'd1;always @ (posedge clk or negedge reset)if(!reset)mol4<=7'd0;else if(out3)mol4<=(mol4==7'd124)?7'd0:mol4+7'd1;always @ (mol1 or mol2 or mol3 or mol4)beginout1=(mol1==6'd39);out2=((mol2==6'd39)&&out1);out3=((mol3==7'd124)&&out2);out=((mol4==7'd124)&&out3);endendmodulemodule traffic_light(reset,clk,func,green,red,yellow);//交通灯主模块input reset,clk;input [1:0] func;output [1:0] green,red,yellow;reg [1:0] green,red,yellow;reg [2:0] state;reg [6:0] cnt;wire in;parameter greentime1=6'd57;//主干道绿灯时间parameter greentime0=6'd27;//支干道绿灯时间parameter yellowtime=3'd3;//黄灯时间,绿灯闪时间frequency_divider fenpin(.reset(reset),.clk(clk),.out(in));//调用分频模块 always @ (posedge clk or negedge reset)if(!reset)begincnt<=7'd0;state<=3'd1;green<=2'b00;red<=2'b00;yellow<=2'b00;endelseif(in)//分频器结果当主模块始能if(func==2'b00)//选择不同功能控制开关 if(cnt==7'd0)case(state)//选择不同状态3'd1:begincnt<=greentime1<<1; state<=3'd2;green<=2'b10;red<=2'b01;yellow<=2'b00;end3'd2:begincnt<=yellowtime<<1; state<=3'd3;end3'd3:begincnt<=yellowtime<<1; state<=3'd4;green<=2'b00;red<=2'b01;yellow<=2'b10;end3'd4:begincnt<=greentime1<<1; state<=3'd5;green<=2'b01;red<=2'b10;yellow<=2'b00;end3'd5:begincnt<=yellowtime<<1; state<=3'd6;end3'd6:begincnt<=yellowtime<<1; state<=3'd1;green<=2'b00;red<=2'b10;yellow<=2'b01;endendcaseelsebegincnt<=cnt-7'd1;//倒计数,计数结束进入下一状态 case(state)3'd3:green[1]<=cnt[0];//主干道绿灯闪3'd6:green[0]<=cnt[0];//支干道绿灯闪endcaseendelse if(func==2'b10)//主干道常绿,支干道常红begincnt<=0;state<=3'd1;green<=2'b10;red<=2'b01;yellow<=2'b00;endelse if(func==2'b01)//主干道常红,支干道常绿begincnt<=0;state<=3'd1;green<=2'b01;red<=2'b10;yellow<=2'b00;endelse if(func==2'b11)//主干道,支干道黄灯一直闪begincnt<=0;state<=3'd1;green<=2'b00;red<=2'b00;yellow[1]<=~yellow[1];yellow[0]<=~yellow[1];endendmodule。

verilog课程设计实验报告一、教学目标本课程旨在通过Verilog硬件描述语言的学习,让学生掌握数字电路设计的自动化工具,理解并实践硬件描述语言在数字系统设计中的应用。

通过本课程的学习,学生应达到以下目标:1.知识目标:–理解Verilog的基本语法和结构。

–掌握Verilog中的模块化设计方法。

–学习常用的Verilog描述技巧,包括逻辑门级建模、行为级建模和结构级建模。

2.技能目标:–能够运用Verilog语言进行简单的数字电路设计。

–学会使用至少一种Verilog仿真工具进行电路功能验证。

–能够阅读和理解Verilog代码,进行简单的代码优化。

3.情感态度价值观目标:–培养学生的团队合作意识,在实验报告中能够体现分工合作的精神。

–培养学生的问题解决能力,鼓励学生在遇到问题时积极寻找解决方案。

–培养学生对新技术的好奇心和学习兴趣,激发他们对电子工程领域的热爱。

二、教学内容依据教学目标,本课程的教学内容将围绕Verilog语言的基础知识、实践应用和项目设计展开。

教学大纲安排如下:1.第一部分:Verilog基础知识(2周)–介绍Verilog的背景和基本概念。

–详细讲解Verilog的数据类型、运算符和语句。

2.第二部分:模块化设计(2周)–讲解模块的定义和封装。

–实践模块的端口声明和模块实例化。

3.第三部分:数字电路的Verilog描述(2周)–通过实例教学,掌握逻辑门、触发器等基本组件的Verilog建模。

–学习组合逻辑和时序逻辑的设计方法。

4.第四部分:仿真与测试(1周)–学习使用仿真工具进行电路功能验证。

–理解并实践测试台(testbench)的编写。

5.第五部分:项目设计(3周)–小组合作完成一个较为复杂的数字系统设计项目。

–包括系统模块的划分、编码、仿真和测试。

三、教学方法为了提高学生的学习效果,将采用多种教学方法相结合的方式进行授课:1.讲授法:用于讲解Verilog的基本概念和语法。

一、实验目的使用Verilog 软件编写四种波形任意发生器的源代码,用modelsim 软件进行仿真测试,进一步强化Verilog ,modelsim 软件的编程能力为进一步的编程学习打下良好的基础。

二、实验原理该任意波形发生器要实现三个功能:(1)通过计数器并结合拼接操作产生四种波形正弦波,方波,三角波1,三角波形的5位数据地址。

(2).设定ROM 中对应波形地址地址的8位数值,将所有波形数值存储到ROM 中。

(3).设定2位的波形选择开关端口。

2bit 00000~00111 01000~01111 3bit data[7:0] 10000~1011111000~11111图 1整体设计方案四种波形要在一个周期内等间隔取8个点,定义对应的数据,下图为示意图,由于编程序需要,数据会进行相应的修改。

图2 四种波形一个周期内的取样示意图地址发生器(0-7)正弦波方波三角波1三角波2cl re 波形选择 1-11正弦方波三角波1三角波2y xx88yyx1四种波形数据地址对应的数据的存储器ROM根据示意图,由于实际情况需要,将正弦波平移至x轴以上,并将所有波形的峰峰值取大100倍。

下表1是ROM存储器三、实验内容任意波形发生器verilog程序代码:module wave(data,clk,add1,reset);//顶层模块端口定义output[7:0]data;input clk,reset;input[1:0] addr1;Wire[1:0] addr1;wire clk,reset;//输入输出变量定义ADDR 4(addr,clk,addr1,reset);//地址发生器模块调用rom 1(addr,data);//ROM存储器模块调用endmodulemodule ADDR(addr,clk,addr1,reset);output[4:0] addr;input clk,reset;wire clk,reset;reg[2:0] addr2;wire[1:0] addr1;reg[4:0] addr;initial addr2=3'b000; //定义计数初值always @(posedge clk or posedge reset)//每当有clk,或reset信号开启程序beginif(reset)beginaddr2<=0;//同步复位addr<=0;endelse if(addr2>=7)//addr2计数至7时,addr2复位beginaddr2<=0;endelsebeginaddr2<=addr2+1;//addr2由0至7计数addr<={addr1,addr2};//addr1与addr2地址拼接为addr的最终地址endendendmodulemodule rom(addr,data);//数据存储器模块input[4:0] addr;output[7:0] data;function[6:0] romout;//定义函数,存储32个波形取样点地址的数据input[4:0] addr;reg[4:0] addr;wire[7:0] data;case(addr)//根据不同地址,得到不同数据。

· Word资料 2014-2015-2-G02A3050-1 电子电路设计训练(数字EDA部分)

实验报告 ( 2015 年5 月 20 日)

教学班 学号 组长 签名 成绩

自动化科学与电气工程学院 ·

Word资料 目 录 目 录 ............................................................................................................................. 1 实验一、简单组合逻辑和简单时序逻辑 ............................................................................ 1 1.1 实验任务1——简单组合逻辑 ........................................................................ 1 1.1.1 实验要求 ............................................................................................. 1 1.1.2 模块的核心逻辑设计 .......................................................................... 1 1.1.3 测试程序的核心逻辑设计 ................................................................... 1 1.1.4 仿真实验关键结果及其解释 ................................................................ 2 1.2 实验任务2——简单时序逻辑 ...................................................................... 3 1.2.1 实验要求 ............................................................................................ 3 1.2.2 模块的核心逻辑设计 .......................................................................... 3 1.2.3 测试程序的核心逻辑设计 ................................................................... 4 1.2.4 仿真实验关键结果及其解释 ............................................................... 4 1.3 实验小结 ..................................................................................................... 5 实验二、条件语句和always过程块 ................................................................................. 5 2.1 实验任务1——利用条件语句实现计数分频时序电路 .................................... 5 2.1.1 实验要求 ............................................................................................ 5 2.1.2 模块的核心逻辑设计 .......................................................................... 5 2.1.3 测试程序的核心逻辑设计 ................................................................... 7 2.1.4 仿真实验关键结果及其解释 ............................................................... 8 2.2 实验任务2——用always块实现较复杂的组合逻辑电路 .............................. 9 2.2.1 实验要求 ........................................................................................... 9 2.2.2 模块的核心逻辑设计 ......................................................................... 9 2.2.3 测试程序的核心逻辑设计 ................................................................. 11 2.2.4 仿真实验关键结果及其解释 ............................................................. 13 2.3 实验小结 ................................................................................................... 14 实验三、赋值、函数和任务 ........................................................................................... 14 3.1 实验任务1——阻塞赋值与非阻塞赋值的区别 ............................................. 14 3.1.1 实验要求 .......................................................................................... 14 3.1.2 模块的核心逻辑设计 ........................................................................ 14 3.1.3 测试程序的核心逻辑设计 ................................................................. 16 3.1.4 仿真实验关键结果及其解释 ............................................................. 17 3.2 实验任务2——在Verilog HDL中使用函数 ............................................... 19 3.2.1 实验要求 ......................................................................................... 19 3.2.2 模块的核心逻辑设计 ....................................................................... 20 3.2.3 测试程序的核心逻辑设计 ................................................................ 22 3.2.4 仿真实验关键结果及其解释 ............................................................. 23 3.3 实验任务3——在Verilog HDL中使用任务 ............................................... 24 3.3.1 实验要求 ......................................................................................... 24 3.3.2 模块的核心逻辑设计 ....................................................................... 24 3.2.3 测试程序的核心逻辑设计 ................................................................ 25 · Word资料 3.2.4 仿真实验关键结果及其解释 ............................................................. 26 3.3 实验小结 ................................................................................................... 26 实验四、有限状态机 ...................................................................................................... 27 4.1 实验任务1——基于状态机的串行数据检测器 ............................................. 27 4.1.1 实验要求 .......................................................................................... 27 4.1.2 模块的核心逻辑设计 ........................................................................ 27 4.1.3 测试程序的核心逻辑设计 ................................................................. 29 4.1.4 仿真实验关键结果及其解释 ............................................................. 30 4.2 实验任务2——楼梯灯 .............................................................................. 31 4.2.1 实验要求 ......................................................................................... 31 4.2.2 模块的核心逻辑设计 ....................................................................... 32 4.2.3 测试程序的核心逻辑设计 ................................................................ 37 4.2.4 仿真实验关键结果及其解释 ............................................................. 39 4.3 实验小结 ................................................................................................... 41