Project4 VerilogHDL完成单周期处理器开发(2013.12.2)

- 格式:pdf

- 大小:754.54 KB

- 文档页数:9

MIPS-CPU设计实验报告实验名称:32位单周期MIPS-CPU设计姓名学号:刘高斯11072205实验日期:2014年12月19日目录前言MIPS简介------------------------------------------------------------- 3 实验目的------------------------------------------------------------- 3第一部分VERILOG HDL 语言实现部分实验内容------------------------------------------------------------- 4 试验环境------------------------------------------------------------- 4 模块简介------------------------------------------------------------- 4 实验截图------------------------------------------------------------- 5 实验感想------------------------------------------------------------- 5 实验代码------------------------------------------------------------- 6第二部分LOGISIM 语言实现部分实验内容------------------------------------------------------------- 16 实验环境------------------------------------------------------------- 16模块设计------------------------------------------------------------- 16 试验感想------------------------------------------------------------- 23前言一、MIPS简介MIPS是世界上很流行的一种RISC处理器。

MIPS-CPU设计实验报告实验名称:32位单周期MIPS-CPU设计姓名学号:刘高斯11072205实验日期:2014年12月19日目录前言MIPS简介------------------------------------------------------------- 3 实验目的------------------------------------------------------------- 3第一部分VERILOG HDL 语言实现部分实验内容------------------------------------------------------------- 4 试验环境------------------------------------------------------------- 4 模块简介------------------------------------------------------------- 4 实验截图------------------------------------------------------------- 5 实验感想------------------------------------------------------------- 5 实验代码------------------------------------------------------------- 6第二部分LOGISIM 语言实现部分实验内容------------------------------------------------------------- 16 实验环境------------------------------------------------------------- 16模块设计------------------------------------------------------------- 16 试验感想------------------------------------------------------------- 23前言一、MIPS简介MIPS是世界上很流行的一种RISC处理器。

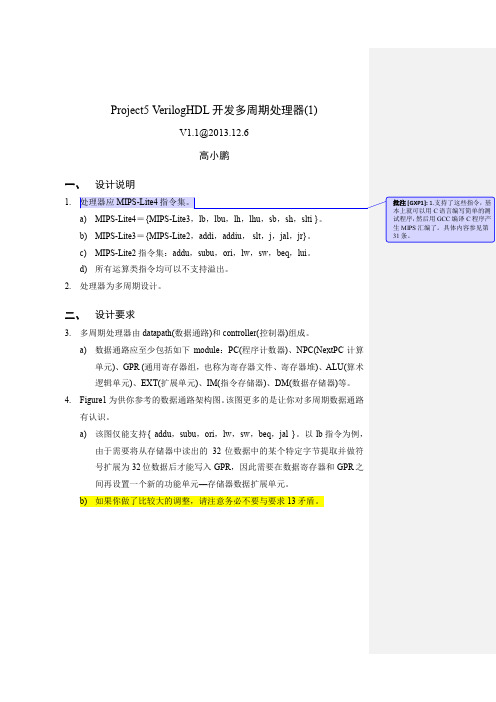

2. 3.4.Figure1 多周期数据通路(供参考)5.多周期数据通路应必须包括PC、NPC、IM、DM这4个独立模块。

其中:a)IM:容量为4KB(32bit×1024字)。

b)DM:容量为4KB(32bit×1024字)。

6.层次及模块实例化命名必须满足下列要求:a)本project的顶层设计文件命名:mips.v。

b)PC必须被实例化命名:U_PC。

下面代码为示例。

pc U_PC(…) ; // 实例化PC(程序计数器)c)指令存储器必须被实例化命名:U_IM。

d)数据存储器必须被实例化命名:U_DM。

e)寄存器文件必须被实例化命名:U_RF。

7.建议datapath中的每个module都由一个独立的V erilogHDL文件组成。

a)建议所有mux(包括不同位数、不同端口数等)都建模在一个mux.v中。

可以有多个module。

8.为使得代码更加清晰可读,建议多使用宏定义,并将宏定义组织在1个或多个头文件中。

9.PC复位后初值为0x0000_3000,目的是与MARS的Memory Configuration相配合。

a)现场测试用的测试程序将通过MARS产生,其配置模式如Figure2所示。

Figure2 MIPS存储配置模式(MARS memory configuration)10.建议你用工程化方法来构造数据通路和状态机。

具体内容请参见随project提供的PPT。

a)你初次接触工程化方法时可能不是非常理解其价值。

但一旦当你运用这个方法后(特别是在后续project中),你会发现设计将被分为2个环节:真正意义上的设计和实现。

b)设计:仅仅在表格中就可以完成,而无需在HDL这个层次进行。

这一方面避免了HDL的大量细节对设计的干扰,另一方面使得你的设计可以被追朔,从而更高效的开发和准确的发现错误。

c)实现:当设计都完成后,可以一次性的完成HDL编码。

这个编码仅仅是对表格的翻译,对你的要求仅仅是掌握基本的HDL和认真细心。

电子科技大学计算机科学与工程学院单周期CPU的设计与实现实验指导书[计算机组成原理实验]张建2013-12-13目录前言 (1)1.1 实验内容 (2)1.2实验要求 (2)2. 实验环境 (3)2.1 硬件平台 (3)2.2 软件平台 (3)2.3 实验主要仪器设备连接框图 (4)3. 实验原理 (5)3.1 概述 (5)3.2 单周期CPU的总体电路 (5)3.3 MIPS指令格式 (6)3.4 数据路径设计 (7)3.4.1 下一条指令地址的选择 (7)3.4.2 ALU的输入端 (8)3.4.3寄存器堆的输入端 (8)4. 基本功能部件的设计与实现 (10)4.1 32位2选1选择器的设计与实现 (10)4.2 32位4选1选择器的设计与实现 (18)4.3 5位2选1选择器的设计与实现 (19)4.4 带有异步清零的32位D触发器的设计与实现 (19)4.5 移位器的设计 (20)4.6 32位加/减法器的设计与实现 (20)5.运算器(ALU)的设计与实现 (21)6.寄存器堆(Register File)的设计与实现 (24)7.控制器(Control Unit)的设计与实现 (27)8. CPU的封装 (30)9. 测试 (32)9.1 指令存储器及测试程序 (32)9.2 数据存储器及测试数据 (33)9.3 仿真测试 (33)9.4 下载到开发板验证 (35)附件: (39)BTN_Anti_Jitter模块 (39)Hex7seg_decode模块 (39)前言《计算机组成原理》是计算机科学专业的一门重要专业基础课。

在该课程中的理论学习中系统地阐述了计算机各组成部件的工作原理、逻辑实现和设计方法及将各部件连接成整机的方法,计算机硬件与底层软件的接口,培养了学生对计算机硬件系统的分析、开发与设计的基本技能能力。

本实验开设的目的是让学生通过设计一个单周期的CPU,加深对计算机各组成部件功能的理解和掌握,更好地理解计算机的基本工作原理,培养和锻炼学生掌握计算机硬件设计的基本方法和技能。

FPGA期末结业论文基于FPGA&VerilogHDL的四路抢答器院系:物理与电子学院专业:电子信息科学与技术任课教师:学号:姓名:2013年12月目录(0)摘要 (2)(1)引言 (3)1.1关于课程设计 (3)1.1.1课程设计目的 (3)1.1.2课程设计内容 (3)1.2开发工具简介 (4)1.2.1 EDA技术 (4)1.2.2 硬件描述语言-Verilog HDL (4)1.2.3 Verilog HDL设计流程 (5)1.2.4 FPGA基本特点 (5)1.2.5 FPGA工作原理 (5)(2)概述 (5)2.1 设计过程 (5)2.1.1系统设计要求 (5)2.1.2系统设计方案 (6)(3)系统设计 (6)3.1系统组图 (6)3.2系统主源程序 (8)(4)仿真综合 (10)(5)结论 (13)(6)参考文献 (13)(7)附录 (13)0摘要抢答器是在竞赛、文体娱乐活动(抢答活动)中,能准确、公正、直观地判断出抢答者的机器。

电子抢答器的中心构造一般都是由抢答器由单片机以及外围电路组成。

本设计是以四路抢答为基本概念。

从实际应用出发,利用电子设计自动化( EDA)技术,用可编程逻辑器件设计具有扩充功能的抢答器。

它以Verilog HDL硬件描述语言作为平台,结合动手实验而完成的。

它的特点是电路简单、制作方便、操作简单、方便、性能可靠,实用于多种智力竞赛活动。

本抢答器的电路主要有四部分组成:鉴别锁存电路、FPGA主芯片EP1C3T144C8电路、计分电路以及扫描显示模块的电路,并利用Quartus II工具软件完成了Verilog HDL源程序编写和硬件下载。

这个抢答器设计基本上满足了实际比赛应用中的各种需要。

在实际中有很大的用途。

关键词:抢答器 Quartus II Verilog HDL EP1C3T144C81引言硬件描述语言 Hardware Description Language 是硬件设计人员和电子设计自动化 EDA 工具之间的界面。

单周期CPU及其Verilog HDL设计一、指令的设计MIPS32的指令的三种格式的参考:R类型:I类型:J类型:R类型指令的op为0,具体操作由func指定。

rs和rt是源寄存器号,rd是目的寄存器号。

只有移位指令使用sa来指定移位位数。

I类型指令的低16位是立即数,计算时要把它扩展到32位。

依指令的不同,有零扩展和符号扩展两种。

J类型指令右边26位是字地址,用于产生跳转的目标地址。

具体的指令格式和内容请参考MIPS32。

设计报告中需自行设计所有指令的二进制格式和对应的汇编指令格式。

二、单周期CPU的设计我们把时钟的电平从低到高变化的瞬间称为时钟上升沿,两个相邻时钟上升沿之间的时间间隔称为一个时钟周期。

单周期CPU指的是一条指令的执行在一个这样的时钟周期内完成,然后开始下一条指令的执行,即一条指令用一个周期。

2.1执行一条指令所需的硬件电路我们的目的地是要设计CPU的硬件电路,使其能够从存储器中读出一条条指令并执行指令所描述的操作。

从存储器中读取指令的动作一般与指令本身的意义无关,可以以同样的方法把指令从存储器中取出。

而执行指令则与指令本身的意义密切相关,因此最重要是首先搞清楚CPU要执行的每条指令的意义。

下面以两种类型的电路来举例。

2.1.1与取指令有关的电路指令存储在存储器中。

CPU取指令时把程序计数器(PC)中的内容作为存储器的地址,根据它来访问存储器,从PC值指定的存储单元中取来一条32位指令。

如果取来的指令执行时没有引起转移,PC的值要加4;如果转移,要把转移的目标地址写入PC,以便在下一个时钟周期取出下一条指令。

图2.1 取指令时用到的硬件电路和指令寄存器如图2.1所示,PC是一个简单的32位寄存器,由32个D触发器构成。

指令存储器(Inst Mem)的输入端a是地址、输出端do是数据输出,即指令。

图中的加法器专供PC+4使用,它的输出接到多路器的一个输入端。

如果取来的指令没有引起转移或跳转,则选择PC+4,在时钟上升沿处将其打入PC;若引起转移或跳转,则用多路器选择下一条指令该打入的PC值。

Verilog HDL程序设计教程红色:做后有错。

粉红色:有疑问。

紫色:第二次仍有错。

绿色:文字错误第1章EDA技术综述 1.1引言1.摩尔定律1.2EDA的发展阶段1.阶段1.3设计方法与设计技术1.两种设计思路2.IP的含义3. IP核的分类。

4. SOC的含义1.4EDA的实现1.实现方法第2章EDA设计软件与设计流程 2.2EDA的设计流程1(FPGA的设计流程 2(综合的定义与类型。

3(仿真的类型第3章Verilog HDL设计初步(P18) 3.2完整的Verilog HDL设计1. 4位全加器的和4位计数器的程序。

2. 4位全加器的仿真程序(1.时间头文件 2.模块名(没有参数)3.参数规定(端口、延时、时钟)4.调用测试对象 5.设置参数(所有的输入端口都应初始化赋值)6.显示设置)。

3.3Verilog模块基本结构剖析 1.端口定义注意事项。

2.逻辑功能定义的几种方式第4章Verilog HDL语言要素(P32)4.1词法1.verilog中的四种基本逻辑状态4.2数据类型1.连线型(Net Type)的特点2.寄存器型(Register Type):定义、与连线型区别(赋值、保值)3.Parameter的使用格式4.3寄存器和存储器1.寄存器定义格式和标矢性2.存储器:定义、格式、位区选择方法4.3运算符1.等式与全等式的区别2.位拼接运算符第5章Verilog HDL行为语句(P45)5.2 Verilog HDL中的过程语句1.always过程语句格式。

2.initial过程语句格式。

5.3 块语句1.块语句。

2.用begin—end产生周期为10的个单位时间的方波.3.用fork—join产生周期为10的个单位时间的方波5.4赋值语句1.分类。

2.阻塞赋值和非阻塞赋值的区别5.5条件语句1.例5.11(模为60的BCD码加法计数器)2.case语句的三种表达形式5.6循环语句1.Verilog HDL中4种类型循环语句。