fpga毕业设计任务书

- 格式:doc

- 大小:26.00 KB

- 文档页数:3

基于FPGA的GPS数据采集存储电路设计毕业设计(10到19)本课题采用AMD公司成产的AM29LV160B FLASH芯片,该芯片是一个16Mbit,3.0V供电,48个管脚,采用TSOP封装的存储芯片,该芯片可以设定为2×8Mbit,也可设定为1×16Mbit,适用于8位、16位的系统存储,具有存储速度快,使用寿命长等优点。

3 系统硬件设计3.1 Altium DesignerAltium Designer 是原Protel软件开发商Altium公司推出的一体化的电子产品开发系统,主要运行在Windows XP操作系统。

这套软件通过把原理图设计、电路仿真、PCB绘制编辑、拓扑逻辑自动布线、信号完整性分析和设计输出等技术的完美融合,为设计者提供了全新的设计解决方案,使设计者可以轻松进行设计,熟练使用这一软件必将使电路设计的质量和效率大大提高。

Altium Designer 除了全面继承包括Protel 99SE、Protel DXP在内的先前一系列版本的功能和优点外,还增加了许多改进和很多高端功能。

该平台拓宽了板级设计的传统界面,全面集成了FPGA设计功能和SOPC设计实现功能,从而允许工程设计人员能将系统设计中的FPGA与PCB设计及嵌入式设计集成在一起。

由于Altium Designer 在继承先前Protel软件功能的基础上,综合了FPGA设计和嵌入式系统软件设计功能,Altium Designer 对计算机的系统需求比先前的版本要高一些。

2005年年底,Protel软件的原厂商 Altium公司推出了Protel系列的最新高端版本Altium Designer 6.0。

Altium Designer 6.0,它是完全一体化电子产品开发系统的一个新版本,也是业界第一款也是唯一一种完整的板级设计解决方案。

Altium Designer 是业界首例将设计流程、集成化PCB 设计、可编程器件(如FPGA)设计和基于处理器设计的嵌入式软件开发功能整合在一起的产品,一种同时进行PCB和FPGA设计以及嵌入式设计的解决方案,具有将设计方案从概念转变为最终成品所需的全部功能。

天津工业大学毕业设计(论文)基于FPGA的LCD显示控制系统的设计姓名:马震院(系)别: 信息与通信工程学院专业: 电子信息工程班级:电子061指导教师:周勇职称:讲师2010年 6 月13 日天津工业大学毕业设计(论文)任务书院长教研室主任指导教师毕业设计(论文)开题报告表天津工业大学毕业设计(论文)进度检查记录天津工业大学本科毕业设计(论文)评阅表摘要本课题主要任务是设计基于FPGA的LCD控制器,兼顾好程序的易用性,以方便之后模块的移植和应用。

本课题的设计采用了带ST7920驱动的12864-12的液晶模块,并使用Xilinx公司的spartanII系列的XC2STQ144来作为核心的控制器。

控制器部分采用VHDL语言编写,主体程序采用了状态机作为主要控制方式。

ST7920是一种内置128x64-12汉字图形点阵地液晶显示控制模块,用于显示汉字和模型。

最后实现使用FPGA在LCD上的任意位置显示任意的16*16像素的中文字符以及16*8的英文字符,另外要能根据输入数据的变化同步变化LCD上显示的内容.同时要能将储存模块中的图片数据正常地显示在LCD上。

该课题的研究将有助于采用FPGA的系列产品的开发,特别是需要用到LCD 的产品的开发。

同时可以大大缩短FPGA的开发时间。

另外,由于模块的易用性,也将使得更多的采用FPGA的产品之上出现LCD,增加人机之间的交互性,为行业和我们的生活带来新的变化。

关键词:ST7920;12864—12 ;VHDL;FPGA ;LCDABSTRACTIn this project, the main object is to design a LCD controller based on FPGA,and at the same time emphasize on the convenience for the later application and migration. In this project, This topic is designed with a belt—driven 12864—12 ST7920 LCD module, and use the Xilinx's spartanII series XC2STQ144 as the core of the controller。

xxxx学院毕业设计论文题目:基于单片机和FPGA的位同步信号提取专业班级:电子信息工程学生姓名:学号:完成日期:指导教师:评阅教师:2006 年6月湖南工程学院应用技术学院毕业设计(论文)诚信承诺书本人慎重承诺和声明:所撰写的《基于单片机和FPGA的位同步信号提取》是在指导老师的指导下自主完成,文中所有引文或引用数据、图表均已注解说明来源,本人愿意为由此引起的后果承担责任。

设计(论文)的研究成果归属学校所有。

学生(签名)年月日湖南工程学院应用技术学院毕业设计(论文)任务书设计(论文)题目:基于单片机和FPGA的位同步信号提取姓名专业电子信息工程班级 0281 学号 16指导老师刘正青职称实验师教研室主任刘望军一、基本任务及要求:本课题是设计一具有通用性的输入信号的位同步提取系统,系统可以实现10HZ~1MHZ的信号同步。

使用单片机进行实时控制现场可编程逻辑门阵列FPGA完成位同步信号提取,通过理论和实验研究,完成硬件电路和软件设计并试制样机,要求完成:1、单片机实时控制FPGA,完成实时频率跟踪测量和自动锁相;2、在FPGA 内部,设计完成以下部分:A、全数字锁相环DPLL,主要包含:数控振荡器、鉴相器、可控模分频器B、LED动态扫描电路、FPGA和单片机的数字接口,以完成两者之间的数字传递3、设计辅助电路:键盘、LED;二、进度安排及完成时间:(1)第二周至第四周:查阅资料、撰写文献综述和开题报告;(2)第五周至第六周:毕业实习;(3)第六周至第七周:项目设计的总体框架:各个模块以及各个模块之间的关系确定,各个模块的方案选择与各个模块的所用主要器件的确定;(4)第八周至第十三周:各个模块的主要器件熟悉及相关知识的熟悉;各个模块的具体任务实现:硬件电路、软件编程;(5)第十四周至第十五周:系统的总体仿真与调试(6)第十六周至第十七周:撰写设计说明书;(7)第十八周:毕业设计答辩;目录摘要........................................................................................................ 错误!未定义书签。

FPGA课程设计报告学部:信息科学与技术学部专业:通信工程班级:10级1班学号:100103011125姓名:万洁指导老师:祝宏合作伙伴:张紫君2012.12.13 一.《任务书》:实验一 100进制的可逆计数器(11——12周)实验二交通灯控制系统(15周)实验三多功能数字钟系统(14-15周)二.实验书写格式:一:题目要求二:程序代码三:操作步骤及运行结果截图四:心得体会三.实验附录:一:老师提供的资源二:关于实验所用EP4CE115F29板的简介实验一 100进制的可逆计数器一、设计一个可控的100进制可逆计数器,要求用实验箱下载。

(1)计数器的时钟输入信号周期为200ns。

(2)以十进制形式显示。

(3)有一个复位端clr和两个控制端plus和minus,在这些控制信号的作用下,计数器具有复位、增或减计数、暂停功能。

clr plus minus 功能0 ××复位为01 1 0 递增计数1 0 1 递减计数1 1 1 暂停计数二、程序如下:module keni100(CLR,CLK,PLUS,MINUS,OUT); //100进制的可逆计数器input CLR,PLUS,MINUS,CLK;output [7:0]OUT;reg [7:0]OUT;always@(posedge CLK)beginif(!CLR) //如果CLR为零,输出为零;反之,运行else程序OUT[7:0]<=0;elsebeginif(PLUS==0 && MINUS==1) //100进制的递减计数beginif (OUT[3:0]==0)beginOUT[3:0]<=9;if (OUT[7:4]==0) OUT[7:4]<=9;elseOUT[7:4]<=OUT[7:4]-1;endelse OUT[3:0]<=OUT[3:0]-1;endif(PLUS==1 && MINUS==0) //100进制的递增计数beginif (OUT[3:0]==9)beginOUT[3:0]<=0;if (OUT[7:4]==9) OUT[7:4]<=0;elseOUT[7:4]<=OUT[7:4]+1;endelse OUT[3:0]<=OUT[3:0]+1;endif(PLUS==1 && MINUS==1) OUT<=OUT; //若PLUS和MINUS都为1,暂停计数if(PLUS==0 && MINUS==0) OUT<=0; //若都为零,输出为零endendendmodule三、运行程序1、在quarters II9.1输入程序打开quarters II界面,点击file→New,在出现的对话框,如图1.1所示,选择Text File,点击OK.——图1.1 在出现的输入界面内输入程序,点击file→save as,在出现的对话框中点击Yes,然后在出现的new project Wizard对话框中点击next,在Family&Device Settings 对话框中选择如下图1.2所示的选项,在选择第三方软件的对话框中的选项选为none后点击next,在随后出现的对话框中,点击finish。

关于fpga的毕业设计

近年来,随着计算机科学技术的不断发展,各种新颖的硬件设备层出不穷,为计算机领域的研究提供了更多的技术支持。

FPGA(Field Programmable Gate Array)是一种可以实现可编程的数字电路的器件,具有高度的灵活性和可扩展性,被广泛地应用于计算机、通信、汽车、航空、医疗等领域。

因此,在计算机科学专业的毕业设计中,FPGA的应用也越来越受到关注。

在FPGA的毕业设计中,一般需要考虑以下几个方面:

1.设计目标:毕业设计中需要明确设计的目标,如实现什么功能、提高什么性能等等。

2.硬件设计:根据设计目标,需要对FPGA进行硬件设计,包括电路图设计、逻辑设计、时序设计等等。

3.软件设计:与硬件设计相辅相成,软件设计是FPGA毕业设计的重要组成部分,包括使用HDL(硬件描述语言)进行代码编写,使用EDA(电子设计自动化)工具进行仿真和综合等。

4.调试和测试:毕业设计完成之后,需要进行调试和测试,确保FPGA的功能和性能达到设计要求。

5.文献综述:毕业设计中需要进行文献综述,了解相关领域内已有的研究成果和技术进展,为FPGA毕业设计的实现提供参考和借鉴。

总之,FPGA毕业设计是计算机科学专业学生的重要任务之一,要求有一定的电路和编程基础,并需要深入了解FPGA的原理和应用场景,才能够完成高水平的毕业设计。

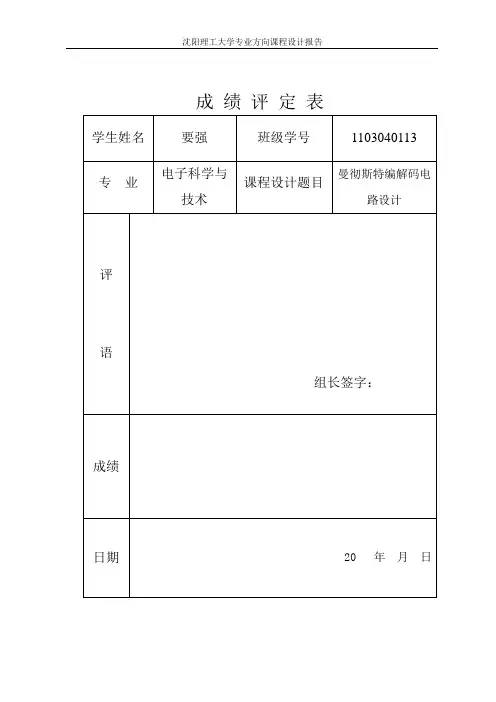

成绩评定表学生姓名要强班级学号1103040113专业电子科学与技术课程设计题目曼彻斯特编解码电路设计评语组长签字:成绩日期20 年月日课程设计任务书学院信息科学与工程学院专业电子科学与技术学生姓名要强班级学号 1103040113课程设计题目曼彻斯特编解码电路设计实践教学要求与任务:工作计划与进度安排:第1-2天:讲解题目,准备参考资料,检查、调试实验软硬件,进入设计环境,开始设计方案和验证方案的准备;第3-5天:完成设计,经指导老师验收后进入模块电路设计(验收设计文档);第6-9天:完成模块电路代码输入,并完成代码的仿真(验收代码与仿真结果);第9-10天:约束设计,综合(验收约束与综合结果);第11-12天:布局布线,完成版图(验收版图结果);第13-14天:物理验证、后仿真,修改设计(验收物理验证结果和时序仿真结果);第15天:整理设计资料,验收合格后进行答辩。

指导教师:201 年月日专业负责人:201 年月日学院教学副院长:201 年月日摘要本设计实现串行NRZ码输入,manchester码输出;manchester码输入,NRZ输出。

其中包括NRZ码字按照编码规则编码;解码恢复NRZ码;编码时2x时钟输入,在内部进行分频;解码时钟恢复选作;工作时钟10kHz即可;自行设计设计下载后的验证方案;完成全部流程:设计文档、模块设计、代码输入、功能仿真、约束与综合、布局布线、下载验证等。

本设计重点采用Verilog HDL描述、ModelSim进行功能仿真、QuartusII进行逻辑综合和适配下载,最后在Altera公司的Cyclone的芯片EP20Q240C8上实现并完成测试。

在此设计过程中,完整地建立了测试平台,通过8段数码管的显示与输出波形的验证,完成了功能和时序仿真,成功实现了串行NRZ码输入,曼彻斯特码输出;曼彻斯特码输入,NRZ输出。

在完成本次设计的同时考虑到其实用性方面,曼彻斯特码是一种数据通讯线性码,它的每一个数据比特都是由至少一次电压转换的形式所表示的。

F PG A课程设计报告(实现多功能数字钟)专业班级: 07通信2班******学号:************时间:2009.12.30一、标题:设计多功能数字钟控制电路二、任务书:用MAX+PLU SⅡ软件及Verilog HDL语言设计一个多功能的数字钟,包括有时、分、秒的计时,以及校时(对小时、分钟和秒能手动调整以校准时间)、正点报时(每逢整点,产生“嘀嘀嘀嘀-嘟”,4短一长的报时音)等附加功能。

三、关键词:24进制、60进制、正点报时、校时、数字钟四、总体方案:多功能数字钟控制电路框图是由三部分组成的,即秒分时控制电路、整点报时控制电路、时段控制电路。

用Verilog HDL硬件描述语言完成编译和仿真。

五、原理框图如下:↓↓↓六、Verilog HDL硬件描述语言编写的功能模块:/*秒计数器m60*/module m60(M,CP60M,CPM,RD);output [7:0]M;output CP60M;input CPM;input RD;reg [7:0]M;wire CP60M;always@(negedge RD or posedge CPM)beginif(!RD)begin M[7:0]<=0;endelsebeginif((M[7:4]==5)&&(M[3:0]==9))beginM[7:0]<=0;endelsebeginif(M[3:0]==9)beginM[3:0]<=0;if(M[7:4]==5)begin M[7:4]<=0;endelse M[7:4]<=M[7:4]+1;endelse M[3:0]<=M[3:0]+1;endendendassign CP60M=~(M[6]&M[4]&M[3]&M[0]); endmodule/*分计数器m60*/module m60(M,CP60M,CPM,RD);output [7:0]M;output CP60M;input CPM;input RD;reg [7:0]M;wire CP60M;always@(negedge RD or posedge CPM) beginif(!RD)begin M[7:0]<=0;endelsebeginif((M[7:4]==5)&&(M[3:0]==9))beginM[7:0]<=0;endelsebeginif(M[3:0]==9)beginM[3:0]<=0;if(M[7:4]==5)begin M[7:4]<=0;endelse M[7:4]<=M[7:4]+1;endelse M[3:0]<=M[3:0]+1;endendendassign CP60M=~(M[6]&M[4]&M[3]&M[0]); endmodule/*小时计数器m24*/module m24(H,CPH,RD);output [7:0]H;input CPH,RD;reg [7:0]H;always@(negedge RD or posedge CPH) beginif(!RD) H[7:0]<=0;elsebeginif((H[7:4]==2)&&(H[3:0]==3))beginH[7:0]<=0;endelsebeginif(H[3:0]==9)begin H[3:0]<=0;H[7:4]<=H[7:4]+1;endelse H[3:0]<=H[3:0]+1;endendendendmodule/*秒分时控制计数器xiaoshi2*/module xiaoshi2(CPM,CPH,CPS,CP60M,CP60S,SWM,SWH);output CPM,CPH;input SWM,SWH;input CPS,CP60S,CP60M;reg CPM,CPH;always@(SWM or SWH or CPS or CP60S or CP60M)begincase({SWM,SWH})2'b01: begin CPM<=CPS;CPH<=CP60M;end2'b10: begin CPM<=CP60S;CPH<=CPS;enddefault: begin CPM<=CP60S;CPH<=CP60M;end endcaseendendmodule/*时段控制器sdkz*/module sdkz(h,sk);input [7:0]h;output sk;reg sk;always@(h)beginif((h<=5)||(h>=19))sk<=1;elsesk<=0;endendmodule/*报时计数器baoshi*/module baoshi(m6,m4,m3,m0,s6,s4,s3,s0,dy,gy,bshi); input m6,m4,m3,m0,s6,s4,s3,s0,dy,gy;output bshi;wire bm;reg bshi;assign bm=m6&m4&m3&m3&m0&s6&s4&s0; always@(bm or s3 or dy or gy)beginif(bm&s3)bshi<=gy;else if(bm)bshi<=dy;elsebshi<=0;endendmodule七:各模块原理图及仿真波形:24进制原理图:60进制原理图:电路原理图:时段控制:报时:1、秒计数器仿真波形2、分计数器的仿真波形3、小时计数器的仿真波形4、秒分时控制电路的仿真波形5、时段控制的仿真波形6、报时器的仿真波形八、顶层文件及仿真波形顶层文件的仿真波形:九:选用ACEX1K芯片中的EP1K30TC144-3型号,对芯片管脚号的分配如下:十:课程设计结论:此次课程设计通过最终下载及编译可实现以上功能,在七段显示器上可实现秒、分计数器60进制,时计数器24进制显示,以及调节CLK1、CLK2的频率可使计数器上数字延时显示。

诚信声明本人声明:我所呈交的本科毕业设计论文是本人在导师指导下进行的研究工作及取得的研究成果。

尽我所知,除了文中特别加以标注和致谢中所罗列的内容以外,论文中不包含其他人已经发表或撰写过的研究成果。

与我一同工作的同志对本研究所做的任何贡献均已在论文中作了明确的说明并表示了谢意。

本人完全意识到本声明的法律结果由本人承担。

申请学位论文与资料若有不实之处,本人承担一切相关责任。

本人签名:日期:年月日毕业设计(论文)任务书设计(论文)题目:基于FPGA的数字调制器的实现学院:信息学院专业:电子信息科学与技术班级:学生:指导教师:专业负责人:1.设计(论文)的主要任务及目标(1) 查阅资料,掌握数字调制器原理及实现方法(2) 完成基于FPGA的数字调制器硬件电路设计(3) 完成各功能模块FPGA编程(4) 完成软件仿真、硬件设计和软硬件调试(5) 完成毕业论文的编写。

2.设计(论文)的基本要求和内容(1) 查阅有关数字调制原理的中外文献,学习相关知识(2) 学习FPGA基本设计原理及简单功能模块的实现方法(3) 结合数字调制原理,进行基于FPGA的数字调制器硬件电路设计。

(4) 利用VHDL语言对各功能模块编程,并完成软件仿真。

(5) 完成FPGA芯片外围电路的设计(6) 进行硬件调试与系统调试(7) 利用Protel完成原理图和PCB图的绘制。

(8) 对多种数字调制系统的性能进行比较分析(9) 编写毕业论文3.主要参考文献[1]潘松,黄继业.EDA技术实用教程[M].第二版.北京:科学出版社,2005.[2]郭梯云,邬国扬,李建东.移动通信[M].修订版.西安:西安电子科技大学出版社,2000.[3]苏小妹.软件无线电系统的研究及其FPGA实现[D].湖南:湖南大学,2005.[4]阳晰.高速数字调制解调[D].成都:电子科技大学,2005.[5]韦维,毕存强,吴兴洁.浅谈移动通信系统数字调制技术[J].无线电技术与信息,2005(10):66-69.[6]ALFREDO LINZ, ALAN HENDRICKSON.Efficient Implementation of an I-QGMSK Modulator[J].IEEE TRANSACTION ON CIRCUITS AND SYSTEMS, 1996,43(1):14-23.[7]ABHIJIT PATAIT.Efficient GMSK Modulator Targets GSMDesign[EB/OL].(2006-03-22)./CommsDesign - Efficient GMSK Modulator Targets GSM Designs.htm.[8]ALTERA CORPORATION. Cyclone Device Handbook[Z]. 2003.摘要本文实现了基于FPGA技术的多种数字调制器。

毕业设计(论文)任务书基于FPGA的LCD驱动显示电路的设计与实现摘要本课题主要任务是设计基于FPGA的LCD驱动电路的设计和实现,兼顾好程序的易用性,以方便之后模块的移植和应用。

控制器部分采用Verilog语言编写,主体程序采用了状态机作为主要控制方式。

最后实现使用FPGA在LCD上显示任意的英文字符和阿拉伯数字,另外要能根据输入数据的变化同步变化LCD上显示的内容。

同时要能将储存模块中的数据正常地显示在LCD上。

该课题的研究将有助于采用FPGA的系列产品的开发,特别是需要用到LCD的产品的开发。

同时可以大大缩短FPGA的开发时间。

另外,由于模块的易用性,也将使得更多的采用FPGA的产品之上出现LCD,增加人机之间的交互性,为行业和我们的生活带来新的变化。

本文中对FPGA,LCD,ModelSim,Xilinx ISE8.2i硬件设计工具等进行了简单的介绍,对其功能进行了简单的描述,并了解了LCD液晶显示器的发展历史,日常应用以及相对比于其他种类显示器的优缺点,并对基于FPGA的LCD液晶显示器驱动电路未来的发展趋势进行了展望。

关键词:FPGA,LCD,状态机,VerilogDesign and Implementation of LCD Drive DisplayCircuit based on FPGAAbstractIn this project, the main object is to design a LCD controller based on FPGA, and at the same time emphasize on the convenience for the later application and migration.The program of the controller is written by Verilog language, and the main body of the program used state machine as the primary control method. displayed picture which was put earlier.In this project, I finally realized the following function. The first one is to display any English and figureon character any position of the display screen. The second one is the display information will instantaneously update as the input data changes.The research of this project will contribute to the developing process of those products which use FPGAs, especially those products also use LCD. And at the same time, it can reduce dramatically on the developing time. In addition, for the convenience of this controller, more and more FPGA based products will come out with LCD screen. This change will enhance the interaction between human and the machine, and bring innovation to the industry and our lives.In this project, FPGA, LCD, ModelSim, Xilinx ISE8.2 I hardware design tools simply introduces its functions were a simple description, and understanding the LCD monitor the development history, and relative everyday applications than in other types of monitor based on FPGA advantages and disadvantages, and the LCD monitor driver circuit future development trends are discussed.Key words:, FPGA, LCD, State Machine, Verilog目录任务书 (I)摘要 ....................................................错误!未定义书签。

FPGA课程设计(报告)题目:学院:电子工程学院系部:微电子学系专业班级:微电子1702学生姓名:指导教师:李哲起止时间:2020年06月01日—2020年06月12日目录1.课程设计题目及要求 (4)1.1设计题目:基于FPGA的波形产生器。

(4)1.2设计内容 (4)1.3基本功能 (4)1.4课程设计目的 (5)1.5已完成功能 (5)2.系统设计 (5)3. FPGA设计 (6)3.1设计思路 (6)3.2顶层模块设计 (7)3.3方波产生模块 (8)3.4 锯齿波产生模块 (8)3.5 三角波产生模块 (8)3.6 正弦波ROM模块 (8)3.7 DAC模块 (9)9 (9)4.2波形选择器 (9)4.3 D/A转换器 (9)4.4低通滤波器 (9)5.模块划分 (10)5.1 模块概述 (10)5.2时钟控制模块 (10)5.3 相位控制模块 (11)5.4偏移控制模块 (12)5.5 波幅控制模块 (13)5.6 波形ROM定制模块 (13)5.7波形数据产生模块 (14)6.仿真 (14)7 心得体会 (14)8 参考文献 (15)9附录 (15)1.课程设计题目及要求1.1设计题目:基于FPGA的波形产生器。

1.2设计内容通过的以Xilinx Spartan 3E实验板为控制核心,用直接数字频率合成技术(DDS),经板上DA转换输出模拟信号,实现频率和输出电压峰-峰值都可调。

1.3基本功能1)具有产生正弦波、方波、三角波三种周期性波形的功能。

2)输出波形的频率范围为100Hz-20kHz(非正弦波频率按10次谐波计算)。

重复频率可调,频率步进间隔≤100Hz。

3) 输出波形幅度范围0-3V(峰峰值),可按步进0.1V(峰峰值)调整。

4)由外界按键输入选择产生波形的种类、频率与幅度。

5)界面显示输出波形的类型、重复频率(周期)和幅度等信号参数。

在完成基本功能的基础上,本系统还可以完成以下扩展功能:1)扩展输出波形频率范围1Hz-100KHz,频率步进间隔最小为1Hz。

摘要本设计介绍了用FPGA对信号发生器进行控制的函数发生器,然后经功率放大器使之产生固定要求的电磁场来清除水垢。

水垢分解的常用方法是利用电磁场,电磁场吸附正负离子,使之分解。

水垢处理的频率在2MHZ到20MHZ范围内。

MAX038具有可调频率特性,其频率范围为1HZ到20MHZ。

满足要求,其还具有占空比可调等优点。

MAX038与FPGA的连接用X9313数控电位器。

实现了数字与模拟的转换。

因功放电路带宽等要求,功率放大器不能用集成来实现,所以用分立元器件搭建的电路。

主要的电路部分是MAX038与FPGA连接的模块。

其全部电路图均用DXP软件来做。

功率放大部分,因为其没有专门的高频率高瓦数的集成元件,抗干扰差和其他不利因素等影响,就会使功率放大器失真。

关键词:MAX038 ;X9313 ;DXPAbstractThis subject introduces signal Generator, function generator,The subject describes the function generator with the control of Signal Generator at FPGA. Through the Generated of the power amplifier ,we need a fixed magnetic field to Clear scale. There are several common methods of the Scale decomposition:The first is the use of electric field. The scale cans decomposition in Adsorption of positive and negative electromagnetic fields. the frequency of the scale cleaning 2MHZ to 20MHZ. MAX038 owes the features of adjustable frequency. The frequency‗s range is between 1HZ and 20MHZ. In order to meet the requirements, he has the advantage of adjustable duty cycle. Connect Digital power controller named X9313 with MAX038 and FPGA. It achieves the digital and analog conversion. Bandwidth requirements for power amplifier, power amplifier cannot be used to achieve integration, so the circuit built using discrete components. The major part of the circuit is connected with the FPGA module. All of its circuits are to do with the DXP software. There is no specific integration of high frequency high wattage components, so interference and other adverse factors such as poor impact; it will make power amplifier distortion.Key words: MAX038; X9511; DXP目录1 引言 (1)1.1 科学意义和社会应用前景 (1)1.2 国内外研究概况、水平和发展趋势 (1)1.3 高频的基本原理 (2)2 总体设计原理 (4)2.1水垢生产的机理 (4)2.2 清除水垢方法 (4)2.3 设计原理 (5)3 高频信号发生器设计 (6)3.1 DXP软件介绍 (6)3.2 设计指标 (6)3.3 方案论证与比较 (7)3.4 MAX038芯片介绍 (8)3.4.1 MAX038简介 (8)3.4.2 芯片引脚 (8)3.4.3 MAX038 内部电路图 (9)3.5 频率、幅值及占空比控制 (10)3.6 芯片X9511介绍 (11)3.7 正弦波发生器设计 (13)3.8 正弦波电路PCB和示波器波形 (14)4 功率放大器设计 (17)4.1 常见功放种类 (17)4.2 功放的输出 (18)4.2.1 定阻式输出 (18)4.2.2 定压式输出 (18)4.3 功率放大器的组成 (18)4.4 功率放大器原理 (18)4.5 功率放大器电流的特点 (20)4.6 功率放大器术语 (21)4.6.1 工作范围 (21)4.6.2 传输增益 (21)4.6.3 输出功率 (21)4.7 功放设计 (21)4.7 功放电路及PCB (22)4.8 功放仿真 (23)5 控制电路设计 (24)5.1 电路功能 (24)5.2 HDL仿真 (24)5.3.1 FPGA介绍 (24)5.3.2、设计流程 (25)总结 (26)致谢 (27)参考文献 (28)附录A 英文原文 (29)附录B 英文翻译 (38)附录C 电路图 (46)1 引言1.1 科学意义和社会应用前景随着高科技工业的发展和生活水准的提高,各类水系统越来越广泛应用于工业生产及民用生活方面,如锅炉,热交换器,中央空调,循环冷却水系统等。

本科毕业设计说明书基于FPGA的高速数据采集卡的设计DESIGN OF HIGH-SPEED DATA ACQUISITION CARDBASED ON FPGA学院(部):电气与信息工程学院专业班级:学生姓名:指导教师:年月日基于FPGA的高速数据采集卡的设计摘要论文还从宏观和微观两个方面来分析数据采集卡的各个组成部分。

从宏观上分析了采集系统中各个芯片间的数据流向、速度匹配和具体通信方式的选择等问题。

使用乒乓机制降低了数据处理的速度,来降低FPGA中的预处理难度,使FPGA 处理时序余量更加充裕。

在ARM与FPGA通信方式上使用DMA传输,大大提高了数据传输的速率,并解放了后端的ARM处理器。

设计从宏观上优化数据传输的效率,充分发挥器件的性能,并提出了一些改进系统性能的方案。

从微观实现上,数据是从前端数据调理电路进入AD转换器,再由FPGA采集AD转换器输出的数据,后经过数据的触发、成帧等预处理,预处理后的数据再传输给后端的ARM处理器,最后由ARM处理器送给LCD显示。

微观实现的过程中遇到了很多问题,主要是在AD数据的采集和采集数据的传输上。

在后期的系统调试中遇到了采集数据错位、ARM与FPGA通信效率低下,还有FPGA中预处理时序紧张等问题,通过硬件软件部分的修改,问题都得到一定程度的解决。

在整个数据采集卡的设计过程中还遇到高速PCB设计、硬件设计可靠性、设计冗余性和可扩展性等问题,这些都是硬件设计中的需要考虑和重视的问题,在论文的最后一章有详细论述。

关键词:高速数据采集,触发,高速PCB设计,高速ADCDESIGN OF HIGH-SPEED DATA ACQUISITION CARDBASED ON FPGAABSTRACTDate acquisition is the premise of measure, the foundation of analysis and the beginning of cognition. Most precise device is based on the date acquisition. With the development of the electronic and digital technology, the speed of date transmission and the calculation of CPU are faster and faster; therefore the requirements of data acquisition and processing are more severe than before.This paper analyzes the system from Macro-and micro respect. From the macro point of view it analyzes data flowing, speed matching and the selection of specific means of communication of acquisition system and so on. We adapt ping-pong mechanism to reduce the speed of analyzing data and pre-difficult of FPGA which lead to the ease of processing Timing Margin of FPGA. DMA transfer is used as communication between ARM and FPGA which improve data transmission rates, and liberate the back-end ARM processor. From the micro point of view, data enter into the A/D converter from the front-end conditioning circuitry, FPGA collecting data on the output of A/D converter and go through thepre-operation of triggering and framing of data. After these operations, data are transmitted to the back-end of the ARM processor and then display on the LCD. A lot of difficult exited in the successful operation in the micro respect which is mainly about A/D data collection and the of transmission data. All of these issues have been settled by the revising of hardware and software.KEYWORDS:High-speed Data Acquisition, Triggering, High-speed PCB High-speed, A/D converter1绪论1.1 引言数计算机技术在飞速发展,微机应用日益普及深入,微机在通信、自动化、工业自动控制、电子测量、信息管理和信息系统等方面得到广泛的应用。

FPGA大作业设计报告设计背景和目标:本次FPGA大作业的设计目标是实现一个基于FPGA的音频播放器。

音频播放器可以接收来自PC或其他音频设备的音频输入,并将其通过FPGA进行处理和放大,最终输出到音频输出设备中。

设计方案:本设计方案主要分为音频输入模块、音频处理模块和音频输出模块三部分。

音频输入模块:音频输入模块主要用于接收来自PC或其他音频设备的音频输入。

首先需要设置一个适当的输入接口,可以选择使用板载的音频输入接口或者通过FPGA的GPIO引脚连接外部音频输入接口。

在接收到音频输入之后,需要对音频数据进行采样和解码。

为了实现高质量的音频播放效果,可以使用高速ADC和DAC芯片进行音频数据的采样和输出。

音频处理模块:音频处理模块主要负责音频数据的处理和增强效果的实现。

首先,可以对音频数据进行数字滤波,包括低通滤波、高通滤波、带通滤波等处理。

滤波可以有效地去除噪音和杂音,提高音频的清晰度和音质。

其次,可以使用FPGA的DSP模块实现音频的均衡器和混响器效果,使音频的频谱更加平衡和丰富。

最后,为了增强音频的立体声效果,可以实现空间声音处理算法,使得音频的声音位置更加立体和自然。

音频输出模块:音频输出模块主要负责将经过处理的音频数据输出到音频输出设备中。

可以选择使用板载的音频输出接口或者通过FPGA的GPIO引脚连接外部音频输出接口。

输出模块还可以添加放大器电路,以增强音频的输出功率和音量。

设计实施:本次FPGA大作业的设计实施主要包括硬件电路设计和软件开发两个方面。

在硬件电路设计方面,需要首先选择合适的FPGA开发板,并配置好音频输入和输出接口。

根据设计方案,设计合适的音频输入和输出电路,并进行连线和焊接。

接下来,需要根据设计方案中的要求,选择合适的ADC和DAC芯片,并与FPGA进行连接。

最后,进行电路的调试和测试,确保音频输入和输出电路的正常工作。

设计成果和展望:通过本次FPGA大作业的设计和实施,成功实现了一个基于FPGA的音频播放器。

目录1.设计思路 (1)1.1设计思想 (1)1.2 系统功能与要求 (1)1.3总体设计 (2)2.主要模块设计程序 (4)2.1时基脉冲发生模块 (4)2.2技术及红绿灯控制模块 (5)2.3译码模块 (9)2.4主程序 (11)3. 所实现功能说明 (14)3.1实现功能 (14)3.2仿真波形 (14)4. 所设计原理图及故障分析 (15)5.心得体会 (17)参考文献 (18)附录1 元件清单 (19)附录2 管脚 (20)1.设计思路1.1设计思想交通灯是城市交通监管系统的重要组成部分,对于保证机动车辆的安全运行,维持城市道路的顺畅起到了重要作用。

目前很多城市交叉路口的交通灯实行的是定时控制,灯亮的时间是预先设定好的,在时间和空间方面的应变性能较差,一定程度上造成了交通资源的浪费,加重了道路交通压力。

本文在EDA技术的基础上,利用FPGA的相关知识设计了交通灯控制系统,可以根据实际情况对灯亮时间进行自由调整,整个设计系统通过Max+PlusⅡ软件进行了模拟仿真,并下载到FPGA器件中进行硬件的调试,验证了设计的交通信号灯控制电路完全可以实现预定的功能,具有一定的实用性。

1.2 系统功能与要求交通灯控制器控制两个主干道交叉路口的交通,路口车辆多,直行信号、左转弯信号分开显示,a,b两个主干道的通行时间相等,其中指示直行的绿灯亮30 s,指示左转弯的绿灯亮12 s,绿灯变至红灯时,黄灯亮3 s,以便于车辆能停在停车线内,红灯信号的最后 3 s相应的黄灯也同时亮,以便提示驾驶人员准备起步。

在两个主干道路口都配备传感器用来检测有无车辆通行。

当两个主干道都有车辆时,自动处于主干道a绿灯,主干道b红灯的状态,然后轮流切换通行。

当主干道a无车辆时,自动处于主干道b绿灯,主干道a红灯的状态;反之亦然,以提高通行效率。

所设计的交通信号灯控制电路,主要适用于在两条干道汇合点形成的十字交叉路口,路口设计两组红绿灯分别对两个方向上的交通运行状态进行管理。