基于PCIe总线的红外探测器图像采集系统设计

- 格式:pdf

- 大小:540.44 KB

- 文档页数:4

基于计算机技术 PCIE的光纤图像实时采集方案摘要:在光学系统中,为了取得更高质量的光学影像,需增加感应器数目,提升感应器解像度,这大大增加了光电影像收集系统收集的计算量。

为了符合高速收集和即时表明大量光学影像资料的要求,提出了一种基于PCIE接口的光学影像收集系统。

该系统以FPGA为掌控主体,使用专属桥接处理器PEX8311构建PCIE协定,使用轻量化设计观念,新建多样的拓展API。

试验结果表明,单通道收集的即时光电影像资料与服务器的具体通讯速度为170MB/S,比学说PCI带阔132MB/S高出约30%,克服了现代基于SATAAPI的系统资料传送传输不足的难题。关键词:光电系统;光电图像采集;PCIE接口;实时性;通讯带宽随着半导体技术的发展,光学感应器的解像度越来越高。

在大型光学系统中,为了取得更高质量的高清晰度影像,通常采用解像度更高的感应器。

为了符合光学影像收集系统与服务器间的即时通讯要求,在光学影像收集系统与服务器间的通讯中普遍使用SATAAPI。

SATA控制器具备资料传输速率高、即插即用、耗电低、适应力强等优点。

然而,SATA的传输有限,不容易通过并行传输敏捷拓展。

作为新的控制器和接口标准,PCIE不仅承继了SATA的优点,还包含许多新机能,如高带宽、低耗电和高可靠性长处。

本文提出了一种基于SATAAPI的光学影像收集系统,以代替现代的基于SATAAPI的光学影像收集系统。

(一)系统组成光学影像收集系统主要由光学转化组件、串串联转化元件,光电影像收集和LBS控制电路、光电影像储存元件、PCIEAPI元件和字符输入API。(二)工作原理光学影像收集系统通过传输API接管传输传送的影像脉冲。

光信号转入光学影像收集系统之后,光学转化组件将光信号转化为总线声波。

串并转化元件回复总线资料并输入译码的平行影像资料和像素时钟。

平行资料转入影像收集控制电路,收集的光学影像资料储存在影像缓冲器元件中。

基于PCIe总线高速数据传输系统的设计与实现的开题报告一、选题背景随着现代科技的飞速发展,数据处理和传输变得越来越重要。

不仅需要高效的数据传输速度以满足现代大数据处理的需要,也需要高可靠性和兼容性以适应不同应用场景的需求。

PCI Express(PCIe)总线技术由于其高速、可靠和广泛的应用支持而成为了一种重要的数据传输标准。

本课题基于此,旨在设计和实现一个基于PCIe总线的高速数据传输系统。

二、研究目的和意义本课题主要研究基于PCIe总线的高速数据传输系统的设计和实现,旨在提供一个具有高速、可靠、兼容性好的数据传输方案,以满足现代数据处理需求。

其意义在于:1. 提高数据处理效率。

PCIe总线技术具有高速传输和低延迟的特点,在大数据处理和高性能计算中能够显著提高数据传输效率。

2. 提高数据传输可靠性。

PCIe总线技术具有高可靠性的特点,其锁定机制和CRC校验功能能够保证数据传输的准确性和完整性。

3. 提高数据传输兼容性。

PCIe总线技术是一种广泛应用的数据传输标准,被应用于各种不同的领域,能够实现不同设备之间的数据交换和共享。

三、研究内容和研究方法本课题的主要研究内容包括:1. 设计一个符合PCIe总线规范的高速数据传输系统。

包括硬件电路设计和软件控制程序设计。

2. 实现高速数据传输系统,采用HDL语言设计硬件电路,采用C++设计软件控制程序。

3. 测试和验证高速数据传输系统,包括性能测试、稳定性测试和兼容性测试等。

本课题研究采用的方法主要包括:1. 系统设计方法。

根据PCIe总线规范,设计一个符合标准的高速数据传输系统,保证系统的性能、稳定性和兼容性。

2. 硬件设计方法。

采用HDL语言设计系统的硬件电路,包括PCIe 总线接口电路、数据传输电路和控制逻辑电路等。

3. 软件设计方法。

采用C++设计软件控制程序,包括系统的控制逻辑和数据传输协议等。

4. 测试和验证方法。

对系统进行性能测试、稳定性测试和兼容性测试等,以验证系统的可靠性和兼容性。

基于FPGA的红外图像实时采集系统设计与实现摘要:随着红外图像在军事、航天、安防等领域的广泛应用,对红外图像的实时采集和处理需求越来越高。

本文基于FPGA设计并实现了一个红外图像实时采集系统,通过系统硬件框架、图像采集流程设计以及软硬件协同优化等方面的探究,实现了高效、稳定的红外图像实时采集和传输,为相关领域的探究和应用提供了重要支持。

一、引言红外图像技术是一种利用物体发射的红外辐射进行成像分析的技术,具有透过阴郁、烟雾等不利环境的能力。

它在军事、航天、安防等领域具有重要应用价值。

红外图像的实时采集和处理对于这些领域的探究和应用至关重要,然而传统的红外图像采集系统存在采集速度慢、波动大、传输距离限制等问题。

因此,设计并实现一种基于FPGA的红外图像实时采集系统具有重要意义。

二、系统框架设计基于FPGA的红外图像实时采集系统主要由硬件和软件两个部分组成。

硬件部分包括红外探测器、FPGA开发板、存储器、图像传输模块等;软件部分主要包括图像采集控制程序和数据处理程序。

硬件框架设计接受分层结构,分为红外图像采集层、控制层、存储层和传输层四个部分。

红外图像采集层包括红外探测器和模拟-数字转换电路,负责将红外辐射信号转换为数字信号。

控制层包括FPGA芯片和时钟控制电路,负责采集信号的控制和同步。

存储层包括高速存储器和图像缓存,负责暂存采集到的红外图像数据。

传输层包括数据传输电路和网络接口,负责将采集到的图像数据传输到外部设备。

三、图像采集流程设计图像采集流程是指将红外图像转换为数字信号并存储的过程。

在红外图像采集层,红外探测器将红外辐射信号转换为模拟信号,经过模拟-数字转换电路转换成数字信号。

在控制层,FPGA芯片控制采集信号的采样频率和位宽,通过时钟控制电路实现同步。

在存储层,高速存储器负责将采集到的图像数据暂存起来,图像缓存则将暂存的图像数据进行处理和压缩。

在传输层,数据传输电路将处理和压缩后的图像数据传输到外部设备。

一种基于I^(2)C总线的温度监控电路的设计

代明清;赵谦;花飞

【期刊名称】《航空计算技术》

【年(卷),期】2022(52)4

【摘要】CPU处理器是嵌入式系统的核心器件,温度异常会影响系统的可靠性及寿命,为了监控CPU处理器的温度,设计实现了一种基于PowerPC处理器和数字测温芯片的温度监控电路。

详细介绍了电路硬件结构、工作原理、软件设计流程及配置方法。

电路以PC8640为主处理器,以ADT7461为测温芯片,通过I^(2)C总线实现了对处理器温度与产品温度的实时采集及监控,并具备超温报警功能。

验证结果表明,电路能够精确获取到处理器温度及产品温度,工作性能稳定、可靠性高、实时性好,满足设计需求。

【总页数】5页(P112-116)

【作者】代明清;赵谦;花飞

【作者单位】航空工业西安航空计算技术研究所

【正文语种】中文

【中图分类】TN274.2

【相关文献】

1.基于RS-485总线的远距离温度监控系统的设计

2.基于Modbus总线的智能烘房温度监控系统的设计

3.基于CAN总线的智能微喷灌监控系统中下位机的硬件电

路组成与设计4.基于RS-485总线的多点温度监控系统设计5.基于CAN总线的分布式锅炉炉膛温度监控系统设计

因版权原因,仅展示原文概要,查看原文内容请购买。

基于PCI总线的心电信号数据采集系统的设计

李宗君;高延滨

【期刊名称】《测控技术》

【年(卷),期】2008(027)007

【摘要】介绍了基于PCI总线的心电信号数据采集系统的设计,由硬件和软件两部分组成.硬件包括心电信号的放大滤波以及基于PCI总线的采集电路,软件包括

E2PROM的配置、FPGA时序设计以及PCI总线驱动程序的设计.

【总页数】3页(P17-19)

【作者】李宗君;高延滨

【作者单位】哈尔滨工程大学,自动化学院,黑龙江,哈尔滨,150001;哈尔滨工程大学,自动化学院,黑龙江,哈尔滨,150001

【正文语种】中文

【中图分类】TP391

【相关文献】

1.基于PCI总线的光谱信号实时数据采集系统 [J], 曹彦波;王兴华;于爱民;金钦汉

2.基于通用串行总线的心电信号数据采集系统 [J], 田建君

3.基于PCI总线的红外探测器图像数据采集系统设计与实现 [J], 郑可旺;黄勇;王聪

4.基于PCI-E总线的高速光纤数据采集系统设计 [J], 王慧英;曹志锋

5.基于PCIe总线的高速数据采集系统设计与实现 [J], 尤焜

因版权原因,仅展示原文概要,查看原文内容请购买。

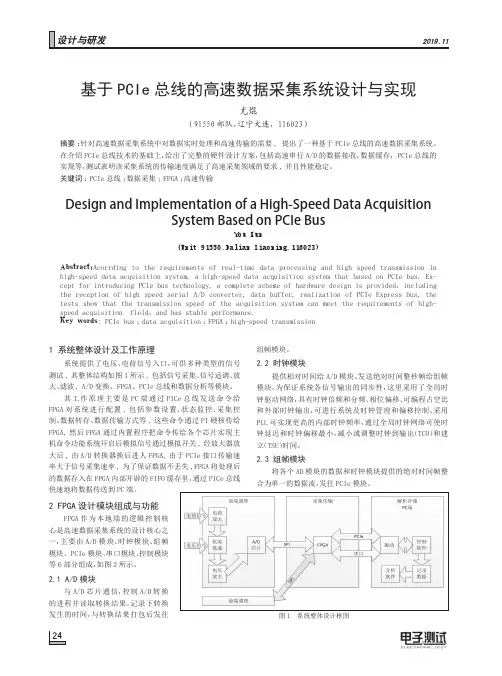

1 系统整体设计及工作原理系统提供了电压、电荷信号入口,可供多种类型的信号测试,其整体结构如图1所示,包括信号采集、信号适调、放大、滤波、A/D 变换、FPGA、PCIe 总线和数据分析等模块。

其工作原理主要是PC 端通过PICe 总线发送命令给FPGA 对系统进行配置,包括参数设置、状态监控、采集控制、数据转存、数据传输方式等,这些命令通过PI 硬核传给FPGA,然后FPGA 通过内置程序把命令传给各个芯片实现主机命令功能系统开启后模拟信号通过模拟开关,经放大器放大后,由A/D 转换器换后进人FPGA,由于PCIe 接口传输速率大于信号采集速率,为了保证数据不丢失,FPGA 将处理后的数据存入在FPGA 内部开辟的FIFO 缓存里,通过PICe 总线快速地将数据传送到PC 端。

2 FPGA 设计模块组成与功能FPGA 作为本地端的逻辑控制核心是高速数据采集系统的设计核心之一,主要由A/D 模块、时钟模块、组帧模块、PCIe 模块、串口模块、控制模块等6部分组成,如图2所示。

2.1 A/D 模块与A/D 芯片通信,控制A/D 转换的进程并读取转换结果。

记录下转换发生的时间,与转换结果打包后发往组帧模块。

2.2 时钟模块提供相对时间给A/D 模块。

发送绝对时间整秒帧给组帧模块。

为保证系统各信号输出的同步性,这里采用了全局时钟驱动网络,具有时钟倍频和分频、相位偏移、可编程占空比和外部时钟输出,可进行系统及时钟管理和偏移控制。

采用PLL 可实现更高的内部时钟频率,通过全局时钟网络可使时钟延迟和时钟偏移最小,减小或调整时钟到输出(TCO)和建立(TSU)时间。

2.3 组帧模块将各个AD 模块的数据和时钟模块提供的绝对时间帧整合为单一的数据流,发往PCIe 模块。

tests show that the transmission speed of the acquisition system can meet the requirements of high-speed acquisition field,and has stable performance.Key words : PCIe bus ;data acquisition ;FPGA ;high-speed transmission图1 系统整体设计框图2.4 PCIe 模块PCIe 模块实现了PCIe 总线的物理层、数据链路层、配置管理层的协议,上层提供一个事务层接口,通过该接口完成应用逻辑,最终实现“设备-主机”方向的数据流传输即可。

基于PCI-E和光纤的红外高速传输系统黄新栋【摘要】With the rapid development of infrared technology, the higher infrared data rate is required. Aiming at the high-speed requirement of a new infrared imaging system, a novel method for infrared image high-speed transmission was proposed, which was implemented with Peripheral Component Interconnect (PCI) Express and optical fiber. The system achieved an infrared image transmission speed of over 100 Mbyte/s. The infrared imaging experimental results show that the system meets the demand for high-speed infrared image acquisition.%随着红外成像探测系统向长线列和大面阵方向发展,红外数据量大幅度增加,传统的数据传输技术已不能满足这么高的传输速度要求,针对这个问题采用先进的PCI(peripheral componentinterconnect,外设组件互联)Express(简称PCI-E)技术和光纤高速传输技术,系统速度达到100 Mbyte/s以上,解决了红外图像超高速传输问题,并通过实验采集到了高质量的红外图像.结果表明,该系统对高速红外图像采集具有很高的实用价值.【期刊名称】《应用光学》【年(卷),期】2011(032)003【总页数】4页(P518-521)【关键词】光纤;红外;PCI;Express;现场可编程门阵列【作者】黄新栋【作者单位】中国科学院,上海技术物理研究所,上海,200083【正文语种】中文【中图分类】TN818;TP336引言红外探测系统通过感应目标的红外辐射,将其转换为电信号输出,形成红外图像,实现目标的探测。

基于PCIe高速通信接口的图像处理系统设计袁柳; 李皓; 李勐; 涂吉【期刊名称】《《科学技术与工程》》【年(卷),期】2019(019)022【总页数】6页(P235-240)【关键词】PCIe; 现场可编程门陈列(FPGA); 图像处理; 手写字符识别; 卷积神经网络【作者】袁柳; 李皓; 李勐; 涂吉【作者单位】中国电子科技集团公司电子科学研究院北京100041; 武汉大学电子信息学院武汉430072【正文语种】中文【中图分类】TP391.41随着大数据、人工智能行业的发展,图像、视频等所需处理的数据量呈爆炸性增长,尤其在以卷积神经网络(convolutional neural network,CNN)为代表的深度学习领域,图像处理系统的计算能力和传输能力需要不断提高。

传统的中央处理器(central processing unit,CPU)、图形处理器(graphics processing unit, GPU)架构存在能耗高、性价比低等问题,现场可编程门陈列(field-programmable gate array,FPGA)作为可编程的硬件,可以根据应用需要实现硬件动态重构,具备高度并行的流水处理能力,CPU+FPGA异构处理架构正成为图像处理的重要解决方案之一[1]。

CPU和FPGA之间高效协同处理需要高速数据传输接口,PCIe总线支持基于PCIe Switch芯片的接口扩展,支持接口位宽、接口数量动态配置,具备优异的可扩展性、灵活性、普适性和低延迟特性,文献[2—5]通过PCIe DMA技术可以实现CPU和FPGA之间的高速数据通信,但是由于PCIe接口复杂,需要丰富的设计经验,目前基于 PCIe接口的图像处理系统还没有得到广泛推广。

文献[6—9]开始借助PCIe高速通信接口实现多路视频图像传输,但是还没有形成一种统一的基于PCIe 的图像处理框架,需要根据不同应用从头开始设计FPGA硬件架构,导致应用开发效率不高。

基于PCIe总线的专用高速信号采集卡设计作者:林连雷易宇来源:《现代电子技术》2015年第21期摘要:在某些雷达对抗试验中,为了精确地评估试验效果,设计了一个高速信号采集系统,该系统具有最高为500 MS/s的采样率,板上缓存为1 GB,同时提供与高速存储系统的数据传输接口以供外扩存储容量。

该系统提供了示波器工作模式和连续采集工作模式两种工作模式,用户可根据需求使用不同的工作模式对采集到的数据进行处理,同时该系统具有完善的触发功能,以方便用户对数据进行分析。

关键词: PCI Express;高速数据采集;模拟信号;同步脉冲信号中图分类号: TN911.7⁃34 文献标识码: A 文章编号: 1004⁃373X(2015)21⁃0052⁃04 Design of dedicated high⁃speed signal acquisition card based on PCIe busLIN Lianlei, YI Yu(Department of Automatic Test and Control, Harbin Institute of Technology, Harbin 150001, China)Abstract: In some radar countermeasure tests, a high⁃speed signal acquisition system was designed to assess the test results accurately. This system has the maximum sampling rate of 500MS/s, in which the cache in the card is 1 GB, and can provide data transmission interface ofhigh⁃speed storage system to expand the storage capacity. Two operation modes of the scope operating mode and the continuous acquisition mode are offered in this system, and users can use the different operating modes according to the requirements to process the collected data. This system has perfect trigger function, and is convenience for the users to analyze the data.Keywords: PCI Express; high⁃speed data acquisition; analog signal; synchronous pulse signal0 引言在某些雷达对抗试验中,为了精确地评估试验效果,需要对雷达接收机产生的回波信号、同步脉冲信号等进行采集,通过对这些信号的分析得出试验结果,基于此目的,需要设计一个具有高速采集能力的系统,用于采集雷达接收机产生的回波信号、同步脉冲信号;同时该系统需要具备大容量存储能力,用于实时存储采集到的数据,为雷达对抗试验后续的数据分析提供数据来源;为了更好地捕捉雷达对抗试验中的关键信号,该系统应该具备完善的触发功能。