基于FPGA的图像采集系统设计与实现

- 格式:doc

- 大小:27.00 KB

- 文档页数:5

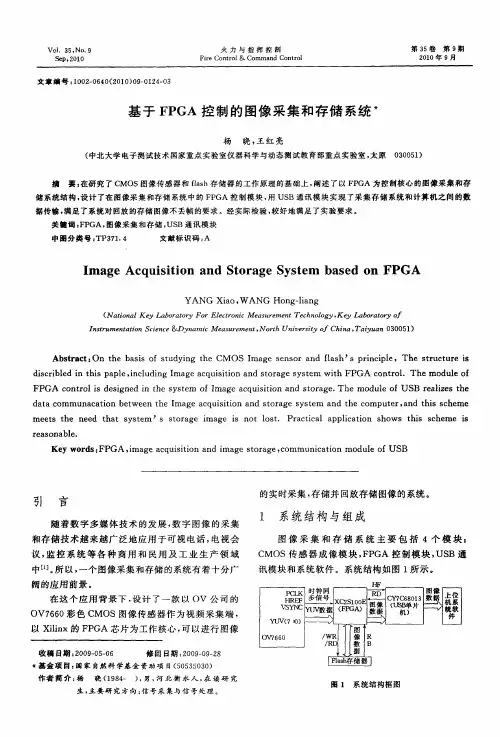

基于ZYNQ FPGA实现图像采集存储显示1 FPGA硬件系统设计基于ZYNQ FPGA实现图像数据采集、存储、处理和显示系统框图如图1所示。

说明:2路摄像头采集系统,4种显示方案,原始数据显示2路,经过算法处理2路。

图1 系统设计OV5640模块:图像传感器,视频流来源。

写VDMA模块:硬件采集到的数据通过写VDMA存储到PS端的DDR中。

ZYNQ模块:ZYNQ-7000系列FPGA,ARM + FPGA架构,核心处理芯片。

读VDMA模块:通过读VDMA从PS端的DDR中读取图像数据。

RGB转换DVI模块:32bit转为RGB888,再转为DVI时序输出到HDMI显示。

HDMI显示器:显示图像视频数据。

2 关键技术1)OV5640摄像头设计中采用两片美国OmniVision公司的CMOS图像传感器OV5640,OV5640芯片支持DVP和MIPI接口。

为保证OV5640正常工作,需要依次实现以下时序要求。

a、ResetB拉低、PWND拉高;b、DOVDD和AVDD同时上电;c、电源稳定5ms后,拉低PWND,再过1ms,拉高ResetB;d、20ms后初始化OV5640DESCCB寄存器。

e、通过IIC接口配置,配置目标为RGB565、30FPS、720输出格式;f、FPGA接收来自OV5640的视频流数据输入,需要对摄像头完成相应的时序操作。

每次传输8bit,16bit为一个像素点,所以要进行数据转换8bit-16bit-32bit;2)图像处理算法边缘检测算法要求首先找到图片中物体的边缘,由于边缘处颜色变化一般比较明显,在工程上一般借助卷积滤波器实现,卷积滤波器相当于求导的离散版本。

针对图像进行边缘检测,有多种不同的滤波器算子,我们采用的Sobel滤波器算子图1,分别针对图像水平方向的边缘以及竖直方向的边缘,求和得出图像的边缘。

图1 滤波器算子3)ZYNQ FPGAZYNQ 7000系列基于Xilinx 全可编程的扩展处理平台结构,芯片内部集成ARM 公司双核Cortex-A9处理器的处理系统(PS端)和基于Xilinx逻辑资源的可编程逻辑系统(PL端)。

基于FPGA的图像处理与识别系统设计摘要:本文章主要介绍了基于FPGA的图像处理与识别系统的设计。

首先,简要介绍了FPGA技术的基本原理和优势。

接着,分析了图像处理与识别系统的关键问题和需求。

然后,详细描述了基于FPGA的图像处理与识别系统的设计步骤和流程。

最后,给出了实验结果和性能评估。

通过本文的阐述,读者可以了解基于FPGA的图像处理与识别系统的设计思路和方法,并且可以应用于实际应用中。

关键词:FPGA,图像处理,识别系统,设计。

1. 引言随着计算机视觉技术的飞速发展,图像处理与识别技术在各个领域得到广泛应用。

基于FPGA的图像处理与识别系统具有并行性能强、低功耗、高速处理等优势,成为研究和应用的热点之一。

本文旨在通过设计一个基于FPGA的图像处理与识别系统,探索FPGA技术在该领域的应用。

2. FPGA技术概述FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,它由大量的逻辑门和可编程的互连电路组成。

与传统的ASIC(Application-Specific Integrated Circuit)相比,FPGA具有灵活性和可重新配置性的特点,可以极大地加快设计周期并降低成本。

3. 图像处理与识别系统的关键问题和需求图像处理与识别系统的关键问题主要包括图像采集、特征提取、分类判断等。

针对不同领域和应用,系统的需求也有所不同,例如实时性要求、算法复杂度、性能稳定性等。

4. 基于FPGA的图像处理与识别系统设计步骤4.1 图像采集与预处理图像采集是构建图像处理与识别系统的基础,可以通过CCD或CMOS等传感器进行图像采集。

在FPGA中,采用外部模块与FPGA进行通信,将图像数据传输到FPGA 芯片中,并进行预处理。

4.2 特征提取与处理特征提取是图像处理与识别系统的核心任务。

在FPGA 中,可以通过利用FPGA的并行计算能力加速特征提取算法。

例如,采用卷积神经网络(CNN)对图像进行卷积运算,提取图像的特征。

基于FPGA的图像处理系统设计与实现图像处理是计算机视觉领域中的重要技术之一,可以对图像进行增强、滤波、分割、识别等操作,广泛应用于医学图像处理、工业检测、安防监控等领域。

而FPGA(Field Programmable Gate Array)可编程门阵列,则是一种自由可编程的数字电路,具有并行处理能力和灵活性。

本文将介绍基于FPGA的图像处理系统的设计与实现。

一、系统设计流程1. 系统需求分析:首先需要明确图像处理系统的具体需求,例如实时性、处理的图像类型、处理的算法等。

根据需求,选择合适的FPGA芯片和外设。

2. 图像采集与预处理:使用图像传感器或摄像头采集图像数据,然后对图像进行预处理,如去噪、增强、颜色空间转换等,从而提高后续处理的准确性和效果。

3. 图像处理算法设计与优化:根据具体的图像处理需求,选择适合的图像处理算法,并对算法进行优化,以提高处理速度和效率。

常用的图像处理算法包括滤波、边缘检测、图像分割等。

4. FPGA硬件设计:基于选定的FPGA芯片,设计硬件电路,包括图像存储、图像处理模块、通信接口等。

通过使用硬件描述语言(如Verilog、VHDL)进行功能模块设计,并进行仿真和验证。

5. 系统集成与编程:将设计好的硬件电路与软件进行集成,包括FPGA程序编写、软件驱动开发、系统调试等。

确保系统的稳定运行和功能实现。

6. 系统测试与优化:对整个系统进行完整的测试和验证,包括功能性测试、性能测试、稳定性测试等。

根据测试结果,对系统进行优化,提高系统的性能和可靠性。

二、关键技术及挑战1. FPGA芯片选择:不同的FPGA芯片具有不同的资源和性能特点,需要根据系统需求选择合适的芯片。

一方面需要考虑芯片的处理能力和资源利用率,以满足图像处理算法的实时性和效果。

另一方面,还需要考虑芯片的功耗和成本,以便在实际应用中具有可行性。

2. 图像处理算法优化:在FPGA上实现图像处理算法需要考虑到算法的计算复杂度和存储开销。

基于FPGA的红外图像实时采集系统设计与实现摘要:随着红外图像在军事、航天、安防等领域的广泛应用,对红外图像的实时采集和处理需求越来越高。

本文基于FPGA设计并实现了一个红外图像实时采集系统,通过系统硬件框架、图像采集流程设计以及软硬件协同优化等方面的探究,实现了高效、稳定的红外图像实时采集和传输,为相关领域的探究和应用提供了重要支持。

一、引言红外图像技术是一种利用物体发射的红外辐射进行成像分析的技术,具有透过阴郁、烟雾等不利环境的能力。

它在军事、航天、安防等领域具有重要应用价值。

红外图像的实时采集和处理对于这些领域的探究和应用至关重要,然而传统的红外图像采集系统存在采集速度慢、波动大、传输距离限制等问题。

因此,设计并实现一种基于FPGA的红外图像实时采集系统具有重要意义。

二、系统框架设计基于FPGA的红外图像实时采集系统主要由硬件和软件两个部分组成。

硬件部分包括红外探测器、FPGA开发板、存储器、图像传输模块等;软件部分主要包括图像采集控制程序和数据处理程序。

硬件框架设计接受分层结构,分为红外图像采集层、控制层、存储层和传输层四个部分。

红外图像采集层包括红外探测器和模拟-数字转换电路,负责将红外辐射信号转换为数字信号。

控制层包括FPGA芯片和时钟控制电路,负责采集信号的控制和同步。

存储层包括高速存储器和图像缓存,负责暂存采集到的红外图像数据。

传输层包括数据传输电路和网络接口,负责将采集到的图像数据传输到外部设备。

三、图像采集流程设计图像采集流程是指将红外图像转换为数字信号并存储的过程。

在红外图像采集层,红外探测器将红外辐射信号转换为模拟信号,经过模拟-数字转换电路转换成数字信号。

在控制层,FPGA芯片控制采集信号的采样频率和位宽,通过时钟控制电路实现同步。

在存储层,高速存储器负责将采集到的图像数据暂存起来,图像缓存则将暂存的图像数据进行处理和压缩。

在传输层,数据传输电路将处理和压缩后的图像数据传输到外部设备。

基于T35F324的FPGA开发板图像采集显示系统方案1.前言个人觉得易灵思的TriOn系列比钛金系列FPGA,就目前而言,更适合做图像显示相关应用,以T35和巨60为例,主要原因如下表所示:易灵思如果专注图像细分领域,毕竟大部分客户还是用DDR和MIPI,因此我觉得钛金系列的架构真的脑袋被驴踢了,DDR和MIP1用硬核才是正确的选择!另外,钛金系列FPGA相对推出时间不够,目前IP也不成熟。

以T35为例,DDR硬核IP在EfinityInterface中直接可以调用DDRIP并设定相关参数,但是钛金系列Ti60还没有包含到工具链中,这让拿不到一手资源的FPGAer就很尴尬,虽然可以理解不集成到IDE中,可以更快的迭代前提不成熟的版本。

M1P1TX/RX 接口,山谷0.8mm40P 接口如上图所示,T35F324的FPGA 开发板,我都做了快半年了,一直没有做一个基于视频图像的像样点的DCm0,甚是惭愧。

为了给当下煎熬的大家送点福利,我打算分2步走,如下:DVP 相机+DDR3+1VDS-1CD 实时显示系统 MIPI 相机+DDR3+1VDS-1CD 实时显示系统前者更关注DDR3硬核、1VDSTX,以及进行并口相机的配置与图像采集,完成实时图像采集、缓存、显示系统;后者则借用1)的基础,更关注MIP1相机的开发,进一步把易灵思FPGA 进行图像采集的优势,发挥一下。

当然这过程肯定还是有不少的坑,有些坑只有自己趟过,才有发言权。

底板串口DC3-40用户接口,兼容兼容@01⑥MT拨动开关BMW 0V5生0等模MIP1摄像头Jr兼容树莓派rOV5640 Efint FPQABOa1Q CraZyfpg>iomEfin1tyT3SF324-Cor∙V1.1一«... M2X>S12202305152.FPGA设计详解言归正传,我们开始干正事:基于T35的摄像头采集、存储、显示系统的介绍。

基于FPGA的图像处理技术设计与实现随着科技的不断发展,图像处理技术的应用也越来越广泛。

FPGA(Field-Programmable Gate Array)作为一种基于可编程逻辑门电路的数字逻辑器件,其在图像处理领域中的应用也越来越受到人们的关注。

本文主要介绍了基于FPGA的图像处理技术的设计与实现。

一、FPGA的基本原理及优势FPGA的基本原理是将逻辑门电路实现的芯片替换为可编程的逻辑门电路阵列,即可灵活编程实现特定功能。

与专用集成电路相比,FPGA具有灵活性强、时间开发短、生产周期短等优势。

在图像处理应用中,FPGA具有以下优势:1. 高速度:FPGA具有并行处理能力,因此在图像处理中可以实现高速运算,提高计算效率。

2. 可编程:FPGA可以根据不同的需求和算法进行灵活编程,可以实现多种图像处理算法。

3. 低功耗:由于FPGA采用可编程的电路设计,因此不需要像传统电路一样进行不必要的计算操作,从而降低功耗。

二、基于FPGA的图像处理技术设计与实现在基于FPGA的图像处理技术中,主要包括图像采集、图像预处理、图像处理、图像输出等步骤。

下面我们将一一介绍。

1. 图像采集图像采集是图像处理的第一步,主要是通过摄像头或其他设备获取输入图像。

在采集图像时,需要进行数字化处理,将模拟信号转换为数字信号,以便后续的图像处理操作。

2. 图像预处理图像预处理主要是对输入图像进行去噪、滤波、增强等操作,以减少噪声和干扰,提高图像质量。

常见的图像预处理算法包括均值滤波、中值滤波、高斯滤波、边缘增强等。

3. 图像处理图像处理是基于FPGA的图像处理技术的核心步骤。

在此步骤中,需要选择适合的算法实现不同的图像处理操作,例如图像分割、目标检测、目标跟踪等。

常见的图像处理算法包括Canny算法、Harris角点检测算法、SIFT算法等。

4. 图像输出图像输出是将处理后的图像输出到显示屏或其他设备上。

常见的输出方式包括液晶显示、投影显示、打印输出等。

基于FPGA的图像采集系统设计与实现

摘要:图像采集是数字化图像处理的第一步,开发图像采集平台是视觉系统开发的基础。

本课题提出了基于FPGA的图像采集系统整体实现方案。

采用Verilog HDL语言编写程序,并用Modelsim等软件进行联合仿真,然后下载到DE2开发板实现图像采集功能。

关键词:FPGA 图像采集DE2开发板Verilog HDL Modelsim

图像采集是视频信号处理系统的前端部分,正在向高速、高分辨率、高集成化、高可靠性方向发展。

图像采集处理器件主要有专用集成芯片、数字信号处理器和现场可编程门阵列以及相关电路组成。

近年来,微电子技术和超大规模的集成电路制造技术的发展,特别FPGA 的发展,为提高图像采集处理系统各种性能提供了新的思路和方法。

1 系统硬件结构设计

本系统采用的是DE2开发平台,系统主芯片采用Altera公司的Cyclone II系列FPGA(EP2C35F672C6),该芯片具有33 216个LE,105个M4K RAM块,472 kb的内部RAM容量,35个内嵌乘法器单元,4个模拟锁相环等,广泛应用于汽车电子、消费电子、音/视频处理、通信以及测试测量等终端产品市场。

系统设计还包含有:D5M视频采集板,8MB SDRAM、视频D/A、VGA接口等,硬件结构如图1所示。

1.1 图像传感器

本系统所采用的TDRB_D5M摄像头套件,使用的是CMOS图像传感器。

集成500万像素摄像头,通过对其内部寄存器的设置,来配置摄像头的图像采集和工作模式。

1.2 视频缓存器设计

DE2平台采用的是型号为IS42S16400的SDRAM,IS42S16400是ISSI公司推出的一种单片存储容量高达64 Mb(即8 MB)的16位字宽高速SDRAM芯片。

1.3 视频D/A电路

DE2平台的Video DAC选用了Analog Device公司的ADV7123。

从图像缓存器中提取的数据转换为视频信号,通过VGA输出显示。

ADV7123是三路高速、10位输入的视频D/A转换器,具有240MHz 的最大采样速度,与多种高精度的显示系统兼容,包括RS-343A和RS-170,可以广泛应用于如HDTV、数字视频系统、高分辨率的彩色图片图像处理、视频信号再现等,因此,能够满足我们多方面应用需求。

2 FPGA内部模块设计

在确定DE2平台的硬件需求部分后,需要在FPGA中设计相应的功能模块,才能使系统正常的工作。

这些功能模块有:图像采集模块、图像格式转换模块、图像缓存模块和图像显示模块。

2.1 像采集模块

系统硬件使用的是D5M摄像头套件,该套件采用的是500万像素CMOS数字图像传感器,可以使用I/C总线配置其相应的寄存器来设置工作模式和采集数据的大小。

图像采集模块可以分为:图像数据捕获模块和COMS传感器配置模块。

2.2 图像格式转换模块

本系统采用的CMOS传感器采集到的数据是Bayer颜色模式,使用数据缓存加流水线的处理方式,将由上一级抓取到行数据实时转换成RGB数据,其中R、G、B各占12位,在输入SDRAM缓存中时,多口SDRAM控制模块只取用R、G、B的高10位来存储,所以RGB最终是30位的数据。

2.3 图像缓存模块

预处理的图像需要放在存储器中,对于大部分的FPGA来说器件内部都含有4 k的内存,而本系统采集的图像容量为1.1 MB左右,还要考虑今后对动态图像处理功能的扩展,所以本设计选用了DE2外扩存储容量为8 M的SDRAM。

2.4 VGA显示模块

要把存储器里的图像在VGA接口显示器中显示,扫描时序是需要我们构造的。

不同的显示模式和刷新频率下,具体同步信号前、后、

同步信号、有效像素数是不同的,要根据像素时钟频率来设置。

本系统从缓存中读出的图像大小为640×480,59.94 Hz(60 Hz)。

3 系统仿真和结果分析

我们采用SignalTap II嵌入逻辑分析仪和ModelSim进行联合测试与仿真。

仿真结果完全符合系统的实时要求。

在Quartus II下在完成了整个系统工程的调试和验证后,通过Compilation仿真的Compilation Report可以看出系统的资源消耗,整个硬件系统消耗的逻辑资源为5%,实验表明,还有大量资源可以应用于其他模块。

本系统实现了实时图像采集,为之后的实时图像预处理和分析做准备。

这些信息可以用于图像分析、目标识别以及图像滤波等领域。

利用本课题所采用的开发环境可以进一步开发出更复杂的图像算法和创建更复杂的系统功能,使整个视频图像处理系统达到全面集成化,最终达到资源的充分利用。

参考文献

[1]张志刚.FPGA与SOPC设计教程DE2实践[M].西安:西安电子科技大学出版社,2007.

[2]李贵华,夏磊,韦先霜,等.基于SOPC的VGA显示技术的研究[J].计算机与数字工程,2007(2):138-139.

[3]胡瑶荣.基于FPGA的实时视频采集系统[J].电视技

术,2005(2):81-83.

[4]胡晓飞,殳国华,张士文.基于视频处理芯片和CPLD的实时图像采集系统[J].电子技术,2002(10):28-30.。