else begin q<=d; qn<=~d; end

end

endmodule

2、带清零端、置1端的JK触发器

module JK_FF(CLK,J,K,Q,RS,SET);

input CLK,J,K,SET,RS;

output Q;

reg Q;

always @(posedge CLK or negedge RS or negedge SET )

采用“assign”语句是描述组合逻辑电路最常用的方法之一。

(3)用“always”或“initial”过程块。 (行为描述)

使用initial和always的区别

“always”块既可用于描述组合逻辑,也可描述时序逻辑。

always语句是不断地重复活动的,直到仿真过程结束。但always语句后的

同步置数,低电平有效. input A,B,C,D; output F;

常见组合与时序逻辑电路Verilog HDL描述 3’b110:out=8’b10111111;

output pass;

default: out =8 'bx;

reg[2:0] outcode;

begin 端口信号名称可以采用位置关联方法和名称关联方法进行连接。

begin if(h) outcode=3’b111;

if(!RS) Q<=1’B0;

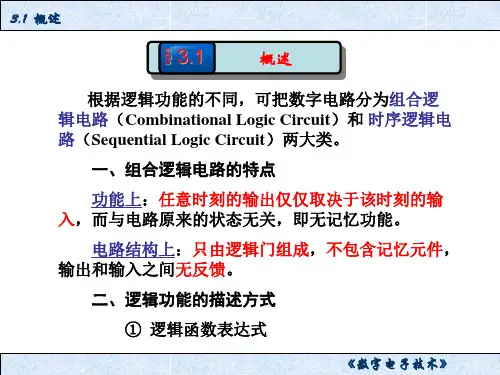

(1)调用内置门元件描述

module gate3(F,A,B,C,D);

input A,B,C,D; output F;

nand (F1,A,B); and(F2,B,C,D); or(F,F1,F2); //调用内置门

4’d6:{a,b,c,d,e,f,g}=7’b1011111;