基于FPGA的AGWN信号生成器

- 格式:docx

- 大小:11.56 KB

- 文档页数:2

一、VGA显示原理1、VGA显示器采用光栅扫描方式,即轰击荧光屏的电子束在CRT显示器上从左到右、从上到下做有规律的移动,其水平移动受水平同步信号HSYNC控制,垂直移动受垂直同步信号VSYNC控制。

扫描方式多采用逐行扫描。

完成一行扫描的时间称为水平扫描时间,其倒数称为行频率,完成一帧扫描时间称为竽扫描时间,其倒数称为场频,又称为刷新率。

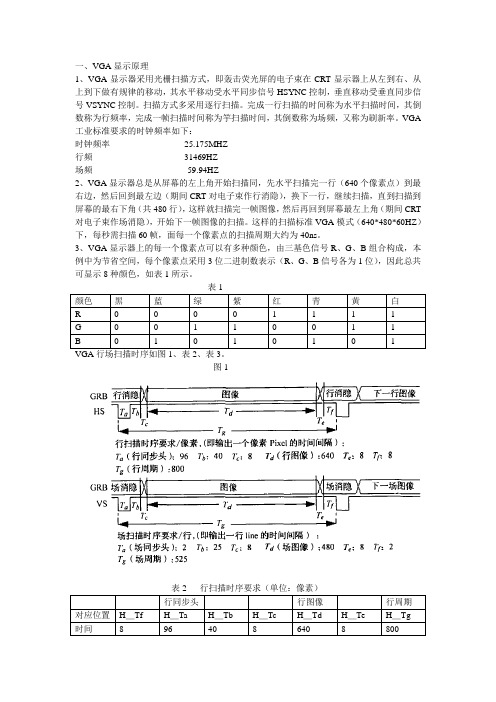

VGA 工业标准要求的时钟频率如下:时钟频率25.175MHZ行频31469HZ场频59.94HZ2、VGA显示器总是从屏幕的左上角开始扫描同,先水平扫描完一行(640个像素点)到最右边,然后回到最左边(期间CRT对电子束作行消隐),换下一行,继续扫描,直到扫描到屏幕的最右下角(共480行),这样就扫描完一帧图像,然后再回到屏幕最左上角(期间CRT 对电子束作场消隐),开始下一帧图像的扫描。

这样的扫描标准VGA模式(640*480*60HZ)下,每秒需扫描60帧,面每一个像素点的扫描周期大约为40ns。

3、VGA显示器上的每一个像素点可以有多种颜色,由三基色信号R、G、B组合构成,本例中为节省空间,每个像素点采用3位二进制数表示(R、G、B信号各为1位),因此总共可显示8种颜色,如表1所示。

图1表2 行扫描时序要求(单位:像素)根据以上的行、场扫描时序的要求,我们可设置两个计数器,一个是行计数器hcnt,进行模800计数;另一个是场计数器vcnt,进行模525计数。

行扫描计数器的驱动时钟频率(像素输出的频率)按照VGA工业标准为25.175MHZ。

场扫描计数器以行同步信号HS为驱动时钟,当HS的下降沿到来时进行计数。

设置完计数器后,就可对行图像H-Td和场图像V-Td 所对应的640*480个点赋值。

二、源代码。

在下面的例子中,实现了一个彩条信号产生器。

其中key为控制按键,当其为“00”时,显示竖彩条;当其为“01”时,显示横彩条。

其它值时显示棋盘格。

VGA彩条信号发生器源代码/*引脚定义clock50MHZ :输入时钟采用50MHZ:key :彩条选择信号,为“00”时显示竖彩条,为“01”时横彩条,其它情况显示棋盘格;rgb :输出三基色;hs :行同步信号;vs :场同步信号。

FPGA驱动VGA测试初版程序使用规则此程序原创于飞琳工作室,可用于fpga学习实验所用,完全个人兴趣编写没有版权限制.文件夹,top&testbench中包含设计的顶层文件,vga接口时序生成部分,新手注意testbench只是在modulesim测试的时候使用,在quartus中编译综合时用不着,不要加在工程里rgb信号通过diamonds_displaydiamonds(.clk(clk),.rst(rst),.h_counter(h_counter),.v_counter(v_counter),.vertical(vert ical),.r(r),.g(g),.b(b));tier_displaytier(.clk(clk),.rst(rst),.h_counter(h_counter),.v_counter(v_counter),.vertical(vertical),.r (r),.g(g),.b(b));row_displayrow(.clk(clk),.rst(rst),.h_counter(h_counter),.v_counter(v_counter),.vertical(vertical),. r(r),.g(g),.b(b));传入顶层文件,默认为第一个反色方框游走于田字窗口中.子程序为diamonds_display如果想测试vga信号产生是否正确可以调用tier_display 和row_display彩条测试子程序如果你特别无聊,想同时测试横竖条,tier_display程序之中还准备了彩色阶梯的测试程序,把注销的部分重新启用就好了,别忘了同时注销掉彩条中生成的rgb的部分如果你还是很无聊,可以自己生成某些图像的rgb,也可以把图片存在调用的ram 中,读取.本程序适用于alter和xilinx的芯片,其实是其他的公司的芯片没见过,只要你的开发板上有VGA接口,注意引脚配置正确.就可以使用,本程序适合初学者使用,欢迎孜孜不倦的成熟工程师检验,期待提出意见,指出不足,开创更好,欢迎加QQ653092769探讨fpga开发相关问题。

VGA(视频图形阵列)作为一种标准的显示接口在视频和计算机领域得到了广泛的应用。

VGA图像信号发生器是电视台、电视机生产企业、电视维修人员常用的仪器,其主要功能就是产生标准的图像测试信号。

VGA图像信号发生器的设计涉及到图像数据的处理,对电路的工作速度和性能要求较高,VGA工业标准要求的时钟频率高达25MHz,使用传统的电子电路设计方法是难以实现的。

采用专用的视频处理芯片,其设计技术难度大、开发成本高。

本文采用FPGA+MCU方案,利用了Cyclone系列的FPGA高达上百兆的工作频率特性为图像数据处理提供了良好的实时性,其内部集成的数字锁相环为系统的工作时钟提供的良好的稳定性,其内部嵌入的存储器可以存储一定容量的图像信息,丰富的I/O资源可以随即扩展外接大容量存储器的特性,因此由 FPGA完成对图像数据的处理及产生行场扫描时序信号。

很好地实现了图象数据处理的实时性和稳定性,达到了性能与价格的完美统一。

此外,FPGA的电路可重构性,为系统功能更改和升级以及功能扩展提供了很大的设计空间。

由微控制器完成功能设置与控制,如键盘扫描,模式选择与显示控制等。

2、系统的工作原理和组成框图FPGA是整个系统的核心,通过对其编程可输出RGB三基色信号和HS 、VS行场扫描同步信号。

当 FPGA 接受单片机输出的控制信号后,内部的数据选择器模块根据控制信号选通相应的图像生成模块,输出图像信号,与行场扫描时序信号一起通过15针D型接口电路送入VGA显示器,在VGA显示器上便可以看到对应的彩色图像。

FPGA所需的工作时钟由外部高精度有源晶振提供;单片机控制器分析键盘扫描结果,控制液晶显示模块显示相应的功能,由LCD显示输出图象和按键控制模式,并送出相应控制信号给FPGA,系统原理框图如图1。

3、VGA显示器原理工业标准的VGA显示模式为:640×468×16色×60Hz。

常见的彩色显示器,一般由CRT (阴极射线管)构成,彩色是由R、G、B(红、绿、蓝)三基色组成,CRT用逐行扫描或隔行扫描的方式实现图像显示,由VGA控制模块产生的水平同步信号和垂直同步信号控制阴极射线枪产生的电子束,打在涂有荧光粉的荧光屏上,产生R、G、B三基色,合成一个彩色像素。

基于FPGA的VGA的字符显⽰题⽬基于FPGA的字符显学⽣姓名指导⽼师学院专业班级1、背景随着电路设计技术的进步,微处理器和微控制器的处理能⼒得到很⼤的提⾼,但是其输出显⽰能⼒却⽐较弱。

还不如普通的PC机的显⽰能⼒,严重制约了其发展。

⽽本⽂提出的基于FPGA的VGA字符显⽰则能很好提⾼其输出显⽰能⼒。

VGA(Video Graphics Array)是IBM在1987年随PS/2机⼀起推出的⼀种视频传输标准,具有分辨率⾼、显⽰速率快、颜⾊丰富等优点,在显⽰器领域得到了⼴泛的应⽤。

近年来FPGA在嵌⼊式系统中得到了⼴泛应⽤,本实验对基于FPGA的VGA显⽰系统进⾏了研究,该系统可以很好的实现VGA 字符的显⽰和控制,系统具有成本低、结构简单、应⽤灵活的优点,具有⼴泛应⽤前景。

基于FPGA的VGA接⼝原理如图l所⽰,图中基于FPGA的VGA接⼝原理如图l所⽰,图中由FPGA产⽣的数据信号经过D/A转换为相应的VGA信号,送到VGA适配器。

1.1 FPGA的发展和其他可编程逻辑器件⼀样,FPGA也由未完成的逻辑阵列所组成,通过将这些逻辑阵列连接到⼀起来完成⼀定的功能。

像PAL⼀样,各个阵列单元之间的相互连接是可以编程的。

下⾯介绍FPGA的发展过程。

1985年,Xilinx公司推出了世界上第⼀款FPGA。

推出的这款FPGA包括两个器件和⽀持布同布线的设计⼯具。

FPGA的发展⾮常快,在不到10年的时间⾥,时钟频率就从不到10MHz 提⾼到100MHz.设计规则已经达到亚微⽶级别,FPGA芯⽚的规模也从⼏千门增加到2万多等效门。

⼤量功能强⼤易⽤的软件⼯具也相继推出,使得FPGA很快占领了电⼦设计领域很⼤的⼀块市场。

20世纪80年代推出的FPGA可以说是Intel公司于1971年推出第⼀款商⽤微处理器的延续。

那个时期,典型的微处理器系统包含微处理器、存储器和⼀些特殊功能的中⼩规模(MSI/SSI)器件。

为追求更佳的件能、更⼩的尺⼨、更低的成本、更快的错误恢复能⼒、⾼可靠性以及更快更易使⽤的原型,集成电路的设计者都意识到⼀定会有⼀种器件要取代当时的中⼩规模电路。

基于FPGA的多功能信号源生成系统设计与实现陈亮;张炜【摘要】为了满足科研与实验需要,提出并实现了一种以FPGA和高速D/A为核心,其结构简单,控制灵活,信号质量高的多功能信号源生成系统.该信号源生成系统能够实时产生中心频率在30~130 MHz的各种雷达、通信、导航和白噪声等信号,且产生的各种信号频率、幅度,相位和其他参数均可控.信号源作为基带信号单元配以混频模块,可实现在任意频段的信号.另外,该信号源还可以作为一个通用平台,通过FPGA内部程序的更新来实现其他复杂信号.【期刊名称】《现代电子技术》【年(卷),期】2009(032)006【总页数】4页(P34-37)【关键词】FPGA;信号源;硬件设计;AD9736【作者】陈亮;张炜【作者单位】国防科学技术大学,电子科学与工程学院,湖南,长沙,410073;中国人民解放军95445部队,云南,祥云,672103;中国人民解放军95445部队,云南,祥云,672103【正文语种】中文【中图分类】TP368.1产品级的信号源往往满足不了科研和实验的需要,尤其在复杂电磁环境的研究和实验中,需要的信号样式多种多样,而且根据场景的不同,需要信号样式、个数都发生了改变。

现场可编程逻辑阵列器件(FPGA)继承了ASIC中大规模、高集成度、高可靠性的优点,克服了普通ASIC设计周期长,投资大,灵活性差的缺点,逐步成为复杂数字硬件电路设计的理想首选。

为了能满足科研与实验的需要,产生一系列需要的信号,设计了一种以FPGA和高速D/A为核心,能产生中心频率在30~130 MHz 的、各种参数均可调的雷达、通信、导航和噪声信号的多功能信号源生成系统。

1 系统硬件结构多功能信号源生成系统在综合控制器的控制下产生一个或多个中心频率在30~130 MHz的雷达、通信、导航、噪声等信号,输出电平-60~0 dBm,步进值为0.06 dB。

系统主要由综合控制器、信号生成器、射频模块和天线4个部分构成,如图1所示。

基于FPGA的正弦信号发生器的设计作者:汪桂霞来源:《价值工程》2014年第03期摘要:本文基于FPGA设计了一个正弦信号发生器,采用直接数字频率合成(DDS)技术,实现了信号发生器的频率、相位可以控制。

并对系统进行了Modelsin功能仿真,仿真结果证实此次设计有较好的可靠性,且产生的波形最高频率可以达到1.25M,频率稳定度在1%以内。

Abstract: This paper describes the design of a sinusoidal signal generator based on FPGA,with direct digital frequency synthesis (DDS) technology, the frequency, the phase signal generator can control. And the system of the Modelsin function simulation, simulation results show that this design has good reliability, high frequency and waveform generation can reach 1.25M,frequency stability within 1%.关键词:直接数字频率合成(DDS);FPGA;正弦波信号发生器Key words: Direct Digital frequency Synthesis (DDS);FPGA;sine wave signal generator中图分类号:TP346 文献标识码:A 文章编号:1006-4311(2014)03-0200-020 引言信号发生器作为一种为电子测试和计量工作电信号的设备,它和示波器、电压表、频率计等仪器一样,是最普通、最基本,也是应用最广泛的电子仪器之一,几乎所有的电参量的测量都要用到信号发生器。

基于FPGA的VGA信号发生器设计韩磊【摘要】进入到数字化与信息化时代,随着电子产品的广泛运用,各种产品更新换代的速度也随之加快,注重向容量大、体积小、重量轻的方向发展.本文对基于FPGA 的彩条及动态字符显示的方案进行论述,在FPGA开发平台Quar-tusII9.0上采用VHDL语言对时序控制模块、彩条像素模块以及存储模块等功能模块进行配置,并对各个模块进行编译、仿真.【期刊名称】《产业与科技论坛》【年(卷),期】2018(017)020【总页数】2页(P54-55)【关键词】FPGA技术;VHDL语言;VGA显示技术【作者】韩磊【作者单位】江海职业技术学院【正文语种】中文一、引言当今社会,已经进入数字化与信息化时代,各种电子产品广泛运用,更新换代的速度也随之加快,伴随着计算机、集成电路等科学技术的高速发展,电子系统的设计愈加趋向于容量大、体积小、重量轻的方向发展,与此同时,液晶显示技术的飞速发展让终端显示方式变得节能健康,目前市场上的智能产品和电子器材逐步采用液晶显示作为显示终端。

但是仍然有一些显示器还是利用VGA显示标准(技术)来呈现一些视频图像,此次设计主要是讲述完成VGA信号发生的驱动,主要由可编程器件FPGA来完成。

随着FPGA技术的不断发展,可编程逻辑设计的应用优势逐渐显现出来,具有价格下降、运算速度快、管脚资源丰富、容易实现大规模的系统设计、有大量的软核可用、抗干扰能力强等特点。

如果想要克服图像的显示不依靠计算机的控制,实现低功耗、实体微型化,那就需要对终端显示装置的VGA接口进行有效的设计,通过逻辑性的程序控制实现视频图像的可靠输出。

FPGA技术正是可以解决这一问题的有效方式,利用FPGA开发平台设计,最终使得需要显示的数据流只需要在整个系统的内部流动,提高了系统的灵活性和现实性。

二、专业技术概述本文主要是对FPGA技术、VHDL语言、VGA显示技术方面知识的综合运用。

(一)FPGA技术。

VGA一、设计目的1、利用VHDL语言的描述方法进行设计完成VGA显示的系统设计;2、自行选择VGA显示模式;3、通过FPGA产生VGA Monitor的控制时序;4、通过FPGA产生彩条图形,在VGA显示器上显示;5、扩展要求:可以在拨动开关控制下,通过FPGA+VGA接口的系统在屏幕上显示不同图像。

二、设计原理1、VGA简要介绍显示绘图阵列(video graphic array,VGA)接口是LCD液晶显示设备的标准接口,大多应用在显示器与显卡之间,同时还可以用在等离子电视输入图像的模数转换上。

VGA显示输出RGB三原色信号,RGB色彩模式是工业界的一种颜色标准,是通过对红(R)、绿(G)、蓝(B)三个颜色通道的变化以及它们相互之间的叠加来得到各式各样的颜色,目前在图像显示领域中应用非常广泛。

2、VGA的显示特点(1)扫描格式繁多,分辨率从320×200一直延伸到1280×102,行频15.8~70Hz,场频50~100Hz。

常见的行频有31.4Hz,37.8Hz,57.9Hz,62.5Hz 等,常见场频有50Hz,60Hz,70Hz,100Hz,16700K之分。

(2)显示器的显示方式有两种:A/N显示方式和APA显示方式,即文本显示方式和图形显示方式。

A/N方式已淘汰不用,目前微机都采用APA图形方式。

(3)VGA接口为显示器提供两类信号,一类是数据信号,一类是控制信号。

数据信号包括红(Red)、绿(Green)、蓝(Blue)信号,简称RGB信号,控制信号包括水平同步信号和垂直同步信号。

输出不同分辨率时,水平同步信号和垂直同步信号的频率也不相同。

3、VGA显示原理常见的彩色显示器一般由CRT(阴极射线管)构成,彩色是由R(红)、G(绿)、B(蓝)三种基色组成。

显示是采用逐行扫描的方式,阴极射线枪发出的电子束打在涂有荧光粉的荧光屏上,产生RGB三色基,最后合成一个彩色图像。

基于FPGA的线性调频信号产生器设计摘要:本文在研究DDWS原理的基础上,给出了一种基于FPGA技术的线性调频信号产生器的设计方案。

采用FPGA技术可以方便地通过修改编程参数,对线性调频信号的起始频率、带宽、频率分辨率进行修改。

仿真结果表明,该设计能够产生符合要求的线性调频信号,并且具有结构简单、集成度高、易于修改等特点。

关键词:FPGA;线性调频;DDWS;线性调频(LFM)信号由于其时宽带宽积远大于1,通过脉冲压缩处理,可以得到良好的距离分辨率和径向速度分辨率,因此在合成孔径雷达、高分辨力雷达、线性调频连续波雷达、雷达高度表等现代雷达系统中得到广泛应用,用于产生LFM 信号的系统称之为线性调频信号产生器。

DDWS技术是近年来采用的生成稳定的点频、线性调频信号的理想方法,具有幅度和相位一致性好、频率转换时间短、频率分辨率高、输出频率相对带宽较宽、输出波形相位连续、电路设计简单、可靠性高等突出的优点。

1 DDWS技术工作原理与特点1.1 DDWS技术工作原理直接数字波形合成技术主要分为两个阶段,存储波形和还原波形。

存储波形是将我们所需要的输出信号波形,由上位机仿真软件按照采样率、带宽和时宽等参数计算出信号波形中各个采样点的值,经量化和编码存储至高速存储器中。

还原波形时,由系统时钟提供一个参考时钟给时钟控制逻辑,时钟控制逻辑分别控制地址控制逻辑和D/A转换。

1.2 DDWS技术的特点1)极高的频率分辨率:在满足奈奎斯特定理情况下,DDWS技术产生信号的频率分辨率仅由D/A转换器件的位宽决定。

D/A转换器的位宽越大,信号的频率分辨率越高。

本文拟产生的LFM信号频率范围是0~150 MHz, 根据奈奎斯特定理,D/A转换器的转换速率应>300 MSPS。

2)极短的频率转换时间:由DDWS技术的原理框图可知,输出信号的波形存储于高速存储器中,切换不同频率的信号时,频率转换时间由高速存储器读取决定,读取时间可达皮秒量级。

基于FPGA的专用信号处理器设计

贾玉臣;吴嗣亮

【期刊名称】《电讯技术》

【年(卷),期】2005(45)6

【摘要】用可编程门阵列(FPGA)实现了一个专用信号处理器,它以快速傅里叶变换(FFT)为核心工作单元,对四路零中频雷达回波依次进行去除直流分量、数据加窗、FFT、目标信号选大和相位参考信号检测等处理.各处理单元流水操作,保证了处理速度,提高了资源的利用效率.FFT算法为输入顺序输出位反序的DIT基2算法,采用递归结构实现,硬件共享设计节省了资源;同时,处理过程中采用块浮点算法,兼顾了定点的高速度与浮点的高精度;并对FFT结果进行了误差分析,给出了定点与块浮点两种算法时的均方误差上限.最后对整个设计进行了仿真验证,结果表明用FPGA实现专用信号处理器满足系统要求.

【总页数】5页(P105-109)

【作者】贾玉臣;吴嗣亮

【作者单位】北京理工大学,信息科学技术学院,电子工程系,北京,100081;北京理工大学,信息科学技术学院,电子工程系,北京,100081

【正文语种】中文

【中图分类】TN957.5

【相关文献】

1.基于FPGA的专用信号处理器设计和实现 [J], 杜兆林;吴嗣亮

2.基于反馈控制结构的FFT信号处理器设计与FPGA实现 [J], 宗爱华;张双;吴恙;杨维明

3.基于FPGA的星载AIS信号处理器的设计 [J], 张喆

4.基于FPGA的星载AIS信号处理器的设计 [J], 张喆

5.基于FPGA多功能数字信号处理器的EDA设计 [J], 吴小红

因版权原因,仅展示原文概要,查看原文内容请购买。

基于FPGA的AGWN信号生成器

在通信系统中分析计算系统抗噪声性能时,经常假定信道噪声为加性高

斯型白噪声(AGWN)。

本文就是通过分析AGWN 的性质,采用自顶向下的设计思路,将AGWN 信号分成若干模块,最终使用Verilog 硬件描述语言,完成了通信系统中AGWN 信号发生电路的设计和仿真,其实质上是设计一个AGWN 信号发生器。

该信号主要应用在数字通信系统中,所以只需要产生数字形式的AGWN 信号,这样既便于信号产生,也便于在数字通信系统中运用。

1 AGWN 信号的产生AWGN 信号指同时满足白噪声和高斯噪声的条件的信号。

白噪声功率密度函数在整个频率域内是常数,即服从均匀分布。

完全理想的白噪声不存在。

高斯噪声指概率密度函数服从高斯分布(即正态分布)。

AGWN 信号其实就是一个具有确定功率谱密度和概率分布函数的随机信号。

由随机过程的理论可以知道,不相关随机序列的功率谱密度为常数(白噪声),伪随机序列(PN)就是这样的不相关序列。

再由中心极限定理,独立同分布的随机变量的和收敛于高斯随机变量。

这样就可根据PN 序列的性质和中心极限定理来设计AWGN 信号。

为简单起见,设计用8 个PN 序列发生器产生8 个独立的伪随机序列(每个分为实部和虚部),根据中心极限定理,将8 个信号相加之后的信号,更加接近于AG-WN 信号,最后再乘以一个可变系数,就产生了可在数字通信系统中直接引用的AGWN 信号。

AGWN 信号生成的总体框图如图1 所示。

在FPGA 内部产生n 位并行伪随机序列,可由n 个并行的结构相同但初始态互不相同的线性反馈移位寄存器(LFSR)产生。

结构相同的LFSR 在不同初始状态下产生的序列之间存在着一种移位关系,导致n 个序列并非相互独立。

如。