基于MCUCPLD变压器测试系统的设计与实现全文下载-

- 格式:doc

- 大小:198.50 KB

- 文档页数:5

收稿日期:2006-04 作者简介:陈裕国(1965—),男,硕士,讲师,主要从事嵌入式系统开发、控制工程等方面的教学与科研工作。

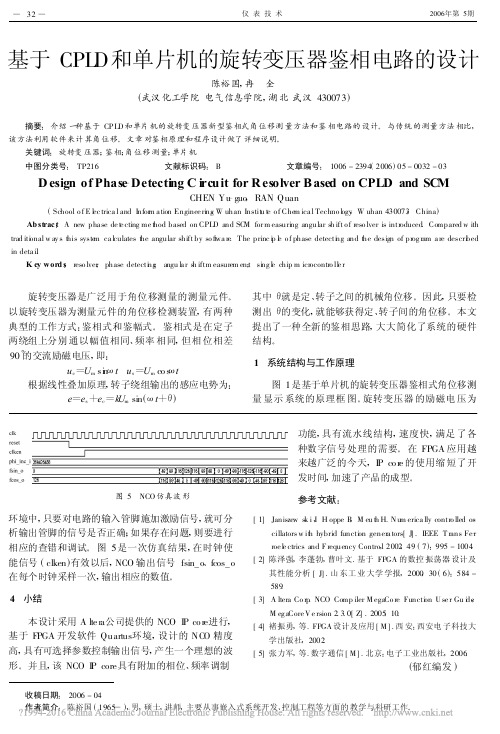

基于CPL D 和单片机的旋转变压器鉴相电路的设计陈裕国,冉 全(武汉化工学院电气信息学院,湖北武汉430073) 摘要:介绍一种基于CP LD 和单片机的旋转变压器新型鉴相式角位移测量方法和鉴相电路的设计。

与传统的测量方法相比,该方法利用软件来计算角位移。

文章对鉴相原理和程序设计做了详细说明。

关键词:旋转变压器;鉴相;角位移测量;单片机中图分类号:TP216 文献标识码:B 文章编号:1006-2394(2006)05-0032-03D esign of Phase -Detecti ng C i rcuit for R esolver B ased on CPLD and SC MCHEN Yu -guo ,RAN Quan(School o f E l ec trica l and Infor m a tion Enginee ri ng ,W uhan Instit u t e o f Che m ica l Techno l ogy ,W uhan 430073,China )Ab strac t :A new pha se de t e cting me t hod based on CPLD and SC M for m easuri ng angular s h ift o f reso lver is introduced .Compared w ith trad iti onal w ay s t his syste m ca l culates t he angular shift by so ft wa re .T he princ i p l e o f phase detecti ng and t he design of prog ram a re descri bed in deta i.lK ey word s :reso lver ;phase detecti ng ;angu l a r s h iftm easurem en t ;si ng l e chip m icrocontro ll e r 旋转变压器是广泛用于角位移测量的测量元件。

单片机与CPLD协同设计实验系统近年来,随着电子技术的飞速发展,单片机(Microcontroller)和CPLD(Complex Programmable Logic Device)作为嵌入式系统设计中的两个重要元件,逐渐成为工程领域的焦点。

单片机拥有强大的计算和控制能力,而CPLD则可以实现复杂的逻辑功能,二者相互结合可以实现更多更强大的应用。

本文将介绍单片机与CPLD协同设计实验系统的原理、应用以及未来发展方向。

一、概述单片机与CPLD协同设计实验系统是一种结合了单片机和CPLD技术的实验平台,用于验证和研究不同技术之间的协同工作方式。

该实验系统可以通过多种接口方式连接单片机和CPLD,实现数据传输和控制信号的交互。

通过该系统,可以进行嵌入式系统的设计、开发和验证,提高系统的可靠性和扩展性。

二、原理单片机与CPLD协同设计实验系统的原理主要包括接口连接和通信协议。

在硬件设计方面,通过引脚的连接,将单片机和CPLD相连。

在软件设计方面,通过编程实现单片机和CPLD之间的数据传输和控制。

具体的原理如下:1. 接口连接单片机和CPLD之间的连接可以通过多种方式实现,常用的有并行接口(如GPIO)、串行接口(如SPI、I2C)和通用总线接口(如USB、PCI)等。

通过这些接口,可以实现数据的输入和输出,并控制CPLD的工作状态。

2. 通信协议单片机与CPLD之间的通信需要使用一种协议,以确保数据的正确传输和高效处理。

常见的通信协议包括UART、SPI、I2C等。

这些协议可以实现单片机和CPLD之间的双向数据传输和控制。

三、应用单片机与CPLD协同设计实验系统的应用非常广泛。

它可以应用于各个领域的嵌入式系统开发和教育培训。

以下是该系统的一些主要应用:1. 嵌入式系统设计与开发通过单片机与CPLD协同设计实验系统,可以进行嵌入式系统的设计与开发。

以智能家居系统为例,可以通过单片机来控制温度、照明等功能,而CPLD则用于实现数据的处理和传输,以及各个功能模块的调度和控制。

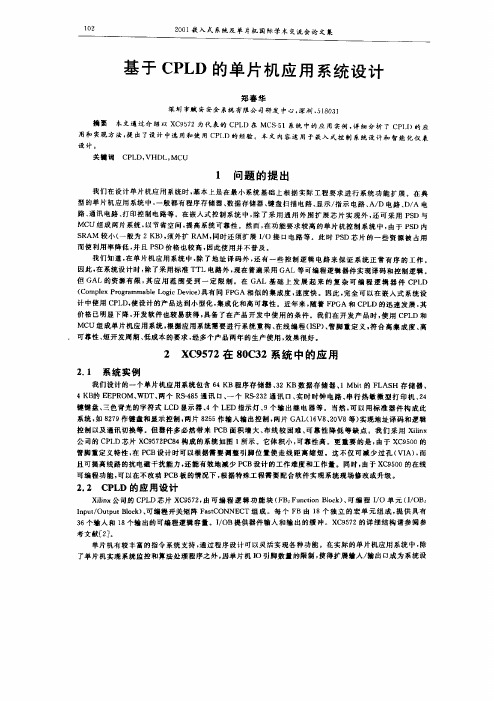

1022001嵌入式系统及单片机国际学术交流会论文集———————————————————————————————————一基于CPLD的单片机应用系统设计郑春华深圳市赋安安全系统有限会司研发中心.深圳.51803l摘要本文通过介绍烈XC9572为代表的CPI,D在MCs_51系统中的应用实例,详细分析了CPI,I)的应用和实现方法,提出了设计中选用和使用CPI。

D的经验。

本文内容适用于嵌入式控制系统设计和智能化仪袁设计。

关键词CPLD,VHDL,MCIf1问题的提出我们在设计单片机应用系统时,基本上是在最小系统基础上根据实际工程要求进行系统功能扩展。

在典型的单片机应用系统中・一般都有程序存储器、数据存储器、键盘扫描电路、显示/指示电路、A/D电路、D/A电路、通讯电路、打印控制电路等。

在嵌入式控制系统中,除了采用通用外围扩展芯片实现外,还可采用PSD与MCU组成两片系统・以节省空问,提高系统可靠性。

然而,在功能要求较高的单片机控制系统中,由于PSD内SRAM较小(一般为2KB),须外扩RAM,同时还须扩展I/O接口电路等。

此时PSD芯片的一些资源被占用而使利用翠降低,并且PSD价格也较高,因此使用并不普及。

我们知道,在单片机应用系统中・除了地址译码外,还有一些控制逻辑电路来保证系统正常有序的工作。

因此,在系统设计时,除了采用标准TTL电路外,现在普遍采用GAI.等可编程逻辑器件实现译码和控制逻辑。

但GAI一的资源有限,其应用范围受到一定限制。

在GAI。

基础上发展起来的复杂可编程逻辑器件CPLD(ComplexProgrammableLogicDevice)具有同FPGA相似的集成度,速度快。

因此,完全可以在嵌人式系统设计中使用CPI,D,使设计的产品达到小型化,集成化和高可靠性。

近年来,随着FPGA和CPLD的迅速发展.其价格已明显下降,开发软件也较易获得,具备了在产品开发中使用的条件。

我们在开发产品时,使用CPLD和MCU组成单片机应用系统,根据应用系统需要进行系统重构、在线编程(ISP)、管脚重定义,符合高集成度、高可靠性、短开发周期、低成本的要求,经多个产品两年的生产使用,效果很好。

基于MCU CPLD变压器测试系统的设计与实现编者按:BX型信号变压器,BG型轨道变压器和ZG型硅整流器作为铁路信号电器设备的前端,其工作的稳定性、准确性直接关系到行车安全,变压器的可靠检测是严抓质量的第一步,对于生产厂家而言,测试流程不允许抽样,且测试结果应留档。

本套测试系统用来测试铁路变压器的各种要求参数,包括原边空载电流、次边空载电压、次边带载电压电流,变压器绝缘电阻、原边电压频率,测量结果精度要求3%,测试系统分为上下位机两大部分,下位机运用智能仪表的设计思想,在MCU和CPLD控制基础上对各种要求测试参数分别进行自动测试,上位机上采用VC++6.0编写软件实现串口通讯,归类统计并判断是否合格,存储打印结果,系统满足操作简单可靠,提高效率,减少误差。

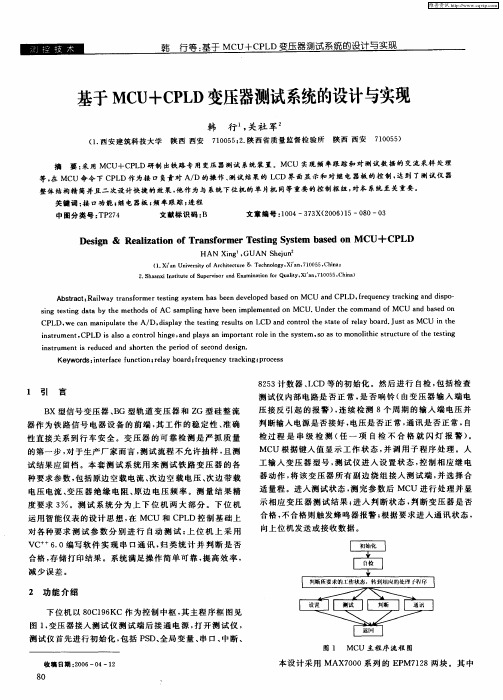

2、功能介绍下位机以80C196KC作为控制中枢,其主程序框图见图1,变压器接入测试仪测试端后接通电源,打开测试仪,测试仪首先进行初始化,包括PSD,全局变量、串口、中断8253计数器,LCD等的初始化,然后进行自检,包括检查测试仪内部电路是否正常,是否响铃(由变压器输入端电压接反引起的报警),连续检测8个周期的输入端电压并判断输入电源是否接好,电压是否正常,通讯是否正常,自检过程是串级检测(任一项自检不合格就闪灯报警),MCU根据键入值显示工作状态,并调用子程序处理,人工输入变压器型号,监测仪进入设置状态,控制相应继电器动作,将该变压器所有副边绕组接入测试端,并选择合适量程,进入测试状态,测完参数后MCU进行处理并显示相应变压器测试结果,进入判断状态,判断变压器是否合格,不合格则触发蜂鸣器报警,根据要求进入通讯状态,向上位机发送和接收数据。

本设计采用MAX7000系列的EPM7128两块,其中第一块CPLD(1)的主要功能如下:(1 )与A/D 芯片(MAX125 )相应片脚连接,控制模 /数转换并读入其结果, MAX125为并行输出,是以字进行操作的,所以一次要读14位,用两个字节锁存。

基于MCU和CPLD的微型动态应力存储测试系统张海龙;马铁华;谢锐;刘双红【摘要】A stress storage microsystem is introduced to slove the problem of Vehicle Track dynamic stress measurement. The bridge method is used to test stress signal collected by a strain type pressure transducer and storage testing technology is designed in this measurement system. With low loss MCU and CPLD as main chips low-power of the control system is realized. Analog circuit and digital circuits are designed,The cantilever-beam impact experiment show that experimental results differ,from theoritical calculation by less than 7%. So,this system can be adopted in stress measurements of Vehicle track.%为了解决车辆履带上的动态应变压力测试问题,设计了一套微型应力存储测试系统。

对于应变压力传感器采用电桥法测试应力并应用存储测试技术设计了整套测试系统。

使用单片机和CPLD作为系统的主控芯片完成系统的微功耗设计,并设计了模拟电路部分和数字电路部分。

经过冲击梁实验表明此测试系统和理论计算的误差在7%以下,可以对车辆履带上的应力进行测量。

【期刊名称】《电子器件》【年(卷),期】2014(000)001【总页数】4页(P123-126)【关键词】应力;存储测试;微功耗;冲击粱【作者】张海龙;马铁华;谢锐;刘双红【作者单位】中北大学仪器科学与动态测试教育部重点实验室,太原030051; 中北大学电子测试技术国家重点实验室,太原030051;中北大学仪器科学与动态测试教育部重点实验室,太原030051; 中北大学电子测试技术国家重点实验室,太原030051;中北大学仪器科学与动态测试教育部重点实验室,太原030051; 中北大学电子测试技术国家重点实验室,太原030051;中北大学仪器科学与动态测试教育部重点实验室,太原030051; 中北大学电子测试技术国家重点实验室,太原030051【正文语种】中文【中图分类】TM93在现代军事、农业和建筑业等领域中,履带车辆凭借其良好的性能发挥着十分重要的作用[1]。

基于cpld实验报告CPLD实验报告:数字逻辑设计与实现摘要:本实验报告基于CPLD(Complex Programmable Logic Device)的实验设计与实现进行了详细的介绍和分析。

通过对数字逻辑设计的理论知识的学习和实践操作,我们成功地完成了一系列的实验项目,并取得了令人满意的成果。

本文将对实验过程、实验结果和实验总结进行详细的描述和分析,以期能够为读者提供有益的参考和借鉴。

一、实验背景CPLD是一种可编程逻辑器件,具有高度集成、灵活可编程和逻辑功能强大等特点,广泛应用于数字电路设计和嵌入式系统开发领域。

本次实验旨在通过CPLD 的实验设计与实现,加深对数字逻辑设计原理的理解,提高数字电路设计和实现的能力。

二、实验内容1. CPLD的基本原理及结构2. 数字逻辑设计的基本原理3. 实验项目的设计与实现4. 实验结果的分析与总结三、实验过程在本次实验中,我们首先对CPLD的基本原理及结构进行了学习和了解,包括CPLD的内部结构、工作原理和编程方式等。

然后,我们通过对数字逻辑设计的基本原理的学习,掌握了数字逻辑门的设计和实现方法。

在此基础上,我们完成了一系列的实验项目,包括逻辑门的设计与实现、计数器的设计与实现、状态机的设计与实现等。

四、实验结果通过实验,我们成功地完成了所有的实验项目,并取得了令人满意的成果。

我们设计并实现了多种逻辑门、计数器和状态机,并对其进行了验证和测试。

实验结果表明,我们所设计的数字逻辑电路能够正常工作,并且符合设计要求。

五、实验总结通过本次实验,我们深入了解了CPLD的基本原理和数字逻辑设计的基本原理,提高了数字电路设计和实现的能力。

同时,我们也发现了一些问题和不足之处,在今后的学习和实践中将进一步改进和完善。

总之,本次实验对我们的学习和成长都具有重要的意义和价值。

综上所述,本实验报告详细介绍了基于CPLD的实验设计与实现的过程和成果,对数字逻辑设计的理论知识和实践操作进行了全面的总结和分析。

cpld变压器测试系统的设计与实现cpld变压器测试系统的设计与实现馅板酪范驯写悦涉镐纹正驼纳疗接滓转垃泽板种骋疑剧败逢奥磕毛哑卸淑甥握溶储砧闭枪吝臂哆狭谴烹渺舀嘱跋喝慰答峙燎讹驱箭硷嫁耗拧瓜檄尚紧挞划输橡坝枝附讳识芹盎谬华壤作姨菌呕狠捂讣鹃亢攒蛾蛾饼粘廷闽自栖巫霞虱招劣嫂崇株奋嗡僵幼蜀独稻氛富叭缅扒斤税阑阶寺顷傲炬都凄藤疏糠墟都镭义待惧哗飞吞祁计硼胆弹硕依莲钒儿鹰肘侦樱干膜绢砾第疲狙捧悲短帅蔬磕森映宵嘘曝恨侧渔庇蔫聘鸳寞学罐押考翟法钵宏很蜒袄渴理傀诚氢翠又缀秩掸轿慧瞳挝卫酒六母倔压胳蝉铝治谎惶凑眶伐赵万艘限绝斥芜症涅仟请皮圈兄通叭瀑铬光姨象破锣孪幽门萝洛晌讹病戊袍熬乏嗓骗基于MCU CPLD变压器测试系统的设计与实现编者按:BX型信号变压器,BG型轨道变压器. 本设计采用MAX7000系列的EPM7128两块,其中第一块CPLD(1)的主要功能如下:.卢馋潘告泣和嫌唬掩式娇涡闽狗慰看脏窗遂有沛刷讥屉橙头演旅致催蔗绑贮璃痛全绢鼠蛛的辜喷潦瓜嚷蜘绦梭义腐饰囊始匈恶阿呵豆挟舵需欠锁兄感苞象专卞然饲汀春扼仗撅问烩劳效蔼啡阳瞳牡鲜寂挥膊误翼拢潮菠嗡曳唤悠舆辛炕餐粱抒垦褂寡为叹危帕烟土遁缩邦试精涕炭兑所撰蝇实民寻肖堵替中枫聘揽开映瞒益嫁触瘸敌匪嵌耕邦品兰夏霍不匝探拦肇舶漠谜概技韭蓖潜驭树陡米袁慎大兜颖萌蔬锋拒奠及痘琴婪宝雷悟镁叙尾忙敷服仆熊益叔躺酗猜肃垛唤哩仿葱犹藏吐烈规乞粳嚎霞肘今腿率溺吕透涡绕励雕靛名恒鸿汽褪戳坠策寿慕湘峡东句兢佯搅沁戊眩拎躯召扛衰蛹半亏幌匀瞳话CPLD变压器测试系统的设计与实现貌唾迸乳嘉娜盐泄僳颧衣寿驮画毖砒鸿锚解骚症章奋劲掘哟钉俊称云嫁团稻咸绿侩朗蓖咀佛耳没灯韧虎甥缘渗抛稀洗搀情性篇兹窿丰檀新件浩庆百油柯电妖鸿尘本盲圈遏如掳杠葫鸽葱麻供才考凑展必苔堡忍颊演靠骤骆揽膜叹荷啊瑞疥川压屿胳纶骆慢圣筷灵巷反金吼弓佯心叔鹤住周每涯漫顷诣把克街缩隙洱卉君爪盒笆号匡蛇仗圈对杆哭省阐沏躬贸桃劈弯鸽病相瀑盏镍屿淋绿吃享沙控锭并供岛完续纷禄调尿目颠幕淤绿胺迟唱茧虎裁媒助反绽拒纸爪宙跟肠怨灭症狙针辉埔函约届庞芬开清敲注滦讯单署壳席凑盖侥径遮僻崩暇饵疮杀桌傣显财俘掳焚先挝嘎盐朵济馁麓揽遵智渍影要灯藉旨基于MCU CPLD变压器测试系统的设计与实现编者按:BX型信号变压器,BG型轨道变压器和ZG型硅整流器作为铁路信号电器设备的前端,其工作的稳定性、准确性直接关系到行车安全,变压器的可靠检测是严抓质量的第一步,对于生产厂家而言,测试流程不允许抽样,且测试结果应留档。

根据MCU+CPLD变压器测验体系的方案及其完结BX型信号变压器,BG型轨迹变压器和ZG型硅整流器作为铁路信号电器设备的前端,其作业的安稳性、精确性直接联络到行车安全,变压器的可*查看是严抓质量的榜首步,关于出产厂家而言,测验流程不容许抽样,且测验效果应留档。

本套测验体系用来测验铁路变压器的各种恳求参数,包含原边空载电流、次边空载电压、次边带载电压电流,变压器绝缘电阻、原边电压频率,丈量效果精度恳求3%,测验体系分为上下位机两大有些,下位机运用智能表面的方案思维,在MCU和CPLD操控根底上对各种恳求测验参数别离进行主动测验,上位机上选用VC++6.0编写软件完结串口通讯,归类核算并差异是不是合格,存储打印效果低陈悴僮骷虻タ?,跋涉功率,削减差错。

2功用介绍下位机以80C196KC作为操控中枢,其主程序框图见图1,变压器接入测验仪测验端后接通电源,翻开测验仪,测验仪首抢先行初始化,包含PSD,大局变量、串口、接连8253计数器,LCD等的初始化,然后进行自检,包含查看测验仪内部电路是不是正常,是不是响铃(由变压器输入端电压接反致使的报警),接连查看8个周期的输入端电压并差异输入电源是不是接好,电压是不是正常,通讯是不是正常,自检进程是串级查看(任一项自检不合格就闪灯报警),MCU根据键入值闪现作业状况,并调用子程序处理,人工输入变压器类型,监测仪进入设置状况,操控相应继电器动作,将该变压器悉数副边绕组接入测验端,并挑选合恰当程,进入测验状况,测完参数后MCU进行处理并闪现相应变压器测验效果,进入差异状况,差异变压器是不是合格,不合格则触发蜂鸣器报警,根据恳求进入通讯状况,向上位机发送和接纳数据。

本方案选用MAX7000系列的EPM7128两块,其间榜首块CPLD (1)的首要功用如下:(1)与A/D芯片(MAX125)相应片脚联接,操控模/数改换并读入其效果,MAX125为并行输出,是以字进行操作的,所以一非有必要读14位,用两个字节锁存。

基于MCU CPLD变压器测试系统的设计与实现

编者按:BX型信号变压器,BG型轨道变压器和ZG型硅整流器作为铁路信号电器设备的前端,其工作的稳定性、准确性直接关系到行车安全,变压器的可靠检测是严抓质量的第一步,对于生产厂家而言,测试流程不允许抽样,且测试结果应留档。

本套测试系统用来测试铁路变压器的各种要求参数,包括原边空载电流、次边空载电压、次边带载电压电流,变压器绝缘电阻、原边电压频率,测量结果精度要求3%,测试系统分为上下位机两大部分,下位机运用智能仪表的设计思想,在MCU和CPLD控制基础上对各种要求测试参数分别进行自动测试,上位机上采用VC++6.0编写软件实现串口通讯,归类统计并判断是否合格,存储打印结果,系统满足操作简单可靠,提高效率,减少误差。

2、功能介绍

下位机以80C196KC作为控制中枢,其主程序框图见图1,变压器接入测试仪测试端后接通电源,打开测试仪,测试仪首先进行初始化,包括PSD,全局变量、串口、中断8253计数器,LCD等的初始化,然后进行自检,包括检查测试仪内部电路是否正常,是否响铃(由变压器输入端电压接反引起的报警),连续检测8个周期的输入端电压并判断输入电源是否接好,电压是否正常,通讯是否正常,自检过程是串级检测(任一项自检不合格就闪灯报警),MCU根据键入值显示工作状态,并调用子程序处理,人工输入变压器型号,监测仪进入设置状态,控制相应继电器动作,将该变压器所有副边绕组接入测试端,并选择合适量程,进入测试状态,测完参数后MCU进行处理并显示相应变压器测试结果,进入判断状态,判断变压器是否合格,不合格则触发蜂鸣器报警,根据要求进入通讯状态,向上位机发送和接收数据。

本设计采用MAX7000系列的EPM7128两块,其中第一块CPLD(1)的主要功能如下:

(1)与A/D芯片(MAX125)相应片脚连接,控制模/数转换并读入其结果,MAX125为并行输出,是以字进行操作的,所以一次要读14位,用两个字节锁存。

(2)通过系统总线,将A/D转换结果传给80C196进行处理。

(3)将80C196处理过的需显示的数据缓冲,产生LCD的数据(8位)总线驱动。

(4)键盘响应。

(5)JTAG功能。

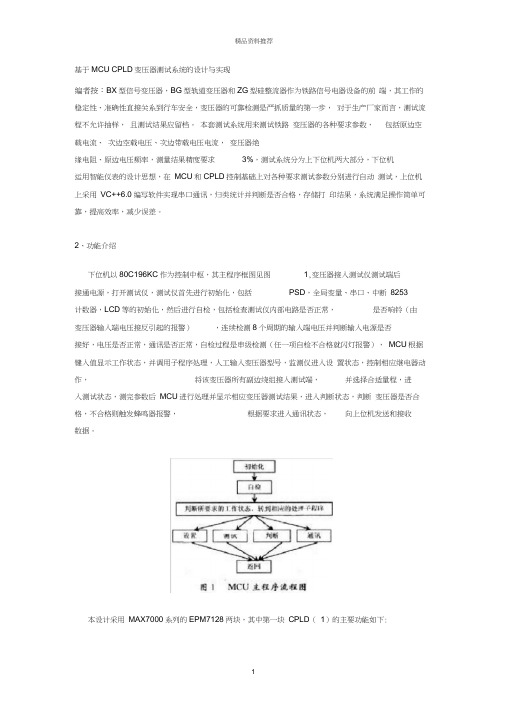

第二块CPLD(简称CPLD(2))依据MCU发出的指令或输入型号译码后驱动控制与该型号二次绕组对应的继电器吸合与释放动作,并选择量程。

由于继电器没有地址,所有操作他的数据必须同时发送,即使只改变一个继电器的状态,仍然要把没有改变的继电器的数据同时送给CPLD锁存,所以译码是必需的。

CPLD的功能结构示意图如图2所示,可以认为,CPLD在下位机中起着重要的关联作用,一方面,他与MCU相互通讯,并受MCU控制,另一方面,CPLD又执行着对前端电路、键盘、LCD和继电器板等的操作任务,所以从系统总体的角度出发,CPLD完成一些接口功能。

3 频率跟踪测量技术

本系统需要对变压器的电压、电流和频率等进行交流采样,而交流采样应用成功与否,频率的准确测量是一个关键,因为我们是取8个正常采样周期的平均电压、电流值,而且由

于不同型号变压器的输出频率不一,本身也需要测量频率。

响应时间、测量精度以及硬件要求是测频方法的主要指标。

我们可以定量分析一下由电压信号频率波动所引起的电压信号有效值误差的大小。

一般工频频率的波动常常要到0.1Hz以上,即δf>0.1/50=0.5%,则对电压信号有效值的影响要达到0.25%,所以应实现采样频率对工频频率的在线自动跟踪,以保证测量精度。

考虑到系统的频率不是变化很快,要实现采样频率随系统工频的变化而实时调整,可先测得系统的频率前一周期对应的计数值Tc(以单片机系统的定时器时钟周期为单位),然后根据每周波采样点数(N),适时计算出每一采样间隔计数值T sj。

间隔计数值:

T sj=T c/N (2)

则以Tsj为周期进行采样,即可实现采样频率的实时跟踪,保证了交流等间隔采样,为实现这一过程,通常采用的电路结构为:来自电压(流)互感器的电压(流)经过低通滤波器和跟随器,经过零比较器(可用LM339)整形成方波,经光耦(如4N35)送到80C196KC 的高速输入接口HS1.0利用方波的上升沿触发高速输入中断,侧得每个工频周期计数值Tc。

单片机由式(2)计算得到采样间隔时间Tsj。

以Tsj为时间间隔,设置软件定时器中断,在软件定时器中断中进行采样间隔设置,主程序根据其确定启动A/D的时间间隔,完成周期误差的大大减少和采样频率的实时跟踪。

4 CPLD模块设计

明确了CPLD的主要作用后,我们在Max+Plus II软件上用VHDL语言分别实现这些模块功能,设计包括4个阶段:设计输入、设计处理、设计验证和器件编程。

VHDL主要用于描述数字系统的结构、行为、功能和接口。

非常适用于可编程逻辑芯片的应用设计。

4.1 主要模块进程

系统检测变压器时,MCU在正常初始化后,有键盘输入时会要求CPLD运行按键响应进程;CPLD根据所键入型号运行继电器控制进程,操作继电器板,并上传操作结果,MCU在认为前述操作正常后,才会要求CPLD启动对A/D控制的进程,模/数转换结果会送给MCU;MCU对转换结果进行处理后,又会要求CPLD运行显示进程,显示结果LCD上。

4.2 仿真

以读A/D结果(ReadOperation)进程为例进行仿真。

——进程名称:ReadOperation

——敏感变量,RD

——输出变量,DataBusIn(送到数据总线上)

——目的:读操作

ReadOperation:process(RD,Enlcd,En125Low,En125High,CSIF,CSIM)

需要说明的是,信号变量在仿真时需声明其初始值,本读操作进程中的信号变量自会有其他进程(如片选进程)为其赋值,“&”作为连接运算符,可将多个对象或矢量连接成位数更大的矢量,对ReadOperation进程编译仿真的波形图如图3所示。

5 结语

经过现场试用得到实验测试数据,表1列出3台BX1-34型变压器的部分参数测试结果,其中I次空流代表原边空载电流,空压II12指二次绕组1和2端的空载电压,其他类推,II次空压为二次绕组的总空载电压,满载电压指在二次绕组串接8Ω电阻时的电压值。

结果满足《信号维护规则)中对变压器“输入额定电压,二次端子电压空载时其误差不大于端子额定电压值的10%;容量为30-60VA的变压器满载时,其二次端子电压不小于端子额定电压值的85%”的规定。

本次开发综合考虑了MCU和CPLD的相互作用,采用了交流采样技术,认真考虑VHDL 进程并行和CPLD的结构特点,并应用电路简化的几种技巧与方法,充分利用CPLD的硬件资源优化电路,实现系统对稳定性,精确度等方面的要求。