miniLVDS简介(中文)

- 格式:pdf

- 大小:405.34 KB

- 文档页数:9

LVDS是低电压差分信号(Low-Voltage Differential Signaling)的简称,它是一种高速串行数字接口标准。

它由National Semiconductor(现在是 Texas Instruments公司)在1980年代末为液晶显示器(LCD)设计开发的。

LVDS信号主要用于高速数据传输,如在计算机、网络、通信设备和显示器等领域中。

LVDS信号的原理是通过两条不同电平的差分信号来传输数据。

一条线路上的信号电平为高电平(通常为Vcc),而另一条线路上的信号电平为低电平(通常为GND)。

由于这两个信号的电平差异很大,因此LVDS可以在长距离传输高速数据而不容易受到干扰。

LVDS信号具有如下特点:低功耗,高带宽,抗干扰能力强,传输距离远。

根据LVDS的标准,传输速率可以达到每秒1.2 Gbit/s(gigabit per second),而功耗却可以控制在1mA以下。

此外,LVDS信号的传输距离可以达到15米,而且不会因为距离的增加而损失信号质量。

在LVDS信号传输中,一般采用对称电阻负载以及差分驱动的方式来减小串扰噪声的影响。

LVDS驱动器通常采用差分晶体管对的方式来提供高驱动电压和高带宽,传输线上也采用了对称的电阻负载。

这两者的结合使得LVDS传输能够抵抗干扰信号的影响,并实现高速稳定的数据传输。

LVDS信号在现代电子设备中得到广泛应用。

例如,在计算机领域中,LVDS信号用于连接显卡和显示器之间的数据传输;在通信设备中,LVDS信号用于传输高速数据和音频信号;在汽车电子中,LVDS信号用于连接汽车内部的各种显示器和摄像头等设备。

总结来说,LVDS信号是一种高速、低功耗、抗干扰能力强的串行数字接口标准。

它通过差分信号的方式实现数据的高速传输,并且具有较长的传输距离。

由于其优越的特性,LVDS信号在现代电子设备中得到广泛的应用。

完整版)LVDS接口详解LVDS输出接口是一种数字视频信号传输方式,它利用低压差分信号技术接口,在两条PCB走线或一对平衡电缆上通过差分进行数据的传输。

相比于TTL接口,LVDS输出接口具有高速率、低噪声、远距离、高准确度等优点,因此在17in及以上液晶显示器中得到了广泛的应用。

LVDS接口电路由驱动板侧的LVDS输出接口电路(LVDS发送器)和液晶面板侧的LVDS输入接口电路(LVDS接收器)组成。

LVDS发送器将驱动板主控芯片输出的17L电平并行RGB数据信号和控制信号转换成低电压串行LVDS信号,然后通过柔性电缆传送到液晶面板侧的LVDS接收器。

LVDS接收器再将串行信号转换为TTL电平的并行信号,送往液晶屏时序控制与行列驱动电路。

在数据传输过程中,LVDS接口采用差分信号对的形式进行传输,每个数据传输通道或时钟传输通道的输出都为两个信号(正输出端和负输出端)。

这种方式不仅可以提高数据传输速率,还可以减少电磁干扰和功耗,使得LVDS输出接口更加稳定可靠。

不同种类的液晶显示器的驱动板上的LVDS发送器并不相同。

有些LVDS发送器是一片或两片独立的芯片,例如DS90C383;而有些则是集成在主控芯片中,例如主控芯片gm5221内部集成了LVDS发送器。

LVDS输出接口也分为四种类型,其中第一种是单路6位LVDS输出接口。

这种接口电路采用单路方式传输,每个基色信号(即RGB三色中的其中任何一种颜色)采用6位数据(XOUT0+、TXOUT0-,TXOUT1+、TXOUT1-,TXOUT2+、TXOUT2-),共18位RGB(6bit X 3(RGB3色))数据,因此也被称为18位或18bit LVDS接口。

第二种是双路6位LVDS输出接口。

在这种接口电路中,两个基色信号(例如红色和绿色)共用一条传输线,而蓝色信号则使用另一条传输线,每个基色信号采用6位数据,因此也被称为双路18位或18bit LVDS接口。

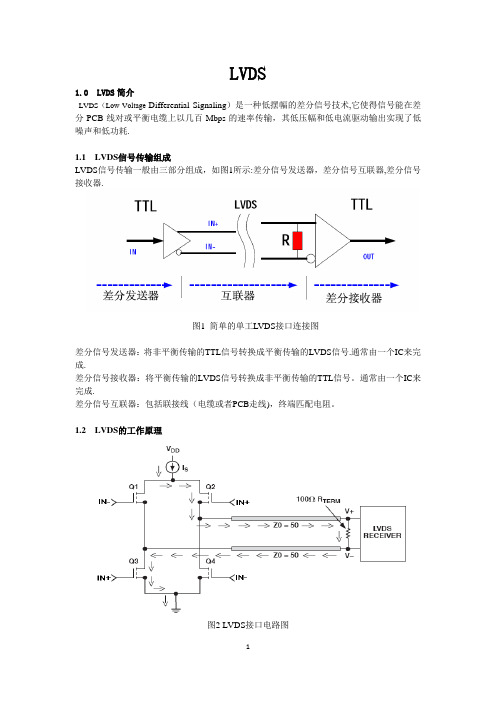

LVDS1.0 LVDS简介LVDS(Low Voltage Differential Signaling)是一种低摆幅的差分信号技术,它使得信号能在差分PCB线对或平衡电缆上以几百Mbps的速率传输,其低压幅和低电流驱动输出实现了低噪声和低功耗.1.1 LVDS信号传输组成LVDS信号传输一般由三部分组成,如图1所示:差分信号发送器,差分信号互联器,差分信号接收器.图1 简单的单工LVDS接口连接图差分信号发送器:将非平衡传输的TTL信号转换成平衡传输的LVDS信号.通常由一个IC来完成.差分信号接收器:将平衡传输的LVDS信号转换成非平衡传输的TTL信号。

通常由一个IC来完成.差分信号互联器:包括联接线(电缆或者PCB走线),终端匹配电阻。

1.2 LVDS的工作原理图2 LVDS接口电路图如图2所示,LVDS驱动器由一个驱动差分线对的电流源组成(通常电流为3。

5mA),LVDS 接收器具有很高输入阻抗,因此驱动器输出的电流大部分都流过100Ω的匹配电阻,并在接收器的输入端产生生大约350mV的电压。

驱动器的输入为两个相反的电平信号,四个nMOS管的尺寸工艺是完全相同的.当输入为“1”时,标号IN+的一对管子导通,另一对管子截止,电流方向如图2,并产生大约350mV的压降;反之,输入为“0”时,电流反向,产生大约350mV的压降.这样根据流经电阻的电流方向,就把要传输的数字信号(CMOS信号)转换成了电流信号(LVDS信号)。

接受端可以通过判断电流的方向就得到有效的逻辑“1”和逻辑“0"状态。

从而实现数字信号的传输过程。

由于MOS管的开关速度很高,并且LVDS的电压摆幅低(350mV),因此可以实现高速传输.其电平特性如下图所示1.3 LVDS的国际标准LVDS是目前高速数字信号传输的国际通用接口标准,国际上有两个工业标准定义了LVDS:ANSI/TIA/EIA(American National Standards Institute/Telecommunications Industry Association/Electronic Industries Association)和IEEE(Institute for Electrical and Electronics Engineering)。

转载什么是LVDS及LVDS针脚定义[转载]什么是LVDS及LVDS针脚定义2010年06月01日 什么是LVDS? 现在的液晶显示屏普遍采用LVDS接口,那么什么是LVDS呢? LVDS(Low Voltage Differential Signaling)即低压差分信号传输,是一种满足当今高性能数据传输应用的新型技术。

由于其可使系统供电电压低至 2V,因此它还能满足未来应用的需要。

此技术基于 ANSI/TIA/EIA-644 LVDS 接口标准。

LVDS 技术拥有 330mV 的低压差分信号 (250mV MIN and 450mV MAX)和快速过渡时间。

这可以让产品达到自 100 Mbps 至超过 1 Gbps的高数据速率。

此外,这种低压摆幅可以降低功耗消散,同时具备差分传输的优点。

LVDS技术用于简单的线路驱动器和接收器物理层器件以及比较复杂的接口通信芯片组。

通道链路芯片组多路复用和解多路复用慢速 TTL信号线路以提供窄式高速低功耗 LVDS 接口。

这些芯片组可以大幅节省系统的电缆和连接器成本,并且可以减少连接器所占面积所需的物理空间。

LVDS 解决方案为设计人员解决高速 I/O 接口问题提供了新选择。

LVDS 为当今和未来的高带宽数据传输应用提供毫瓦每千兆位的方案。

更先进的总线 LVDS (BLVDS)是在LVDS 基础上面发展起来的,总线 LVDS (BLVDS) 是基于 LVDS技术的总线接口电路的一个新系列,专门用于实现多点电缆或背板应用。

它不同于标准的LVDS,提供增强的驱动电流,以处理多点应用中所需的双重传输。

BLVDS 具备大约 250mV 的低压差分信号以及快速的过渡时间。

这可以让产品达到自 100 Mbps 至超过 1Gbps 的高数据传输速率。

此外,低电压摆幅可以降低功耗和噪声至最小化。

差分数据传输配置提供有源总线的 +/-1V 共模范围和热插拔器件。

BLVDS 产品有两种类型,可以为所有总线配置提供最优化的接口器件。

LVDS(低电压差分信号)原理简介1 、LVDS信号介绍LVDS:Low Voltage Differential Signaling,低电压差分信号。

LVDS传输支持速率一般在155Mbps(大约为77MHZ)以上。

LVDS是一种低摆幅的差分信号技术,它使得信号能在差分PCB线对或平衡电缆上以几百Mbps的速率传输,其低压幅和低电流驱动输出实现了低噪声和低功耗。

IEEE在两个标准中对LVDS信号进行了定义。

ANSI/TIA/EIA-644中,推荐最大速率为655Mbps,理论极限速率为1.923Mbps。

1.1 LVDS信号传输组成图1 LVDS信号传输组成图LVDS信号传输一般由三部分组成:差分信号发送器,差分信号互联器,差分信号接收器。

差分信号发送器:将非平衡传输的TTL信号转换成平衡传输的LVDS信号。

通常由一个IC来完成,如:DS90C031差分信号接收器:将平衡传输的LVDS信号转换成非平衡传输的TTL信号。

通常由一个IC来完成,如:DS90C032差分信号互联器:包括联接线(电缆或者PCB走线),终端匹配电阻。

按照IEEE 规定,电阻为100欧。

我们通常选择为100,120欧。

1.2 LVDS信号电平特性LVDS物理接口使用1.2V偏置电压作为基准,提供大约400mV 摆幅。

LVDS驱动器由一个驱动差分线对的电流源组成(通常电流为3.5mA),LVDS接收器具有很高的输入阻抗,因此驱动器输出的电流大部分都流过100Ω的匹配电阻,并在接收器的输入端产生大约350mV 的电压。

电流源为恒流特性,终端电阻在100――120欧姆之间,则电压摆动幅度为:3.5mA * 100 = 350mV ;3.5mA * 120 = 420mV 。

下图为LVDS与PECL(光收发器使用的电平)电平变化。

图2 LVDS与PECL电平图示由逻辑“0”电平变化到逻辑“1”电平是需要时间的。

由于LVDS信号物理电平变化在0。

FPGA的LVDS介绍和xilin x原语的使用方法中文说明低压差分传送技术是基于低压差分信号(L ow Volt-agc Diff erential signali n g)的传送技术,从一个电路板系统内的高速信号传送到不同电路系统之间的快速数据传送都可以应用低压差分传送技术来实现,其应用正变得越来越重要。

低压差分信号相对于单端的传送具有较高的噪声抑制功能,其较低的电压摆幅允许差分对线具有较高的数据传输速率,消耗较小的功率以及产生更低的电磁辐射。

L VDS:Low VoltageDifferential Sig naling,低电压差分信号。

LVDS传输支持速率一般在155Mbps(大约为77MHZ)以上。

LVDS是一种低摆幅的差分信号技术,它使得信号能在差分P CB线对或平衡电缆上以几百Mbp s的速率传输,其低压幅和低电流驱动输出实现了低噪声和低功耗。

差分信号抗噪特性从差分信号传输线路上可以看出,若是理想状况,线路没有干扰时,在发送侧,可以形象理解为:IN= IN+ —IN-在接收侧,可以理解为:IN+ —IN- =OUT所以:OUT = I N在实际线路传输中,线路存在干扰,并且同时出现在差分线对上,在发送侧,仍然是:IN =IN+ —IN-线路传输干扰同时存在于差分对上,假设干扰为q,则接收则:(IN+ +q) —(IN- + q) =IN+ —IN- = OUT所以:OUT = IN噪声被抑止掉。

上述可以形象理解差分方式抑止噪声的能力。

F rom: 美国国家半导体的《LV DS用户手册》P9FPGA中的差分管脚为了适用于高速通讯的场合,现在的FPGA都提供了数目众多的LVDS接口。

如Spartan-3E系列FPGA提供了下列差分标准:LVD SBus LVDSm ini-LVDSRSDSDifferential H STL (1.8V, Types I and III)Di fferential SSTL(2.5V and 1.8V,Type I)2.5V L VPECL inputs所拥有的差分I/O管脚数目如下From:Spart an-3E FPGA Famil y:Complete DataSheet p5I/O管脚的命名方式:Fro m:Spartan-3E FPG A Family:Complet e Data Sheet p164From:Sp artan-3E FPGA Fa mily:Complete Da ta Sheet p18Spartan-3E系列FPG A器件差分I/O接口输入工作的特性参数:Fro m:Spartan-3E FPG A Family:Complet e Data Sheet p126Spartan-3E系列FPGA器件差分I/O接口输出工作的特性参数:From:Spartan-3EFPGA Family:Comp lete Data Sheetp127Xilinx公司差分原语的使用(原语,其英文名字为Primitive,是Xi linx针对其器件特征开发的一系列常用模块的名字,用户可以将其看成Xilinx公司为用户提供的库函数,类似于C+ +中的“cout”等关键字,是芯片中的基本元件,代表FPGA中实际拥有的硬件逻辑单元,如LUT,D触发器,RAM等,相当于软件中的机器语言。

Proposal for mini-LVDS specification in JEITA28th December, 2007Leader Keiichi Nakajima (NEC Electronics Corp.)LCD Driver IC Standardization Project GroupTechnical Committee on Integrated CircuitSemiconductor Product Technology Committee Japan Electronics and Information Technology Industries AssociationDear SirWe have set up to discuss about specifications and terminology of LCD driver ICs and timing controllers who are listed in below at November 2006 in JEITA.Now many kinds of LCD driver ICs and timing controllers are applied in LCD displays but there are no standard. And so each LCD manufacturer and semiconductor venders are facing to spend much time to agree the specifications for driver ICs and timing controllers.Therefore we would like to provide the reference document and standard for intra-panel interface based on mini-LVDS.Our technical document for intra-panel interface doesn’t mean a forced standard and it means to provide the guide line to consider the specification between the driver ICs and the timing controller at this moment.Now we disclose out technical document for the intra-panel interface specification to LCD manufacturers and we expect to get some feed back to make tight relation ship between LCD manufacturers and semiconductor venders.If you have an interesting and any questions or request for us, Please fill up the attached form and feed back to us.Best Regards,Project Group MemberKawasaki Microelectronics, Inc., Matsushita Electric Industrial Co., Ltd., NEC Electronics Corp., Oki Electric Industry Co.,Renesas Technology Corp., Rohm Co., Ltd.Sanyo Semiconductor Co., Ltd., Seiko Epson Corp.,Inc.,ThineElectronics,SharpCorp.,Toshiba Corp.Special Member from the Display Board in JEITAToshiba Matsushita Display Technology Co., Ltd.,NEC LCD Technology Co., Ltd.Feed back form regarding the JEITA mini-LVDS standard To JEITA LCD driver IC standardization PG memberFromName :Title :Company:Date :Your opinions for the standardization and feed back for the proposalThank you for your cooperation.Proposal For mini-LVDSSpecifications ver. 0.1December 2007LCD Driver IC Specification Standardization Project GroupIntegrated Circuit Sub CommitteeSemiconductor Product Technology CommitteeJapan Electronics and Information Technology Industries Association1. Pin configuration and Data Mapping 1.1 12-bit transferring1.2 10-bit transferring1.3 8-bit transferring(d) 4-pair mode1.3 6-bit transferring2. Transmitter SpecificationIf there are much margin between driver IC and timing controller, these specifications are able to be relax to 0.2 TM.The TP1 signal means latch pulse for driver IC that the latch pulse comes from timing controller and transfer display data to internal memory in every horizontal line.The POL signal defines the analog output polarity.63. Receiver Specification784. Timing Chart of specification 4.1 TransmitterRL=100 OhmV CM+V OD-VOD+V trtfV P -V NUse a differentialprobe to observe this waveform9su su h hLVCLKPLVCLKNLVnNLVnPm=0,1, (7)SKEW104.2 ReceiverV ICM+V ID-VID+V trtfV P -V NUse a differentialprobe to observe this waveform11su su h hLVCLKPLVCLKN124.3 Reset Timing134.4 POL and TP1 TimingTP1The end of document14。

Mini LVDS规范及其眼图测试Mini LVDS是一种高速串行差分信号,广泛应用于液晶显示领域。

对于Tconless屏,目前行业内所有2K屏,部分4K都支持mini LVDS作为传输视频数据。

Mini LVDS是LVDS的一种延伸,mini LVDS与LVDS具有如下异同点:1.LVDS与mini LVDS均为以直流电平基础上传输交流信号,LVDS与Min LVDS差分信号约有1.1-1.3V直流电平2.交流电平(Swing)幅值电平;LVDS与Mini LVDS一般要求为200-400mV;Swing过大,会造成EMI问题,但过少同样会造成显示问题行业LVDS的Data在一个CLK周期内传输7bit数据,mini LVDS仅在CLK上升沿与下降沿传输数据,即在一个CLK周期内传输2bit数据。

4.CLK时钟频率不一样,LVDS普遍为74.25MHz,mini LVDS时钟频率普通更高大概在189MHz < Clock Frequency < 290MHzmini-LVDS是一个可以解决这些问题的高速串行接口。

本文档描述了该接口的电气特性和逻辑特性。

mini-LVDS提供了一个低EMI,高带宽的显示驱动程序接口,这是特别适合TFT LCD面板列驱动程序。

mini-LVDS是定时控制器和列驱动程序之间的接口(见图1)。

该文档不包括定时控制器和行驱动器之间的信号,也不包括列驱动器之间的信号(例如,可用于将列驱动器进入断电模式)mini-LVDS是一个从定时控制器到列驱动程序的单向接口。

从拓扑上讲,它是一个双总线,每个总线都携带面板左或右半部分的视频数据。

这些总线随后分别被称为RLV和LLV。

见图2物理上,每条总线由印刷电路板上的多对传输线路组成,每对都携带差分序列化视频和控制信息。

信号对的数量留给特定的实现,并且主要由列驱动器半导体技术可以支持的最大频率决定。

组成xLV(x是R或L)的个体对称为xLVi,对于由n个+1个数据对组成的总线,i的范围从0到n。

摘要在平板显示领域,尤其对于液晶显示面板,分辨率越来越高的这种趋势正一步一步将常规接口对显示面板的驱动能力推向极限。

现代技术水平的显示器,其总带宽要求已经在5 Gbps的范围内,而且还会增加。

这就必需要时序控制器和显示驱动器之间有大量的连接,这也成为显示器面积进一步减小的瓶颈。

由于这种大量的互连还会带来电磁干扰,这也是一个问题。

传统的并行CMOS接口,虽然在过去的低分辨率显示时代表现良好,却再也不适用于如今的显示器。

Mini-LVDS是一种高速串行接口,应运而生。

本SPEC就是来说明该接口的电气特性与逻辑特性。

Mini-LVDS产生很低的电磁干扰(EMS),为显示驱动提供很高的带宽,这尤其适合用于TFT LCD列驱动器。

TFT液晶面板就是像素的二维点阵,n行×m列。

每个像素又包含三个子像素(RBG),在同一行紧密相连。

面板的像素采用有源矩阵寻址方案写入的,即通过列驱动器将整行像素同时更新,从第一行到最后一行顺序更新,如此反复。

时序控制器必须在一个行周期(~10us)内为一整行像素寻找视频数据源。

此视频数据包含了这三个子像素的强度信息(6bit 或8bit)。

时序控制器从图形控制器那里获得视频数据。

输入的视频数据已将控制信号格式化为规定的视频帧信号和行信号。

时序控制器从中提取视频数据并将其重新分配到列驱动器,同时向行驱动器发出控制信号对TFT矩阵进行寻址。

1. 概览Mini-LVDS是连接时序控制器与列驱动器的接口,见图1。

在后续的章节中会具体描述。

注意此标准并不涉及时序控制器与行驱动器间交换的信号,或列驱动器间交换的信号(如列驱动器要进入掉电模式可能会用到)。

2.概述Mini-LVDS接口是单向性的,数据只能从时序控制芯片传到列驱动器。

从拓扑结构上看,它是双总线,每根总线分别携带着左半面板和右半面板的视频数据。

相应总线分别表示为LLV和RLV.见图2.从物理结构中看,在PCB板上每根总线包含很多对传输线,每一对传输线上携带着差分串行视频信号和控制信号。

液晶电视cof边板电路诊断解析及维修实例本文以三星屏、奇美等屏进行分析和介绍,主要讲解边板的作用及组成形式、边板的电路介绍(T-CON板)、如何识别各厂家液晶屏的代表符号、边板上常见问题分析、边板部分的维修思路分析以及维修案例解析等内容。

一、边板的作用及组成形式由主板到屏体之间的信息传递主要包含了T-CON电路、边板和COF后两者是信号的链接线,是OC与PCB链接的纽带,所以要重点研究T-CON电路的原理与维修。

根据厂家屏体设计的不同,主要包含以下几种形式:1、单独的T-CON板电路这是传统的电路组合形式,单独的边条被大多数厂家采用,同时故障率也最高,尤其是LG的边条,只要进水必须要更换便条,严重的还要坏掉COF.原理:由主板产生的LVDS信号送到T-CON板上进行处理转换成需要的各种控制信号(STV、CKV、STH、CKH、POL)及图像数据信号(RSDS)。

以并行的形式加到OC上,呈现图像。

2、边板和T-CON板一体的电路这也是传统的电路组合形式,控制方式同上,只是没有了单独的T-CON板,维修系数增加。

维修时检测几个主要的电压尤为重要:VGH、VGL、VCOM等。

3、高压板、T-CON板和边板一体这款机器少,海尔一款T315XW06 V5的OC使用这种形式。

4、主板直接输出STV、CKV、STH、CKH、POL及图像数据信号(RSDS)到边板,一般都是采用扁排线进边板,现在的一体板很多数采用这种形式,给维修带来了不便。

二、边板的电路介绍(T-CON板)T-CON板,即我们常说的逻辑板,它的结构框图如图1所示,它又被称为中控板、解压板、解码板,是液晶屏显示视频图像信号的关键部件,英语为Timer-Control(时序控制器),缩写为T-CON。

液晶屏驱动电路的供电系统,主要产生四路驱动电路所需的电压, LVDS 信号包括图像的RGB信号和行、场同步信号及时钟、使能信号;这些信号进入时序控制电路后,RGB基色信号经过转换成为RSDS图像数据信号(MINI-LVDS )。

FPGA的LVDS介绍和xilinx原语的使用方法中文说明低压差分传送技术是基于低压差分信号(Low Volt-agc Differential signalin g)的传送技术,从一个电路板系统内的高速信号传送到不同电路系统之间的快速数据传送都可以应用低压差分传送技术来实现,其应用正变得越来越重要。

低压差分信号相对于单端的传送具有较高的噪声抑制功能,其较低的电压摆幅允许差分对线具有较高的数据传输速率,消耗较小的功率以及产生更低的电磁辐射。

LVDS:Low Voltage Differential Signaling,低电压差分信号。

LVDS传输支持速率一般在155Mbps(大约为77MHZ)以上。

LVDS是一种低摆幅的差分信号技术,它使得信号能在差分PCB线对或平衡电缆上以几百Mbps的速率传输,其低压幅和低电流驱动输出实现了低噪声和低功耗。

差分信号抗噪特性从差分信号传输线路上可以看出,若是理想状况,线路没有干扰时,在发送侧,可以形象理解为:IN= IN+ —IN-在接收侧,可以理解为:IN+ —IN- =OUT所以:OUT = IN在实际线路传输中,线路存在干扰,并且同时出现在差分线对上,在发送侧,仍然是:IN = IN+ —IN-线路传输干扰同时存在于差分对上,假设干扰为q,则接收则:(IN+ + q) —(IN- + q) = IN+ —IN- = OUT 所以:OUT = IN噪声被抑止掉。

上述可以形象理解差分方式抑止噪声的能力。

From: 美国国家半导体的《LVDS用户手册》P9FPGA中的差分管脚为了适用于高速通讯的场合,现在的FPGA都提供了数目众多的LVDS接口。

如Spartan-3E系列FPGA提供了下列差分标准:LVDSBus LVDSmini-LVDSRSDSDifferential HSTL (1.8V, Types I and III)Differential SSTL (2.5V and 1.8V, Type I)2.5V LVPECL inputs所拥有的差分I/O管脚数目如下From:Spartan-3E FPGA Family:Complete Data Sheet p5I/O管脚的命名方式:From:Spartan-3E FPGA Family:Complete Data Sheet p164From:Spartan-3E FPGA Family:Complete Data Sheet p18 Spartan-3E系列FPGA器件差分I/O接口输入工作的特性参数:From:Spartan-3E FPGA Family:Complete Data Sheet p126 Spartan-3E系列FPGA器件差分I/O接口输出工作的特性参数:From:Spartan-3E FPGA Family:Complete Data Sheet p127Xilinx公司差分原语的使用(原语,其英文名字为Primitive,是Xilinx针对其器件特征开发的一系列常用模块的名字,用户可以将其看成Xilinx公司为用户提供的库函数,类似于C+ +中的“cout”等关键字,是芯片中的基本元件,代表FPGA中实际拥有的硬件逻辑单元,如LUT,D触发器,RAM等,相当于软件中的机器语言。

本科生毕业设计(论文)外文资料译文( 2011 届)译文题目Cyclone II器件系列的简介论文题目Cyclone II Device Family Data Sheet学生姓名学号专业电子信息科学班级指导教师职称信息科学与工程学院教务科制/literature/hb/cyc2/cyc2_cii51001.pdf 外文资料译文规范说明一、外文资料译文:Cyclone II器件系列简介关键词:cyclone II器件;特点;简介;在非常成功的第一代Cyclone器件系列之后,Altera的Cyclone II FPGA系列扩大低成本的FPGA的密度,最多达68,416个逻辑单元(LE),提供622个可用的输入/输出引脚和1.1M比特的嵌入式寄存器。

Cyclone II器件的制造基于300毫米晶圆,采用台积电90nm、低K值电介质工艺,这种工艺技术是使用低绝缘体过程以确保了快速有效性和低成本。

通过使硅片面积最小化,Cyclone II器件可以在单芯片上支持复杂的数字系统,而在成本上则可以和ASIC竞争。

不像其他用电力功耗和性能来换取低成本的FPGA卖主,Altera 最新一代低价位的FPGA——cyclone II FPGA系列,和同类90nmFPGA器件相比,它提高了百分之六十的性能和降低了一半的功耗。

低成本和优化特征使Cyclone II FPGA系列为各种各样的汽车、消费、通讯、视频处理、测试与测量、和其他最终市场提供理想的解决方案。

在参考设计、系统图,和IP,使用cyclone II FPGA系列可以帮助你迅速实现最总市场方案开发。

低成本的嵌入式解决方案Cyclone II 器件支持Nio s II 嵌入式处理器,能够自己完成自定义的嵌入式处理器。

Cyclone II器件还能够扩展各种外部存储器和I/O口或者嵌入式处理器的性能。

单个或多个NiosII嵌入式系统中嵌入式处理器也可以设计成cyclone II设备以提供一些额外的同时处理的能力或者甚至取代已经在你的系统中存在的嵌入式处理器。

LVDSJawen_tao2011-05-09目录一、简介 (2)1、为何要用LVDS? (2)2、LVDS信号传输组成 (2)二、LVDS电气特性 (4)三、传输协议 (5)四、线路接法 (10)五、Layout (13)一、简介LVDS(Low Voltage Differential Signal)即低电压差分信号。

1、为何要用LVDS?LVDS接口又称RS644总线接口,1994年由美国国家半导体公司(NS)提出的为克服以TTL电平方式传输宽带高码率数据时功耗大、EMI电磁干扰大等缺点而研制的一种视频信号传输模式,是一种电平标准,广泛应用于液晶屏接口。

液晶显示器驱动板输出的数字信号是TTL信号,除了包括RGB数据信号外,还包括行同步、场同步、像素时钟等信号,像素时钟信号的最高频率可超过28MHZ.采用TTL接口,数据传输速率不高(一个CLK周期只能传输1bit数据),传输距离较短,且抗电磁干扰能力比较差,会对RGB数据造成一定的影响。

另外,TTL 多路数据信号采用并行的传输方式,整个并口数量达几十路(RGB各8位,8x3=24,加 DE,HSYNC,VSYNC,至少27位),不但连接不便,而且不适合超薄化的趋势。

采用LVDS输出接口传输数据,可以使这些问题迎刃而解,实现数据的高速率、低噪声、远距离、高准确度的传输。

2、LVDS信号传输组成最基本的LVDS器件就是LVDS驱动器和接收器。

LVDS的驱动器由驱动差分线对的电流源组成,电流通常为3.5 mA。

如下图,LVDS接收器具有很高的输入阻抗,因此驱动器输出的大部分电流都流过100 Ω的匹配电阻(R=100Ω),并在接收器的输入端产生大约350 mV的电压。

(电流源为恒流特性,终端电阻在100—120 欧姆之间,则电压摆动幅度为:3.5mA x 100=350Mv;3.5mA x 120=420mV。

)当驱动器(LVDS发送)翻转时,它改变流经电阻的电流方向,因此产生有效的逻辑“1”和逻辑“0”状态。

LVDSJawen_tao2011-05-09目录一、简介 (2)1、为何要用LVDS? (2)2、LVDS信号传输组成 (2)二、LVDS电气特性 (4)三、传输协议 (5)四、线路接法 (10)五、Layout (13)一、简介LVDS(Low Voltage Differential Signal)即低电压差分信号。

1、为何要用LVDS?LVDS接口又称RS644总线接口,1994年由美国国家半导体公司(NS)提出的为克服以TTL电平方式传输宽带高码率数据时功耗大、EMI电磁干扰大等缺点而研制的一种视频信号传输模式,是一种电平标准,广泛应用于液晶屏接口。

液晶显示器驱动板输出的数字信号是TTL信号,除了包括RGB数据信号外,还包括行同步、场同步、像素时钟等信号,像素时钟信号的最高频率可超过28MHZ.采用TTL接口,数据传输速率不高(一个CLK周期只能传输1bit数据),传输距离较短,且抗电磁干扰能力比较差,会对RGB数据造成一定的影响。

另外,TTL 多路数据信号采用并行的传输方式,整个并口数量达几十路(RGB各8位,8x3=24,加 DE,HSYNC,VSYNC,至少27位),不但连接不便,而且不适合超薄化的趋势。

采用LVDS输出接口传输数据,可以使这些问题迎刃而解,实现数据的高速率、低噪声、远距离、高准确度的传输。

2、LVDS信号传输组成最基本的LVDS器件就是LVDS驱动器和接收器。

LVDS的驱动器由驱动差分线对的电流源组成,电流通常为3.5 mA。

如下图,LVDS接收器具有很高的输入阻抗,因此驱动器输出的大部分电流都流过100 Ω的匹配电阻(R=100Ω),并在接收器的输入端产生大约350 mV的电压。

(电流源为恒流特性,终端电阻在100—120 欧姆之间,则电压摆动幅度为:3.5mA x 100=350Mv;3.5mA x 120=420mV。

)当驱动器(LVDS发送)翻转时,它改变流经电阻的电流方向,因此产生有效的逻辑“1”和逻辑“0”状态。

Mini-LVDS图像采集卡( PCIe-6516)

概述 :

Mini-LVDS图像采集卡通过采集TCON板输出的Mini-LVDS信号,通过PCI-Express接口将数据传输到计算机,还原成完整的图像供显示和分析。

特性:

1、可替代从 640*480到 1920*1080等所有分辨率的 LCD屏;

2、采集到的图像数据可以实时显示到普通显示器;

3、采集到的数据可用于分析处理,可避免人为因素引起的误判;

4、遵循 mini-LVDS Specifications ver.0.2开发;

5、使用灵活,通过软件设置即可实现对多种制式的支持;

6、传输速度快,采用 PCI-Express高速总线传输。

规格:

1、支持 single bank数据总线格式

2、支持 6bit、8bit图像位宽

3、支持 3pairs、6pairs数据传输方式

4、支持从 640*480到 1920*1080的所有分辨率格式;。

![电视机板卡miniLVDS信号检测电路及装置[实用新型专利]](https://img.taocdn.com/s1/m/daf9483b33d4b14e8424685f.png)

专利名称:电视机板卡miniLVDS信号检测电路及装置专利类型:实用新型专利

发明人:陈江海,钟俊,蒋利,翁武强

申请号:CN202020273084.7

申请日:20200306

公开号:CN211481395U

公开日:

20200911

专利内容由知识产权出版社提供

摘要:一种电视机板卡miniLVDS信号(mini Low‑Voltage Differential Signaling,mini低电压差分信号)检测电路及装置,通过加入第一信号转换电路、第二信号转换电路以及主控电路,采集待测电视机板卡的miniLVDS信号,并将信号转换为目标LVTTL(Low Voltage Transistor‑Transistor Logic,低电压晶体管‑晶体管逻辑)信号再转换为主控电路易于识别和检测的HDMI信号,从而使得主控电路检测HDMI(High Definition Multimedia Interface,高清晰度多媒体接口)信号是否为标准的HDMI信号以判定待测电视机板卡的miniLVDS信号是否正确,从而解决了传统的技术方案中,由于采用人工检测的方式而存在的容易误判和效率低的问题。

申请人:东莞市金锐显数码科技有限公司

地址:523000 广东省东莞市塘厦镇沙新路59号1栋201室

国籍:CN

代理机构:深圳中一联合知识产权代理有限公司

代理人:胡鹏飞

更多信息请下载全文后查看。

摘要

在平板显示领域,尤其对于液晶显示面板,分辨率越来越高的这种趋势正一步一步将常规接口对显示面板的驱动能力推向极限。

现代技术水平的显示器,其总带宽要求已经在5 Gbps的范围内,而且还会增加。

这就必需要时序控制器和显示驱动器之间有大量的连接,这也成为显示器面积进一步减小的瓶颈。

由于这种大量的互连还会带来电磁干扰,这也是一个问题。

传统的并行CMOS接口,虽然在过去的低分辨率显示时代表现良好,却再也不适用于如今的显示器。

Mini-LVDS是一种高速串行接口,应运而生。

本SPEC就是来说明该接口的电气特性与逻辑特性。

Mini-LVDS产生很低的电磁干扰(EMS),为显示驱动提供很高的带宽,这尤其适合用于TFT LCD列驱动器。

TFT液晶面板就是像素的二维点阵,n行×m列。

每个像素又包含三个子像素(RBG),在同一行紧密相连。

面板的像素采用有源矩阵寻址方案写入的,即通过列驱动器将整行像素同时更新,从第一行到最后一行顺序更新,如此反复。

时序控制器必须在一个行周期(~10us)内为一整行像素寻找视频数据源。

此视频数据包含了这三个子像素的强度信息(6bit 或8bit)。

时序控制器从图形控制器那里获得视频数据。

输入的视频数据已将控制信号格式化为规定的视频帧信号和行信号。

时序控制器从中提取视频数据并将其重新分配到列驱动器,同时向行驱动器发出控制信号对TFT矩阵进行寻址。

1. 概览

Mini-LVDS是连接时序控制器与列驱动器的接口,见图1。

在后续的章节中会具体描述。

注意此标准并不涉及时序控制器与行驱动器间交换的信号,或列驱动器间交换的信号(如列驱动器要进入掉电模式可能会用到)。

2.概述

Mini-LVDS接口是单向性的,数据只能从时序控制芯片传到列驱动器。

从拓扑结构上看,它是双总线,每根总线分别携带着左半面板和右半面板的视频数据。

相应总线分别表示为LLV和RLV.见图2.

从物理结构中看,在PCB板上每根总线包含很多对传输线,每一对传输线上携带着差分串行视频信号和控制信号。

信号对的数量主要由列驱动器半导体技术所能支持的最大频率决定。

组成xLV(x为R或L)的单独的信号对表示为xLVi ,对一个有n+1 个数据对的总线来说,i从0到n. xLVi 的两根线是xLV iP与xLViM ,P与M表示线的正负。

xLViP 的电压高于xLViM的电压时就认为是xLVi 为高电平(逻辑值为1).

xLV包含的各组信号对都伴随着一个时钟信号对,和数据信号一样是差分对。

为了在不增加接受器复杂度的情况下降低EMI,在时钟信号的上升沿和下降沿都传输信号;也就是说,时钟频率是最大数据传输速率的一半。

时钟信号对表示为xLVCLK (x为R 或L),对应的两条线为xLVCLKP 和xLVCLKM ,见图3.

除了携带视频数据的差分信号对,构成mini-LVDS的还有两个信号,TP1 与POL。

这两种信号是由RLV与LLV共有的CMOS电平信号。

TP1是本质上是一种行分隔符,由定时控制器生成以表示每行数据传输的结束。

POL控制列驱动器输出的极性。

3.DC电气规格

3.1传输线阻抗

Mini-LVDS的数据对都有两根传输线。

实际在PCB板上,这些传输线是利用带状线或微带拓扑结构实现的。

为了支持各种不同厚度的PCB材料,时序控制器中的mini-LVDS发射机建议要能够驱动阻抗从25Ω至75Ω的传输线。

为保证信号质量,实际传输线的阻抗应在标称阻抗(Z O)的±5%以内。

3.2终止

每一数据对都要以R T=2 Z O终止。

见图4

3.3mini-LVDS发射机输出电平

当正确终止时,驱动器输出会产生一个小摆幅的差分电压。

该差分电压包含两个单端输出。

The single-ended outputs alternate between sourcing and sinking a constant current.差分电压是此恒定电流与截止电阻R T的乘积。

为了使R T能在一个很宽的范围内变动(50Ω到150Ω),在发射机内调整输出电流就很方便,且有几种方法。

在允许的截止电阻范围及操作电压下,以下规格参数对时钟信号对(xLVCLK)和数据信号对(xLV i)都适用:

3.4mini-LVDS接收机特性

Mini-LVDS接收器在接收时钟信号和数据信号时,必须在所有可运行条件下符合下列要求:

3.5 TP1与POL的输出参数

3.6 TP1与POL的输入参数

4.差分信号的时序

4.1 mini-LVDS发射机时序

4.2 接收机的交流规格参数

在可运行的条件下,接收机接收的信号必须符合如下要求才能正常工作:

5.控制信号时序

5.1 重置脉冲

此重置信号嵌套在数据流中,用来表示每一行数据的开始。

见图9。

重置脉冲的格式见图10。

重置脉冲的周期必须满足下列两个条件:

5.2 最后显示数据与TP1

时序控制器产生的TP1信号表示每一行显示数据的结束。

时序关系如图11与12所示。

图13显示在每一行结束时的综合时序图

5.3 POL 与TPI的时序关系

TPI 与POL满足以下条件,列驱动器才能正常工作:

时序控制器产生的POL信号应具有以下特点:

6.逻辑接口

6.1 概述与定义

本节定义了在mini-LVDS连接中的数据排序。

平板显示器上的任何一个像素都可用一组二维数据(i , j )唯一表示,其中i和j 分别表示该像素所在位置的行数与列数。

此处的像素表示为(i , j )P,三个子像素分别表示为(i , j )R ,(i , j )B ,(i , j)G。

用来表示子像素(i , j )X的强度的6位或8位数据被标识为(i , j )X5-0 ,或(i , j )X7-0 ,其中(i , j )Xk中的k表示强度数据的第k位,(i , j )X0 是LSB ,X表示R,B,或G。

显示数据是通过Mini-LVDS接口逐行传输的。

不同行数据的传输方式是一样的。

但行驱动器不同,各个行驱动器由时序控制器分别控制。

所以我们可以简化以上的表示方法,有iP 来表示某一行的上的第i 个像素,由此i R,i B,i G表法i P的子像素,iXk 即为强度数据iX 的第k位。

6.2 数据序列

本节讲述数据从时序控制器到列驱动器通过LLV和RLV传输时,数据位的传输顺序。

假设显示器的每一行有2m个像素。

以下的例子涵盖了很多不同的情况,有6位数据,8位数据,还有不同的数据对。

而且这此序列可以轻松扩展到有更多或更少数据对的情况下。

图如PDF资料。